Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 14                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                 |

| Supplier Device Package    | 20-LSSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f10269dsp-v0 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### NOTES FOR CMOS DEVICES

- (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN: Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between VIL (MAX) and VIH (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between VIL (MAX) and VIH (MIN).

- (2) HANDLING OF UNUSED INPUT PINS: Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

- (3) PRECAUTION AGAINST ESD: A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

- (4) STATUS BEFORE INITIALIZATION: Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

- (5) POWER ON/OFF SEQUENCE: In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current. The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

- (6) INPUT OF SIGNAL DURING POWER OFF STATE : Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

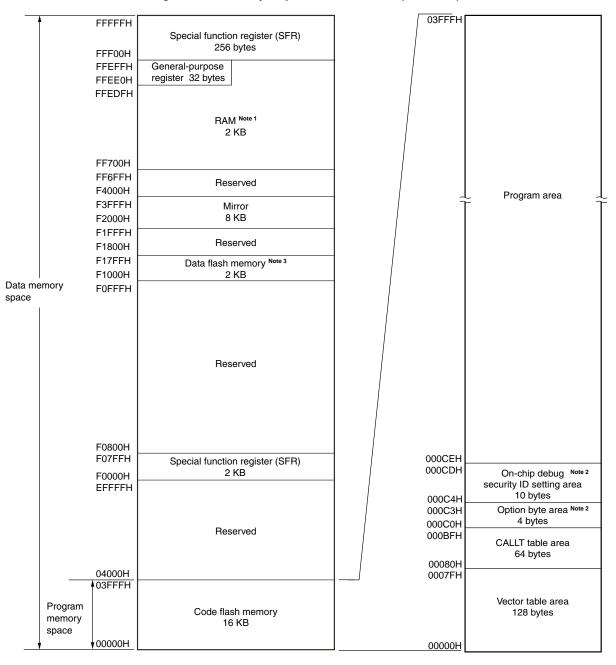

Figure 3-6. Memory Map for the R5F10xAA (x = 2 or 3)

- <R> Notes 1. Do not allocate the stack area, data buffers for use by the flash library, arguments of library functions, branch destinations in the processing of vectored interrupts, or destinations or sources for DMA transfer to the area from FFE20H to FFEDFH when performing self-programming or rewriting of the data flash memory.

- 2. Instructions can be executed from the RAM area excluding the general-purpose register area.

- 3. Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

- 4. The areas are reserved in the R5F103AA.

- **Caution** While RAM parity error resets are enabled (RPERDIS = 0), be sure to initialize RAM areas where data access is to proceed and the RAM area +10 bytes when instructions are fetched from RAM areas, respectively. Reset signal generation sets RAM parity error resets to enabled (RPERDIS = 0). For details, see 21.3.2 RAM parity error detection.

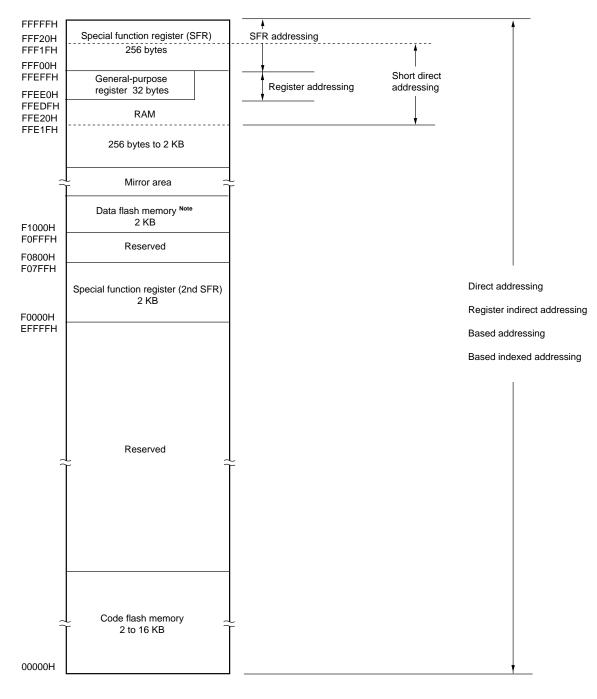

## 3.1.6 Data memory addressing

Addressing refers to the method of specifying the address of the instruction to be executed next or the address of the register or memory relevant to the execution of instructions.

Several addressing modes are provided for addressing the memory relevant to the execution of instructions for the RL78 microcontroller, based on operability and other considerations. In particular, special addressing methods designed for the functions of the special function registers (SFR) and general-purpose registers are available for use. Figure 3-8 shows correspondence between data memory and addressing.

For details of each addressing, see 3.4 Addressing for Processing Data Addresses.

Figure 3-8. Correspondence Between Data Memory and Addressing

**Note** The areas are reserved in the R5F103 products.

| 20-, 24-pi           | n produc <sup>.</sup> | ts                   |            |             |           |      |                        |      |                |                    |                     |

|----------------------|-----------------------|----------------------|------------|-------------|-----------|------|------------------------|------|----------------|--------------------|---------------------|

| Symbol               | 7                     | 6                    | 5          | 4           | 3         | 2    | 1                      | 0    | Address        | After reset        | R/W                 |

| P0                   | 0                     | 0                    | 0          | 0           | P03       | P02  | P01                    | P00  | FFF00H         | 00H (output latch) | R/W                 |

| P1                   | 0                     | 0                    | 0          | P14         | P13       | P12  | P11                    | P10  | FFF01H         | 00H (output latch) | R/W                 |

| P2                   | 0                     | 0                    | 0          | 0           | P23       | P22  | P21                    | P20  | FFF02H         | 00H (output latch) | R/W                 |

| P4                   | 0                     | 0                    | 0          | 0           | 0         | P42  | P41                    | P40  | FFF04H         | 00H (output latch) | R/W                 |

| P6                   | 0                     | 0                    | 0          | 0           | 0         | 0    | P61                    | P60  | FFF06H         | 00H (output latch) | R/W                 |

| P12                  | 0                     | 0                    | P125       | 0           | 0         | P122 | P121                   | 0    | FFF0CH         | Undefined          | R                   |

| P13                  | P137                  | 0                    | 0          | 0           | 0         | 0    | 0                      | 0    | FFF0DH         | Undefined          | R                   |

| 30-pin pro<br>Symbol | oducts<br>7           | 6                    | 5          | 4           | 3         | 2    | 1                      | 0    | Address        | After reset        | R/W                 |

| P0                   | 0                     | 0                    | 0          | 0           | 0         | 0    | P01                    | P00  | FFF00H         | 00H (output latch) |                     |

| P1                   | P17                   | P16                  | P15        | P14         | P13       | P12  | P11                    | P10  | FFF01H         | 00H (output latch) | R/W                 |

| P2                   | 0                     | 0                    | 0          | 0           | P23       | P22  | P21                    | P20  | FFF02H         | 00H (output latch) | R/W                 |

| P3                   | 0                     | 0                    | 0          | 0           | 0         | 0    | P31                    | P30  | FFF03H         | 00H (output latch) | R/W                 |

| P4                   | 0                     | 0                    | 0          | 0           | 0         | 0    | 0                      | P40  | FFF04H         | 00H (output latch) | R/W                 |

| P5                   | 0                     | 0                    | 0          | 0           | 0         | 0    | P51                    | P50  | FFF05H         | 00H (output latch) | R/W                 |

| P6                   | 0                     | 0                    | 0          | 0           | 0         | 0    | P61                    | P60  | FFF06H         | 00H (output latch) | R/W                 |

| P12                  | 0                     | 0                    | 0          | 0           | 0         | P122 | P121                   | P120 | FFF0CH         | Undefined          | R/W <sup>Note</sup> |

| P13                  | P137                  | 0                    | 0          | 0           | 0         | 0    | 0                      | 0    | FFF0DH         | Undefined          | R                   |

| P14                  | P147                  | 0                    | 0          | 0           | 0         | 0    | 0                      | 0    | FFF0EH         | 00H (output latch) | R/W                 |

|                      | Pmn                   |                      | utput data | control (in | output mo | de)  | lan di                 |      | ta read (in ir | put mode)          |                     |

|                      | 0                     | Output 0<br>Output 1 |            |             |           |      | Input lov<br>Input hiç |      |                |                    |                     |

|                      |                       |                      |            |             |           |      |                        |      |                |                    |                     |

Figure 4-2. Format of Port Register

m = 0 to 6, 12, 13, 14; n = 0 to 7

Note P121 and P122 are read-only.

Caution Be sure to set bits that are not mounted to their initial values.

## 4.3.6 Port mode control registers (PMCxx)

These registers set the digital I/O or analog input in 1-bit units.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

### Figure 4-6. Format of Port Mode Control Register

| 20-, 24-pi | in products | s           |             |            |              |              |              |              |                |             |     |  |

|------------|-------------|-------------|-------------|------------|--------------|--------------|--------------|--------------|----------------|-------------|-----|--|

| Symbol     | 7           | 6           | 5           | 4          | 3            | 2            | 1            | 0            | Address        | After reset | R/W |  |

| PMC1       | 1           | 1           | 1           | PMC14      | PMC13        | PMC12        | PMC11        | PMC10        | F0061H         | FFH         | R/W |  |

|            |             |             |             |            |              | -            |              |              |                |             |     |  |

| PMC4       | 1           | 1           | 1           | 1          | 1            | PMC42        | PMC41        | 1            | F0064H         | FFH         | R/W |  |

|            |             |             |             |            |              |              |              |              |                |             |     |  |

| 30-pin pro | oducts      |             |             |            |              |              |              |              |                |             |     |  |

| Symbol     | 7           | 6           | 5           | 4          | 3            | 2            | 1            | 0            | Address        | After reset | R/W |  |

| PMC0       | 1           | 1           | 1           | 1          | 1            | 1            | PMC01        | PMC00        | F0060H         | FFH         | R/W |  |

|            | ·           |             |             |            |              |              |              |              |                |             |     |  |

| PMC12      | 1           | 1           | 1           | 1          | 1            | 1            | 1            | PMC120       | F006CH         | FFH         | R/W |  |

|            | · · · · · · |             | 1           | •          | 1            | n            | 1            |              |                |             |     |  |

| PMC14      | PMC147      | 1           | 1           | 1          | 1            | 1            | 1            | 1            | F006EH         | FFH         | R/W |  |

|            |             |             |             |            |              |              |              |              |                |             |     |  |

|            | PMCmn       |             | Р           | mn pin dig | ital I/O/ana | alog input s | selection (r | m = 1, 4, 12 | 2, 14; n = 0 t | o 4, 7)     |     |  |

|            | 0           | Digital I/0 | O (alternat | e function | other than   | analog inp   | out)         |              |                |             |     |  |

|            | 1           | Analog ir   | nput        |            |              |              |              |              |                |             |     |  |

Cautions 1. Use the port mode register m (PMm) to select the input mode for the ports that are set to analog input by using the PMCxx register.

- 2. Do not use the analog input channel specification register (ADS) to set the pins that will be set to digital I/O by using the PMCxx register.

- 3. Be sure to set bits that are not mounted to their initial values.

# 5.6 Controlling Clock

## 5.6.1 Example of setting high-speed on-chip oscillator

After a reset release, the CPU/peripheral hardware clock (fcLK) always starts operating with the high-speed on-chip oscillator clock. The frequency of the high-speed on-chip oscillator can be selected from 24, 16, 12, 8, 6, 4, 3, 2, and 1 MHz by using FRQSEL0 to FRQSEL3 of the option byte (000C2H). The frequency can also be changed by the high-speed on-chip oscillator frequency select register (HOCODIV).

## [Option byte setting]

Address: 000C2H

| Option   | 7      | 6      | 5 | 4 | 3       | 2       | 1       | 0       |

|----------|--------|--------|---|---|---------|---------|---------|---------|

| byte     | CMODE1 | CMODE0 |   |   | FRQSEL3 | FRQSEL2 | FRQSEL1 | FRQSEL0 |

| (000C2H) | 0/1    | 0/1    | 1 | 0 | 0/1     | 0/1     | 0/1     | 0/1     |

|          |        |        |   |   |         |         |         |         |

| CMODE1     | CMODE0   | Setting                   | of flash operation mode                                                                                                                                        |

|------------|----------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | 0        | LS (low speed main) mode  | $V_{DD}$ = 1.8 V to 5.5 V @ 1 MHz to 8 MHz                                                                                                                     |

| 1          | 1        | HS (high speed main) mode | $V_{DD} = 2.4 \text{ V to } 5.5 \text{ V} @ 1 \text{ MHz to } 16 \text{ MHz}$<br>$V_{DD} = 2.7 \text{ V to } 5.5 \text{ V} @ 1 \text{ MHz to } 24 \text{ MHz}$ |

| Other that | an above | Setting prohibited        |                                                                                                                                                                |

| FRQSEL3 | FRQSEL2    | FRQSEL1  | FRQSEL0 | Frequency of the high-speed on-chip oscillator |

|---------|------------|----------|---------|------------------------------------------------|

| 0       | 0          | 0        | 0       | 24 MHz                                         |

| 1       | 0          | 0        | 1       | 16 MHz                                         |

| 0       | 0          | 0        | 1       | 12 MHz                                         |

| 1       | 0          | 1        | 0       | 8 MHz                                          |

| 0       | 0          | 1        | 0       | 6 MHz                                          |

| 1       | 0          | 1        | 1       | 4 MHz                                          |

| 0       | 0          | 1        | 1       | 3 MHz                                          |

| 1       | 1          | 0        | 0       | 2 MHz                                          |

| 1       | 1          | 0        | 1       | 1 MHz                                          |

|         | Other that | an above |         | Setting prohibited                             |

[High-speed on-chip oscillator frequency selection register (HOCODIV) setting]

|         | 7         | 6              | 5         | 4      | 3             | 2                | 1                  | 0         |  |  |

|---------|-----------|----------------|-----------|--------|---------------|------------------|--------------------|-----------|--|--|

| HOCODIV | 0         | 0              | 0         | 0      | 0             | HOCODIV 2        | HOCODIV 1          | HOCODIV 0 |  |  |

|         |           |                |           |        |               |                  |                    |           |  |  |

|         | HOCODIV 2 | HOCODIV 1      | HOCODIV 0 | High-s | peed on-chip  | oscillator clock | c frequency se     | lection   |  |  |

|         |           |                |           | FRQS   | SEL3 bit is 0 |                  | FRQSEL3 b          | it is 1   |  |  |

|         | 0         | 0              | 0         | 2      | 24 MHz        |                  | Setting prohibited |           |  |  |

|         | 0         | 0              | 1         | -      | 12 MHz        |                  | 16 MHz             | 2         |  |  |

|         | 0         | 1              | 0         |        | 6 MHz         |                  | 8 MHz              |           |  |  |

|         | 0         | 1              | 1         |        | 3 MHz         |                  | 4 MHz              |           |  |  |

|         | 1         | 0              | 0         | Settin | ng prohibited |                  | 2 MHz              |           |  |  |

|         | 1         | 0              | 1         | Settin | ng prohibited |                  | 1 MHz              |           |  |  |

|         | O         | ther than abov | ve        |        |               |                  |                    |           |  |  |

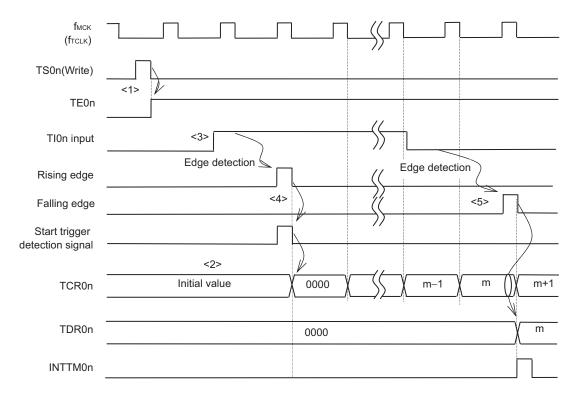

## (5) Capture & one-count mode operation (high-level width is measured)

- <1> Operation is enabled (TE0n = 1) by writing 1 to the TS0n bit of timer channel start register 0 (TS0).

- <2> Timer count register 0n (TCR0n) holds the initial value until start trigger generation.

- <3> Rising edge of the TIOn input is detected.

- <4> On start trigger detection, the value of 0000H is loaded to the TCR0n register and count starts.

- <5> On detection of the falling edge of the TI0n input, the value of the TCR0n register is captured to timer data register 0n (TDR0n) and INTTM0n is generated.

### Figure 6-26. Operation Timing (In Capture & One-count Mode: High-level Width Measurement)

**Remark** The timing is shown in **Figure 6-28** indicates while the noise filter is not used. By making the noise filter on-state, the edge detection becomes 2 fMCK cycles (it sums up to 3 to 4 cycles) later than the normal cycle of TI0n input. The error per one period occurs be the asynchronous between the period of the TI0n input and that of the count clock (fMCK).

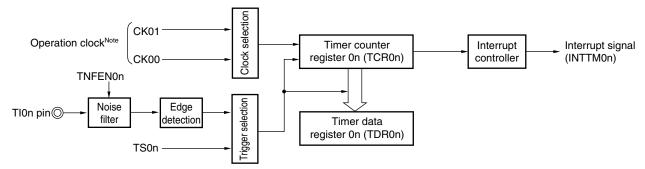

### 6.8.4 Operation as input pulse interval measurement

The count value can be captured at the TIOn valid edge and the interval of the pulse input to TIOn can be measured. In addition, the count value can be captured by using software operation (TSOn = 1) as a capture trigger while the TEOn bit is set to 1.

The pulse interval can be calculated by the following expression.

TIOn input pulse interval = Period of count clock × ((10000H × TSR0n: OVF) + (Capture value of TDR0n + 1))

**Caution** The TI0n pin input is sampled using the operating clock selected with the CKS0n bit of timer mode register 0n (TMR0n), so an error of up to one operating clock cycle occurs.

Timer count register 0n (TCR0n) operates as an up counter in the capture mode.

When the channel start trigger bit (TS0n) of timer channel start register 0 (TS0) is set to 1, the TCR0n register counts up from 0000H in synchronization with the count clock.

When the TI0n pin input valid edge is detected, the count value of the TCR0n register is transferred (captured) to timer data register 0n (TDR0n) and, at the same time, the TCR0n register is cleared to 0000H, and the INTTM0n is output. If the counter overflows at this time, the OVF bit of timer status register 0n (TSR0n) is set to 1. If the counter does not overflow, the OVF bit is cleared. After that, the above operation is repeated.

As soon as the count value has been captured to the TDR0n register, the OVF bit of the TSR0n register is updated depending on whether the counter overflows during the measurement period. Therefore, the overflow status of the captured value can be checked.

If the counter reaches a full count for two or more periods, it is judged to be an overflow occurrence, and the OVF bit of the TSR0n register is set to 1. However, a normal interval value cannot be measured for the OVF bit, if two or more overflows occur.

Set the STS0n2 to STS0n0 bits of the TMR0n register to 001B to use the valid edges of TI0n as a start trigger and a capture trigger.

Figure 6-50. Block Diagram of Operation as Input Pulse Interval Measurement

Note When channels 1 and 3, the clock can be selected from CK00, CK01, CK02, and CK03.

**Remark** n: Channel number (n = 0 to 7)

## 9.3 Register Controlling Watchdog Timer

The watchdog timer is controlled by the watchdog timer enable register (WDTE).

### 9.3.1 Watchdog timer enable register (WDTE)

Writing "ACH" to the WDTE register clears the watchdog timer counter and starts counting again. This register can be set by an 8-bit memory manipulation instruction. Reset signal generation sets this register to 9AH or 1AH<sup>Note</sup>.

### Figure 9-2. Format of Watchdog Timer Enable Register (WDTE)

| Address: | FFFABH | After reset: 9A | H/1AH <sup>Note</sup> | R/W |   |   |   |   |

|----------|--------|-----------------|-----------------------|-----|---|---|---|---|

| Symbol   | 7      | 6               | 5                     | 4   | 3 | 2 | 1 | 0 |

| WDTE     |        |                 |                       |     |   |   |   |   |

**Note** The WDTE register reset value differs depending on the WDTON bit setting value of the option byte (000C0H). To operate watchdog timer, set the WDTON bit to 1.

| WDTON Bit Setting Value                     | WDTE Register Reset Value |

|---------------------------------------------|---------------------------|

| 0 (watchdog timer count operation disabled) | 1AH                       |

| 1 (watchdog timer count operation enabled)  | 9AH                       |

- **Cautions 1.** If a value other than "ACH" is written to the WDTE register, an internal reset signal is generated.

- **2.** If a 1-bit memory manipulation instruction is executed for the WDTE register, an internal reset signal is generated.

- The value read from the WDTE register is 9AH/1AH (this differs from the written value (ACH)).

## **10.4 A/D Converter Conversion Operations**

The A/D converter conversion operations are described below.

- <1> The voltage input to the selected analog input channel is sampled by the sample & hold circuit.

- <2> When sampling has been done for a certain time, the sample & hold circuit is placed in the hold state and the sampled voltage is held until the A/D conversion operation has ended.

- <3> Bit 9 of the successive approximation register (SAR) is set. The series resistor string voltage tap is set to (1/2) AVREF by the tap selector.

- <4> The voltage difference between the series resistor string voltage tap and sampled voltage is compared by the voltage comparator. If the analog input is greater than (1/2) AVREF, the MSB bit of the SAR register remains set to 1. If the analog input is smaller than (1/2) AVREF, the MSB bit is reset to 0.

- <5> Next, bit 8 of the SAR register is automatically set to 1, and the operation proceeds to the next comparison. The series resistor string voltage tap is selected according to the preset value of bit 9, as described below.

- Bit 9 = 1: (3/4) AVREF

- Bit 9 = 0: (1/4) AVREF

- The voltage tap and sampled voltage are compared and bit 8 of the SAR register is manipulated as follows.

- Sampled voltage  $\geq$  Voltage tap: Bit 8 = 1

- Sampled voltage < Voltage tap: Bit 8 = 0

- <6> Comparison is continued in this way up to bit 0 of the SAR register.

- <7> Upon completion of the comparison of 10 bits, an effective digital result value remains in the SAR register, and the result value is transferred to the A/D conversion result register (ADCR, ADCRH) and then latched <sup>Note 1</sup>. At the same time, the A/D conversion end interrupt request (INTAD) can also be generated <sup>Note 1</sup>.

- <8> Repeat steps <1> to <7>, until the ADCS bit is cleared to 0 <sup>Note 2</sup>. To stop the A/D converter, clear the ADCS bit to 0.

- **Notes 1.** If the A/D conversion result is outside the A/D conversion result range specified by the ADRCK bit and the ADUL and ADLL registers (see **Figure 10-8**), the A/D conversion result interrupt request signal is not generated and no A/D conversion results are stored in the ADCR and ADCRH registers.

- 2. While in the sequential conversion mode, the ADCS flag is not automatically cleared to 0. This flag is not automatically cleared to 0 while in the one-shot conversion mode of the hardware trigger no-wait mode, either. Instead, 1 is retained.

- **Remarks 1.** Two types of the A/D conversion result registers are available.

- ADCR register (16 bits): Store 10-bit A/D conversion value

- ADCRH register (8 bits): Store 8-bit A/D conversion value

- AVREF: The + side reference voltage of the A/D converter. This can be selected from AVREFP, the internal reference voltage (1.45 V), and VDD.

### 10.6.2 Software trigger mode (select mode, one-shot conversion mode)

- <1> In the stop status, the ADCE bit of A/D converter mode register 0 (ADM0) is set to 1, and the system enters the A/D conversion standby status.

- <2> After the software counts up to the stabilization wait time (1 µs), the ADCS bit of the ADM0 register is set to 1 to perform the A/D conversion of the analog input specified by the analog input channel specification register (ADS).

- <3> When A/D conversion ends, the conversion result is stored in the A/D conversion result register (ADCR, ADCRH), and the A/D conversion end interrupt request signal (INTAD) is generated.

- <4> After A/D conversion ends, the ADCS bit is automatically cleared to 0, and the system enters the A/D conversion standby status.

- <5> When ADCS is overwritten with 1 during conversion operation, the current A/D conversion is interrupted, and conversion restarts. The partially converted data is discarded.

- <6> When the value of the ADS register is rewritten or overwritten during conversion operation, the current A/D conversion is interrupted, and A/D conversion is performed on the analog input respecified by the ADS register. The partially converted data is discarded.

- <7> When ADCS is cleared to 0 during conversion operation, the current A/D conversion is interrupted, and the system enters the A/D conversion standby status.

- <8> When ADCE is cleared to 0 while in the A/D conversion standby status, the A/D converter enters the stop status. When ADCE = 0, specifying 1 for ADCS is ignored and A/D conversion does not start. In addition, A/D conversion does not start even if a hardware trigger is input while in the A/D conversion standby status.

## Figure 10-18. Example of Software Trigger Mode (Select Mode, One-Shot Conversion Mode) Operation Timing

|                      |          | <                 | 1> AC | OCE is set to 1.                                              |      |                                                       |                  |                                                            |   |    |                       |                  |                                                                                 |                       | ADCE i           | s cleared to 0. <     | 8>                 |

|----------------------|----------|-------------------|-------|---------------------------------------------------------------|------|-------------------------------------------------------|------------------|------------------------------------------------------------|---|----|-----------------------|------------------|---------------------------------------------------------------------------------|-----------------------|------------------|-----------------------|--------------------|

| ADCE                 |          | trigger<br>is not | <2    | ADCS is set<br>> 1 while in the<br>conversion<br>standby stat | ə <4 | ADCS is<br>> automatically <<br>cleared to<br>0 after | 1                | ADCS is overwritt<br>with 1 during A/D<br>conversion opera |   | 1  | - <2                  | >                | <4                                                                              | 4> <2                 | > <7             |                       | The trigger is not |

| ADCS                 | acknowle | edged.            |       | Standby Stat                                                  | /    | conversion<br>ends.                                   |                  |                                                            | / | 1  |                       | <6:              | > ADS is rewritten during /<br>A/D conversion operation<br>(from ANI0 to ANI1). |                       |                  | conversion operation. | acknowledged       |

| ADS                  | _        |                   |       | Data 0<br>(ANI0)                                              |      |                                                       |                  |                                                            |   |    |                       |                  | Data 1<br>(ANI1)                                                                |                       |                  |                       |                    |

| A/D                  |          |                   |       |                                                               | <3:  | A/D<br>> conversion<br>, ends.                        |                  | Conversion is interrupted and restarts.                    | < | 3> |                       |                  | <                                                                               | >                     |                  | Conversion is         |                    |

| conversion<br>status |          | Stop<br>tatus     |       | Data 0<br>(ANI0)                                              |      | Conversion<br>standby                                 | Data 0<br>(ANI0) | Data 0<br>(ANI0)                                           |   |    | Conversion<br>standby | Data 0<br>(ANI0) | Data 1<br>(ANI1)                                                                | Conversion<br>standby | Data 1<br>(ANI1) | Conversion<br>standby | Stop<br>status     |

| ADCR,<br>ADCRH       | -        |                   |       |                                                               |      |                                                       | Data<br>(ANI     |                                                            |   |    |                       | Data<br>(ANI     |                                                                                 |                       | Data<br>(ANI1    |                       |                    |

| INTAD                | _        |                   |       |                                                               |      |                                                       |                  |                                                            |   |    |                       |                  |                                                                                 |                       |                  |                       |                    |

### 11.3.5 Serial data register mn (SDRmn)

The SDRmn register is the transmit/receive data register of channel n (16 bits). Bits 8 to 0 (lower 9 bits) of SDR00 and SDR01 or bits 7 to 0 (lower 8 bits) of SDR02, SDR03, SDR10, and SDR11 function as a transmit/receive buffer register, and bits 15 to 9 (higher 7 bits) are used as a register that sets the division ratio of the operation clock (fMck).

If the CCSmn bit of serial mode register mn (SMRmn) is cleared to 0, the operating clock divided by the division ratios specified by bits 15 to 9 (higher 7 bits) of the SDRmn register is used as the transfer clock.

If the CCSmn bit of SMRmn is set to 1, set bits 15 to 9 (higher 7 bits) of SDR00, SDR01, SDR10, and SDR11 to 0000000B. The input clock fsck (slave transfer in CSI mode) from the SCKp pin is used as the transfer clock.

The lower 8/9 bits of the SDRmn register function as a transmit/receive buffer register. During reception, the parallel data converted by the shift register is stored in the lower 8/9 bits, and during transmission, the data to be transmitted to the shift register is set to the lower 8/9 bits.

The SDRmn register can be read or written in 16-bit units.

However, the higher 7 bits can be written or read only when the operation is stopped (SEmn = 0). During operation (SEmn = 1), a value is written only to the lower 9 bits of the SDRmn register. When the SDRmn register is read during operation, the higher 7 bits are always read as 0.

Reset signal generation clears the SDRmn register to 0000H.

#### Figure 11-10. Format of Serial Data Register mn (SDRmn)

|                     |    |                               | F      | FF11H   | (SDR00  | ))     |   | FFF10H (SDR00) |          |         |          |          |         |            |           |      |

|---------------------|----|-------------------------------|--------|---------|---------|--------|---|----------------|----------|---------|----------|----------|---------|------------|-----------|------|

|                     |    |                               |        |         |         |        |   |                |          |         |          |          |         |            |           |      |

| Symbol              | 15 | 14                            | 13     | 12      | 11      | 10     | 9 | 8              | 7        | 6       | 5        | 4        | 3       | 2          | 1         | 0    |

| SDRmn               |    |                               |        |         |         |        |   |                |          |         |          |          |         |            |           |      |

| Address: FFF<br>FFF |    | FF45H<br>FF49H                | (SDR10 | ), FFF4 | 1AH, FF | F4BH ( |   |                | r reset: | 0000H   |          | -F44H    | (SDB02  | )          |           |      |

|                     | _  | FFF45H (SDR02) FFF44H (SDR02) |        |         |         |        |   |                |          |         |          |          |         |            |           |      |

| Symbol              | 15 |                               |        |         |         |        |   |                |          |         |          |          |         |            |           | 0    |

| SDRmn               |    |                               |        |         |         |        |   | 0              |          |         |          |          |         |            |           |      |

|                     |    |                               |        |         |         |        |   |                |          |         |          |          |         |            |           |      |

|                     |    |                               | SD     | Rmn[1   | 5:9]    |        |   | Tra            | nsfer cl | ock set | ing by c | dividing | the ope | erating of | clock (fr | иск) |

|                     | 0  | 0                             | 0      | 0       | 0       | 0      | 0 | fмск/2         |          |         |          |          |         |            |           |      |

|                     | 0  | 0                             | 0      | 0       | 0       | 0      | 1 |                |          |         |          | fмск/4   |         |            |           |      |

|                     | 0  | 0                             | 0      | 0       | 0       | 1      | 0 |                |          |         |          | fмск/6   |         |            |           |      |

|                     | 0  | 0                             | 0      | 0       | 0       | 1      | 1 |                |          |         |          | fмск/8   |         |            |           |      |

|                     | •  | •                             | •      | •       | •       | •      | • | • •            |          |         |          |          |         |            |           |      |

|                     | •  | •                             | •      | •       | •       | •      | • | •              |          |         |          |          |         |            |           |      |

|                     | •  | •                             | •      | •       | •       | •      | • |                |          |         |          |          |         |            |           |      |

|                     | 1  | 1                             | 1      | 1       | 1       | 1      | 0 |                |          |         |          | мск/254  |         |            |           |      |

|                     | 1  | 1                             | 1      | 1       | 1       | 1      | 1 |                |          |         | f        | мск/256  | 6       |            |           |      |

Address: FFF10H, FFF11H (SDR00), FFF12H, FFF13H (SDR01) After reset: 0000H R/W

(Cautions and Remarks are listed on the next page.)

## 11.5.2 Master reception

Master reception is that the RL78 microcontroller outputs a transfer clock and receives data from other device.

| 3-Wire Serial I/O             | CSI00                                                                                                                                                                                                                                                             | CSI01             | CSI11             | CSI20             |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|--|--|

| Target channel                | Channel 0 of SAU0                                                                                                                                                                                                                                                 | Channel 1 of SAU0 | Channel 3 of SAU0 | Channel 0 of SAU1 |  |  |

| Pins used                     | SCK00, SI00                                                                                                                                                                                                                                                       | SCK01, SI01       | SCK11, SI11       | SCK20, SI20       |  |  |

| Interrupt                     | INTCSI00                                                                                                                                                                                                                                                          | INTCSI01          | INTCSI11          | INTCSI20          |  |  |

|                               | Transfer end interrupt (in single-transfer mode) or buffer empty interrupt (in continuous transf<br>mode) can be selected.                                                                                                                                        |                   |                   |                   |  |  |

| Error detection flag          | Overrun error detection flag (OVFmn) only                                                                                                                                                                                                                         |                   |                   |                   |  |  |

| Transfer data length          | 7 or 8 bits                                                                                                                                                                                                                                                       |                   |                   |                   |  |  |

| Transfer rate <sup>Note</sup> | Max. fclk/2 [Hz] (CSI00 only), fclk/4 [Hz]                                                                                                                                                                                                                        |                   |                   |                   |  |  |

|                               | Min. fcLk/( $2 \times 2^{15} \times 128$ ) [Hz] fcLk: System clock frequency                                                                                                                                                                                      |                   |                   |                   |  |  |

| Data phase                    | <ul> <li>Selectable by the DAPmn bit of the SCRmn register</li> <li>DAPmn = 0: Data input starts at the start of the operation of the serial clock.</li> <li>DAPmn = 1: Data input starts half a clock before the start of the serial clock operation.</li> </ul> |                   |                   |                   |  |  |

| Clock phase                   | Selectable by the CKPmn bit of the SCRmn register<br>• CKPmn = 0: Non-inversion<br>• CKPmn = 1: Inverted                                                                                                                                                          |                   |                   |                   |  |  |

| Data direction                | MSB or LSB first                                                                                                                                                                                                                                                  |                   |                   |                   |  |  |

Note Use this operation within a range that satisfies the conditions above and the peripheral functions characteristics in the electrical specifications (see CHAPTER 28 ELECTRICAL SPECIFICATIONS (A, D: TA = -40 to +85°C) or CHAPTER 29 ELECTRICAL SPECIFICATIONS (G: TA = -40 to +105°C)).

**Remark** m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), mn = 00 to 03, 10 to 13

## (2) Operation procedure

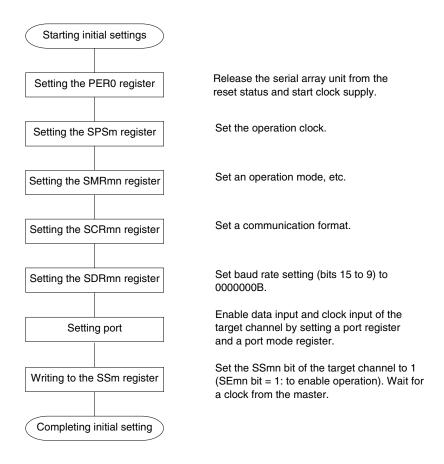

### Figure 11-58. Initial Setting Procedure for Slave Reception

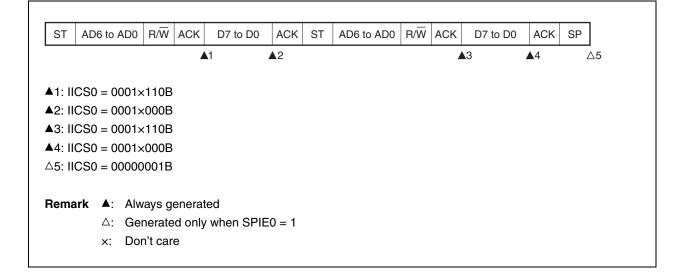

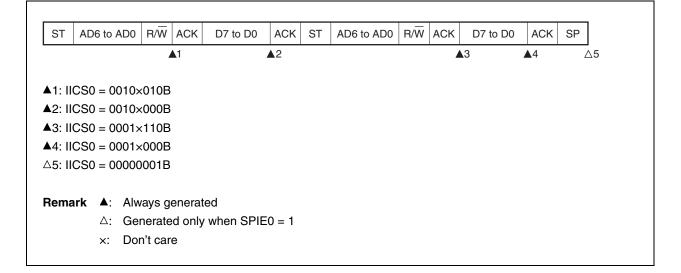

## (b) Start ~ Address ~ Data ~ Start ~ Address ~ Data ~ Stop

## (i) When WTIM0 = 0 (after restart, matches with SVA0)

(ii) When WTIM0 = 1 (after restart, matches with SVA0)

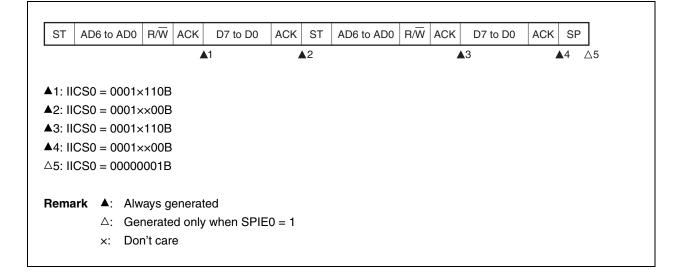

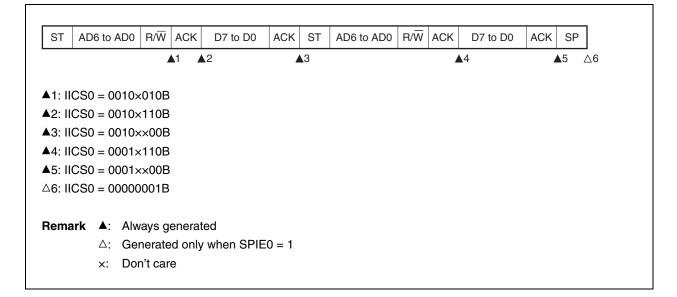

# (b) Start ~ Code ~ Data ~ Start ~ Address ~ Data ~ Stop

## (i) When WTIM0 = 0 (after restart, matches SVA0)

## (ii) When WTIM0 = 1 (after restart, matches SVA0)

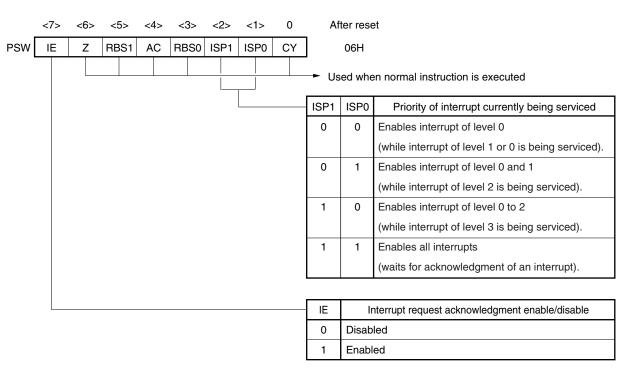

## 15.3.5 Program status word (PSW)

The program status word is a register used to hold the instruction execution result and the current status for an interrupt request. The IE flag that sets maskable interrupt enable/disable and the ISP0 and ISP1 flags that controls multiple interrupt servicing are mapped to the PSW.

Besides 8-bit read/write, this register can carry out operations using bit manipulation instructions and dedicated instructions (EI and DI). When a vectored interrupt request is acknowledged, if the BRK instruction is executed, the contents of the PSW are automatically saved into a stack and the IE flag is reset to 0. Upon acknowledgment of a maskable interrupt request, if the value of the priority specification flag register of the acknowledged interrupt is not 00, its value minus 1 is transferred to the ISP0 and ISP1 flags. The PSW contents are also saved into the stack with the PUSH PSW instruction. They are restored from the stack with the RETI, RETB, and POP PSW instructions.

Reset signal generation sets PSW to 06H.

### Figure 15-9. Configuration of Program Status Word

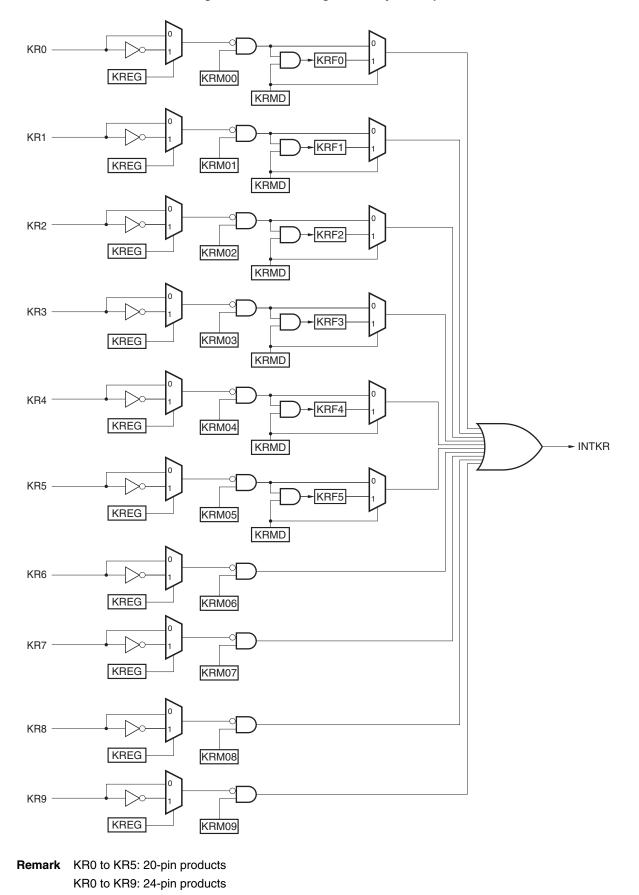

## Figure 16-1. Block Diagram of Key Interrupt

# 28.9 Dedicated Flash Memory Programmer Communication (UART)

| $(114 = -40 \ 10 \ +65 \ C, \ 1.6 \ V \le VDD \le 5.5 \ V, \ VSS = 0 \ V)$ |        |                           |         |      |           |      |  |  |

|----------------------------------------------------------------------------|--------|---------------------------|---------|------|-----------|------|--|--|

| Parameter                                                                  | Symbol | Conditions                | MIN.    | TYP. | MAX.      | Unit |  |  |

| Transfer rate                                                              |        | During serial programming | 115,200 |      | 1,000,000 | bps  |  |  |

# $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{ V}_{SS} = 0 \text{ V})$

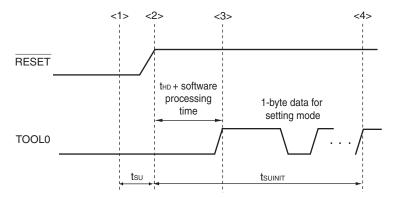

## 28.10 Timing of Entry to Flash Memory Programming Modes

## $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{ V}_{SS} = 0 \text{ V})$

| Parameter                                                                                                                                                             | Symbol  | Conditions                                                         | MIN. | TYP. | MAX. | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------|------|------|------|------|

| Time to complete the communication for the initial setting after the external reset is released                                                                       | tsuinit | POR and LVD reset are<br>released before external<br>reset release |      |      | 100  | ms   |

| Time to release the external reset after the TOOL0 pin is set to the low level                                                                                        | ts∪     | POR and LVD reset are<br>released before external<br>reset release | 10   |      |      | μS   |

| Time to hold the TOOL0 pin at the low level after<br>the external reset is released<br>(excluding the processing time of the firmware to<br>control the flash memory) | tнd     | POR and LVD reset are<br>released before external<br>reset release | 1    |      |      | ms   |

- <1> The low level is input to the TOOL0 pin.

- <2> The external reset is released (POR and LVD reset must be released before the external reset is released.).

- <3> The TOOL0 pin is set to the high level.

- <4> Setting of the flash memory programming mode by UART reception and complete the baud rate setting.

- **Remark** tsuinit: Communication for the initial setting must be completed within 100 ms after the external reset is released during this period.

- $t_{\text{SU}}$ : Time to release the external reset after the TOOL0 pin is set to the low level

- the: Time to hold the TOOL0 pin at the low level after the external reset is released (excluding the processing time of the firmware to control the flash memory)

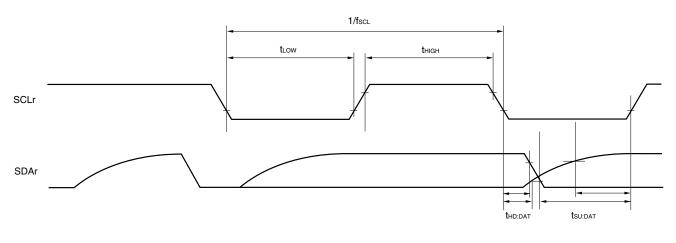

|                               | <u>= = 0.0, .</u> | •••••                                                                      |                                |            |      |  |

|-------------------------------|-------------------|----------------------------------------------------------------------------|--------------------------------|------------|------|--|

| Parameter                     | Symbol            | Conditions                                                                 | HS (high-speed main) Mode      |            | Unit |  |

|                               |                   |                                                                            | MIN.                           | MAX.       |      |  |

| SCLr clock frequency          | fsc∟              | $C_{\text{b}} = 100 \text{ pF},  \text{R}_{\text{b}} = 3  \text{k} \Omega$ |                                | 100 Note 1 | kHz  |  |

| Hold time when SCLr = "L"     | t∟ow              | $C_b$ = 100 pF, $R_b$ = 3 k $\Omega$                                       | 4600                           |            | ns   |  |

| Hold time when SCLr = "H"     | tнıgн             | $C_b$ = 100 pF, $R_b$ = 3 k $\Omega$                                       | 4600                           |            | ns   |  |

| Data setup time (reception)   | tsu:dat           | $C_{\text{b}} = 100 \text{ pF},  \text{R}_{\text{b}} = 3  \text{k} \Omega$ | 1/fмск + 580 <sup>Note 2</sup> |            | ns   |  |

| Data hold time (transmission) | thd:dat           | $C_b$ = 100 pF, $R_b$ = 3 k $\Omega$                                       | 0                              | 1420       | ns   |  |

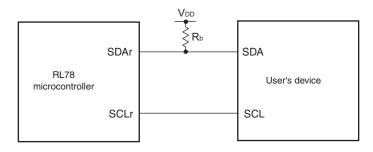

# (4) During communication at same potential (simplified I<sup>2</sup>C mode)

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{ V}_{SS} = 0 \text{ V})$

Notes 1. The value must also be equal to or less than fmck/4.

- Set tsu:DAT so that it will not exceed the hold time when SCLr = "L" or SCLr = "H". 2.

- Caution Select the N-ch open drain output (VDD tolerance) mode for SDAr by using port output mode register h (POMh).

Simplified I<sup>2</sup>C mode connection diagram (during communication at same potential)

Simplified I<sup>2</sup>C mode serial transfer timing (during communication at same potential)

- **Remarks 1.**  $R_b$  [ $\Omega$ ]:Communication line (SDAr) pull-up resistance Cb [F]: Communication line (SCLr, SDAr) load capacitance

- 2. r: IIC number (r = 00, 01, 11, 20), h: = POM number (h = 0, 1, 4, 5)

- 3. fMCK: Serial array unit operation clock frequency (Operation clock to be set by the serial clock select register m (SPSm) and the CKSmn bit of serial mode register mn (SMRmn).

m: Unit number (m = 0, 1), n: Channel number (0, 1, 3)

RENESAS