Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, UART/USART                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 18                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 2K x 8                                                                          |

| RAM Size                   | 1.5K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                     |

| Data Converters            | A/D 11x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 24-WFQFN Exposed Pad                                                            |

| Supplier Device Package    | 24-HWQFN (4x4)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f1027adna-u0 |

RL78/G12 CHAPTER 1 OUTLINE

Table 1-1. List of Ordering Part Numbers

Pin Package Data flash Part Number count Application R5F1026AASP#V5, R5F10269ASP#V5, R5F10268ASP#V5, R5F10267ASP#V5, 20 20-pin plastic Mounted < R> pins LSSOP R5F10266ASP#V5 R5F1026AASP#X5, R5F10269ASP#X5, R5F10268ASP#X5, R5F10267ASP#X5,  $(4.4 \times 6.5 \text{ mm},$ 0.65 mm pitch) R5F10266ASP#X5 D R5F1026ADSP#V5, R5F10269DSP#V5, R5F10268DSP#V5, R5F10267DSP#V5, R5F10266DSP#V5 R5F1026ADSP#X5, R5F10269DSP#X5, R5F10268DSP#X5, R5F10267DSP#X5, R5F10266DSP#X5 G R5F1026AGSP#V5, R5F10269GSP#V5, R5F10268GSP#V5, R5F10267GSP#V5, R5F10266GSP#V5 R5F1026AGSP#X5, R5F10269GSP#X5, R5F10268GSP#X5, R5F10267GSP#X5, B5F10266GSP#X5 R5F1036AASP#V5, R5F10369ASP#V5, R5F10368ASP#V5, R5F10367ASP#V5, Not mounted R5F10366ASP#V5 R5F1036AASP#X5, R5F10369ASP#X5, R5F10368ASP#X5, R5F10367ASP#X5, R5F10366ASP#X5 D R5F1036ADSP#V5, R5F10369DSP#V5, R5F10368DSP#V5, R5F10367DSP#V5, R5F10366DSP#V5 R5F1036ADSP#X5, R5F10369DSP#X5, R5F10368DSP#X5, R5F10367DSP#X5, R5F10366DSP#X5 24 24-pin plastic Mounted R5F1027AANA#U5, R5F10279ANA#U5, R5F10278ANA#U5, R5F10277ANA#U5 Α <R> **HWQFN** pins R5F1027AANA#W5, R5F10279ANA#W5, R5F10278ANA#W5,  $(4 \times 4 \text{ mm}, 0.5)$ R5F10277ANA#W5 mm pitch) D R5F1027ADNA#U5, R5F10279DNA#U5, R5F10278DNA#U5, R5F10277DNA#U5 R5F1027ADNA#W5, R5F10279DNA#W5, R5F10278DNA#W5, R5F10277DNA#W5 G R5F1027AGNA#U5, R5F10279GNA#U5, R5F10278GNA#U5, R5F10277GNA#U5 R5F1027AGNA#W5, R5F10279GNA#W5, R5F10278GNA#W5, R5F10277GNA#W5 Not mounted Α R5F1037AANA#V5, R5F10379ANA#V5, R5F10378ANA#V5, R5F10377ANA#V5 R5F1037AANA#X5, R5F10379ANA#X5, R5F10378ANA#X5, R5F10377ANA#X5 D R5F1037ADNA#V5, R5F10379DNA#V5, R5F10378DNA#V5, R5F10377DNA#V5 R5F1037ADNA#X5, R5F10379DNA#X5, R5F10378DNA#X5, R5F10377DNA#X5 R5F102AAASP#V0, R5F102A9ASP#V0, R5F102A8ASP#V0, R5F102A7ASP#V0 30 30-pin plastic Mounted Α LSSOP R5F102AAASP#X0, R5F102A9ASP#X0, R5F102A8ASP#X0, R5F102A7ASP#X0 pins (7.62 mm D R5F102AADSP#V0, R5F102A9DSP#V0, R5F102A8DSP#V0, R5F102A7DSP#V0 (300), 0.65 mm R5F102AADSP#X0, R5F102A9DSP#X0, R5F102A8DSP#X0, R5F102A7DSP#X0 pitch ) G R5F102AAGSP#V0. R5F102A9GSP#V0. R5F102A8GSP#V0. R5F102A7GSP#V0 R5F102AAGSP#X0, R5F102A9GSP#X0, R5F102A8GSP#X0, R5F102A7GSP#X0 R5F103AAASP#V0, R5F103A9ASP#V0, R5F103A8ASP#V0, R5F103A7ASP#V0 Not mounted Α R5F103AAASP#X0, R5F103A9ASP#X0, R5F103A8ASP#X0, R5F103A7ASP#X0 R5F103AADSP#V0. R5F103A9DSP#V0. R5F103A8DSP#V0. R5F103A7DSP#V0 D R5F103AADSP#X0, R5F103A9DSP#X0, R5F103A8DSP#X0, R5F103A7DSP#X0

Note For fields of application, see Figure 1-1 Part Number, Memory Size, and Package of RL78/G12.

**Caution** The ordering part numbers represent the numbers at the time of publication. For the latest ordering part numbers, refer to the target product page of the Renesas Electronics website.

<R>

PU register (PUmn)

RDPORT

Alternate function

RESET

PORTSELB

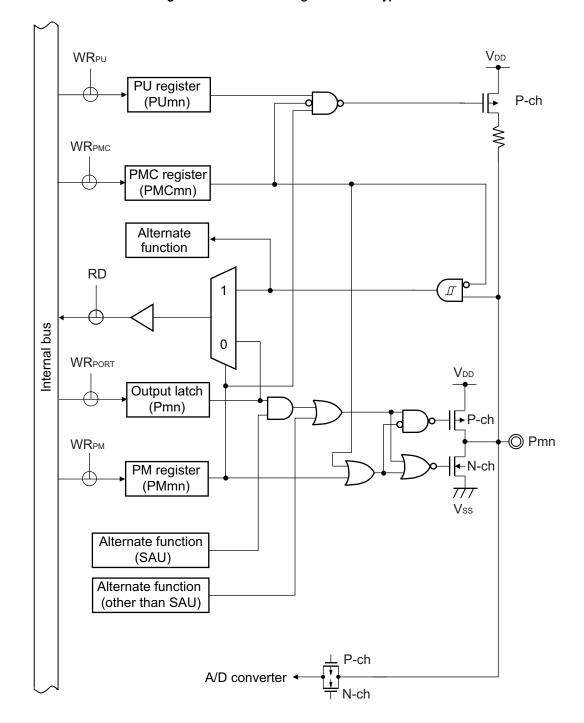

Figure 2-4. Pin Block Diagram for Pin Type 3-1-1

Figure 2-8. Pin Block Diagram for Pin Type 7-3-1

Remarks 1. For alternate functions, see 2.1 Port Functions.

2. SAU: Serial array unit

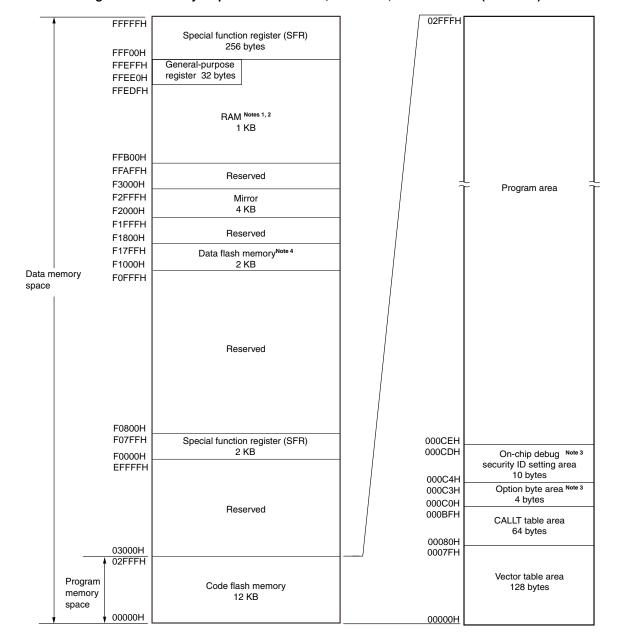

Figure 3-4. Memory Map for the R5F10x69, R5F10x79, and R5F10xA9 (x = 2 or 3)

- <R> Notes 1. Do not allocate the stack area, data buffers for use by the flash library, arguments of library functions, branch destinations in the processing of vectored interrupts, or destinations or sources for DMA transfer to the area from FFE20H to FFEDFH when performing self-programming or rewriting of the data flash memory. For R5F10x69 and R5F10x79, the RAM area used by the flash library starts at FFB00H. For the RAM areas used by the flash library, see Self RAM list of Flash Self-Programming Library for RL78 Family (R20UT2944).

- 2. Instructions can be executed from the RAM area excluding the general-purpose register area.

- 3. Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

- 4. The areas are reserved in the R5F10369, R5F10379, and R5F103A9.

Caution While RAM parity error resets are enabled (RPERDIS = 0), be sure to initialize RAM areas where data access is to proceed and the RAM area +10 bytes when instructions are fetched from RAM areas, respectively. Reset signal generation sets RAM parity error resets to enabled (RPERDIS = 0). For details, see 21.3.2 RAM parity error detection.

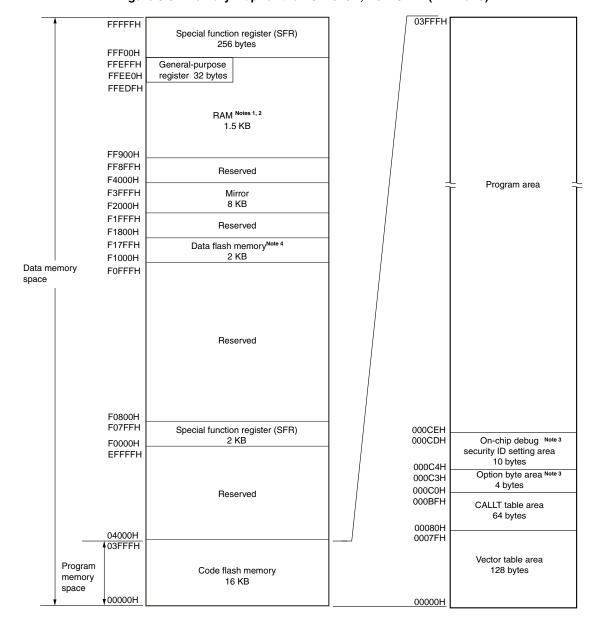

Figure 3-5. Memory Map for the R5F10x6A, R5F10x7A (x = 2 or 3)

- Notes 1. Do not allocate the stack area, data buffers for use by the flash library, arguments of library functions, branch destinations in the processing of vectored interrupts, or destinations or sources for DMA transfer to the area from FFE20H to FFEDFH when performing self-programming or rewriting of the data flash memory. For R5F10x6A and R5F10x7A, the RAM area used by the flash library starts at FF900H. For the RAM areas used by the flash library, see Self RAM list of Flash Self-Programming Library for RL78 Family (R20UT2944).

- 2. Instructions can be executed from the RAM area excluding the general-purpose register area.

- 3. Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

- 4. The areas are reserved in the R5F1036A and R5F1037A.

**Caution** While RAM parity error resets are enabled (RPERDIS = 0), be sure to initialize RAM areas where data access is to proceed and the RAM area +10 bytes when instructions are fetched from RAM areas, respectively. Reset signal generation sets RAM parity error resets to enabled (RPERDIS = 0). For details, see 21.3.2 RAM parity error detection function.

## 4.6 Cautions When Using Port Function

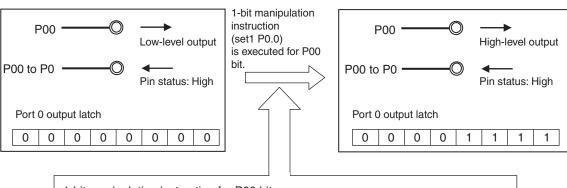

#### 4.6.1 Cautions on 1-Bit Manipulation Instruction for Port Register n (Pn)

When a 1-bit manipulation instruction is executed on a port that provides both input and output functions, the output latch value of an input port that is not subject to manipulation may be written in addition to the targeted bit.

Therefore, it is recommended to rewrite the output latch when switching a port from input mode to output mode.

Example When P00 is an output port, P01 to P03 are input ports (all pin statuses are high level), and the output

latch value of port 0 is 00H, if the output of output port P00 is changed from low level to high level via a

1-bit manipulation instruction, the output latch value of port 0 is 0FH.

Explanation: The targets of writing to and reading from the Pn register of a port whose PMmn bit is 1 are the output

latch and pin status, respectively.

A 1-bit manipulation instruction is executed in the following order in the RL78/G12.

- <1> The Pn register is read in 8-bit units.

- <2> The targeted one bit is manipulated.

- <3> The Pn register is written in 8-bit units.

In step <1>, the output latch value (0) of P00, which is an output port, is read, while the pin statuses of P01 to P03, which are input ports, are read. If the pin statuses of P01 to P03 are high level at this time, the read value is 0EH.

The value is changed to 0FH by the manipulation in <2>.

0FH is written to the output latch by the manipulation in <3>.

Figure 4-10. Bit Manipulation Instruction (P00)

1-bit manipulation instruction for P00 bit

- <1> Port register 0 (P0) is read in 8-bit units.

- For P00, an output port, the value of the port output latch (0) is read.

- For P01 to P03, input ports, the pin status (1) is read.

- <2> Set the P00 bit to 1.

- <3> Write the results of <2> to the output latch of port register 0 (P0) in 8-bit units.

#### 5.3.1 Clock operation mode control register (CMC)

This register is used to set the operation mode of the X1/P121 and X2/EXCLK/P122 pins, and to select a gain of the oscillator.

The CMC register can be written only once by an 8-bit memory manipulation instruction after reset release. This register can be read by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

Figure 5-2. Format of Clock Operation Mode Control Register (CMC)

| Address: FF | FA0H Afte | r reset: 00H | R/W |   |   |   |   |      |

|-------------|-----------|--------------|-----|---|---|---|---|------|

| Symbol      | 7         | 6            | 5   | 4 | 3 | 2 | 1 | 0    |

| CMC         | EXCLK     | OSCSEL       | 0   | 0 | 0 | 0 | 0 | AMPH |

| EXCLK | OSCSEL | High-speed system clock pin operation mode | X1/P121/KR3 pin                      | X2/EXCLK/P122/KR2<br>pin |  |  |

|-------|--------|--------------------------------------------|--------------------------------------|--------------------------|--|--|

| 0     | 0      | Input port mode                            | Input port                           |                          |  |  |

| 0     | 1      | X1 oscillation mode                        | Crystal/ceramic resonator connection |                          |  |  |

| 1     | 0      | Input port mode                            | Input port                           |                          |  |  |

| 1     | 1      | External clock input mode                  | Input port External clock inp        |                          |  |  |

| AMPH | Control of X1 clock oscillation frequency |

|------|-------------------------------------------|

| 0    | 1 MHz $\leq$ fx $\leq$ 10 MHz             |

| 1    | 10 MHz < fx ≤ 20 MHz                      |

# Cautions 1. The CMC register can be written only once after reset release, by an 8-bit memory manipulation instruction. When using the CMC register with its initial value (00H), be

- manipulation instruction. When using the CMC register with its initial value (00H), be sure to set the register to 00H after a reset ends in order to prevent malfunction due to a program loop. Such a malfunction becomes unrecoverable when a value other than 00H is mistakenly written.

- 2. After reset release, set the CMC register before X1 oscillation is started as set by the clock operation status control register (CSC).

- 3. Be sure to set the AMPH bit to 1 if the X1 clock oscillation frequency exceeds 10 MHz.

- **4.** Specify the setting for the AMPH bit while  $f_{IH}$  is selected as  $f_{CLK}$  after a reset ends (before  $f_{CLK}$  is switched to  $f_{MX}$ ).

- **5.** Although the maximum system clock frequency is 24 MHz, the maximum frequency of the X1 oscillator is 20 MHz.

Remark fx: X1 clock frequency

#### 10.3.1 Peripheral enable register 0 (PER0)

This register is used to enable or disable supplying the clock to the peripheral hardware. Clock supply to a hardware macro that is not used is stopped in order to reduce the power consumption and noise.

When the A/D converter is used, be sure to set bit 5 (ADCEN) of this register to 1.

The PER0 register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

Figure 10-2. Format of Peripheral Enable Register 0 (PER0)

Address: F00F0H After reset: 00H R/W <7> Symbol <5> <4> <3> <2> <0> 1 PER0 **TMKAEN** 0 **ADCEN** IICA0EN SAU1EN<sup>Note</sup> SAU0EN 0 TAU0EN

| ADCEN | Control of clock supply to the A/D converter                                                                         |

|-------|----------------------------------------------------------------------------------------------------------------------|

| 0     | Stops clock supply.  • SFR used by the A/D converter cannot be written.  • The A/D converter is in the reset status. |

| 1     | Enables clock supply.  • SFR used by the A/D converter can be read/written.                                          |

Note 30-pin products only.

- Cautions 1. When setting the A/D converter, be sure to set the following registers first while the ADCEN bit is set to 1. If ADCEN = 0, the values of the A/D converter control registers are cleared to their initial values, and writing to them is ignored (except for port mode registers 0, 1, 2, 4, 12, and 14 (PM0, PM1, PM2, PM4, PM12, and PM14), port mode control registers 0, 1, 4, 12, and 14 (PMC0, PMC1, PMC4, PMC12, and PMC14), and A/D port configuration register (ADPC)).

- · A/D converter mode register 0 (ADM0)

- A/D converter mode register 1 (ADM1)

- · A/D converter mode register 2 (ADM2)

- 10-bit A/D conversion result register (ADCR)

- · 8-bit A/D conversion result register (ADCRH)

- Analog input channel specification register (ADS)

- · Conversion result comparison upper limit setting register (ADUL)

- · Conversion result comparison lower limit setting register (ADLL)

- · A/D test register (ADTES).

- 2. Be sure to clear the following bits to 0.

20- or 24-pin products: Bits 1, 3, and 6 30-pin products: Bits 1 and 6

#### 11.3.2 Serial clock select register m (SPSm)

The SPSm register is a 16-bit register that is used to select two types of operation clocks (CKm0, CKm1) that are commonly supplied to each channel. CKm1 is selected by bits 7 to 4 of the SPSm register, and CKm0 is selected by bits 3 to 0.

Rewriting the SPSm register is prohibited when the register is in operation (when SEmn = 1).

The SPSm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the SPSm register can be set with an 8-bit memory manipulation instruction with SPSmL.

Reset signal generation clears the SPSm register to 0000H.

Figure 11-7. Format of Serial Clock Select Register m (SPSm)

Address: F0126H, F0127H (SPS0), F0166H, F0167H (SPS1) After reset: 0000H R/W 7 6 5 0 Symbol 12 4 3 2 15 14 13 11 0 PRS **PRS PRS PRS** PRS **PRS PRS** PRS SPSm 0 0 0 0 0 0 m03 m01 m00 m13 m12 m11 m10 m02

| PRS | PRS | PRS | PRS |                      |          | Section of o | peration cloc | k (CKmk) <sup>Note</sup> |          |          |

|-----|-----|-----|-----|----------------------|----------|--------------|---------------|--------------------------|----------|----------|

| mk3 | mk2 | mk1 | mk0 |                      | fclk=    | fclk=        | fclk=         | fclk=                    | fclk=    | fcьк =   |

|     |     |     |     |                      | 2 MHz    | 4 MHz        | 8 MHz         | 16 MHz                   | 20 MHz   | 24 MHz   |

| 0   | 0   | 0   | 0   | fclk                 | 2 MHz    | 4 MHz        | 8 MHz         | 16 MHz                   | 20 MHz   | 24 MHz   |

| 0   | 0   | 0   | 1   | fclk/2               | 1 MHz    | 2 MHz        | 4 MHz         | 8 MHz                    | 10 MHz   | 12 MHz   |

| 0   | 0   | 1   | 0   | fclk/2 <sup>2</sup>  | 500 kHz  | 1 MHz        | 2 MHz         | 4 MHz                    | 5 MHz    | 6 MHz    |

| 0   | 0   | 1   | 1   | fclk/23              | 250 kHz  | 500 kHz      | 1 MHz         | 2 MHz                    | 2.5 MHz  | 3 MHz    |

| 0   | 1   | 0   | 0   | fclk/2 <sup>4</sup>  | 125 kHz  | 250 kHz      | 500 kHz       | 1 MHz                    | 1.25 MHz | 1.5 MHz  |

| 0   | 1   | 0   | 1   | fc∟к/2⁵              | 62.5 kHz | 125 kHz      | 250 kHz       | 500 kHz                  | 625 kHz  | 750 kHz  |

| 0   | 1   | 1   | 0   | fclk/2 <sup>6</sup>  | 31.3 kHz | 62.5 kHz     | 125 kHz       | 250 kHz                  | 313 kHz  | 375 kHz  |

| 0   | 1   | 1   | 1   | fclk/27              | 15.6 kHz | 31.3 kHz     | 62.5 kHz      | 125 kHz                  | 156 kHz  | 188 kHz  |

| 1   | 0   | 0   | 0   | fclk/28              | 7.81 kHz | 15.6 kHz     | 31.3 kHz      | 62.5 kHz                 | 78.1 kHz | 93.8 kHz |

| 1   | 0   | 0   | 1   | fclk/29              | 3.91 kHz | 7.81 kHz     | 15.6 kHz      | 31.3 kHz                 | 39.1 kHz | 46.9 kHz |

| 1   | 0   | 1   | 0   | fclk/2 <sup>10</sup> | 1.95 kHz | 3.91 kHz     | 7.81 kHz      | 15.6 kHz                 | 19.5 kHz | 23.4 kHz |

| 1   | 0   | 1   | 1   | fcьк/2 <sup>11</sup> | 977 Hz   | 1.95 kHz     | 3.91 kHz      | 7.81 kHz                 | 9.77 kHz | 11.7 kHz |

| 1   | 1   | 0   | 0   | fcLK/2 <sup>12</sup> | 488 Hz   | 977 Hz       | 1.95 kHz      | 3.91 kHz                 | 4.88 kHz | 5.86 kHz |

| 1   | 1   | 0   | 1   | fclk/2 <sup>13</sup> | 244 Hz   | 488 Hz       | 977 Hz        | 1.95 kHz                 | 2.44 kHz | 2.93 kHz |

| 1   | 1   | 1   | 0   | fclk/2 <sup>14</sup> | 122 Hz   | 244 Hz       | 488 Hz        | 977 Hz                   | 1.22 kHz | 1.46 kHz |

| 1   | 1   | 1   | 1   | fclk/2 <sup>15</sup> | 61 Hz    | 122 Hz       | 244 Hz        | 488 Hz                   | 610 Hz   | 732 Hz   |

**Note** When changing the clock selected for fclk while the serial array unit (SAU) is operating (by changing the system clock control register (CKC) value), do so after having stopped (serial channel stop register m (STm) = 000FH) the operation of SAU.

Caution Be sure to clear bits 15 to 8 to "0".

Remarks 1. fclk: CPU/peripheral hardware clock frequency

**2.** m: Unit number (m = 0, 1) k = 0, 1

#### 11.3.9 Serial channel stop register m (STm)

The STm register is a trigger register that is used to enable stopping communication/count for each channel.

When 1 is written to a bit of this register (STmn), the corresponding bit (SEmn) of serial channel enable status register m (SEm) is cleared to 0 (operation is stopped). Because the STmn bit is a trigger bit, it is cleared immediately when SEmn = 0.

The STm register is set by a 16-bit memory manipulation instruction.

The lower 8 bits of the STm register can be set with a 1-bit or 8-bit memory manipulation instruction as STmL.

Reset signal generation clears the STm register to 0000H.

Figure 11-14. Format of Serial Channel Stop Register m (STm)

| Address: F01          | 24H, F0 | )125H ( | ST0)     | After re | eset: 00 | 00H | R/W |   |   |   |   |   |                |                |      |      |

|-----------------------|---------|---------|----------|----------|----------|-----|-----|---|---|---|---|---|----------------|----------------|------|------|

| Symbol                | 15      | 14      | 13       | 12       | 11       | 10  | 9   | 8 | 7 | 6 | 5 | 4 | 3              | 2              | 1    | 0    |

| ST0                   | 0       | 0       | 0        | 0        | 0        | 0   | 0   | 0 | 0 | 0 | 0 | 0 | ST03<br>Note 1 | ST02<br>Note 1 | ST01 | ST00 |

| Address: F01          | )165H ( | ST1)    | After re | eset: 00 | 00H      | R/W |     |   |   |   |   |   |                |                |      |      |

| Symbol                | 15      | 14      | 13       | 12       | 11       | 10  | 9   | 8 | 7 | 6 | 5 | 4 | 3              | 2              | 1    | 0    |

| ST1 <sup>Note 1</sup> | 0       | 0       | 0        | 0        | 0        | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0              | 0              | ST11 | ST10 |

|                       |         |         |          |          |          |     |     |   |   |   |   |   |                |                |      |      |

|   | STmn | Operation stop trigger of channel n                                             |

|---|------|---------------------------------------------------------------------------------|

|   | 0    | No trigger operation                                                            |

| ĺ | 1    | Clears the SEmn bit to 0 and stops the communication operation <sup>Note2</sup> |

Notes 1. 30-pin product only.

**2.** While holding the value of the control register and shift register, and the status of the, SCKmn, SOmn pins, FEFmn, PEFmn, OVFmn flag.

**Caution** Be sure to clear bits 15 to 2 of the ST0 register for 20- or 24-pin products, bits 15 to 4 of the ST0 register for 30-pin products, and bits 15 to 2 of the ST1 register to "0".

**Remarks 1.** m: Unit number (m = 0, 1) n: Channel number (n = 0 to 3)

2. When the STm register is read, 0000H is always read.

## 11.4 Operation Stop Mode

Each serial interface of serial array unit has the operation stop mode.

In this mode, serial communication cannot be executed, thus reducing the power consumption.

In addition, the pin for serial interface can be used as port function pins in this mode.

### 11.4.1 Stopping the operation by units

The stopping of the operation by units is set by using peripheral enable register 0 (PER0).

The PER0 register is used to enable or disable supplying the clock to the peripheral hardware. Clock supply to a hardware macro that is not used is stopped in order to reduce the power consumption and noise.

To stop the operation of serial array unit 0, set bit 2 (SAU0EN) to 0. To stop the operation of serial array unit 1, set bit 3 (SAU1EN) to 0.

Figure 11-23. Peripheral Enable Register 0 (PER0) Setting When Stopping Operation by Units

(a) Peripheral enable register 0 (PER0) ... Set only the bit of SAUm to be stopped to 0. 7 6 5 4 3 2 1 0 PER0 TMKAEN ADCEN IICA0EN SAU1EN<sup>Note</sup> SAU0EN TAU0EN 0 0/1 0/1 0

Control of SAUm input clock

0: Stops supply of input clock

1: Supplies input clock

Note Provided only in 30-pin products.

**Cautions 1.** If SAUmEN = 0, writing to a control register of serial array unit m is ignored, and, even if the register is read, only the default value is read

Note that this does not apply to the following registers.

- Noise filter enable register 0 (NFEN0)

- Port input mode register 0, 1 (PIM0, PIM1)

- Port output mode registers 0, 1, 4, 5 (POM0, POM1, POM4, POM5)

- Port mode registers 0, 1, 3 to 6 (PM0, PM1, PM3 to PM6)

- Port registers 0, 1, 3 to 6 (P0, P1, P3 to P6)

- Port mode control registers 0, 1, 4 (PMC0, PMC1, PMC4)

- 2. Be sure to clear the following bits to 0.

20, 24-pin products: bits 1, 3, 6

30-pin products: bits 1, 6

**Remark** : Setting disabled (fixed by hardware)

x: Bits not used with serial array units (depending on the settings of other peripheral functions)

0/1: Set to 0 or 1 depending on the usage of the user.

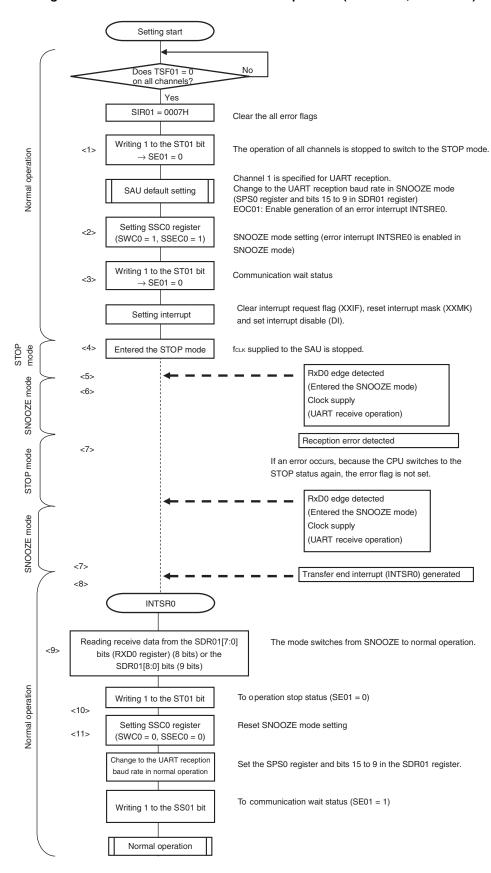

Setting start <R> No Does TSF01 = 0 on all channels? Yes The operation of all channels is also stopped to switch to the Does TSF01 = 0 on all STOP mode. channels? Normal operation Channel 1 is specified for UART reception SAU default setting (change to the UART reception baud rate in SNOOZE mode (SPS0 register and bits 15 to 9 in SDR01 register)). Setting SSC0 register SNOOZE mode setting (SWC0 = 1)Writing 1 to the SS01 bit Communication wait status → SE01 = 1 Clear interrupt request flag (XXIF), reset interrupt mask (XXMK) Enable interrupt and set interrupt enable (EI = 1). SNOOZE mode STOP mode fclk supplied to the SAU is stopped. Entered the STOP mode The valid edge of the RxD0 pin <5> detected (Entered the SNOOZE mode) Input of the start bit on the RxD0 pin <6> detected (UART receive operation) Transfer end interrupt (INTSR0) or error <8> interrupt (INTSRE0) generated? INTSRE0 INTSR0 Reading receive data from the <9> Reading receive data from the The mode switches from SNOOZE to SDR00[7:0] bits (RXD0 register) SDR00[7:0] bits (RXD0 register) normal operation. (8 bits) or the SDR00[8:0] (9 bits) (8 bits) or the SDR00[8:0] (9 bits) Writing 1 to the ST01 bit Writing 1 to the ST01 bit To operation stop status (SE01 = 0) <10> Normal operation Writing 0 to the SWC0 bit <11> Writing 0 to the SWC0 bit Clear SNOOZE mode setting Error processing Set the SPS0 register and bits 15 to 9 in the Change to the UART Change to the UART reception baud rate in reception baud rate in SDR01 register. normal operation normal operation Writing 1 to the SS01 bit Writing 1 to the SS01 bit <12> To communication wait status (SE01 = 1) Normal operation Normal operation

Figure 11-92. Flowchart of SNOOZE Mode Operation (EOC01 = 0, SSEC0 = 0/1 or EOC01 = 1, SSEC0 = 0)

Remark <1> to <11> in the figure correspond to <1> to <11> in Figure 11-90 Timing Chart of SNOOZE Mode Operation (EOC01 = 0, SSEC0 = 0/1) and Figure 11-91 Timing Chart of SNOOZE Mode Operation (EOC01 = 1, SSEC0 = 0).

Figure 11-94. Flowchart of SNOOZE Mode Operation (EOC01 = 1, SSEC0 = 1)

#### (11) Start condition generator

This circuit generates a start condition when the STT0 bit is set to 1.

However, in the communication reservation disabled status (IICRSV0 bit = 1), when the bus is not released (IICBSY0 bit = 1), start condition requests are ignored and the STCF bit is set to 1.

# (12) Stop condition generator

This circuit generates a stop condition when the SPT0 bit is set to 1.

#### (13) Bus status detector

This circuit detects whether or not the bus is released by detecting start conditions and stop conditions.

However, as the bus status cannot be detected immediately following operation, the initial status is set by the STCEN bit.

Remark STT0 bit: Bit 1 of IICA control register 00 (IICCTL00)

SPT0 bit: Bit 0 of IICA control register 00 (IICCTL00)

IICRSV0 bit: Bit 0 of IICA flag register 0 (IICF0)

IICBSY0 bit: Bit 6 of IICA flag register 0 (IICF0)

STCF0 bit: Bit 7 of IICA flag register 0 (IICF0)

STCEN0 bit: Bit 1 of IICA flag register 0 (IICF0)

# Figure 12-8. Format of IICA Flag Register 0 (IICF0)

| Address | : FFF52H | After re | eset: 00H | R/W <sup>Not</sup> | е |   |        |         |

|---------|----------|----------|-----------|--------------------|---|---|--------|---------|

| Symbol  | <7>      | <6>      | 5         | 4                  | 3 | 2 | <1>    | <0>     |

| IICF0   | STCF0    | IICBSY0  | 0         | 0                  | 0 | 0 | STCEN0 | IICRSV0 |

| STCF0     | STT0 clear flag                                              |                                                                                                                                   |  |  |  |  |

|-----------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0         | Generate start condition                                     |                                                                                                                                   |  |  |  |  |

| 1         | Start condition generation unsuccessful: clear the STT0 flag |                                                                                                                                   |  |  |  |  |

| Condition | n for clearing (STCF0 = 0)                                   | Condition for setting (STCF0 = 1)                                                                                                 |  |  |  |  |

| 1         | by STT0 = 1<br>CE0 = 0 (operation stop)                      | - Generating start condition unsuccessful and the STT0 bit cleared to 0 when communication reservation is disabled (IICRSV0 = 1). |  |  |  |  |

| IICBSY0   | I <sup>2</sup> C bus status flag                                        |                                                                              |  |  |  |  |

|-----------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|

| 0         | Bus release status (communication initial status when STCEN0 = 1)       |                                                                              |  |  |  |  |

| 1         | Bus communication status (communication initial status when STCEN0 = 0) |                                                                              |  |  |  |  |

| Condition | n for clearing (IICBSY0 = 0)                                            | Condition for setting (IICBSY0 = 1)                                          |  |  |  |  |

| 1         | on of stop condition<br>CE0 = 0 (operation stop)                        | - Detection of start condition<br>- Setting of the IICE0 bit when STCEN0 = 0 |  |  |  |  |

| STCEN0    | Initial start enable trigger                                                                                       |                                    |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|

| 0         | After operation is enabled (IICE0 = 1), enable generation of a start condition upon detection of a stop condition. |                                    |  |  |  |  |

| 1         | After operation is enabled (IICE0 = 1), enable generation of a start condition without detecting a stop condition. |                                    |  |  |  |  |

| Condition | for clearing (STCEN0 = 0)                                                                                          | Condition for setting (STCEN0 = 1) |  |  |  |  |

|           | by instruction<br>n of start condition                                                                             | - Set by instruction               |  |  |  |  |

| IICRSV0                             | Communication reservation function disable bit |                                     |  |  |

|-------------------------------------|------------------------------------------------|-------------------------------------|--|--|

| 0                                   | Enable communication reservation               |                                     |  |  |

| 1                                   | Disable communication reservation              |                                     |  |  |

| Condition                           | for clearing (IICRSV0 = 0)                     | Condition for setting (IICRSV0 = 1) |  |  |

| - Cleared by instruction<br>- Reset |                                                | - Set by instruction                |  |  |

Note Bits 6 and 7 are read-only.

**Cautions 1.** Write to the STCEN bit only when the operation is stopped (IICE0 = 0).

- 2. As the bus release status (IICBSY = 0) is recognized regardless of the actual bus status when STCEN = 1, when generating the first start condition (STT0 = 1), it is necessary to verify that no third party communications are in progress in order to prevent such communications from being destroyed.

- 3. Write to IICRSV only when the operation is stopped (IICE0 = 0).

Remarks 1. STT0: Bit 1 of IICA control register 00 (IICCTL00)

2. IICE0: Bit 7 of IICA control register 00 (IICCTL00)

**MACOF**

MACSF

DIVST

Figure 13-5. Format of Multiplication/Division Control Register (MDUC)

Address: F00E8H After reset: 00H R/W<sup>Note 1</sup> Symbol <7> <6> <3> <2> <1> <0>

0

0

**MDUC** DIVMODE

| DIVMODE          | MACMODE | MDSM | Operation mode selection                                                           |  |

|------------------|---------|------|------------------------------------------------------------------------------------|--|

| 0                | 0       | 0    | Multiplication mode (unsigned) (default)                                           |  |

| 0                | 0       | 1    | Multiplication mode (signed)                                                       |  |

| 0                | 1       | 0    | Multiply-accumulator mode (unsigned)                                               |  |

| 0                | 1       | 1    | Multiply-accumulator mode (signed)                                                 |  |

| 1                | 0       | 0    | Division mode (unsigned), generation of a division completion interrupt (INTMD)    |  |

| 1                | 1       | 0    | Division mode (unsigned), not generation of a division completic interrupt (INTMD) |  |

| Other than above |         | /e   | Setting prohibited                                                                 |  |

**MDSM**

| MACOF | Overflow flag of multiply-accumulation result (accumulated value) |

|-------|-------------------------------------------------------------------|

| 0     | No overflow                                                       |

| 1     | With over flow                                                    |

#### <Set condition>

· For the multiply-accumulator mode (unsigned)

MACMODE

The bit is set when the accumulated value goes outside the range from 00000000h to FFFFFFFh.

For the multiply-accumulator mode (signed)

The bit is set when the result of adding a positive product to a positive accumulated value exceeds 7FFFFFFh and is negative, or when the result of adding a negative product to a negative accumulated value exceeds 80000000h and is positive.

| MACSF                                 | Sign flag of multiply-accumulation result (accumulated value) |                                                          |  |

|---------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|--|

| 0                                     | The accumulated value is positive.                            |                                                          |  |

| 1                                     | The accumulated value is negative.                            |                                                          |  |

| Multiply-accumulator mode (unsigned): |                                                               | The bit is always 0.                                     |  |

| Multiply-accumulator mode (signed):   |                                                               | The bit indicates the sign bit of the accumulated value. |  |

| DIVST <sup>Note 2</sup> | Division operation start/stop                                       |

|-------------------------|---------------------------------------------------------------------|

| 0                       | Division operation processing complete                              |

| 1                       | Starts division operation/division operation processing in progress |

## **Notes**

- 1. Bits 1 and 2 are read-only bits.

- 2. The DIVST bit can only be set (1) in the division mode. In the division mode, division operation is started by setting (1) the DIVST bit. The DIVST bit is automatically cleared (0) when the operation ends. In the multiplication mode, operation is automatically started by setting the multiplier and multiplicand to multiplication/division data register A (MDAH, MDAL), respectively.

- Cautions 1. Do not rewrite the DIVMODE, MDSM bits during operation processing (while the DIVST bit is 1). If it is rewritten, the operation result will be an undefined value.

- 2. The DIVST bit cannot be cleared (0) by using software during division operation processing (while the DIVST bit is 1).

Figure 15-3. Format of Interrupt Request Flag Registers (IF0L, IF0H, IF1L, IF1H, IF2L, IF2H) (30-pin product)

| Address: FFFE0H After reset: 00H R/W |              |               |                         |                        |                        |                        |                         |                         |

|--------------------------------------|--------------|---------------|-------------------------|------------------------|------------------------|------------------------|-------------------------|-------------------------|

| Symbol                               | <7>          | <6>           | <5>                     | <4>                    | <3>                    | <2>                    | <1>                     | <0>                     |

| IF0L                                 | PIF5         | PIF4          | PIF3                    | PIF2                   | PIF1                   | PIF0                   | LVIIF                   | WDTIIF                  |

| •                                    |              |               |                         |                        |                        |                        |                         |                         |

| Address: FFF                         | E1H After re | set: 00H R/\  | V                       |                        |                        |                        |                         |                         |

| Symbol                               | <7>          | <6>           | <5>                     | <4>                    | <3>                    | <2>                    | <1>                     | <0>                     |

| IF0H                                 | SREIF0       | SRIF0         | STIF0                   | DMAIF1 <sup>Note</sup> | DMAIF0 <sup>Note</sup> | SREIF2 <sup>Note</sup> | SRIF2 <sup>Note</sup>   | STIF2 <sup>Note</sup>   |

|                                      | TMIF01H      |               | CSIIF00                 |                        |                        |                        |                         | CSIIF20 <sup>Note</sup> |

|                                      |              |               | IICIF00 <sup>Note</sup> |                        |                        |                        |                         | IICIF20 <sup>Note</sup> |

|                                      |              |               |                         |                        |                        |                        |                         |                         |

| Address: FFF                         | E2H After re | set: 00H R/V  | V                       |                        |                        |                        |                         |                         |

| Symbol                               | <7>          | <6>           | <5>                     | <4>                    | <3>                    | <2>                    | <1>                     | <0>                     |

| IF1L                                 | TMIF03       | TMIF02        | TMIF01                  | TMIF00                 | IICAIF0                | SREIF1 Note            | SRIF1 <sup>Note</sup>   | STIF1 <sup>Note</sup>   |

|                                      |              |               |                         |                        |                        | TMIF03H                | CSIIF11 <sup>Note</sup> |                         |

|                                      |              |               |                         |                        |                        |                        | IICIF11 <sup>Note</sup> |                         |

|                                      |              |               |                         |                        |                        |                        |                         |                         |

| Address: FFF                         |              |               |                         |                        |                        |                        |                         |                         |

| Symbol                               | <7>          | 6             | 5                       | 4                      | 3                      | <2>                    | 1                       | <0>                     |

| IF1H                                 | TMIF04       | 0             | 0                       | 0                      | 0                      | TMKAIF                 | 0                       | ADIF                    |

|                                      |              |               |                         |                        |                        |                        |                         |                         |

| Address: FFF                         | D0H After re | eset: 00H R/\ |                         |                        |                        |                        |                         |                         |

| Symbol                               | 7            | 6             | 5                       | 4                      | 3                      | <2>                    | <1>                     | <0>                     |

| IF2L                                 | 0            | 0             | 0                       | 0                      | 0                      | TMIF07                 | TMIF06                  | TMIF05                  |

|                                      |              |               |                         |                        |                        |                        |                         |                         |

| Address: FFF                         | D1H After re | eset: 00H R/\ | N                       |                        |                        |                        |                         |                         |

| Symbol                               | 7            | 6             | <5>                     | 4                      | 3                      | 2                      | 1                       | 0                       |

| IF2H                                 | FLIF         | 0             | MDIF                    | 0                      | 0                      | 0                      | 0                       | 0                       |

|                                      |              |               |                         |                        |                        |                        |                         |                         |

| XXIFXX | Interrupt request flag                                   |

|--------|----------------------------------------------------------|

| 0      | No interrupt request signal is generated                 |

| 1      | Interrupt request is generated, interrupt request status |

Note Provided in the R5F102 products only.

Cautions 1. Be sure to set bits that are not available to the initial value.

When manipulating a flag of the interrupt request flag register, use a 1-bit memory manipulation instruction (CLR1). When describing in C language, use a bit manipulation instruction such as IF0L.0 = 0; or \_asm("clr1 IF0L, 0"); because the compiled assembler must be a 1-bit memory manipulation instruction (CLR1). If a program is described in C language using an 8-bit memory manipulation instruction

such as IF0L &= 0xfe; and compiled, it becomes the assembler of three instructions.

mov a, IF0L

mov a, IF0L and a, #0FEH mov IF0L, a

# 16.3 Register Controlling Key Interrupt

The key interrupt function is controlled by the following registers:

- Key return control register (KRCTL)

- Key return mode control registers (KRM0, KRM1)

- Key return flag register (KRF)

- Port mode registers 0, 4, 6 (PM0, PM4, PM6)

# 16.3.1 Key return control register (KRCTL)

This register controls the usage of the key interrupt flags (KRF0 to KRF5) and sets the detection edge.

The KRCTL register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

Figure 16-2. Format of Key Return Control Register (KRCTL)

Address: FFF34H After reset: 00H R/W

| Symbol | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|--------|------|---|---|---|---|---|---|------|

| KRCTL  | KRMD | 0 | 0 | 0 | 0 | 0 | 0 | KREG |

| KRMD | Usage of Key Interrupt Flags (KRF0 to KRF5) |  |  |  |

|------|---------------------------------------------|--|--|--|

| 0    | Does not use key interrupt flags            |  |  |  |

| 1    | Uses key interrupt flags                    |  |  |  |

| KRRG | Selection of Detection Edge (KR0 to KR9) |

|------|------------------------------------------|

| 0    | Falling edge                             |

| 1    | Rising edge                              |

| KRMD | KREG | Interrupt Function                                                      |  |  |  |  |

|------|------|-------------------------------------------------------------------------|--|--|--|--|

| 0    | 0    | Generates a key interrupt (INTKR) when detecting a falling edge.        |  |  |  |  |

|      |      | Identify the channel by checking the port level).                       |  |  |  |  |

| 0    | 1    | enerates a key interrupt (INTKR) when detecting a rising edge.          |  |  |  |  |

|      |      | (Identify the channel by checking the port level).                      |  |  |  |  |

| 1    | 0    | Generates a key interrupt (INTKR) when detecting a falling edge.        |  |  |  |  |

|      |      | (Identify the channel by using the key interrupt flags (KRF0 to KRF5)). |  |  |  |  |

| 1    | 1    | Generates a key interrupt (INTKR) when detecting a rising edge.         |  |  |  |  |

|      |      | (Identify the channel by using the key interrupt flags (KRF0 to KRF5)). |  |  |  |  |

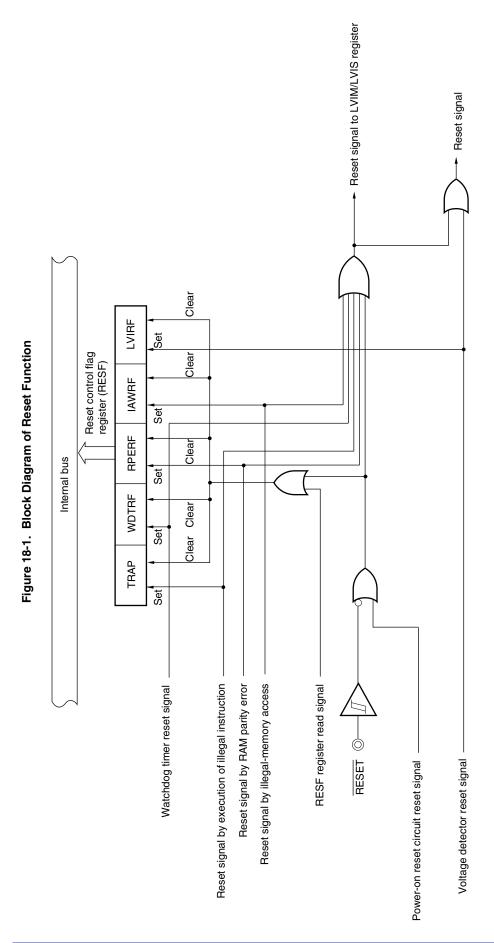

Caution An LVD circuit internal reset does not reset the LVD circuit.

Remarks 1. LVIM: Voltage detection register

2. LVIS: Voltage detection level register

<R>

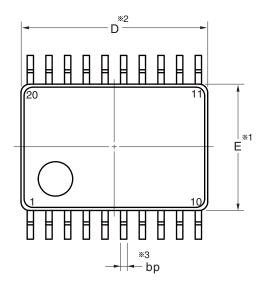

#### **CHAPTER 30 PACKAGE DRAWINGS**

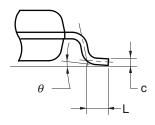

# 30.1 20-pin products

R5F1026AASP, R5F10269ASP, R5F10268ASP, R5F10267ASP, R5F10266ASP R5F1036AASP, R5F10369ASP, R5F10368ASP, R5F10367ASP, R5F10366ASP R5F1026ADSP, R5F10269DSP, R5F10268DSP, R5F10267DSP, R5F10366DSP R5F1036ADSP, R5F10369DSP, R5F10368DSP, R5F10367DSP, R5F10366DSP R5F1026AGSP, R5F10269GSP, R5F10268GSP, R5F10267GSP, R5F10266GSP

| JEITA Package Code     | RENESAS Code | Previous Code  | MASS (TYP.) [g] |

|------------------------|--------------|----------------|-----------------|

| P-LSSOP20-4.4x6.5-0.65 | PLSP0020JB-A | P20MA-65-NAA-1 | 0.1             |

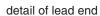

#### NOTE

- 1. Dimensions "X1" and "X2" do not include mold flash.

- 2.Dimension "¾3" does not include trim offset.

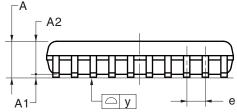

|          | (UNIT:mm)                |

|----------|--------------------------|

| ITEM     | DIMENSIONS               |

| D        | 6.50±0.10                |

| Е        | 4.40±0.10                |

| HE       | 6.40±0.20                |

| Α        | 1.45 MAX.                |

| A1       | 0.10±0.10                |

| A2       | 1.15                     |

| е        | 0.65±0.12                |

| bp       | $0.22 + 0.10 \\ -0.05$   |

| С        | $0.15 \pm 0.05 \\ -0.02$ |

| L        | 0.50±0.20                |

| У        | 0.10                     |

| $\theta$ | 0° to 10°                |

|          |                          |

©2012 Renesas Electronics Corporation. All rights reserved.