# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USI                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                      |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                             |

| Data Converters            | A/D 11x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 20-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny167-sur |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

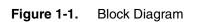

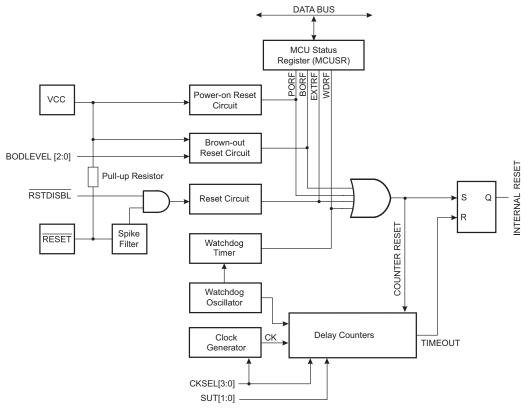

### 1.3 Block Diagram

**Atmel**

8265D-AVR-01/2014

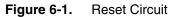

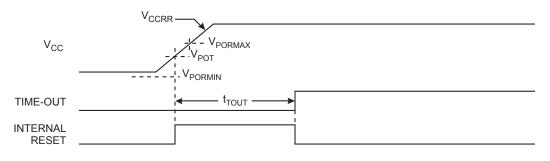

#### 6.1.3 Power-on Reset

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detection level is defined in Table 22-4 on page 245. The POR is activated whenever  $V_{CC}$  is below the detection level. The POR circuit can be used to trigger the start-up Reset, as well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the Power-on Reset threshold voltage invokes the delay counter, which determines how long the device is kept in RESET after  $V_{CC}$  rise. The RESET signal is activated again, without any delay, when  $V_{CC}$  decreases below the detection level.

Figure 6-2. MCU Start-up, RESET Tied to V<sub>CC</sub>

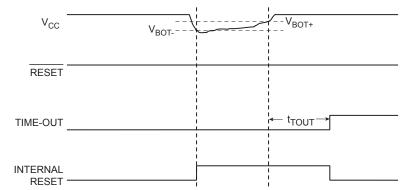

Figure 6-5. Brown-out Reset During Operation

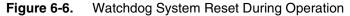

#### 6.1.6 Watchdog System Reset

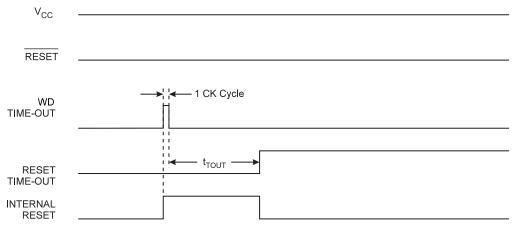

When the Watchdog times out, it will generate a short reset pulse of one CK cycle duration. On the falling edge of this pulse, the delay timer starts counting the Time-out period  $t_{TOUT}$ . Refer to page 53 for details on operation of the Watchdog Timer.

#### 6.1.7 MCUSR – MCU Status Register

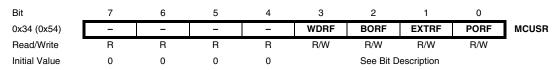

The MCU Status Register provides information on which reset source caused an MCU reset.

#### • Bits 7:4 - Res: Reserved Bits

These bits are reserved bits in the ATtiny87/167 and will always read as zero.

#### Bit 3 – WDRF: Watchdog System Reset Flag

This bit is set if a Watchdog System Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

#### Bit 2 – BORF: Brown-out Reset Flag

This bit is set if a Brown-out Reset occurs. The bit is reset by a Power-on Reset, or by writing a logic zero to the flag.

#### 9.2.6 Digital Input Enable and Sleep Modes

As shown in Figure 9-2, the digital input signal can be clamped to ground at the input of the Schmitt Trigger. The signal denoted SLEEP in the figure, is set by the MCU Sleep Controller in Power-down or Power-save mode to avoid high power consumption if some input signals are left floating, or have an analog signal level close to  $V_{CC}/2$ .

SLEEP is overridden for port pins enabled as external interrupt pins. If the external interrupt request is not enabled, SLEEP is active also for these pins. SLEEP is also overridden by various other alternate functions as described in "Alternate Port Functions" on page 72.

If a logic high level ("one") is present on an asynchronous external interrupt pin configured as "Interrupt on Rising Edge, Falling Edge, or Any Logic Change on Pin" while the external interrupt is **not** enabled, the corresponding External Interrupt Flag will be set when resuming from the above mentioned Sleep mode, as the clamping in these sleep mode produces the requested logic change.

#### 9.2.7 Unconnected Pins

If some pins are unused, it is recommended to ensure that these pins have a defined level. Even though most of the digital inputs are disabled in the deep sleep modes as described above, floating inputs should be avoided to reduce current consumption in all other modes where the digital inputs are enabled (Reset, Active mode and Idle mode).

The simplest method to ensure a defined level of an unused pin, is to enable the internal pull-up. In this case, the pull-up will be disabled during reset. If low power consumption during reset is important, it is recommended to use an external pull-up or pull-down. Connecting unused pins directly to  $V_{CC}$  or GND is not recommended, since this may cause excessive currents if the pin is accidentally configured as an output.

#### 9.3 Alternate Port Functions

Most port pins have alternate functions in addition to being general digital I/Os. Figure 9-6 shows how the port pin control signals from the simplified Figure 9-2 can be overridden by alternate functions. The overriding signals may not be present in all port pins, but the figure serves as a generic description applicable to all port pins in the AVR microcontroller family.

The alternate pin configuration is as follows:

#### Port A, Bit 7 – PCINT7/ADC7/AIN1/XREF/AREF

- PCINT7: Pin Change Interrupt, source 7.

- ADC7: Analog to Digital Converter, channel 7.

- AIN1: Analog Comparator Positive Input. This pin is directly connected to the positive input of the Analog Comparator.

- XREF: Internal Voltage Reference Output. The internal voltage reference 2.56V or 1.1V is output when XREFEN is set and if either 2.56V or 1.1V is used as reference for ADC conversion. When XREF output is enabled, the pin port pull-up and digital output driver are turned off.

- AREF: External Voltage Reference Input for ADC. The pin port pull-up and digital output driver are disabled when the pin is used as an external voltage reference input for ADC or as when the pin is only used to connect a bypass capacitor for the voltage reference of the ADC.

#### Port A, Bit 6 – PCINT6/ADC6/AIN0/SS

- PCINT6: Pin Change Interrupt, source 6.

- ADC6: Analog to Digital Converter, channel 6.

- AIN0: Analog Comparator Negative Input. This pin is directly connected to the negative input of the Analog Comparator.

- SS: SPI Slave Select Input. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDA6. As a slave, the SPI is activated when this pin is driven low. When the SPI is enabled as a master, the data direction of this pin is controlled by DDA6. When the pin is forced to be an input, the pull-up can still be controlled by the PORTA6 bit.

#### • Port A, Bit 5 – PCINT5/ADC5/T1/USCK/SCL/SCK

- PCINT5: Pin Change Interrupt, source 5.

- ADC5: Analog to Digital Converter, channel 5.

- T1: Timer/Counter1 Clock Input.

- USCK: Three-wire Mode USI Clock Input.

- SCL: Two-wire Mode USI Clock Input.

- SCK: SPI Master Clock output, Slave Clock input pin. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDA5. When the SPI is enabled as a master, the data direction of this pin is controlled by DDA5. When the pin is forced to be an input, the pull-up can still be controlled by the PORTA5 bit.

#### Port A, Bit 4 – PCINT4/ADC4/ICP1/DI/SDA/MOSI

- PCINT4: Pin Change Interrupt, source 4.

- ADC4: Analog to Digital Converter, channel 4.

- ICP1: Timer/Counter1 Input Capture Trigger. The PA3 pin can act as an Input Capture pin for Timer/Counter1.

- DI: Three-wire Mode USI Data Input. USI Three-wire mode does not override normal port functions, so pin must be configure as an input for DI function.

- SDA: Two-wire Mode Serial Interface (USI) Data Input / Output.

• MOSI: SPI Master Output / Slave Input. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDA4. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDA4. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTA4 bit.

#### • Port A, Bit 3 - PCINT3/ADC3/ISRC/INT1

- PCINT3: Pin Change Interrupt, source 3.

- ADC3: Analog to Digital Converter, channel 3.

- ISCR: Current Source Output pin. While current is sourced by the Current Source module, the user can use the Analog to Digital Converter channel 3 (ADC3) to measure the pin voltage.

- INT1: External Interrupt, source 1. The PA3 pin can serve as an external interrupt source.

#### • Port A, Bit 2 – PCINT2/ADC2/OC0A/DO/MISO

- PCINT2: Pin Change Interrupt, source 2.

- ADC2: Analog to Digital Converter, channel 2.

- OC0A: Output Compare Match A or output PWM A for Timer/Counter0. The pin has to be configured as an output (DDA2 set (one)) to serve these functions.

- DO: Three-wire Mode USI Data Output. Three-wire mode data output overrides PORTA2 and it is driven to the port when the data direction bit DDA2 is set. PORTA2 still enables the pull-up, if the direction is input and PORTA2 is set (one).

- MISO: Master Data input, Slave Data output pin for SPI channel. When the SPI is enabled as a Master, this pin is configured as an input regardless of the setting of DDA2. When the SPI is enabled as a Salve, the data direction of this pin is controlled by DDA2. When the pin is forced to be an input, the pull-up can still be controlled by PORTA2.

#### • Port A, Bit 1 – PCINT1/ADC1/TXD/TXLIN

- PCINT1: Pin Change Interrupt, source 1.

- ADC1: Analog to Digital Converter, channel 1.

- TXD: UART Transmit pin. When the UART transmitter is enabled, this pin is configured as an output regardless the value of DDA1. PORTA1 still enables the pull-up, if the direction is input and PORTA2 is set (one).

- TXLIN: LIN Transmit pin. When the LIN is enabled, this pin is configured as an output regardless the value of DDA1. PORTA1 still enables the pull-up, if the direction is input and PORTA2 is set (one).

#### Port A, Bit 0 – PCINT0/ADC0/RXD/RXLIN

- PCINT0: Pin Change Interrupt, source 0.

- ADC0: Analog to Digital Converter, channel 0.

- RXD: UART Receive pin. When the UART receiver is enabled, this pin is configured as an input regardless of the value of DDA0. When the pin is forced to be an input, a logical one in PORTA0 will turn on the internal pull-up.

- RXLIN: LIN Receive pin. When the LIN is enabled, this pin is configured as an input regardless of the value of DDA0. When the pin is forced to be an input, a logical one in PORTA0 will turn on the internal pull-up.

### 9.4 Register Description

#### 9.4.1 PORTA – Port A Data Register

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| 0x02 (0x22)   | PORTA7 | PORTA6 | PORTA5 | PORTA4 | PORTA3 | PORTA2 | PORTA1 | PORTA0 | PORTA |

| Read/Write    | R/W    |       |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

#### 9.4.2 DDRA – Port A Data Direction Register

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

| 0x01 (0x21)   | DDA7 | DDA6 | DDA5 | DDA4 | DDA3 | DDA2 | DDA1 | DDA0 | DDRA |

| Read/Write    | R/W  | •    |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

#### 9.4.3 PINA – Port A Input Pins Register

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| 0x00 (0x20)   | PINA7 | PINA6 | PINA5 | PINA4 | PINA3 | PINA2 | PINA1 | PINA0 | PINA |

| Read/Write    | R/(W) | •    |

| Initial Value | N/A   |      |

#### 9.4.4 PORTB – Port B Data Register

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _     |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| 0x05 (0x25)   | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

| Read/Write    | R/W    |       |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

#### 9.4.5 DDRB – Port B Data Direction Register

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

| 0x04 (0x24)   | DDB7 | DDB6 | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write    | R/W  | -    |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

#### 9.4.6 PINB – Port B Input Pins Register

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| 0x03 (0x23)   | PINB7 | PINB6 | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write    | R/(W) |      |

| Initial Value | N/A   |      |

#### 10.2.1 Definitions

The following definitions are used extensively throughout the section:

| BOTTOM | The counter reaches the BOTTOM when it becomes zero (0x00).                                                                                                                                                                                                   |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX    | The counter reaches its MAXimum when it becomes 0xFF (decimal 255).                                                                                                                                                                                           |

| ТОР    | The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be the fixed value 0xFF (MAX) or the value stored in the OCR0A Register. The assignment is dependent on the mode of operation. |

#### 10.3 Timer/Counter Clock Sources

The Timer/Counter can be clocked by an internal synchronous or an external asynchronous clock source. The clock source is selected by the clock select logic which is controlled by the clock select (CS0[2:0]) bits located in the Timer/Counter control register (TCCR0). The clock source clk<sub>T</sub>0 is by default equal to the MCU clock, clk<sub>I/O</sub>. When the AS0 bit in the ASSR Register is written to logic one, the clock source is taken from the Timer/Counter Oscillator connected to XTAL1 and XTAL2 or directly from XTAL1. For details on asynchronous operation, see "ASSR – Asynchronous Status Register" on page 102. For details on clock sources and prescaler, see "Timer/Counter0 Prescaler" on page 99.

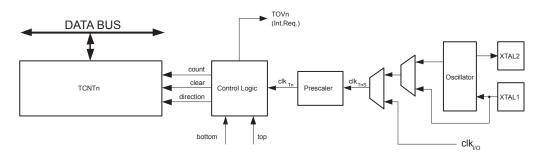

#### 10.4 Counter Unit

The main part of the 8-bit Timer/Counter is the programmable bi-directional counter unit. Figure 10-2 shows a block diagram of the counter and its surrounding environment.

Figure 10-2. Counter Unit Block Diagram

Signal description (internal signals):

| count                     | Increment or decrement TCNT0 by 1.                      |

|---------------------------|---------------------------------------------------------|

| direction                 | Selects between increment and decrement.                |

| clear                     | Clear TCNT0 (set all bits to zero).                     |

| <b>clk</b> <sub>T</sub> 0 | Timer/Counter0 clock.                                   |

| top                       | Signalizes that TCNT0 has reached maximum value.        |

| bottom                    | Signalizes that TCNT0 has reached minimum value (zero). |

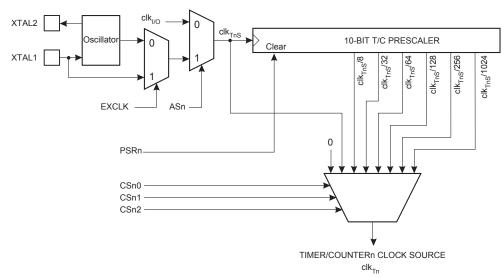

#### 10.10 Timer/Counter0 Prescaler

Figure 10-12. Prescaler for Timer/Counter0

The clock source for Timer/Counter0 is named  $clk_T0_S$ .  $clk_T0_S$  is by default connected to the main system I/O clock  $clk_{IO}$ . By setting the AS0 bit in ASSR, Timer/Counter0 is asynchronously clocked from the XTAL oscillator or XTAL1 pin. This enables use of Timer/Counter0 as a Real Time Counter (RTC).

A crystal can then be connected between the XTAL1 and XTAL2 pins to serve as an independent clock source for Timer/Counter0.

A external clock can also be used using XTAL1 as input. Setting AS0 and EXCLK enables this configuration.

For Timer/Counter0, the possible prescaled selections are:  $clk_T0_S/8$ ,  $clk_T0_S/32$ ,  $clk_T0_S/64$ ,  $clk_T0_S/128$ ,  $clk_T0_S/256$ , and  $clk_T0_S/1024$ . Additionally,  $clk_T0_S$  as well as 0 (stop) may be selected. Setting the PSR0 bit in GTCCR resets the prescaler. This allows the user to operate with a predictable prescaler.

#### **10.11 Register Description**

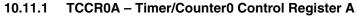

#### • Bits 7:6 – COM0A[1:0]: Compare Match Output Mode A

Atmel

These bits control the Output Compare pin (OC0A) behavior. If one or both of the COM0A[1:0] bits are set, the OC0A output overrides the normal port functionality of the I/O pin it is connected to. However, note that the Data Direction Register (DDR) bit corresponding to OC0A pin must be set in order to enable the output driver.

## ATtiny87/167

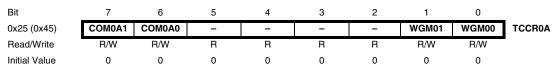

#### 10.11.8 GTCCR – General Timer/Counter Control Register

#### • Bit 1 – PSR0: Prescaler Reset Timer/Counter0

When this bit is one, the Timer/Counter0 prescaler will be reset. This bit is normally cleared immediately by hardware. If the bit is written when Timer/Counter0 is operating in asynchronous mode, the bit will remain one until the prescaler has been reset. The bit will not be cleared by hardware if the TSM bit is set. Refer to the description of the "Bit 7 – TSM: Timer/Counter Synchronization Mode" on page 108 for a description of the Timer/Counter Synchronization mode.

The Timer/Counter can be clocked internally, via the prescaler, or by an external clock source on the Tn pin. The Clock Select logic block controls which clock source and edge the Timer/Counter uses to increment (or decrement) its value. The Timer/Counter is inactive when no clock source is selected. The output from the Clock Select logic is referred to as the timer clock (clk<sub>Tn</sub>).

The double buffered Output Compare Registers (OCR1A/B) are compared with the Timer/Counter value at all time. The result of the compare can be used by the Waveform Generator to generate a PWM or variable frequency output on the Output Compare pins See "Output Compare Units" on page 118.. The compare match event will also set the Compare Match Flag (OCF1A/B) which can be used to generate an Output Compare interrupt request.

The Input Capture Register can capture the Timer/Counter value at a given external (edge triggered) event on either the Input Capture pin (ICP1) or on the Analog Comparator pins (See "AnaComp - Analog Comparator" on page 210.). The Input Capture unit includes a digital filtering unit (Noise Canceler) for reducing the chance of capturing noise spikes.

The TOP value, or maximum Timer/Counter value, can in some modes of operation be defined by either the OCR1A Register, the ICR1 Register, or by a set of fixed values. When using OCR1A as TOP value in a PWM mode, the OCR1A Register can not be used for generating a PWM output. However, the TOP value will in this case be double buffered allowing the TOP value to be changed in run time. If a fixed TOP value is required, the ICR1 Register can be used as an alternative, freeing the OCR1A to be used as PWM output.

#### 12.2.2 Definitions

The following definitions are used extensively throughout the section:

| BOTTOM | The counter reaches the BOTTOM when it becomes 0x0000.                                                                                                                                                                                                                                            |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX    | The counter reaches its MAXimum when it becomes 0xFFFF (decimal 65,535).                                                                                                                                                                                                                          |

| ТОР    | The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be one of the fixed values: 0x00FF, 0x01FF, or 0x03FF, or to the value stored in the OCR1A or ICR1 Register. The assignment is dependent of the mode of operation. |

#### 12.3 Accessing 16-bit Registers

The TCNT1, OCR1A/B, and ICR1 are 16-bit registers that can be accessed by the AVR CPU via the 8-bit data bus. The 16-bit register must be byte accessed using two read or write operations. Each 16-bit timer has a single 8-bit register for temporary storing of the high byte of the 16-bit access. The same temporary register is shared between all 16-bit registers within each 16-bit timer. Accessing the low byte triggers the 16-bit read or write operation. When the low byte of a 16-bit register is written by the CPU, the high byte stored in the temporary register, and the low byte written are both copied into the 16-bit register in the same clock cycle. When the low byte of a 16-bit register is read by the CPU, the high byte of the 16-bit register is copied into the temporary register in the same clock cycle. When the low byte of a 16-bit register is read by the CPU, the high byte of the 16-bit register is copied into the temporary register in the same clock cycle as the low byte is read.

Not all 16-bit accesses uses the temporary register for the high byte. Reading the OCR1A/B 16-bit registers does not involve using the temporary register.

To do a 16-bit write, the high byte must be written before the low byte. For a 16-bit read, the low byte must be read before the high byte.

Atmel

The Timer/Counter Overflow Flag (TOV1) is set according to the mode of operation selected by the WGM1[3:0] bits. TOV1 can be used for generating a CPU interrupt.

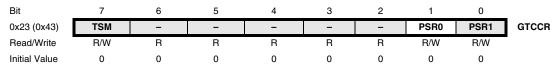

#### 12.6 Input Capture Unit

The Timer/Counter incorporates an Input Capture unit that can capture external events and give them a time-stamp indicating time of occurrence. The external signal indicating an event, or multiple events, can be applied via the ICP1 pin or alternatively, via the analog-comparator unit. The time-stamps can then be used to calculate frequency, duty-cycle, and other features of the signal applied. Alternatively the time-stamps can be used for creating a log of the events.

The Input Capture unit is illustrated by the block diagram shown in Figure 12-3. The elements of the block diagram that are not directly a part of the Input Capture unit are gray shaded.

Figure 12-3. Input Capture Unit Block Diagram

When a change of the logic level (an event) occurs on the Input Capture pin (ICP1), alternatively on the Analog Comparator output (ACO), and this change confirms to the setting of the edge detector, a capture will be triggered. When a capture is triggered, the 16-bit value of the counter (TCNT1) is written to the Input Capture Register (ICR1). The Input Capture Flag (ICF1) is set at the same system clock as the TCNT1 value is copied into ICR1 Register. If enabled (ICIE1 = 1), the Input Capture Flag generates an Input Capture interrupt. The ICF1 flag is automatically cleared when the interrupt is executed. Alternatively the ICF1 flag can be cleared by software by writing a logical one to its I/O bit location.

Reading the 16-bit value in the Input Capture Register (ICR1) is done by first reading the low byte (ICR1L) and then the high byte (ICR1H). When the low byte is read the high byte is copied into the high byte temporary register (TEMP). When the CPU reads the ICR1H I/O location it will access the TEMP Register.

The ICR1 Register can only be written when using a Waveform Generation mode that utilizes the ICR1 Register for defining the counter's TOP value. In these cases the Waveform Generation mode (WGM1[3:0]) bits must be set before the TOP value can be written to the ICR1

#### 12.11.2 TCCR1B – Timer/Counter1 Control Register B

| Bit           | 7     | 6     | 5 | 4     | 3     | 2    | 1    | 0    | _      |

|---------------|-------|-------|---|-------|-------|------|------|------|--------|

| (0x81)        | ICNC1 | ICES1 | - | WGM13 | WGM12 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write    | R/W   | R/W   | R | R/W   | R/W   | R/W  | R/W  | R/W  | -      |

| Initial Value | 0     | 0     | 0 | 0     | 0     | 0    | 0    | 0    |        |

#### • Bit 7 – ICNC1: Input Capture Noise Canceler

Setting this bit (to one) activates the Input Capture Noise Canceler. When the noise canceler is activated, the input from the Input Capture pin (ICP1) is filtered. The filter function requires four successive equal valued samples of the ICP1 pin for changing its output. The Input Capture is therefore delayed by four Oscillator cycles when the noise canceler is enabled.

#### Bit 6 – ICES1: Input Capture Edge Select

This bit selects which edge on the Input Capture pin (ICP1) that is used to trigger a capture event. When the ICES1 bit is written to zero, a falling (negative) edge is used as trigger, and when the ICES1 bit is written to one, a rising (positive) edge will trigger the capture.

When a capture is triggered according to the ICES1 setting, the counter value is copied into the Input Capture Register (ICR1). The event will also set the Input Capture Flag (ICF1), and this can be used to cause an Input Capture Interrupt, if this interrupt is enabled.

When the ICR1 is used as TOP value (see description of the WGM1[3:0] bits located in the TCCR1A and the TCCR1B Register), the ICP1 is disconnected and consequently the Input Capture function is disabled.

#### Bit 5 – Res: Reserved Bit

This bit is reserved for future use. For ensuring compatibility with future devices, this bit must be written to zero when TCCR1B is written.

#### • Bits 4:3 – WGM1[3:2]: Waveform Generation Mode

See TCCR1A Register description.

#### Bits 2:0 – CS1[2:0]: Clock Select

The three Clock Select bits select the clock source to be used by the Timer/Counter, see Figure 12-11 and Figure 12-12.

| CS12 | CS11 | CS10 | Description                                             |  |  |  |  |

|------|------|------|---------------------------------------------------------|--|--|--|--|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped).                |  |  |  |  |

| 0    | 0    | 1    | clk <sub>I/O</sub> /1 (No prescaling)                   |  |  |  |  |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)                  |  |  |  |  |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64 (From prescaler)                 |  |  |  |  |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256 (From prescaler)                |  |  |  |  |

| 1    | 0    | 1    | clk <sub>I/O</sub> /1024 (From prescaler)               |  |  |  |  |

| 1    | 1    | 0    | External clock source on T1 pin. Clock on falling edge. |  |  |  |  |

| 1    | 1    | 1    | External clock source on T1 pin. Clock on rising edge.  |  |  |  |  |

Table 12-5.

Clock Select Bit Description

#### Bit 5 – DORD: Data Order

When the DORD bit is written to one, the LSB of the data word is transmitted first.

When the DORD bit is written to zero, the MSB of the data word is transmitted first.

#### • Bit 4 – MSTR: Master/Slave Select

This bit selects Master SPI mode when written to one, and Slave SPI mode when written logic zero. If  $\overline{SS}$  is configured as an input and is driven low while MSTR is set, MSTR will be cleared, and SPIF in SPSR will become set. The user will then have to set MSTR to re-enable SPI Master mode.

#### • Bit 3 – CPOL: Clock Polarity

When this bit is written to one, SCK is high when idle. When CPOL is written to zero, SCK is low when idle. Refer to Figure 13-3 and Figure 13-4 for an example. The CPOL functionality is summarized below:

Table 13-2. CPOL Functionality

| CPOL | Leading Edge | Trailing Edge |

|------|--------------|---------------|

| 0    | Rising       | Falling       |

| 1    | Falling      | Rising        |

#### Bit 2 – CPHA: Clock Phase

The settings of the Clock Phase bit (CPHA) determine if data is sampled on the leading (first) or trailing (last) edge of SCK. Refer to Figure 13-3 and Figure 13-4 for an example. The CPOL functionality is summarized below:

| Table 13-3. | CPHA Functionality |

|-------------|--------------------|

|-------------|--------------------|

| СРНА | Leading Edge | Trailing Edge |

|------|--------------|---------------|

| 0    | Sample       | Setup         |

| 1    | Setup        | Sample        |

#### Bits 1:0 – SPR[1:0]: SPI Clock Rate Select 1 and 0

These two bits control the SCK rate of the device configured as a Master. SPR1 and SPR0 have no effect on the Slave. The relationship between SCK and the  $clk_{IO}$  frequency  $f_{clkio}$  is shown in the following table:

Table 13-4.

Relationship Between SCK and the Oscillator Frequency

|       | 1    |      |                         |

|-------|------|------|-------------------------|

| SPI2X | SPR1 | SPR0 | SCK Frequency           |

| 0     | 0    | 0    | f <sub>clkio</sub> /4   |

| 0     | 0    | 1    | f <sub>clkio</sub> /16  |

| 0     | 1    | 0    | f <sub>clkio</sub> /64  |

| 0     | 1    | 1    | f <sub>clkio</sub> /128 |

| 1     | 0    | 0    | f <sub>clkio</sub> /2   |

| 1     | 0    | 1    | f <sub>clkio</sub> /8   |

| 1     | 1    | 0    | f <sub>clkio</sub> /32  |

| 1     | 1    | 1    | f <sub>clkio</sub> /64  |

## ATtiny87/167

## 15. LIN / UART - Local Interconnect Network Controller or UART

The LIN (Local Interconnect Network) is a serial communications protocol which efficiently supports the control of mechatronics nodes in distributed automotive applications, but is equally suited for industrial applications. The main properties of the LIN bus are:

- · Single master with multiple slaves concept

- Low cost silicon implementation based on common UART/SCI interface

- · Self synchronization with on-chip oscillator in slave node

- Deterministic signal transmission with signal propagation time computable in advance

- Low cost single-wire implementation

- Speed up to 20 Kbit/s.

LIN provides a cost efficient bus communication where the bandwidth and versatility of CAN are not required. The specification of the line driver/receiver needs to match the ISO9141 NRZ-standard.

If LIN is not required, the controller alternatively can be programmed as Universal Asynchronous serial Receiver and Transmitter (UART).

#### 15.1 LIN Features

- Hardware Implementation of LIN 2.1 (LIN 1.3 Compatibility)

- Small, CPU Efficient and Independent Master/Slave Routines Based on "LIN Work Flow Concept" of LIN 2.1 Specification

- Automatic LIN Header Handling and Filtering of Irrelevant LIN Frames

- Automatic LIN Response Handling

- Extended LIN Error Detection and Signaling

- Hardware Frame Time-out Detection

- "Break-in-data" Support Capability

- Automatic Re-synchronization to Ensure Proper Frame Integrity

- Fully Flexible Extended Frames Support Capabilities

#### 15.2 UART Features

- Full Duplex Operation (Independent Serial Receive and Transmit Processes)

- Asynchronous Operation

- High Resolution Baud Rate Generator

- Hardware Support of 8 Data Bits, Odd/Even/No Parity Bit, 1 Stop Bit Frames

- Data Over-Run and Framing Error Detection

#### 15.4.1 LIN Overview

The LIN/UART controller is designed to match as closely as possible to the LIN software application structure. The LIN software application is developed as independent tasks, several slave tasks and one master task (c.f. Section 15.3.4 on page 163). The ATtiny87/167 conforms to this perspective. The only link between the master task and the slave task will be at the cross-over point where the interrupt routine is called once a new identifier is available. Thus, in a master node, housing both master and slave task, the Tx LIN Header function will alert the slave task of an identifier presence. In the same way, in a slave node, the Rx LIN Header function will alert the slave task of an identifier presence.

When the slave task is warned of an identifier presence, it has first to analyze it to know what to do with the response. Hardware flags identify the presence of one of the specific identifiers from 60 (0x3C) up to 63 (0x3F).

For LIN communication, only four interrupts need to be managed:

- LIDOK: New LIN identifier available,

- LRXOK: LIN response received,

- LTXOK: LIN response transmitted,

- LERR: LIN Error(s).

The wake-up management can be automated using the UART wake-up capability and a node sending a minimum of 5 low bits (0xF0) for LIN 2.1 and 8 low bits (0x80) for LIN 1.3. Pin change interrupt on LIN wake-up signal can be also used to exit the device of one of its sleep modes.

Extended frame identifiers 62 (0x3E) and 63 (0x3F) are reserved to allow the embedding of user-defined message formats and future LIN formats. The byte transfer mode offered by the UART will ensure the upwards compatibility of LIN slaves with accommodation of the LIN protocol.

#### 15.4.2 UART Overview

The LIN/UART controller can also function as a conventional UART. By default, the UART operates as a full duplex controller. It has local loop back circuitry for test purposes. The UART has the ability to buffer one character for transmit and two for receive. The receive buffer is made of one 8-bit serial register followed by one 8-bit independent buffer register. Automatic flag management is implemented when the application puts or gets characters, thus reducing the software overhead. Because transmit and receive services are independent, the user can save one device pin when one of the two services is not used. The UART has an enhanced baud rate generator providing a maximum error of 2% whatever the clock frequency and the targeted baud rate.

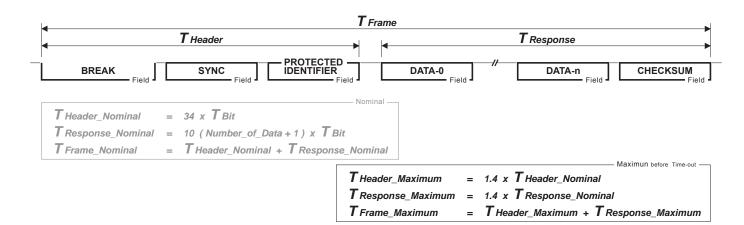

#### 15.5.10 Frame Time Out

According to the LIN protocol, a frame time-out error is flagged if:  $T_{Frame} > T_{Frame}_{Maximum}$ . This feature is implemented in the LIN/UART controller.

Figure 15-12. LIN timing and frame time-out

#### 15.5.11 Break-in-data

According to the LIN protocol, the LIN/UART controller can detect the BREAK/SYNC field sequence even if the break is partially superimposed with a byte of the response. When a BREAK/SYNC field sequence happens, the transfer in progress is aborted and the processing of the new frame starts.

- On slave node(s), an error is generated (i.e. LBERR in case of *Tx Response* or LFERR in case of *Rx Response*). Information on data error is also available, refer to the Section 15.5.7.5.

- On master node, the user (code) is responsible for this aborting of frame. To do this, the

master task has first to abort the on-going communication (clearing LCMD bits *LIN Abort*command) and then to apply the *Tx Header* command. In this case, the abort error flag LABORT is set.

On the slave node, the BREAK detection is processed with the synchronization setting available when the LIN/UART controller processed the (aborted) response. But the re-synchronization restarts as usual. Due to a possible difference of timing reference between the BREAK field and the rest of the frame, the time-out values can be slightly inaccurate.

#### 15.5.12 Checksum

The last field of a frame is the checksum.

In LIN 2.1, the checksum contains the inverted eight bit sum with carry over all data bytes and the protected identifier. This calculation is called enhanced checksum.

$$\mathsf{CHECKSUM} = 255 - \left(\mathsf{unsigned} \ \mathsf{char}\left(\left(\sum_{0}^{n} \mathsf{DATA}_{n}\right) + \mathsf{PROTECTED} \ \mathsf{ID.}\right) + \mathsf{unsigned} \ \mathsf{char}\left(\left(\left(\sum_{0}^{n} \mathsf{DATA}_{n}\right) + \mathsf{PROTECTED} \ \mathsf{ID.}\right) \\ \ast \ \mathsf{8}\right)\right)$$

In LIN 1.3, the checksum contains the inverted eight bit sum with carry over all data bytes. This calculation is called classic checksum.

#### 17.11.4 ADCSRB – ADC Control and Status Register B

| Bit           | 7   | 6    | 5     | 4     | 3 | 2     | 1     | 0     | _      |

|---------------|-----|------|-------|-------|---|-------|-------|-------|--------|

| (0x7B)        | BIN | ACME | ACIR1 | ACIR0 | - | ADTS2 | ADTS1 | ADTS0 | ADCSRB |

| Read/Write    | R/W | R/W  | R/W   | R/W   | R | R/W   | R/W   | R/W   | •      |

| Initial Value | 0   | 0    | 0     | 0     | 0 | 0     | 0     | 0     |        |

#### • Bit 7 – BIN: Bipolar Input Mode

The gain stage is working in the unipolar mode as default, but the bipolar mode can be selected by writing the BIN bit in the ADCSRB register. In the unipolar mode only one-sided conversions are supported and the voltage on the positive input must always be larger than the voltage on the negative input. Otherwise the result is saturated to the voltage reference. In the bipolar mode two-sided conversions are supported and the result is represented in the two's complement form. In the unipolar mode the resolution is 10 bits and the bipolar mode the resolution is 9 bits + 1 sign bit.

#### • Bit 3 - Res: Reserved Bit

This bit is reserved for future use. For compatibility with future devices it must be written to zero when ADCSRB register is written.

#### • Bits 2:0 – ADTS[2:0]: ADC Auto Trigger Source

If ADATE in ADCSRA register is written to one, the value of these bits selects which source will trigger an ADC conversion. If ADATE is cleared, the ADTS[2:0] settings will have no effect. A conversion will be triggered by the rising edge of the selected Interrupt Flag. Note that switching from a trigger source that is cleared to a trigger source that is set, will generate a positive edge on the trigger signal. If ADEN in ADCSRA register is set, this will start a conversion. Switching to Free Running mode (ADTS[2:0]=0) will not cause a trigger event, even if the ADC Interrupt Flag is set.

| ADTS2 | ADTS1 | ADTS0 | Trigger Source                 |

|-------|-------|-------|--------------------------------|

| 0     | 0     | 0     | Free Running mode              |

| 0     | 0     | 1     | Analog Comparator              |

| 0     | 1     | 0     | External Interrupt Request 0   |

| 0     | 1     | 1     | Timer/Counter1 Compare Match A |

| 1     | 0     | 0     | Timer/Counter1 Overflow        |

| 1     | 0     | 1     | Timer/Counter1 Compare Match B |

| 1     | 1     | 0     | Timer/Counter1 Capture Event   |

| 1     | 1     | 1     | Watchdog Interrupt Request     |

Table 17-7.

ADC Auto Trigger Source Selections

#### 17.11.5 DIDR0 – Digital Input Disable Register 0

| Bit           | 7                | 6                | 5     | 4     | 3     | 2     | 1     | 0     |       |

|---------------|------------------|------------------|-------|-------|-------|-------|-------|-------|-------|

| (0x7E)        | ADC7D /<br>AIN1D | ADC6D /<br>AIN0D | ADC5D | ADC4D | ADC3D | ADC2D | ADC1D | ADC0D | DIDR0 |

| Read/Write    | R/W              | R/W              | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |       |

| Initial Value | 0                | 0                | 0     | 0     | 0     | 0     | 0     | 0     |       |

#### 22.4.3 External Clock Drive

|                     |                                                      |      | c =<br>5.5V |      | c =<br>5.5V | _    | c =<br>5.5V |       |

|---------------------|------------------------------------------------------|------|-------------|------|-------------|------|-------------|-------|

| Symbol              | Parameter                                            | Min. | Max.        | Min. | Max.        | Min. | Max.        | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency                                 | 0    | 4           | 0    | 8           | 0    | 16          | MHz   |

| t <sub>CLCL</sub>   | Clock Period                                         | 250  |             | 125  |             | 62.5 |             | ns    |

| t <sub>CHCX</sub>   | High Time                                            | 100  |             | 50   |             | 25   |             | ns    |

| t <sub>CLCX</sub>   | Low Time                                             | 100  |             | 50   |             | 25   |             | ns    |

| t <sub>CLCH</sub>   | Rise Time                                            |      | 2.0         |      | 1.6         |      | 0.5         | μS    |

| t <sub>CHCL</sub>   | Fall Time                                            |      | 2.0         |      | 1.6         |      | 0.5         | μS    |

| $\Delta t_{CLCL}$   | Change in period from one<br>clock cycle to the next |      | 2           |      | 2           |      | 2           | %     |

Table 22-2.External Clock Drive

## 22.5 **RESET Characteristics**

| Symbol           | Parameter                             | Condition                                        | Min                 | Тур | Max                 | Units |

|------------------|---------------------------------------|--------------------------------------------------|---------------------|-----|---------------------|-------|

| V <sub>RST</sub> | RESET Pin Threshold<br>Voltage        | $V_{CC} = 5V$                                    | 0.2 V <sub>CC</sub> |     | 0.9 V <sub>CC</sub> | V     |

| t <sub>RST</sub> | Minimum pulse width on RESET Pin      | $V_{CC} = 5V$                                    |                     |     | 2.5                 | μs    |

| $V_{BG}$         | Bandgap reference voltage             | V <sub>CC</sub> = 2.7V,<br>T <sub>A</sub> = 25°C | 1.0                 | 1.1 | 1.2                 | V     |

| t <sub>BG</sub>  | Bandgap reference start-up time       | V <sub>CC</sub> = 2.7V,<br>T <sub>A</sub> = 25°C |                     | 40  | 70                  | μs    |

| I <sub>BG</sub>  | Bandgap reference current consumption | V <sub>CC</sub> = 2.7V,<br>T <sub>A</sub> = 25°C |                     | 15  |                     | μA    |

Table 22-3. External Reset Characteristics

Table 22-4. Power On Reset Characteristics

| Symbol              | Parameter                                                          | Min   | Тур | Max | Units |

|---------------------|--------------------------------------------------------------------|-------|-----|-----|-------|

| V                   | Power-on Reset Threshold Voltage (rising)                          |       | 1.4 |     | V     |

| V <sub>POT</sub>    | Power-on Reset Threshold Voltage (falling) <sup>(1)</sup>          | 1.0   | 1.3 | 1.6 | V     |

| V <sub>PORMAX</sub> | VCC Max. start voltage to ensure internal<br>Power-on Reset signal |       |     | 0.4 | V     |

| V <sub>PORMIN</sub> | VCC Min. start voltage to ensure internal<br>Power-on Reset signal | - 0.1 |     |     | V     |

| V <sub>CCRR</sub>   | VCC Rise Rate to ensure Power-on Reset                             | 0.01  |     |     | V/ms  |

Note: 1. Before rising, the supply has to be between VPORMIN and VPORMAX to ensure a Reset.

**Atmel**

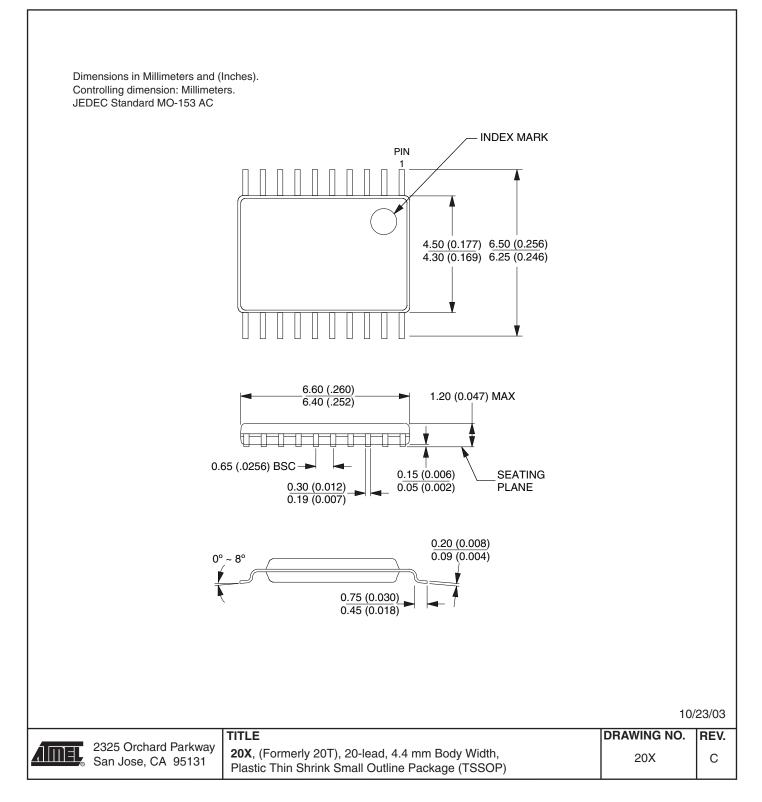

27.3 20X