Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | Z8                                                          |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 12MHz                                                       |

| Connectivity               | -                                                           |

| Peripherals                | POR, WDT                                                    |

| Number of I/O              | 14                                                          |

| Program Memory Size        | 2KB (2K x 8)                                                |

| Program Memory Type        | ROM                                                         |

| EEPROM Size                | -                                                           |

| RAM Size                   | 125 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                   |

| Data Converters            | -                                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                             |

| Mounting Type              | Through Hole                                                |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                     |

| Supplier Device Package    | 18-DIP                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86c0812pscr2409 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **GENERAL DESCRIPTION** (Continued)

**Note:** All signals with a preceding front slash, "/", are active Low. For example, B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>cc</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>ss</sub> |

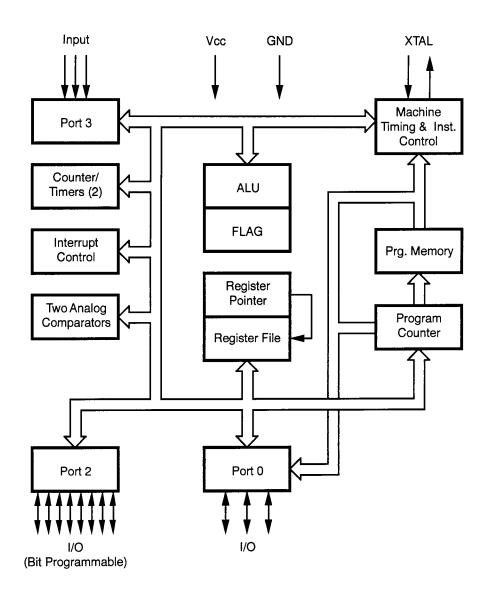

Figure 1. Z86C04/C08 Functional Block Diagram

# ABSOLUTE MAXIMUM RATINGS

| Parameter                                              | Min     | Max                | Units | Notes |

|--------------------------------------------------------|---------|--------------------|-------|-------|

| Ambient Temperature under Bias                         | -40     | +105               | С     |       |

| Storage Temperature                                    | -65     | +150               | С     |       |

| Voltage on any Pin with Respect to V <sub>ss</sub>     | -0.7    | +12                | V     | 1     |

| Voltage on $V_{_{DD}}$ Pin with Respect to $V_{_{SS}}$ | -0.3    | +7                 | V     |       |

| Voltage on Pin 7 with Respect to Vss                   | -0.7    | V <sub>DD</sub> +1 | V     | 2     |

| Total Power Dissipation                                |         | 462                | mW    |       |

| Maximum Current out of V <sub>ss</sub>                 |         | 84                 | mA    |       |

| Maximum Current into V                                 |         | 84                 | mA    |       |

| Maximum Current into an Input Pin                      | -600    | +600               | μA    | 3     |

| Maximum Current into an Open-Drain Pin                 | -600    | +600               | μA    | 4     |

| Maximum Output Current Sinked by Any I/O Pin           |         | 12                 | mA    |       |

| Maximum Output Current Sourced by Any I/O Pin          | · · · · | 12                 | mA    |       |

| Total Maximum Output Current Sinked by Port 2          |         | 70                 | mA    |       |

| Total Maximum Output Current Sourced by Port 2         |         | 70                 | mA    |       |

|                                                        |         |                    |       |       |

#### Notes:

- 1. This applies to all pins except where otherwise noted. Maximum current into pin must be ±600µA.

- 2. There is no input protection diode from pin to  $V_{\text{DD}}$ .

- 3. This excludes Pin 6 and Pin 7.

- 4. Device pin is not at an output Low state.

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability. Total power dissipation should not exceed 462 mW for the package. Power dissipation is calculated as follows:

Total Power dissipation =  $V_{DD} \times [I_{DD} - (\text{sum of } I_{OH})] + \text{sum of} [(V_{DD} - V_{OH}) \times I_{OH}] + \text{sum of} (V_{OL} \times I_{OL}).$

### STANDARD TEST CONDITIONS

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to Ground. Positive current flows into the referenced pin (Figure 4).

Figure 4. Test Load Diagram

### CAPACITANCE

$T_{A} = 25^{\circ}C$ ,  $V_{CC} = GND = 0V$ , f = 1.0 MHz, unmeasured pins returned to GND.

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 15 pF |

| Output capacitance | 0   | 20 pF |

| I/O capacitance    | 0   | 25 pF |

## DC ELECTRICAL CHARACTERISTICS (Continued)

| I <sub>CC</sub>  | Supply Current                     | 5.5V | 15   | 9.0  | mA | All Output and I/O Pins Floating @ 12 MHz                           | 5,7 |

|------------------|------------------------------------|------|------|------|----|---------------------------------------------------------------------|-----|

| I<br>CC1         | Standby Current                    | 3.0V | 2.5  | 0.7  | mA |                                                                     | 5,7 |

|                  |                                    | 5.5V | 4.0  | 2.5  | mA | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>cc</sub> @ 2 MHz          | 5,7 |

|                  |                                    | 3.0V | 4.0  | 1.0  | mA | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>cc</sub> @ 8 MHz          | 5,7 |

|                  |                                    | 5.5V | 5.0  | 3.0  | mA | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>cc</sub> @ 8 MHz          | 5,7 |

|                  |                                    | 3.0V | 4.5  | 1.5  | mA | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>cc</sub> @ 12 MHz         | 5,7 |

|                  |                                    | 5.5V | 7.0  | 4.0  | mA | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>cc</sub> @ 12 MHz         | 5,7 |

| I <sub>cc</sub>  | Supply Current<br>(Low Noise Mode) | 3.0V | 3.5  | 1.5  | mA | All Output and I/O Pins Floating @<br>1 MHz                         | 7   |

|                  |                                    | 5.5V | 7.0  | 3.8  | mA | All Output and I/O Pins Floating @<br>1 MHz                         | 7   |

|                  |                                    | 3.0V | 5.8  | 2.5  | mA | All Output and I/O Pins Floating @ 2 MHz                            | 7   |

|                  |                                    | 5.5V | 9.0  | 4.0  | mA | All Output and I/O Pins Floating @ 2 MHz                            | 7   |

| I<br>CC1         | Standby Current                    | 3.0V | 2.5  | 0.7  | mA | HALT Mode V <sub>IN</sub> = 0V, V <sub>cc</sub> @ 1MHz              | 7   |

|                  | (Low Noise Mode)                   | 5.5V | 4.0  | 2.5  | mA | HALT Mode V <sub>IN</sub> = 0V, V <sub>cc</sub> @ 1MHz              | 7   |

|                  |                                    | 3.0V | 3.0  | 0.9  | mA | HALT Mode $V_{IN} = 0V, V_{CC} @ 2 MHz$                             | 7   |

|                  |                                    | 5.5V | 4.5  | 2.8  | mA | HALT Mode V <sub>IN</sub> = 0V, V <sub>cc</sub> @ 2 MHz             | 7   |

| I <sub>CC2</sub> | Standby Current                    | 3.0V | 20   | 1.0  | μA | STOP Mode V <sub>IN</sub> = 0V, V <sub>cc</sub> ;WDT is not Running | 7   |

|                  |                                    | 5.5V | 20   | 1.0  | μA | STOP Mode V <sub>IN</sub> = 0V, V <sub>cc</sub> ;WDT is not Running | 7   |

| I <sub>ALL</sub> | Auto Latch Low Current             | 3.0V | 8.0  | 3.0  | μA | $0V < V_{IN} < V_{CC}$                                              |     |

|                  |                                    | 5.5V | 36   | 16   | μA | $0V < V_{IN} < V_{cc}$                                              |     |

| I <sub>ALH</sub> | Auto Latch High Current            | 3.0V | -5.0 | -1.5 | μA | $0V < V_{IN} < V_{cc}$                                              |     |

|                  |                                    | 5.5V | -22  | -8.0 | μA | 0V < V <sub>IN</sub> < V <sub>cc</sub>                              |     |

#### Notes:

1. Port 0, 2, and 3 only

2.  $V_{SS} = 0V = GND$

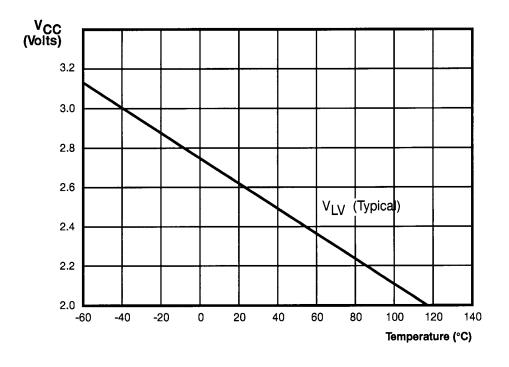

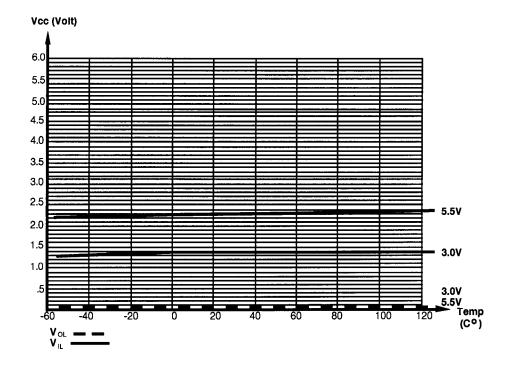

3. The device operates down to  $V_{LV}$ . The minimum operational  $V_{CC}$  is determined on the value of the voltage  $V_{LV}$  at the ambient temperature. The  $V_{LV}$  increases as the temperature decreases.

4. V<sub>CC</sub> = 3.0V to 5.5V, typical values measured at V<sub>CC</sub> = 3.3V and V<sub>CC</sub> = 5.0V.

5. Standard Mode (not Low EMI Mode)

6. Z86C08 only

7. Inputs at power rail and outputs are unloaded.

8. Low EMI Mode

|                     |                                                  |          | ~ ~                  | 0°C to<br>0°C        | ~                    | 0°C to<br>5°C        | Typical |       |                                                |       |

|---------------------|--------------------------------------------------|----------|----------------------|----------------------|----------------------|----------------------|---------|-------|------------------------------------------------|-------|

| Symbol              | Parameter                                        | $v_{cc}$ | Min                  | Max                  | Min                  | Max                  | @ 25°C  | Units | Conditions                                     | Notes |

| V <sub>CH</sub>     | Clock Input High<br>Voltage                      | 3.0V     | 0.8 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 0.8 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 1.7     | V     | Driven by External<br>Clock Generator          |       |

|                     |                                                  | 5.5V     | 0.8 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 0.8 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 2.8     | V     | Driven by External<br>Clock Generator          |       |

| V <sub>CL</sub>     | Clock Input Low<br>Voltage                       | 3.0V     | V <sub>SS</sub> 0.3  | 0.2 V <sub>CC</sub>  | V <sub>SS</sub> –0.3 | 0.2 V <sub>CC</sub>  | 0.8     | V     | Driven by External<br>Clock Generator          |       |

|                     |                                                  | 5.5V     | V <sub>SS</sub> –0.3 | 0.2 V <sub>CC</sub>  | V <sub>SS</sub> –0.3 | 0.2 V <sub>CC</sub>  | 1.7     | V     | Driven by External<br>Clock Generator          |       |

| V <sub>IH</sub>     | Input High Voltage                               | 3.0V     | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | $0.7 V_{CC}$         | V <sub>CC</sub> +0.3 | 1.8     | V     |                                                | 1     |

|                     |                                                  | 5.5V     | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 2.8     | V     |                                                | 1     |

| V <sub>IL</sub>     | Input Low Voltage                                | 3.0V     | V <sub>SS</sub> -0.3 | 0.2 V <sub>CC</sub>  | V <sub>SS</sub> -0.3 | $0.2 V_{CC}$         | 0.8     | V     |                                                | 1     |

|                     |                                                  | 5.5V     | V <sub>SS</sub> -0.3 | $0.2 V_{CC}$         | V <sub>SS</sub> -0.3 | $0.2  V_{CC}$        | 1.5     | V     |                                                | 1     |

| V <sub>oh</sub>     | Output High Voltage                              |          | V <sub>CC</sub> -0.4 |                      | V <sub>CC</sub> -0.4 |                      | 3.0     | V     | I <sub>OH</sub> = -2.0 mA                      | 5     |

|                     |                                                  | 5.5V     | V <sub>CC</sub> -0.4 |                      | V <sub>CC</sub> -0.4 |                      | 4.8     | V     | I <sub>OH</sub> = -2.0 mA                      | 5     |

|                     |                                                  | 3.0V     | V <sub>CC</sub> -0.4 |                      | V <sub>CC</sub> 0.4  |                      | 3.0     | V     | Low Noise @<br>I <sub>OH</sub> = -0.5 mA       | 6     |

|                     |                                                  | 5.5V     | V <sub>CC</sub> -0.4 |                      | V <sub>CC</sub> -0.4 |                      | 4.8     | V     | Low Noise @<br>I <sub>OH</sub> = -0.5 mA       | 6     |

| V <sub>OL1</sub>    | Output Low Voltage                               | 3.0V     |                      | 0.8                  |                      | 0.8                  | 0.2     | V     | l <sub>OL</sub> = +4.0 mA                      | 5     |

| 021                 |                                                  | 5.5V     |                      | 0.4                  |                      | 0.4                  | 0.1     | V     | l <sub>OL</sub> = +4.0 mA                      | 5     |

|                     |                                                  | 3.0V     |                      | 0.4                  |                      | 0.4                  | 0.2     | V     | Low Noise @<br>I <sub>OL</sub> = 1.0 mA        | 6     |

|                     |                                                  | 5.5V     |                      | 0.4                  |                      | 0.4                  | 0.1     | V     | Low Noise @<br>I <sub>OL</sub> = 1.0 mA        | 6     |

| V <sub>OL2</sub>    | Output Low Voltage                               | 3.0V     |                      | 1.0                  |                      | 1.0                  | 0.8     | V     | l <sub>oL</sub> = +12 mA                       | 5     |

| 011                 |                                                  | 5.5V     |                      | 0.8                  |                      | 0.8                  | 0.3     | V     | l <sub>OL</sub> = +12 mA                       | 5     |

| V <sub>offset</sub> | Comparator Input                                 | 3.0V     |                      | 25                   |                      | 25                   | 10      | mV    | · · · · ·                                      |       |

|                     | Offset Voltage                                   | 5.5V     |                      | 25                   |                      | 25                   | 10      | mV    |                                                |       |

| V <sub>LV</sub>     | V <sub>CC</sub> Low Voltage<br>Auto Reset        |          | 2.0                  | 2.8                  |                      |                      | 2.6     | V     | Int. CLK Freq @<br>6 MHz Max.                  |       |

|                     |                                                  |          |                      |                      | 1.8                  | 3.0                  | 2.6     | V     | Int. CLK Freq @<br>4 MHz Max.                  |       |

| l <sub>iL</sub>     | Input Leakage                                    | 3.0V     | -1.0                 | 1.0                  | -1.0                 | 1.0                  |         | -     | $V_{IN} = 0V, V_{CC}$                          |       |

|                     | (Input Bias Current of Comparator)               | 5.5V     | -1.0                 | 1.0                  | -1.0                 | 1.0                  |         | -     | $V_{IN} = 0V, V_{CC}$                          |       |

| I <sub>OL</sub>     | Output Leakage                                   | 3.0V     | -1.0                 | 1.0                  | -1.0                 | 1.0                  |         |       | $V_{IN} = 0V, V_{CC}$                          |       |

|                     |                                                  | 5.5V     | -1.0                 | 1.0                  | -1.0                 | 1.0                  |         |       | $V_{IN} = 0V, V_{CC}$                          |       |

| V <sub>VICR</sub>   | Comparator Input<br>Common Mode<br>Voltage Range |          | 0                    | V <sub>CC</sub> -1.0 | 0                    | V <sub>CC</sub> –1.5 |         | V     |                                                |       |

| l<br>cc             | Supply Current                                   | 3.0V     |                      | 3.5                  |                      | 3.5                  | 1.5     | mA    | All Output and I/O<br>Pins Floating @<br>2 MHz | 5,7   |

|                     |                                                  | 5.5V     |                      | 7.0                  |                      | 7.0                  | 3.8     | mA    | All Output and I/O<br>Pins Floating @<br>2 MHz | 5,7   |

## DC ELECTRICAL CHARACTERISTICS (Continued)

|                  |                               |                 | ••  | 0°C to<br>0°C |     | 0°C to<br>5°C | Typical |       |                                                            |       |

|------------------|-------------------------------|-----------------|-----|---------------|-----|---------------|---------|-------|------------------------------------------------------------|-------|

| Symbol           | Parameter                     | V <sub>cc</sub> | Min | Max           | Min | Max           | @ 25°C  | Units | Conditions                                                 | Notes |

| I <sub>cc</sub>  | Supply Current                | 3.0V            |     | 8.0           |     | 8.0           | 3.0     | mA    | All Output and I/O<br>Pins Floating @<br>8 MHz             | 5,7   |

|                  |                               | 5.5V            |     | 11.0          |     | 11.0          | 4.4     | mA    | All Output and I/O<br>Pins Floating @<br>8 MHz             | 5,7   |

|                  |                               | 3.0V            |     | 10            |     | 10            | 3.6     | mA    | All Output and I/O<br>Pins Floating @<br>12 MHz            | 5,7   |

|                  |                               | 5.5V            |     | 15            |     | 15            | 9.0     | mA    | All Output and I/O<br>Pins Floating @<br>12 MHz            | 5,7   |

| I <sub>CC1</sub> | Standby Current               | 3.0V            |     | 2.5           |     | 2.5           | 0.7     | mA    | HALT Mode $V_{IN} = 0V$ ,<br>$V_{cc} @ 2 MHz$              | 5,7   |

|                  |                               | 5.5V            |     | 4.0           |     | 4.0           | 2.5     | mA    | HALT Mode $V_{IN} = 0V$ ,<br>$V_{cc} @ 2 MHz$              | 5,7   |

|                  |                               | 3.0V            |     | 4.0           |     | 4.0           | 1.0     | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>cc</sub> @ 8 MHz | 5,7   |

|                  |                               | 5.5V            |     | 5.0           |     | 5.0           | 3.0     | mA    | HALT Mode $V_{IN} = 0V$ ,<br>$V_{cc} @ 8 MHz$              | 5,7   |

|                  |                               | 3.0V            |     | 4.5           |     | 4.5           | 1.5     | mΑ    | HALT Mode $V_{IN} = 0V$ ,<br>$V_{cc} @ 12 \text{ MHz}$     | 5,7   |

|                  |                               | 5.5V            |     | 7.0           |     | 7.0           | 4.0     | mA    | HALT Mode $V_{IN} = 0V$ ,<br>$V_{cc} @ 12 MHz$             | 5,7   |

| I <sub>cc</sub>  | Supply Current<br>(Low Noise) | 3.0V            |     | 3.5           |     | 3.5           | 1.5     | mA    | All Output and I/O<br>Pins Floating @<br>1 MHz             | 7     |

|                  |                               | 5.5V            |     | 7.0           |     | 7.0           | 3.8     | mA    | All Output and I/O<br>Pins Floating @<br>1 MHz             | 7     |

|                  |                               | 3.0V            |     | 5.8           |     | 5.8           | 2.5     | mA    | All Output and I/O<br>Pins Floating @<br>2 MHz             | 7     |

|                  |                               | 5.5V            |     | 9.0           |     | 9.0           | 4.0     | mA    | All Output and I/O<br>Pins Floating @<br>2 MHz             | 7     |

|                  |                               | 3.0V            |     | 8.0           |     | 8.0           | 3.0     | mA    | All Output and I/O<br>Pins Floating @<br>4 MHz             | 7     |

|                  |                               | 5.5V            |     | 11.0          |     | 11.0          | 4.4     | mA    | All Output and I/O<br>Pins Floating @<br>4 MHz             | 7     |

|                  |                                     |                 | T <sub>A</sub> = 0<br>+70 |     | T <sub>A</sub> = -40<br>+10 |      | Typical |       |                                                             |       |

|------------------|-------------------------------------|-----------------|---------------------------|-----|-----------------------------|------|---------|-------|-------------------------------------------------------------|-------|

| Symbol           | Parameter                           | V <sub>cc</sub> | Min                       | Max | Min                         | Max  | @ 25°C  | Units | Conditions                                                  | Notes |

| I <sub>CC1</sub> | Standby Current<br>(Low Noise Mode) | 3.0V            |                           | 2.5 |                             | 2.5  | 0.7     | mA    | HALT Mode $V_{IN} = 0V$ ,<br>$V_{cc} @ 2 MHz$               | 5,7   |

|                  |                                     | 5.5V            |                           | 4.0 |                             | 4.0  | 2.5     | mA    | HALT Mode $V_{IN} = 0V$ ,<br>$V_{cc} @ 2 MHz$               | 5,7   |

|                  |                                     | 3.0V            |                           | 3.5 |                             | 5.0  | 0.9     | mA    | HALT Mode $V_{IN} = 0V$ ,<br>$V_{cc} @ 4 MHz$               | 5,7   |

|                  |                                     | 5.5V            |                           | 5.0 |                             | 5.0  | 2.8     | mA    | HALT Mode $V_{IN} = 0V$ ,<br>$V_{cc} @ 4MHz$                | 5,7   |

| I <sub>CC2</sub> | Standby Current                     | 3.0V            |                           | 10  |                             | 20   | 1.0     | μA    | STOP Mode V <sub>IN</sub> =<br>0V,Vcc WDT is not<br>Running | 7     |

|                  |                                     | 5.5V            |                           | 10  |                             | 20   | 1.0     | μA    | STOP Mode V <sub>IN</sub> =<br>0V,Vcc WDT is not<br>Running | 7     |

|                  | Auto Latch Low                      | 3.0V            |                           | 12  |                             | 8.0  | 3.0     | μA    | $0V < V_{IN} < V_{cc}$                                      |       |

|                  | Current                             | 5.5V            |                           | 30  |                             | 32   | 16      | μA    | $0V < V_{IN} < V_{cc}$                                      |       |

|                  | Auto Latch High                     | 3.0V            |                           | -8  |                             | -5.0 | -1.5    | μA    | $0V < V_{IN} < V_{cc}$                                      |       |

|                  | Current                             | 5.5V            |                           | -16 |                             | -20  | -8.0    | μA    | $0V < V_{IN} < V_{cc}$                                      |       |

#### Notes:

1. Port 0, 2, and 3 only

2.  $V_{SS} = 0V = GND$

The device operates down to V<sub>LV</sub>. The minimum operational V<sub>CC</sub> is determined on the value of the voltage V<sub>LV</sub> at the ambient temperature. The V<sub>LV</sub> increases as the temperature decreases.

4.  $V_{CC}$  = 3.0V to 5.5V, typical values measured at  $V_{CC}$  = 3.3V and  $V_{CC}$  = 5.0V.

5. Standard Mode (not Low EMI Mode).

6. Z86C08 only

7. Inputs at power rail and outputs are unloaded.

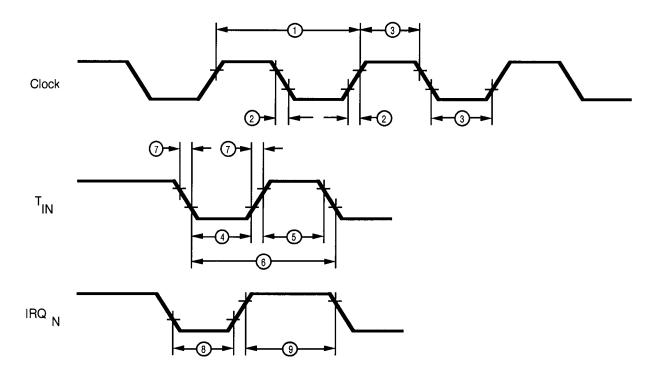

Figure 5. AC Electrical Timing Diagram

## **AC ELECTRICAL CHARACTERISTICS**

Timing Table (Standard Mode for SCLK/TCLK = XTAL/2)

|    |         |                              |          |      | $T_{A} = -400$ | to +125C |     |       |       |

|----|---------|------------------------------|----------|------|----------------|----------|-----|-------|-------|

|    |         |                              |          | 8 N  | ſHz            | 12 N     | /Hz |       |       |

| No | Symbol  | Parameter                    | $v_{cc}$ | Min  | Max            | Min      | Мах | Units | Notes |

| 1  | ТрС     | Input Clock Period           | 3.0V     | 125  | DC             | 83       | DC  | ns    | 1     |

|    |         |                              | 5.5V     | 125  | DC             | 83       | DC  | ns    | 1     |

| 2  | TrC,TfC | Clock Input Rise             | 3.0V     |      | 25             |          | 15  | ns    | 1     |

|    |         | and Fall Times               | 5.5V     |      | 25             |          | 15  | ns    | 1     |

| 3  | TwC     | Input Clock Width            | 3.0V     |      | 62             |          | 41  | ns    | 1     |

|    |         |                              | 5.5V     |      | 62             |          | 41  | ns    | 1     |

| 4  | TwTinL  | Timer Input Low Width        | 3.0V     | 100  |                | 100      |     | ns    | 1     |

|    |         |                              | 5.5V     | 70   |                | 70       |     | ns    | 1     |

| 5  | TwTinH  | Timer Input High Width       | 3.0V     | 5TpC |                | 5TpC     |     |       | 1     |

|    |         |                              | 5.5V     | 5TpC |                | 5TpC     |     |       | 1     |

| 6  | TpTin   | Timer Input Period           | 3.0V     | 8TpC |                | 8TpC     |     |       | 1     |

|    |         |                              | 5.5V     | 8TpC |                | 8TpC     |     |       | 1     |

| 7  | TrTin,  | Timer Input Rise             | 3.0V     |      | 100            |          | 100 | ns    | 1     |

|    | TtTin   | and Fall Time                | 5.5V     |      | 100            |          | 100 | ns    | 1     |

| 8  | TwiL    | Int. Request Input           | 3.0V     | 100  |                | 100      |     | ns    | 1,2   |

|    |         | Low Time                     | 5.5V     | 70   |                | 70       |     | ns    | 1,2   |

| 9  | TwlH    | Int. Request Input           | 3.0V     | 5TpC |                | 5TpC     |     |       | 1     |

|    |         | High Time                    | 5.5V     | 5TpC |                | 5TpC     |     |       | 1,2   |

| 10 | Twdt    | Watch-Dog Timer              | 3.0V     | 25   |                | 25       |     | ms    |       |

|    |         | Delay Time Before<br>Timeout | 5.5V     | 8    |                | 8        |     | ms    |       |

| 11 | Tpor    | Power-On Reset Time          | 3.0V     | 50   | 180            | 50       | 180 | ms    | 3     |

|    |         |                              | 5.5V     | 18   | 100            | 18       | 100 | ms    | 3     |

|    |         |                              | 3.0V     | 4    | 30             | 4        | 30  | ms    | 4     |

|    |         |                              | 5.5V     | 2    | 15             | 2        | 15  | ms    | 4     |

Notes:

1. Timing Reference uses 0.7  $V_{cc}$  for a logic 1 and 0.2  $V_{cc}$  for a logic 0. 2. Interrupt request through Port 3 (P33-P31).

3. Z86C08

4. Z86C04

# **AC ELECTRICAL CHARACTERISTICS**

Low Noise Mode (SCLK/TCLK = XTAL)

|    |         |                           |          | T <sub>A</sub> : | =40°C | to +125°C | >   |       |       |

|----|---------|---------------------------|----------|------------------|-------|-----------|-----|-------|-------|

|    |         |                           |          | 1 M              | Hz    | 2 M       | Hz  |       |       |

| No | Symbol  | Parameter                 | $v_{cc}$ | Min              | Max   | Min       | Max | Units | Notes |

| 1  | ТрС     | Input Clock Period        | 3.0V     | 1000             | DC    | 500       | DC  | ns    | 1     |

|    |         |                           | 5.5V     | 1000             | DC    | 500       | DC  | ns    | 1     |

| 2  | TrC,TfC | Clock Input Rise          | 3.0V     |                  | 25    |           | 25  | ns    | 1     |

|    |         | and Fall Times            | 5.5V     |                  | 25    |           | 25  | ns    | 1     |

| 3  | TwC     | Input Clock Width         | 3.0V     | 500              |       | 250       |     | ns    | 1     |

|    |         |                           | 5.5V     | 500              |       | 250       |     | ns    | 1     |

| 4  | TwTinL  | Timer Input Low Width     | 3.0V     | 100              |       | 100       |     | ns    | 1     |

|    |         |                           | 5.5V     | 70               |       | 70        |     | ns    | 1     |

| 5  | TwTinH  | Timer Input High Width    | 3.0V     | 2.5TpC           |       | 2.5TpC    |     | 1     | 1     |

|    |         |                           | 5.5V     | 2.5TpC           |       | 2.5TpC    |     |       | 1     |

| 6  | TpTin   | Timer Input Period        | 3.0V     | 4TpC             |       | 4TpC      |     |       | 1     |

|    |         |                           | 5.5V     | 4TpC             |       | 4TpC      |     |       | 1     |

| 7  | TrTin,  | Timer Input Rise          | 3.0V     |                  | 100   |           | 100 | ns    | 1     |

|    | TtTin   | and Fall Time             | 5.5V     |                  | 100   |           | 100 | ns    | 1     |

| 8  | TwiL    | Int. Request Input        | 3.0V     | 100              |       | 100       |     | ns    | 1,2   |

|    |         | Low Time                  | 5.5V     | 70               |       | 70        |     | ns    | 1,2   |

| 9  | TwlH    | Int. Request Input        | 3.0V     | 2.5TpC           |       | 2.5TpC    |     |       | 1     |

|    |         | High Time                 | 5.5V     | 2.5TpC           |       | 2.5TpC    |     |       | 1,2   |

| 10 | Twdt    | Watch-Dog Timer           | 3.0V     | 25               |       | 25        |     | ms    | 3     |

|    |         | Delay Time Before Timeout | 5.5V     | 8                |       | 8         |     | ms    | 3     |

#### Notes:

Timing Reference uses 0.7 V<sub>cc</sub> for a logic 1 and 0.2 V<sub>cc</sub> for a logic 0.

Interrupt request through Port 3 (P33-P31).

Internal RC Oscillator driving WDT.

# AC ELECTRICAL CHARACTERISTICS (Continued)

|    |         |                        |                 | Τ,     | ∖= 0°C | to 70°C |     | <b>T</b> <sub>A</sub> = · | -40°C | c to +10 | 5°C |       |       |

|----|---------|------------------------|-----------------|--------|--------|---------|-----|---------------------------|-------|----------|-----|-------|-------|

|    |         |                        |                 | 1 MI   | Ηz     | 4 Mł    | ١z  | 1 M                       | Hz    | 4 M      | Hz  |       |       |

| No | Symbol  | Parameter              | V <sub>cc</sub> | Min    | Max    | Min     | Max | Min                       | Max   | Min      | Max | Units | Notes |

| 1  | ТрС     | Input Clock Period     | 3.0V            | 1000   | DC     | 250     | DC  | 1000                      | DC    | 250      | DC  | ns    | 1     |

|    |         |                        | 5.5V            | 1000   | DC     | 250     | DC  | 1000                      | DC    | 250      | DC  | ns    | 1     |

| 2  | TrC,TfC | Clock Input Rise       | 3.0V            |        | 25     |         | 25  |                           | 25    |          | 25  | ns    | 1     |

|    |         | and Fall Times         | 5.5V            |        | 25     |         | 25  |                           | 25    |          | 25  | ns    | 1     |

| 3  | TwC     | Input Clock Width      | 3.0V            | 500    |        | 125     |     | 500                       |       | 125      |     | ns    | 1     |

|    |         |                        | 5.5V            | 500    |        | 125     |     | 500                       |       | 125      |     | ns    | 1     |

| 4  | TwTinL  | Timer Input Low Width  | 3.0V            | 100    |        | 100     |     | 100                       |       | 100      |     | ns    | 1     |

|    |         |                        | 5.5V            | 70     |        | 70      |     | 70                        |       | 70       |     | ns    | 1     |

| 5  | TwTinH  | Timer Input High Width | 3.0V            | 2.5TpC |        | 2.5TpC  |     | 2.5TpC                    |       | 2.5TpC   |     |       | 1     |

|    |         |                        | 5.5V            | 2.5TpC |        | 2.5TpC  |     | 2.5TpC                    |       | 2.5TpC   |     |       | 1     |

| 6  | TpTin   | Timer Input Period     | 3.0V            | 4TpC   |        | 4TpC    |     | 4TpC                      |       | 4TpC     |     |       | 1     |

|    |         |                        | 5.5V            | 4TpC   |        | 4TpC    |     | 4TpC                      |       | 4TpC     |     |       | 1     |

| 7  | TrTin,  | Timer Input Rise       | 3.0V            |        | 100    |         | 100 |                           | 100   |          | 100 | ns    | 1     |

|    | TtTin   | and Fall Timer         | 5.5V            |        | 100    |         | 100 |                           | 100   |          | 100 | ns    | 1     |

| 8  | TwiL    | Int. Request Input     | 3.0V            | 100    |        | 100     |     | 100                       |       | 100      |     | ns    | 1,2   |

|    |         | Low Time               | 5.5V            | 70     |        | 70      |     | 70                        |       | 70       |     | ns    | 1,2   |

| 9  | TwlH    | Int. Request Input     | 3.0V            | 2.5TpC |        | 2.5TpC  |     | 2.5TpC                    |       | 2.5TpC   |     |       | 1     |

|    |         | High Time              | 5.5V            | 2.5TpC |        | 2.5TpC  |     | 2.5TpC                    |       | 2.5TpC   |     |       | 1,2   |

| 10 | Twdt    | Watch-Dog Timer        | 3.0V            | 25     |        | 25      |     | 25                        |       | 25       |     | ms    | 3     |

|    |         | Delay Time Before      | 5.5V            | 10     |        | 10      |     | 8                         |       | 8        |     | ms    | 3,5   |

|    |         | Timeout                | 5.5V            | 12     |        | 12      |     | 12                        |       | 12       |     | ms    | 3,4   |

#### Notes:

Timing Reference uses 0.7 V<sub>cc</sub> for a logic 1 and 0.2 V<sub>cc</sub> for a logic 0.

Interrupt request through Port 3 (P33-P31).

Internal RC Oscillator driving WDT.

4. Z86C04

5. Z86C08

### PIN DESCRIPTION

**XTAL1, XTAL2** *Crystal In, Crystal Out* (time-based input and output, respectively). These pins connect a RC, parallel-resonant crystal, LC, or an external single-phase clock to the on-chip clock oscillator and buffer.

Auto Latch. The Auto Latch puts valid CMOS levels on all CMOS inputs (except P33, P32, P31) that are not externally driven. After Power-On Reset, this level is 0 or 1 cannot be determined. A valid CMOS level, rather than a floating

node, reduces excessive supply current flow in the input buffer. To change the Auto Latch state, the auto latches must be over driven with current greater than  $I_{ALH}$  (high to low) or  $I_{ALH}$  (low to high).

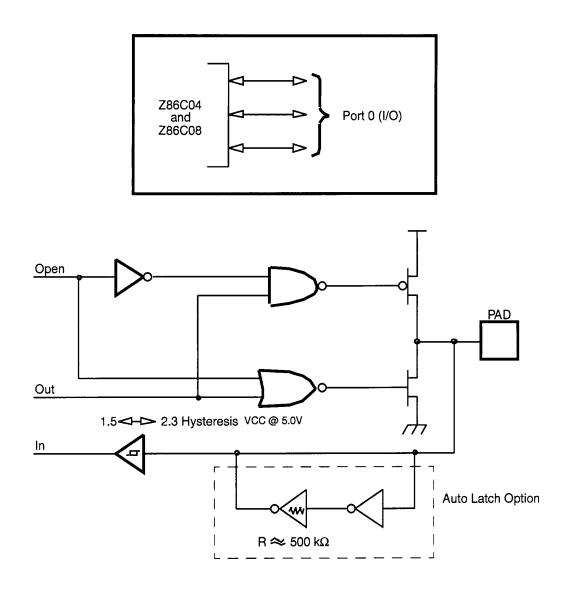

**Port 0** (P02-P00). Port 0 is a 3-bit I/O, bidirectional, Schmitt-triggered CMOS-compatible I/O port. These three I/O lines can be configured under software control to be all inputs or all outputs (Figure 6).

Figure 6. Port 0 Configuration

Zilog

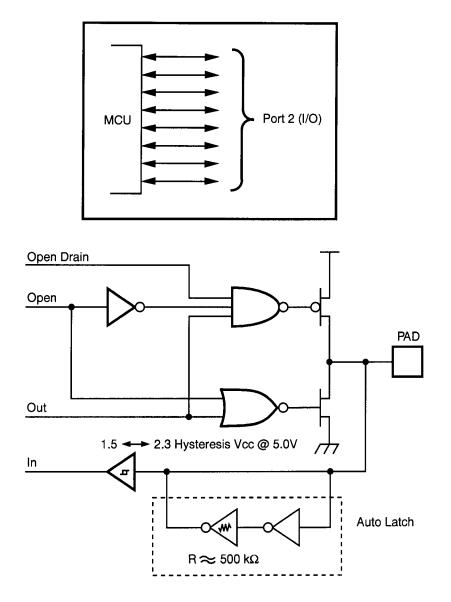

**Port 2** (P27-P20). Port 2 is an 8-bit I/O, bit-programmable, bidirectional, Schmitt-triggered CMOS-compatible I/O port. These eight I/O lines can be configured under soft-

ware control to be an input or output, independently. Bits programmed as outputs may be globally programmed as either push-pull or open-drain (Figure 7).

Figure 7. Port 2 Configuration

## **PIN DESCRIPTION** (Continued)

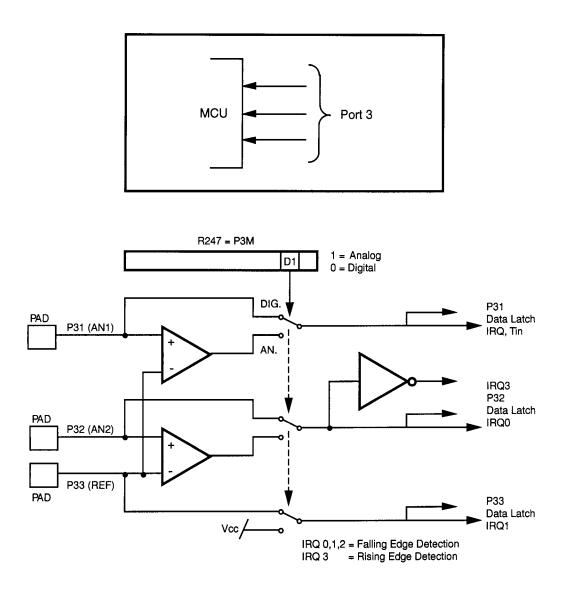

**Port 3** (P33-P31). Port 3 is a 3-bit, Schmitt-triggered CMOS-compatible port with three fixed input (P33-P31) lines. These three input lines can be configured under soft-

ware control as digital inputs or analog inputs. These three input lines can also be used as the interrupt sources IRQ0-IRQ3 and as the timer input signal  $(T_{IN})$  (Figure 8).

**Comparator Inputs.** Two analog comparators are added to Port 3 inputs for interface flexibility. Typical applications for these on-board comparators are: Zero crossing detection, A/D conversion, voltage scaling, and threshold detection.

The dual comparator (common inverting terminal) features a single power supply that discontinues power in STOP Mode. The common voltage range is 0-4V when the  $V_{cc}$  is 5.0V. Before the comparitor outputs are valid, two NOP delays are required after enabling the analog comparitors.

Interrupts are generated on either edge of Comparator 2's output, or on the falling edge of Comparator 1's output. The comparator output may be used for interrupt generation, Port 3 data inputs, or  $T_{\rm IN}$  through P31. Alternately, the comparators may be disabled, freeing the reference input (P33) for use as IRQ1 and/or P33 input.

## FUNCTIONAL DESCRIPTION

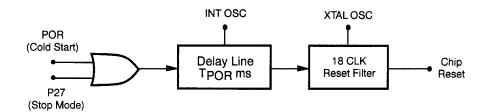

**RESET.** Upon power-up, the Power-On Reset circuit waits for  $T_{POR}$  ms, plus 18 clock cycles, and then starts program

execution at address %000C (Hex) (Figure 9). The device control registers' reset value is shown in Table 1.

### Figure 9. Internal Reset Configuration

#### Table 1. Z86C04/C08 & C05/C07 Control Registers

|            |        |    |    | Reset C | onditio | n  |    |    |    |                                          |

|------------|--------|----|----|---------|---------|----|----|----|----|------------------------------------------|

| Addr.      | Reg.   | D7 | D6 | D5      | D4      | D3 | D2 | D1 | D0 | Comments                                 |

| 03H (3)*   | Port 3 | U  | U  | U       | U       | U  | U  | U  | U  |                                          |

| 02H (2)*   | Port 2 | U  | U  | U       | U       | U  | U  | U  | U  |                                          |

| 00H (0)*   | Port 0 | U  | U  | U       | U       | U  | U  | U  | U  |                                          |

| FFH(255)   | SPL    | 0  | 0  | 0       | 0       | 0  | 0  | 0  | 0  |                                          |

| FEH (254)  | GPR    | 0  | 0  | 0       | 0       | 0  | 0  | 0  | 0  |                                          |

| FDH (253)  | RP     | 0  | 0  | 0       | 0       | 0  | 0  | 0  | 0  |                                          |

| FCH (252)  | FLAGS  | U  | U  | U       | U       | U  | U  | U  | U  |                                          |

| FBH (251)  | IMR    | 0  | U  | U       | U       | U  | U  | U  | U  |                                          |

| FAH (250)  | IRQ    | U  | U  | 0       | 0       | 0  | 0  | 0  | 0  | IRQ3 is used for positive edge detection |

| F9H (249)  | IPR    | U  | U  | U       | U       | U  | U  | U  | U  |                                          |

| F8H (248)* | P01M   | U  | U  | U       | 0       | U  | U  | 0  | 1  |                                          |

| F7H (247)* | P3M    | U  | U  | U       | U       | U  | U  | 0  | 0  |                                          |

| F6H (246)* | P2M    | 1  | 1  | 1       | 1       | 1  | 1  | 1  | 1  | Inputs after reset                       |

| F5H (245)  | PRE0   | U  | U  | U       | U       | U  | U  | U  | 0  |                                          |

| F4H (244)  | Т0     | U  | U  | U       | U       | U  | U  | U  | U  |                                          |

| F3H (243)  | PRE1   | U  | U  | U       | U       | U  | U  | 0  | 0  |                                          |

| F2H (242)  | T1     | U  | U  | U       | U       | U  | U  | U  | U  |                                          |

| F1H (241)  | TMR    | 0  | 0  | 0       | 0       | 0  | 0  | 0  | 0  |                                          |

**Note:** \*Registers are not reset after a Stop-Mode Recovery using P27 pin. A subsequent reset will cause these control registers to be re-configured as shown in Table 1 and the user must avoid bus contention on the port pins or it may affect device reliability.

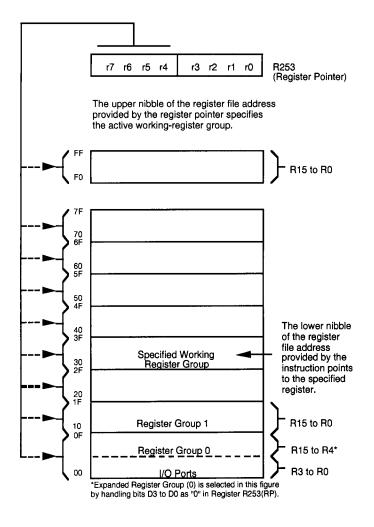

The Z8 instructions can access registers directly or indirectly through an 8-bit address field. This allows short 4-bit register addressing using the Register Pointer. In the 4-bit mode, the register file is divided into eight working register groups, each occupying 16 continuous locations. The Register Pointer (Figure 12) addresses the starting location of the active working-register group. Upon power-up, the general purpose registers are undefined.

Figure 12. Register Pointer

**Stack Pointer.** The Z8 has an 8-bit Stack Pointer (R255) used for the internal stack that resides within the 124 general-purpose registers.

**General-Purpose Register (GPR).** The general-purpose register upon device power-up is undefined. The general-purpose register upon a Stop-Mode Recovery and reset stays in its last state. It may not keep its last state from a  $V_{LV}$  reset if the  $V_{cc}$  drops below 2.6V.

**Note:** Register R254 has been designated as a generalpurpose register and is set to 00H after any reset.

### FUNCTIONAL DESCRIPTION (Continued)

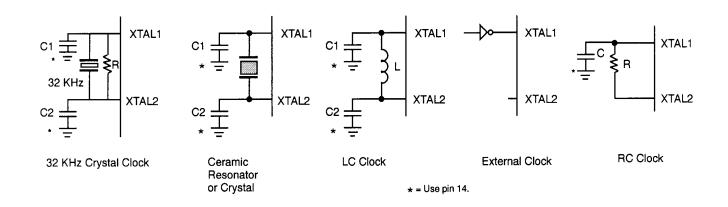

**Clock.** The on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a RC, crystal, ceramic resonator, LC, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal should be AT cut, 12 MHz max, with a series resistance (RS) less than or equal to 100 ohms.

The crystal should be connected across XTAL1 and XTAL2 using the vendor's crystal recommended capacitors (which depends on the crystal manufacturer, ceramic resonator and PCB layout) from each pin directly to device Ground pin 14 (Figure 15).

Note that the crystal capacitor loads should be connected to  $V_{ss}$  pin 14 to reduce ground noise injection.

To use 32 kHz crystal, the 32 kHz operational mask option must be selected, and an external resistor R must be connected across XTAL1 and XTAL2.To use RC oscillator, the RC oscillator option must be selected.

HALT Mode. This instruction turns off the internal CPU clock but not the crystal oscillation. The counter/timers and external interrupts IRQ0, IRQ1, IRQ2, and IRQ3 remain active. The device can be recovered by interrupts, either externally or internally generated. An interrupt request must be executed (enabled) to exit HALT Mode. After the interrupt service routine, the program continues from the instruction after the HALT.

**STOP Mode.** This instruction turns off the internal clock and external crystal oscillation and reduces the standby current. The STOP Mode can be released by two methods. The first method is a RESET of the device by removing  $V_{CC}$  or dropping the  $V_{CC}$  below  $V_{LV}$ . The second method is if P27 is at a low level when the device executes the STOP instruction. A low condition on P27 releases the STOP Mode regardless if configured for input or output.

Program execution under both conditions begins at location 000C (Hex). However, when P27 is used to release the STOP Mode, the I/O port mode registers are not reconfigured to their default power-on conditions. This prevents any I/O, configured as output when the STOP instruction was executed, from glitching to an unknown state. To use the P27 release approach with STOP Mode, use the following instruction:

| LD   | P2M, #1XXX XXXXB |

|------|------------------|

| NOP  |                  |

| STOP |                  |

Note: (X = dependent upon user's application.)

In order to enter STOP or HALT Mode, it is necessary to first flush the instruction pipeline to avoid suspending execution in mid-instruction. To do this, the user must execute a NOP (opcode = FFH) immediately before the appropriate sleep instruction, that is, as follows:

| FF | NOP  |    | ; clear the pipeline |

|----|------|----|----------------------|

| 6F | STOP |    | ; enter STOP Mode    |

|    |      | or |                      |

| FF | NOP  |    | ; clear the pipeline |

| 7F | HALT |    | ; enter HALT Mode    |

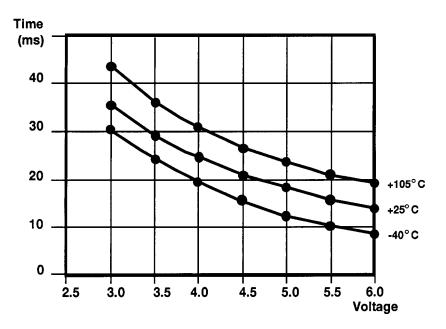

**Watch-Dog Timer (WDT).** The Watch-Dog Timer is enabled by instruction WDT. When the WDT is enabled, it cannot be stopped by the instruction. With the WDT instruction, the WDT should be refreshed once the WDT is enabled within every Twdt period; otherwise, the Z8 resets itself. The WDT instruction affects the Flags accordingly: Z = 1, S = 0, V = 0.

WDT = 5F (Hex)

Figure 15. Oscillator Configuration

**Opcode WDT** (5FH). The first time Opcode 5FH is executed, the WDT is enabled, and subsequent execution clears the WDT counter. This has to be done within the maximum  $T_{WDT}$  period; otherwise, the WDT times out and generates a Reset. The generated Reset is the same as a Power-On Reset of  $T_{POR}$  plus 18 XTAL clock cycles. The WDT does not work (run) in STOP Mode. The WDT is disabled during and after a Reset, until the WDT is enabled again.

**Opcode WDH** (4FH). When this instruction is executed it will enable the WDT during HALT. If not, the WDT will stop when entering HALT. This instruction does not clear the counters, it facilitates running the WDT function during HALT Mode. A WDH instruction executed without executing WDT (5FH) has no effect.

**Permanent WDT Mask Option.** Only when the Permanent WDT Mask Option is selected, then the WDT is hardwired to be enabled after reset. The WDT will operate in Run Mode, HALT Mode, and STOP Mode. The Opcode 5FH is used to refresh or clear the WDT counter. The WDT instruction (4FH) has no effect The WDT will not run in STOP Mode if the system clock driving the WDT is selected (Z86C04 only).

### System Clock Driving WDT Mask Option (Z86C04 only)

When this option is selected, the Z8's system clock drives the WDT instead of the on-board RC oscillator driving the WDT. The WDT time-out will be SCLK x 32,512. The WDT will not run in STOP Mode.

| Low-Voltage Protection (V <sub>LV</sub> ). Maximum (V <sub>LV</sub> ) |                                                |  |

|-----------------------------------------------------------------------|------------------------------------------------|--|

|                                                                       | Conditions:                                    |  |

| Case 1:                                                               | T <sub>A</sub> = -40°C, +85°C, Internal Clock  |  |

|                                                                       | Frequency equal or less than 6 MHz             |  |

| Case 2:                                                               | T <sub>A</sub> = -40°C, +105°C, Internal Clock |  |

|                                                                       | Frequency equal or less than 4 MHz             |  |

**Note:** The internal clock frequency is one-half the external clock frequency in standard mode.

The device will function normally at or above 3.0V under all conditions. Below 3.0V, the device functions normally until the Low-Voltage Protection trip point  $(V_{LV})$  is reached. The device is guaranteed to function normally at supply voltages above the low voltage trip point for the temperatures and operating frequencies in Cases 1 and 2. The actual low voltage trip point is a function of temperature and process parameters (Figure 16).

| 1 MHz (Typical) |       |      |       |       |        |        |

|-----------------|-------|------|-------|-------|--------|--------|

| Temp            | -40C° | 0°C  | +25°C | +70°C | +105°C | +125°C |

| $V_{LV}$        | 3.0   | 2.75 | 2.6   | 2.3   | 2.1    | 1.9    |

**ROM Protect.** ROM Protect fully protects the Z86C04/C08 ROM code from being read internally. When ROM Protect is selected, ROM look-up tables can be used in this mode.

Figure 16. Typical Z86C04/C08  $V_{LV}$  vs. Temperature

# **DEVICE CHARACTERISTICS**

Standard Mode

Figure 31.  $V_{\mu}$ ,  $V_{oL}$  vs. Temperature

# **Z8 CONTROL REGISTER DIAGRAMS** (Continued)

Figure 34. Typical WDT Time Out Period vs.  $\rm V_{cc}$  Over Temperature

### **ORDERING INFORMATION**

| Z860<br>(12 M<br>Standard Te | Hz)         | Z86C08<br>(12 MHz)<br>Standard Temperature |             |  |

|------------------------------|-------------|--------------------------------------------|-------------|--|

| 18-Pin DIP                   | 18-Pin SOIC | 18-Pin DIP                                 | 18-Pin SOIC |  |

| Z86C0412PSC                  | Z86C0412SSC | Z86C0812PSC                                | Z86C0812SSC |  |

| Extended Temperature         |             | Extended Temperature                       |             |  |

| 18-Pin DIP                   | 18-Pin SOIC | 18-Pin DIP                                 | 18-Pin SOIC |  |

| Z86C0412PEC                  | Z86C0412SEC | Z86C0812PEC                                | Z86C0812SEC |  |

| Z86C0412PAC                  | Z86C0412SAC | Z86C0812PAC                                | Z86C0812SAC |  |

For fast results, contact your local Zilog sale offices for assistance in ordering the part(s) desired.

### CODES

Preferred Package P = DIP S = SOIC

### Preferred Temperature

$S = 0^{\circ}C \text{ to } +70^{\circ}C$

Longer Lead Time  $E = -40^{\circ}C$  to  $+105^{\circ}C$  $A = -40^{\circ}C$  to  $+125^{\circ}C$

**Speeds** 12 = 12 MHz

Environmental C = Plastic Standard

Example:

Z 86C04 12 P S C

is a Z86C04, 12 MHz, DIP, 0°C to +70°C, Plastic Standard Flow