Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Obsolete                                                   |

| Core Processor             | Z8                                                         |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 8MHz                                                       |

| Connectivity               | -                                                          |

| Peripherals                | POR, WDT                                                   |

| Number of I/O              | 14                                                         |

| Program Memory Size        | 512B (512 x 8)                                             |

| Program Memory Type        | OTP                                                        |

| EEPROM Size                | -                                                          |

| RAM Size                   | 61 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                             |

| Supplier Device Package    | -                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e0208hec1925 |

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact:

#### **ZiLOG Worldwide Headquarters**

532 Race Street San Jose, CA 95126 Telephone: 408.558.8500

Fax: 408.558.8300 www.ZiLOG.com

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated.

#### **Document Disclaimer**

©2003 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

## Table of Contents

| Architectural Overview                                  |     |

|---------------------------------------------------------|-----|

| Z86E02 SL1925 Features                                  | 1   |

| Electrical Characteristics                              | 8   |

| Absolute Maximum Ratings                                |     |

| Standard Test Conditions                                | 9   |

| Capacitance                                             | 9   |

| DC Electrical Characteristics                           | 9   |

| Standard Temperature Range                              | 9   |

| Extended Temperature Range                              | 12  |

| AC Electrical Timing Characteristics                    | 16  |

| STANDARD Mode at Standard Temperature                   |     |

| LOW EMI Mode at Extended Temperature                    |     |

| Low-EMI Mode                                            | 21  |

| Software Work Around on the Z86CCP01ZEM Emulator        |     |

| to Emulate Low EMI Mode                                 | 21  |

| Pin Functions                                           | 22  |

| EPROM Mode                                              | 22  |

| Pin Function Changes in EPROM Mode                      | 22  |

| Application Precaution                                  | 22  |

| STANDARD Mode                                           | 23  |

| Hardware Work Around on the on the Z86CCP01ZEM Emulator |     |

| to P32 Rising Edge Digital Interrupt                    | 27  |

| Hardware Work Around on the on the Z86CCP01ZEM Emulator |     |

| to P32 Rising Edge Analog Interrupt                     | 27  |

| Functional Description                                  |     |

| RESET                                                   | 28  |

| Program Memory                                          | 30  |

| Register File                                           | 30  |

| Stack Pointer                                           |     |

| Counter/Timer                                           |     |

| Interrupts                                              |     |

| Hardware Work Around on the on the Z86CCP01ZEM Emulator |     |

| to P32 Rising Edge Digital Interrupt                    | 34  |

| Hardware Work Around on the on the Z86CCP01ZEM Emulator | 0.4 |

| to P32 Rising Edge Analog Interrupt                     |     |

| Clock                                                   |     |

| HALT Mode                                               |     |

| STOP Mode                                               | 37  |

#### Z86E02 SL 1925 | General-Purpose OTP MCU with 14 I/O Lines

| Software Work Around on the 286CCP012EM Emulator |    |

|--------------------------------------------------|----|

| to Enable P27 as Stop-Mode Recovery Source       | 38 |

| Watch-Dog Timer (WDT)                            | 38 |

| Software Work Around on the Z86CCP01ZEM Emulator |    |

| to Emulate the Software WDT Running in HALT Mode | 39 |

| Software Work Around on the Z86CCP01ZEM Emulator |    |

| to Emulate the Hardware Enabled Permanent WDT    |    |

| in HALT Mode and Stop Mode                       |    |

| Auto Reset Voltage (V <sub>LV</sub> )            |    |

| OTP Option Bit Description                       |    |

| Control Registers                                | 43 |

| Package Information                              | 51 |

| Ordering Information                             | 52 |

| Part Number Description                          | 53 |

| Document Information                             | 53 |

| Document Number Description                      | 53 |

| Customer Feedback Form                           | 54 |

| Z86E02 SL1925 Product Specification              | 54 |

| Customer Information                             | 54 |

| Product Information                              | 54 |

| Return Information                               | 54 |

| Problem Description or Suggestion                | 54 |

## List of Tables

| Table 1. Z86E02 SL1925 Features                                            |

|----------------------------------------------------------------------------|

| Table 2. 18-Pin DIP/SOIC Pin Identification, STANDARD Mode                 |

| Table 3. 18-Pin DIP/SOIC Pin Identification, EPROM Mode                    |

| Table 4. 20-Pin SSOP Pin Identification, STANDARD Mode                     |

| Table 5. 20-Pin SSOP Pin Identification, EPROM Mode                        |

| Table 6. Absolute Maximum Ratings                                          |

| Table 7. Capacitance                                                       |

| Table 8. DC Characteristics, Standard Temperature Range 10                 |

| Table 9. DC Characteristics, Extended Temperature Range                    |

| Table 10. AC Electrical Characteristics, Standard Mode and Temperature 10  |

| Table 11. AC Electrical Timing, Standard Mode at Extended Temperature 18   |

| Table 12. AC Electrical Timing, Standard Mode at Extended Temperature 19   |

| Table 13. AC Electrical Timing, Low EMI Mode at Extended Temperature 20    |

| Table 14. Z8 <sup>®</sup> Control Registers Reset Values*                  |

| Table 15. Interrupt Types, Sources, and Vectors                            |

| Table 16. Typical Frequency (MHz) vs. RC Values $V_{CC}$ = 5.0 V @ 25°C 30 |

| Table 17. Timer Mode Register, R241 TMR F1h Bank 0h: READ/WRITE 4          |

| Table 18. Counter/Timer 1 Register, R242 T1 F2h Bank 0h: READ/WRITE 4      |

| Table 19. Prescaler 1 Register, R243 PRE1 F3h Bank 0h: WRITE ONLY 4        |

| Table 20. Port 2 Mode Register, R246 P2M F6h Bank 0h: WRITE ONLY 4         |

| Table 21. Port 3 Mode Register, R247 P3M F7h Bank 0h: WRITE ONLY 4         |

| Table 22. Port 0 and 1 Mode Register, R248 P01 F8h Bank 0h: WRITE ONLY 4   |

| Table 23. Interrupt Priority Register, R249 IPR F9h Bank 0h: WRITE ONLY 4  |

| Table 24. Interrupt Request Register, R250 IPR FAh Bank 0h: READ/WRITE 4   |

| Table 25. Interrupt Mask Register, R251 IMR FBh Bank 0h: READ/WRITE 4      |

| Table 26. Flag Register, R252 FCh Bank 0h: READ/WRITE                      |

| Table 27. Register Pointer, R253 RP FDh Bank 0h: READ/WRITE 4              |

| Table 28. General-Purpose Register, R254 GPR FEh Bank 0h: READ/WRITE 49    |

| Table 29. Stack Pointer Low, R255 SPL FFh Bank 0h: READ/WRITE 50           |

| Table 30. Ordering Information                                             |

#### **PIN DESCRIPTION**

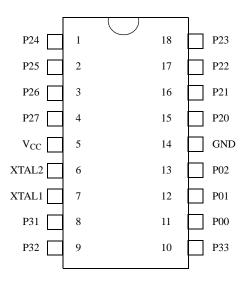

Pin diagrams and identification for the device are displayed in Figure 3 through Figure 6, and in Table 2 through Table 5.

Figure 3. 18-Pin DIP/SOIC Configuration, STANDARD Mode

Table 2. 18-Pin DIP/SOIC Pin Identification, STANDARD Mode

| Pin#  | Symbol          | Function                 | Direction    |

|-------|-----------------|--------------------------|--------------|

| 1-4   | P24-P27         | Port 2, Pins 4-7         | Input/Output |

| 5     | V <sub>CC</sub> | Power Supply             |              |

| 6     | XTAL2           | Crystal Oscillator Clock | Output       |

| 7     | XTAL1           | Crystal Oscillator Clock | Input        |

| 8     | P31             | Port 3, Pin 1 AN1        | Input        |

| 9     | P32             | Port 3, Pin 1 AN2        | Input        |

| 10    | P33             | Port 3, Pin 3, REF       | Input        |

| 11-13 | P00-P02         | Port 0, Pins 0-2         | Input/Output |

| 14    | GND             | Ground                   |              |

| 15-18 | P20-P23         | Port 2, Pins 0-3         | Input/Output |

Figure 5. 20-Pin SSOP Pin Configuration, STANDARD Mode

Table 4. 20-Pin SSOP Pin Identification, STANDARD Mode

| Pin#  | Symbol          | Function                 | Direction    |

|-------|-----------------|--------------------------|--------------|

| 1,2   | P24-P25         | Port 2, Pins 4-5         | Input/Output |

| 3     | P27             | Port 2, Pin 7            | Input/Output |

| 4     | P26             | Port 2, Pin 6            | Input/Output |

| 5     | V <sub>CC</sub> | Power Supply             |              |

| 6     | V <sub>CC</sub> | Power Supply             |              |

| 7     | XTAL1           | Crystal Oscillator Clock | Input        |

| 8     | XTAL2           | Crystal Oscillator Clock | Output       |

| 9     | P31             | Port 3, Pin 1, AN1       | Input        |

| 10    | P32             | Port 3, Pin 2, AN2       | Input        |

| 11    | P33             | Port 3, Pin 3, REF       | Input        |

| 12    | P00             | Port 0, Pin 0            | Input/Output |

| 13    | P02             | Port 0, Pin 1            | Input/Output |

| 14    | P01             | Port 0, Pin 1            | Input/Output |

| 15    | GND             | Ground                   |              |

| 16    | GND             | Ground                   |              |

| 17    | P21             | Port 2, Pin 1            | Input/Output |

| 18    | P20             | Port 2, Pin 0            | Input/Output |

| 19-20 | P22-P23         | Port 2, Pins 2-3         | Input/Output |

#### **Electrical Characteristics**

#### **Absolute Maximum Ratings**

Stresses greater than those listed on Table 6 may cause permanent damage to the device. This rating is a stress rating only; functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability. Total power dissipation should not exceed 462 m $\Omega$  for the package. See Table 6. Power dissipation is calculated as follows:

$$\begin{split} \text{Total Power Dissipation} = & \quad \mathsf{V_{CC}} \; \mathsf{X} \; [\mathsf{I_{CC}}\text{-}(\mathsf{sum of I_{OH}})] \\ & \quad + \mathsf{sum of} \; [(\mathsf{V_{CC}}\text{-}\mathsf{V_{OH}}) \; \mathsf{X} \; \mathsf{I_{OH}}] \\ & \quad + \mathsf{sum of} \; (\mathsf{V_{OL}} \; \mathsf{X} \; \mathsf{I_{OL}}) \end{aligned}$$

**Table 6. Absolute Maximum Ratings**

| Parameter                                                       | Min  | Max                | Units | Note |

|-----------------------------------------------------------------|------|--------------------|-------|------|

| Ambient Temperature under Bias                                  | -40  | +105               | С     |      |

| Storage Temperature                                             | -65  | +150               | С     |      |

| Voltage on any Pin with Respect to V <sub>SS</sub>              | -0.7 | +12                | V     | 1    |

| Voltage on V <sub>DD</sub> Pin with Respect to V <sub>SS</sub>  | -0.3 | +7                 | V     |      |

| Voltage on XTAL1, P31, P32, P33 with respect to V <sub>SS</sub> | -0.6 | V <sub>DD</sub> +1 | V     | 3    |

| Total Power Dissipation                                         |      | 462                | mΩ    |      |

| Maximum Allowable Current out of V <sub>SS</sub>                |      | 300                | mA    |      |

| Maximum Allowable Current into V <sub>DD</sub>                  |      | 270                | mA    |      |

| Maximum Allowable Current into an Input Pin                     | -600 | +600               | μA    | 4    |

| Maximum Allowable Current into an Open-Drain Pin                | -600 | +600               | μA    | 2    |

| Maximum Allowable Output Current Linked by any I/O Pin          |      | 20                 | mA    |      |

| Maximum Allowable Output Current Sourced by any I/O Pin         |      | 20 mA              |       |      |

- 1. Applies to all pins except where otherwise noted. Maximum current into or out of pin must be  $\pm 600 \, \mu A$ .

- 2. Device pin is not at an output Low state.

- 3. There is no input protection diode from pin to  $V_{DD}$ .

- 4. This excludes XTAL1 and XTAL2.

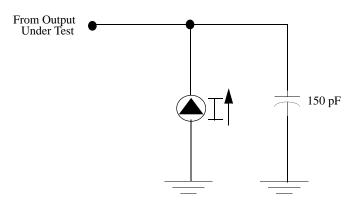

#### **Standard Test Conditions**

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to Ground. Positive current flows into the referenced pin See Figure 7.

Figure 7. Test Load Diagram

#### **Capacitance**

$\rm T_A=25^{\circ}C,\,V_{CC}=GND=OV,\,f=1.0$  MHz, unmeasured pins returned to GND. See Table 7.

Table 7. Capacitance

| Parameter          | Min | Max   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 10 pF |

| Output capacitance | 0   | 20 pF |

| I/O capacitance    | 0   | 25 pF |

#### **DC Electrical Characteristics**

#### **Standard Temperature Range**

Table 8 provides Direct Current characteristics for the Z86E02 SL1925 microcontroller, at a standard ambient temperature range of 0°C to 70°C.

Table 8. DC Characteristics, Standard Temperature Range

|                                                                        | $TA = 0^{\circ}C \text{ to } +70^{\circ}C$ |      |     |    |   |                          |   |  |  |  |  |

|------------------------------------------------------------------------|--------------------------------------------|------|-----|----|---|--------------------------|---|--|--|--|--|

| Typical @ Sym Parameter V <sub>CC</sub> Min Max 25°C¹ Units Conditions |                                            |      |     |    |   |                          |   |  |  |  |  |

| $V_{\text{INMAX}}$                                                     | Max Input Voltage                          | 3.5V | -12 | 12 | V | I <sub>IN</sub> < 250 μA | 2 |  |  |  |  |

|                                                                        |                                            | 5.5V | -12 | 12 | V | I <sub>IN</sub> < 250 μA | 2 |  |  |  |  |

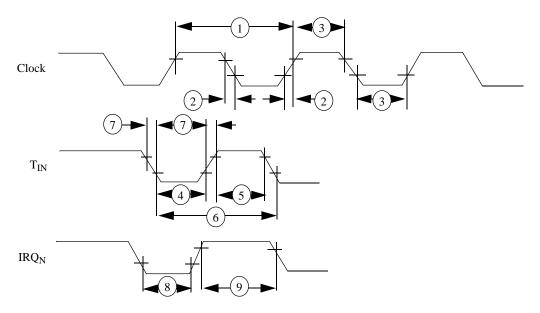

### **AC Electrical Timing Characteristics**

Figure 8 illustrates Alternating Current timing for the Z86E02 SL1925 microcontroller.

Figure 8. AC Electrical Timing

#### **STANDARD Mode at Standard Temperature**

Table 10 describes timing characteristics in STANDARD mode at standard temperature for the timing diagram noted in Figure 8.

Table 10. AC Electrical Characteristics, Standard Mode and Temperature

|    |                  |                                 | TA = 0°C to $+70$ °C |     |      |       |       |  |

|----|------------------|---------------------------------|----------------------|-----|------|-------|-------|--|

|    |                  |                                 |                      |     | 8MHz |       |       |  |

| No | Symbol           | Parameter                       | $v_{cc}$             | Min | Max  | Units | Notes |  |

| 1  | T <sub>P</sub> C | Input Clock Period              | 3.5V                 | 125 | DC   | ns    | 1     |  |

|    |                  | _                               | 5.5V                 | 125 | DC   | ns    | 1     |  |

| 2  | $T_RC,T_FC$      | Clock Input Rise and Fall Times | 3.5V                 |     | 25   | ns    | 1     |  |

|    |                  |                                 | 5.5V                 |     | 25   | ns    | 1     |  |

| 3  | T <sub>W</sub> C | Input Clock Width               | 3.5V                 | 62  |      | ns    | 1     |  |

|    |                  | _                               | 5.5V                 | 62  |      | ns    | 1     |  |

Table 10. AC Electrical Characteristics, Standard Mode and Temperature (Continued)

|                      |                                                   |                                |          | $TA = 0^{\circ}C$ | to +70°C |       |       |

|----------------------|---------------------------------------------------|--------------------------------|----------|-------------------|----------|-------|-------|

|                      |                                                   |                                |          |                   | 8MHz     |       |       |

| No                   | Symbol                                            | Parameter                      | $V_{CC}$ | Min               | Max      | Units | Notes |

| 4                    | $T_WT_{IN}L$                                      | Timer Input Low Width          | 3.5V     | 100               |          | ns    | 1     |

| 5 Tu Tu H Timor Inpu | -<br>-                                            | 5.5V                           | 70       |                   | ns       | 1     |       |

| 5                    | $T_WT_{IN}H$                                      | Timer Input High Width         | 3.5V     | 5TpC              |          |       | 1     |

|                      | T <sub>P</sub> T <sub>IN</sub> Timer Input Period | -                              | 5.5V     | 5TpC              |          |       | 1     |

| 6                    | $T_PT_{IN}$                                       | Timer Input Period             | 3.5V     | 8ТрС              |          |       | 1     |

|                      |                                                   | 5.5V                           | 8ТрС     |                   |          | 1     |       |

| 7                    | $T_R T_{IN}, T_T T_{IN}$                          | Timer Input Rise and Fall Time | 3.5V     |                   | 100      | ns    | 1     |

|                      |                                                   |                                | 5.5V     |                   | 100      | ns    | 1     |

| 8                    | T <sub>W</sub> IL Interrupt Re                    | Interrupt Request Input Low    | 3.5V     | 100               |          | ns    | 1,2   |

|                      |                                                   | Time                           | 5.5V     | 70                |          | ns    | 1,2   |

| 9                    | T <sub>W</sub> IH                                 | Interrupt Request Input High   | 3.5V     | 5TpC              |          |       | 1,2   |

|                      |                                                   | Time                           | 5.5V     | 5TpC              |          |       | 1,2   |

| 10                   | T <sub>WDT</sub>                                  | Watch-Dog Timer Delay Time     | 3.5V     | 10                |          | ms    |       |

|                      |                                                   | before Time-out                | 5.5V     | 5                 |          | ms    |       |

| 11                   | T <sub>POR</sub>                                  | Power-On Reset Time            | 3.5V     | 4                 | 36       | ms    |       |

|                      |                                                   | _                              | 5.5V     | 2                 | 18       | ms    |       |

Interrupt request through Port 3 (P33-P31)

#### **LOW EMI Mode at Standard Temperature**

Table 12 describes timing characteristics in LOW EMI mode at standard temperature for the timing diagram noted in Figure 8.

Table 12. AC Electrical Timing, Standard Mode at Extended Temperature

|    |                                     |                               | $TA = 0^{\circ}C \text{ to } +70^{\circ}C$ |      |     |      |     |       |       |  |

|----|-------------------------------------|-------------------------------|--------------------------------------------|------|-----|------|-----|-------|-------|--|

|    |                                     |                               |                                            | 1M   | Hz  | 4M   | Hz  |       |       |  |

| No | Symbol                              | Parameter                     | V <sub>CC</sub>                            | Min  | Max | Min  | Max | Units | Notes |  |

| 1  | T <sub>P</sub> C                    | Input Clock Period            | 3.5V                                       | 1000 | DC  | 250  | DC  | ns    | 1     |  |

|    |                                     | ·                             | 5.5V                                       | 1000 | DC  | 250  | DC  | ns    | 1     |  |

| 2  | 2 T <sub>R</sub> C,T <sub>F</sub> C | Clock Input Rise and          | 3.5V                                       |      | 25  |      | 25  | ns    | 1     |  |

|    |                                     | Fall Times                    | 5.5V                                       |      | 25  |      | 25  | ns    | 1     |  |

| 3  | T <sub>W</sub> C                    | Input Clock Width             | 3.5V                                       | 500  |     | 125  |     | ns    | 1     |  |

|    |                                     | -                             | 5.5V                                       | 500  |     | 125  |     | ns    | 1     |  |

| 4  | $T_WT_INL$                          | Timer Input Low               | 3.5V                                       | 70   |     | 70   |     | ns    | 1     |  |

|    |                                     | Width -                       | 5.5V                                       | 70   |     | 70   |     | ns    | 1     |  |

| 5  | 5 T <sub>W</sub> T <sub>IN</sub> H  | Timer Input High<br>Width     | 3.5V                                       | 3TpC |     | 3TpC |     |       | 1     |  |

|    |                                     |                               | 5.5V                                       | 3TpC |     | 3TpC |     |       | 1     |  |

| 6  | $T_PT_IN$                           | Timer Input Period            | 3.5V                                       | 4TpC |     | 4TpC |     | -     | 1     |  |

|    |                                     |                               | 5.5V                                       | 4TpC |     | 4TpC |     | -     | 1     |  |

| 7  | $T_RT_IN,T_TT_IN$                   | Timer Input Rise and          | 3.5V                                       |      | 100 |      | 100 | ns    | 1     |  |

|    |                                     | Fall Time                     | 5.5V                                       |      | 100 |      | 100 | ns    | 1     |  |

| 8  | T <sub>W</sub> IL                   | Interrupt Request             | 3.5V                                       | 70   |     | 70   |     | ns    | 1,2   |  |

|    |                                     | Input Low Time                | 5.5V                                       | 70   |     | 70   |     | ns    | 1,2   |  |

| 9  | T <sub>W</sub> IH                   | Interrupt Request             | 3.5V                                       | 3ТрС |     | 3ТрС |     |       | 1,2   |  |

|    |                                     | Input High Time               | 5.5V                                       | 3TpC |     | 3TpC |     |       | 1,2   |  |

| 10 | T <sub>WDT</sub>                    | Watch-Dog Timer               | 3.5V                                       | 10   |     | 10   |     | ms    |       |  |

|    |                                     | Delay Time before<br>Time-out | 5.5V                                       | 5    |     | 5    |     | ms    |       |  |

Recommendations for dampening voltage surges in both test and OTP mode include the following:

- Using a clamping diode to V<sub>CC</sub>.

- Adding a capacitor to the affected pin.

- **Note:** Programming the EPROM/Test Mode Disable option prevents accidental entry into EPROM Mode or Test Mode.

#### **STANDARD Mode**

**XTAL1, XTAL2.** Crystal In, Crystal Out (time-based input and output, respectively). These pins connect an external parallel-resonant crystal, resonator, RC, LC, or an external single-phase clock (8 MHz max) to the on-chip clock oscillator and buffer.

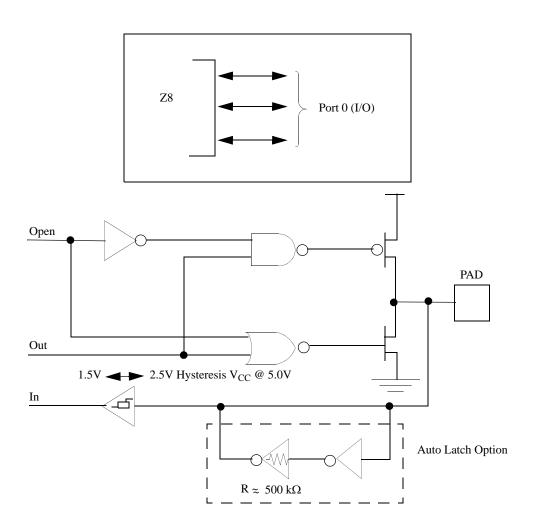

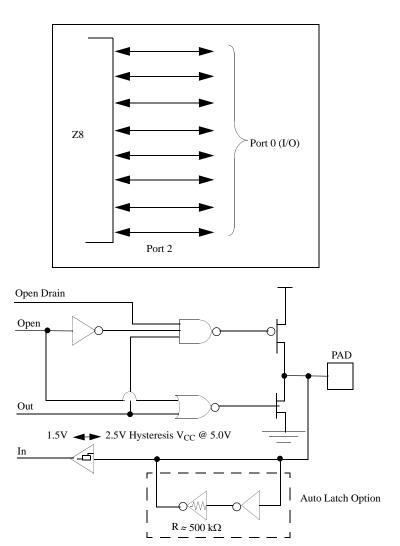

**Port 0, P02–P00.** Port 0 is a 3-bit bidirectional, Schmitt-triggered CMOS-compatible I/O port. These three I/O lines can be globally configured under software control to be inputs or outputs (Figure 9).

**Auto Latch.** The Auto Latch places valid CMOS levels on all CMOS inputs (except P33, P32, P31) that are not externally driven. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer. On Power-up and Reset, the Auto Latch sets the ports to an undetermined state of 0 or 1. The default condition is AUTO LATCH ENABLED. The Auto Latch can be disabled by programming the AUTO LATCH DISABLE option bit.

Figure 9. Port 0 Configuration

**Port 2, P27–P20.** Port 2 is an 8-bit, bit programmable, bidirectional, Schmitt-triggered CMOS-compatible I/O port. These eight I/O lines can be configured under software control to be inputs or outputs, independently. Bits programmed as outputs can be globally programmed as either push-pull or open-drain (Figure 10).

Figure 10. Port 2 Configuration

**Port 3, P33–P31.** Port 3 is a 3-bit, CMOS-compatible port with three fixed input (P33–P31) lines. These three input lines can be configured under software control as digital Schmitt-trigger inputs.

These three input lines are also used as the interrupt sources IRQ0–IRQ3, and as the timer input signal  $T_{\rm IN}$  (Figure 11).

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register. All Z8 interrupts are vectored through locations in program memory. When an interrupt machine cycle is activated, an Interrupt Request is granted, thus disabling all subsequent interrupts, saving the Program Counter and Status Flags, and then branching to the program memory vector location reserved for that interrupt. This memory location and the next byte contain the 16-bit starting address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the interrupt request register is polled to determine which of the interrupt requests requires service.

Note: The rising edge interrupt is not supported. on the CCP emulator (a hardware/software work around must be employed).

## Hardware Work Around on the on the Z86CCP01ZEM Emulator to P32 Rising Edge Digital Interrupt

To emulate the P32 rising edge digital interrupt the emulator must be modified in the following way:

- 1. Connect P32 by soldering a wire jumper from either emulation socket (P3, pin 17) or (P2, pin 12) to 74HCT04 U27 pin 1.

- 2. Connect 74HCT04 U27 pin 2 by soldering a wire jumper from U27 pin 2 to P30 on either emulator socket (P3, pin 25) or (P2, pin 18).

## Hardware Work Around on the on the Z86CCP01ZEM Emulator to P32 Rising Edge Analog Interrupt

To emulate the P32 rising edge analog interrupt the emulator must be modified in the following way:

- 1. Connect P32 by soldering a wire jumper from either emulation socket (P2, pin 16) or (P1, pin 23) to 74HCT04 U27 pin 1.

- 2. Connect 74HCT04 U27 pin 2 by soldering a wire jumper from U27 pin 2 to P30 on either emulator socket (P3, pin 25) or (P2, pin 18).

The following routine must be added to the initialization of the device:

HSWP32AFIX Push RP

LD RP, #0Fh LD R0, #0FFh POP RP

#### Op Code WDT (5Fh)

The first time Op Code 5Fh is executed, the WDT is enabled; subsequent execution clears the WDT counter. This clearing of the counter must be performed at least every  $\mathsf{T}_{\mathsf{WDT}}$  otherwise, the WDT times out and generates a reset. The generated reset is the same as a power-on reset of  $\mathsf{T}_{\mathsf{PQR}}$ , plus 18 crystal clock cycles. The software enabled WDT does not run in STOP mode.

On the CCP emulator, a software workaround must be used to emulate the software WDT. This workaround follows.

SWFIXSWDT: PUSH RP

LD RP, #0Fh

LD R15,#00000101B

POP RP

#### Op Code WDH (4Fh)

When this instruction is executed it enables the WDT during HALT. If not, the WDT stops when entering HALT. This instruction does not clear the counters – it just makes it possible to operate the WDT during HALT mode. A WDH instruction executed without executing WDT (5Fh) yields no effect.

Not

**Note:** On the CCP emulator, a software workaround must be used to enable the software in HALT Mode/STOP Mode or hardware-enabled WDT. This workaround follows.

# Software Work Around on the Z86CCP01ZEM Emulator to Emulate the Software WDT Running in HALT Mode

SWFIXSWDT: PUSH RP

LD RP, #0Fh

LD R15.#00000101B

POP RP

#### **Permanent WDT**

Selecting the hardware-enabled Permanent WDT option bit automatically enables the WDT upon exiting reset. The permanent WDT always runs in HALT mode and STOP mode, and it cannot be disabled.

# Software Work Around on the Z86CCP01ZEM Emulator to Emulate the Hardware Enabled Permanent WDT in HALT Mode and Stop Mode

The following functions must be performed

1. The first instruction after reset at address 000Ch must be the WDT instruction or op code 5F. The following routine must be added in the initialization of the

HSWFIXHWDT: PUSH RP

LD RP, #0Fh

LD R15,#00000101B

POP RP

## Auto Reset Voltage (V<sub>LV</sub>)

The Z8 features an auto-reset built-in. The auto-reset circuit resets the Z8 when it detects the  $V_{CC}$  below  $V_{LV}$  Figure 19 shows the Auto Reset Voltage versus temperature. If the  $V_{CC}$  drops below the  $V_{CC}$  operating voltage range, the Z8 functions down to the  $V_{LV}$  unless the internal clock frequency is higher than the specified maximum  $V_{LV}$  frequency.

Table 21. Port 3 Mode Register, R247 P3M F7h Bank 0h: WRITE ONLY

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|---|---|---|---|---|---|

| R/W   | W | W | W | W | W | W | W | W |

| Reset | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Х |

| Bit<br>Position | Bit Field | R/W | Reset<br>Value | Description                                   |  |

|-----------------|-----------|-----|----------------|-----------------------------------------------|--|

| 7-2             | Reserved  | W   | Х              | Reserved-must be 0                            |  |

| 1               | Port 3    | W   | 0              | Port 3 Outputs 0: DIGITAL Mode 1: ANALOG Mode |  |

| 0               | Port 2    | W   | 0              | Port 2 Outputs 0: Open-Drain 1: Push-Pull     |  |

Table 22. Port 0 and 1 Mode Register, R248 P01 F8h Bank 0h: WRITE ONLY

| Bit                                | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------|---|---|---|---|---|---|---|---|

| R/W                                | W | W | W | W | W | W | W | W |

| Reset                              | Χ | Х | Χ | 0 | Χ | 1 | 0 | 1 |

| Note: W = Write, X = Indeterminate |   |   |   |   |   |   |   |   |

| Bit<br>Position | Bit Field | R/W | Reset<br>Value | Description                     |

|-----------------|-----------|-----|----------------|---------------------------------|

| 7-5, 3          | Reserved  | W   | Х              | Reserved-must be 0              |

| 4               | Reserved  | W   | 0              | Reserved-must be 0              |

| 2               | Reserved  | W   | Х              | Reserved-must be 1              |

| 1-0             | P02-P00   | W   | 01             | P02-P00 Mode 0: Output 1: Input |

Table 25. Interrupt Mask Register, R251 IMR FBh Bank 0h: READ/WRITE

| Bit                       | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W                       | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: R = Read, W = Write |     |     |     |     |     |     |     |     |

Bit Reset **Position** Bit Field R/W Value **Description** 7 0 R/W 0: Disables global interrupts\* Master Interrupt 1: Enables global interrupts\* Enable 6 Reserved R/W Χ Reserved-must be 0 5-0 IRQ0-R/W Χ 1: Enables IRQ0-IRQ5 (D0 = IRQ0) IRQ5 Note: \*Must use Ei/Di instruction to set/reset this bit.

Table 26. Flag Register, R252 FCh Bank 0h: READ/WRITE

| Bit                              | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W                              | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset                            | 0   | Х   | Х   | Х   | Х   | Χ   | Х   | Х   |

| Note: R = Read, X= Indeterminate |     |     |     |     |     |     |     |     |

| Bit        |                    |     | Reset |                     |

|------------|--------------------|-----|-------|---------------------|

| Position   | Bit Field          | R/W | Value | Description         |

| 7          | Carry              | R/W | Χ     | Carry Flag          |

| 6          | Zero               | R/W | Χ     | Zero Flag           |

| 5          | Sign               | R/W | Χ     | Sign Flag           |

| 4          | Overflow           | R/W | Χ     | Overflow Flag       |

| 3          | Decimal Adjust     | R/W | Χ     | Decimal Adjust Flag |

| 2          | Half Carry         | R/W | Х     | Half Carry Flag     |

| 1          | User               | R/W | Х     | User Flag F2*       |

| 0          | User               | R/W | Х     | User Flag F1*       |

| Note: *Not | affected by RESET. |     |       |                     |

PS014802-0903

Table 29. Stack Pointer Low, R255 SPL FFh Bank 0h: READ/WRITE

| Bit                      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------------------------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| R/W                      | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset 0 0 0 0 0 0 0 0    |     |     |     |     |     |     |     |     |  |

| Note: R = Read. W= Write |     |     |     |     |     |     |     |     |  |

| Bit<br>Position | Bit Field | R/W | Reset<br>Value | Description                        |

|-----------------|-----------|-----|----------------|------------------------------------|

| 7-0             | Stack     | R/W | 0              | Stack Pointer Lower Byte (SP0-SP7) |