# E·XFL

#### Zilog - Z86E0208HSC1925TR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | Z8                                                           |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 8MHz                                                         |

| Connectivity               | -                                                            |

| Peripherals                | POR, WDT                                                     |

| Number of I/O              | 14                                                           |

| Program Memory Size        | 512B (512 x 8)                                               |

| Program Memory Type        | ОТР                                                          |

| EEPROM Size                | -                                                            |

| RAM Size                   | 61 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                  |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e0208hsc1925tr |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Architectural Overview**

ZiLOG's Z86E02 SL1925 Microcontroller (MCU) is a One-Time Programmable (OTP) member of ZiLOG's single-chip Z8<sup>®</sup> MCU family that allows easy software development, debug, prototyping, and small production runs not economically desirable with masked ROM versions.

For applications demanding powerful I/O capabilities, the Z86E02 SL1925's dedicated input and output lines are grouped into three ports, and are configurable under software control to provide timing, status signals, or parallel I/O. One onchip counter/timer, with a large number of user-selectable modes, offload the system of administering real-time tasks such as counting/timing and I/O data communications.

## Z86E02 SL1925 Features

#### Table 1. Z86E02 SL1925 Features

| Device            | OTP (KB) | RAM* (Bytes) | Speed (MHz) |

|-------------------|----------|--------------|-------------|

| Z86E02 SL1925     | 0.5      | 61           | 8           |

| Note: *General-Pu | irpose.  |              |             |

- 3.5V to 5.5V Operating Range @ 0°C to +70°C

- 4.5V to 5.5V Operating Range @ -40°C to +105°C

- 14 Input/Output Lines

- Six Vectored, Prioritized Interrupts (3 falling edge, 1 rising edge, 1 timer, 1 software)

- Program Options:

- Low Noise

- ROM Protect

- Auto Latch

- Watch-Dog Timer (WDT)

- RC Oscillator

- One Programmable 8-Bit Counter/Timer, with 6-bit Programmable Prescaler

- WDT/Power-On Reset (POR)

- On-Chip Oscillator that accepts XTAL, Ceramic Resonance, LC, RC, or External Clock

- Clock-Free WDT Reset

- Low-Power Consumption (50 mΩ typical)

- Fast Instruction Pointer (1.5µs @ 8 MHz)

- RAM Bytes (61)

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |

| Ground     | GND             | $V_{SS}$        |

## **BLOCK DIAGRAMS**

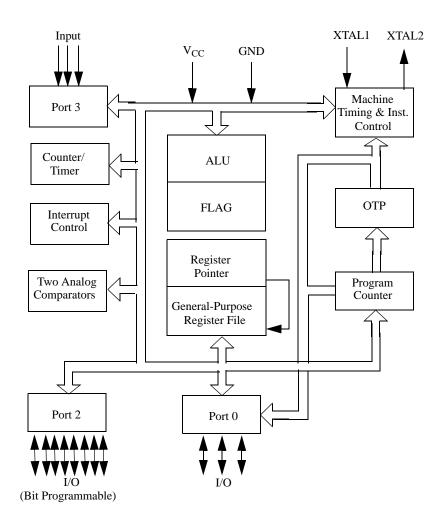

Figure 1. Functional Block Diagram

| Pin # | Symbol          | Function                 | Direction    |

|-------|-----------------|--------------------------|--------------|

| 1,2   | P24-P25         | Port 2, Pins 4-5         | Input/Output |

| 3     | P27             | Port 2, Pin 7            | Input/Output |

| 4     | P26             | Port 2, Pin 6            | Input/Output |

| 5     | V <sub>CC</sub> | Power Supply             |              |

| 6     | V <sub>CC</sub> | Power Supply             |              |

| 7     | XTAL1           | Crystal Oscillator Clock | Input        |

| 8     | XTAL2           | Crystal Oscillator Clock | Output       |

| 9     | P31             | Port 3, Pin 1, AN1       | Input        |

| 10    | P32             | Port 3, Pin 2, AN2       | Input        |

| 11    | P33             | Port 3, Pin 3, REF       | Input        |

| 12    | P00             | Port 0, Pin 0            | Input/Output |

| 13    | P02             | Port 0, Pin 1            | Input/Output |

| 14    | P01             | Port 0, Pin 1            | Input/Output |

| 15    | GND             | Ground                   |              |

| 16    | GND             | Ground                   |              |

| 17    | P21             | Port 2, Pin 1            | Input/Output |

| 18    | P20             | Port 2, Pin 0            | Input/Output |

| 19-20 | P22-P23         | Port 2, Pins 2-3         | Input/Output |

20 mA

## **Electrical Characteristics**

## **Absolute Maximum Ratings**

Stresses greater than those listed on Table 6 may cause permanent damage to the device. This rating is a stress rating only; functional operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability. Total power dissipation should not exceed 462 m $\Omega$  for the package. See Table 6. Power dissipation is calculated as follows:

Total Power Dissipation =  $V_{CC} \times [I_{CC} - (\text{sum of } I_{OH})]$ +sum of  $[(V_{CC} - V_{OH}) \times I_{OH}]$ + sum of  $(V_{OL} \times I_{OL})$

#### Parameter Units Min Max Note Ambient Temperature under Bias -40 +105 С Storage Temperature -65 +150С Voltage on any Pin with Respect to VSS -0.7 +12 V 1 Voltage on V<sub>DD</sub> Pin with Respect to V<sub>SS</sub> -0.3 +7 V Voltage on XTAL1, P31, P32, P33 with respect to V<sub>SS</sub> 3 -0.6 V<sub>DD</sub>+1 V **Total Power Dissipation** 462 mΩ Maximum Allowable Current out of VSS 300 mΑ Maximum Allowable Current into VDD 270 mΑ Maximum Allowable Current into an Input Pin -600 +600uА 4 Maximum Allowable Current into an Open-Drain Pin -600 +600 μA 2 Maximum Allowable Output Current Linked by any I/O Pin 20 mΑ

#### Table 6. Absolute Maximum Ratings

1. Applies to all pins except where otherwise noted. Maximum current into or out of pin must be  $\pm 600 \ \mu$ A.

2. Device pin is not at an output Low state.

3. There is no input protection diode from pin to  $V_{DD}$ .

Maximum Allowable Output Current Sourced by any I/O Pin

4. This excludes XTAL1 and XTAL2.

#### **Standard Test Conditions**

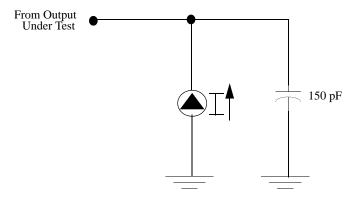

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to Ground. Positive current flows into the referenced pin See Figure 7.

Figure 7. Test Load Diagram

## Capacitance

$\rm T_{A}$  = 25°C,  $\rm V_{CC}$  = GND = OV, f = 1.0 MHz, unmeasured pins returned to GND. See Table 7.

| Parameter          | Min | Мах   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 10 pF |

| Output capacitance | 0   | 20 pF |

| I/O capacitance    | 0   | 25 pF |

#### Table 7. Capacitance

## **DC Electrical Characteristics**

### **Standard Temperature Range**

Table 8 provides Direct Current characteristics for the Z86E02 SL1925 microcontroller, at a standard ambient temperature range of 0°C to 70°C.

|                    | TA = 0°C to +70°C |                 |     |     |                                      |                          |       |  |  |  |  |

|--------------------|-------------------|-----------------|-----|-----|--------------------------------------|--------------------------|-------|--|--|--|--|

| Sym                | Parameter         | V <sub>CC</sub> | Min | Max | Typical @<br>25°C <sup>1</sup> Units | Conditions               | Notes |  |  |  |  |

| V <sub>INMAX</sub> | Max Input Voltage | 3.5V            | -12 | 12  | V                                    | I <sub>IN</sub> < 250 μA | 2     |  |  |  |  |

|                    |                   | 5.5V            | -12 | 12  | V                                    | I <sub>IN</sub> < 250 μA | 2     |  |  |  |  |

#### Table 8. DC Characteristics, Standard Temperature Range

|                  |                            |                 | ТА  | . = -40°C | to +105°C                      |       |                                       |       |

|------------------|----------------------------|-----------------|-----|-----------|--------------------------------|-------|---------------------------------------|-------|

| Sym              | Parameter                  | V <sub>CC</sub> | Min | Max       | Typical<br>@ 25°C <sup>1</sup> | Units | Conditions                            | Notes |

| I <sub>CC</sub>  | Supply Current             | 4.5V            |     | 7.0       | 6.8                            | mA    | @ 2 MHz                               | 3,6   |

|                  | -                          | 5.5V            |     | 7.0       | 6.8                            | mA    | @ 2 MHz                               | 3,6   |

|                  | -                          | 4.5V            |     | 11.0      | 8.2                            | mA    | @ 8 MHz                               | 3,6   |

|                  | -                          | 5.5V            |     | 11.0      | 8.2                            | mA    | @ 8 MHz                               | 3,6   |

| I <sub>CC1</sub> | Standby Current            | 4.5V            |     | 3.0       | 2.5                            | mA    | @ 2 MHz                               | 3,6   |

|                  | (HALT Mode)                | 5.5V            |     | 3.0       | 2.5                            | mA    | @ 2 MHz                               | 3,6   |

|                  |                            | 4.5V            |     | 5.0       | 3.0                            | mA    | @ 8 MHz                               | 3,6   |

|                  | -                          | 5.5V            |     | 5.0       | 3.0                            | mA    | @ 8 MHz                               | 3,6   |

| I <sub>CC</sub>  | Supply Current (Low        | 4.5V            |     | 7.0       | 6.8                            | mA    | @ 1 MHz                               | 6,10  |

|                  | EMI Mode)                  | 5.5V            |     | 7.0       | 6.8                            | mA    | @ 1 MHz                               | 6,10  |

|                  |                            | 4.5V            |     | 9.0       | 7.5                            | mA    | @ 2 MHz                               | 6,10  |

|                  |                            | 5.5V            |     | 9.0       | 7.5                            | mA    | @ 2 MHz                               | 6,10  |

|                  |                            | 4.5V            |     | 11.0      | 8.2                            | mA    | @ 4 MHz                               | 6,10  |

|                  |                            | 5.5V            |     | 11.0      | 8.2                            | mA    | @ 4 MHz                               | 6,10  |

| I <sub>CC1</sub> | Standby Current            | 4.5V            |     | 1.6       | 0.9                            | mA    | @ 1 MHz                               | 6,10  |

|                  | (HALT and Low EMI<br>Mode) | 5.5V            |     | 1.6       | 0.9                            | mA    | @ 1 MHz                               | 6,10  |

|                  |                            | 4.5V            |     | 1.9       | 1.0                            | mA    | @ 2 MHz                               | 6,10  |

|                  | -                          | 5,5V            |     | 1.9       | 1.0                            | mA    | @ 2 MHz                               | 6,10  |

|                  | -                          | 4.5V            |     | 2.4       | 3.0                            | mA    | @ 4 MHz                               | 6,10  |

|                  |                            | 5.5V            |     | 2.4       | 3.0                            | mA    | @ 4 MHz                               | 6,10  |

| I <sub>CC2</sub> | Standby Current            | 4.5V            |     | 20        | 1.0                            | μA    | WDT is not Running                    | 6,7,8 |

|                  | (Stop mode)                | 5.5V            |     | 20        | 1.0                            | μA    | WDT is not Running                    | 6,7,8 |

| I <sub>ALL</sub> | Auto Latch Low             | 4.5V            |     | 40        | 16                             | μA    | 0V< V <sub>IN</sub> < V <sub>CC</sub> | 9     |

|                  | Current                    | 5.5V            |     | 40        | 16                             | μA    | $0V < V_{IN} < V_{CC}$                | 9     |

## Table 9. DC Characteristics, Extended Temperature Range (Continued)

#### Table 9. DC Characteristics, Extended Temperature Range (Continued)

|                                                                                                                        |                     | ТА   | ∖ = -40°C 1 | to +105°C                      |       |                                       |       |

|------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------------|--------------------------------|-------|---------------------------------------|-------|

| Sym Parame                                                                                                             | ter V <sub>CC</sub> | Min  | Max         | Typical<br>@ 25°C <sup>1</sup> | Units | Conditions                            | Notes |

| I <sub>ALH</sub> Auto Latch H<br>Current                                                                               | igh 4.5V            |      | -20.0       | -8.0                           | μA    | 0V< V <sub>IN</sub> < V <sub>CC</sub> | 9     |

|                                                                                                                        | 5.5V                |      | -20.0       | -8.0                           | μA    | $0V < V_{IN} < V_{CC}$                | 9     |

| <ol> <li>Typical values are</li> <li>Port 2, Port 3, and</li> <li>STANDARD mode</li> <li>These values apply</li> </ol> | Port 0 only.        | de). | de or HALT  | mode                           |       |                                       |       |

7. If the analog comparator is selected, then the comparator inputs must be at the V<sub>CC</sub> level. 8. A 10-M $\Omega$  pull-up resistor is required in the circuit between the XTAL1 pin to the V<sub>CC</sub> pin.

9. Auto latches are enabled.

10. Low EMI Mode (not Standard Mode)

## **STANDARD Mode at Extended Temperature**

Table 11 describes timing characteristics in STANDARD mode at extended temperature for the timing diagram noted in Figure 8.

#### Table 11. AC Electrical Timing, Standard Mode at Extended Temperature

|    |                                   |                                 | 1               | TA = -40°C | to +105° | С     |       |

|----|-----------------------------------|---------------------------------|-----------------|------------|----------|-------|-------|

|    |                                   |                                 |                 |            | 8MHz     |       |       |

| No | Symbol                            | Parameter                       | V <sub>CC</sub> | Min        | Max      | Units | Notes |

| 1  | T <sub>P</sub> C                  | Input Clock Period              | 4.5V            | 125        | DC       | ns    | 1     |

|    |                                   | -                               | 5.5V            | 125        | DC       | ns    | 1     |

| 2  | T <sub>R</sub> C,T <sub>F</sub> C | Clock Input Rise and Fall Times | 4.5V            |            | 25       | ns    | 1     |

|    |                                   |                                 | 5.5V            |            | 25       | ns    | 1     |

| 3  | T <sub>W</sub> C                  | Input Clock Width               | 4.5V            |            | 62       | ns    | 1     |

|    |                                   | -                               | 5.5V            |            | 62       | ns    | 1     |

| 4  | $T_W T_{IN} L$                    | Timer Input Low Width           | 4.5V            | 70         |          | ns    | 1     |

|    |                                   |                                 | 5.5V            | 70         |          | ns    | 1     |

| 5  | Τ <sub>W</sub> T <sub>IN</sub> H  | Timer Input High Width          | 4.5V            | 5TpC       |          |       | 1     |

|    |                                   | -                               | 5.5V            | 5TpC       |          |       | 1     |

| 6  | $T_P T_{IN}$                      | Timer Input Period              | 4.5V            | 8TpC       |          |       | 1     |

|    |                                   | -                               | 5.5V            | 8TpC       |          |       | 1     |

| 7  | $T_R T_{IN}, T_T T_{IN}$          | Timer Input Rise and Fall Time  | 4.5V            |            | 100      | ns    | 1     |

|    |                                   |                                 | 5.5V            |            | 100      | ns    | 1     |

| 8  | T <sub>W</sub> IL                 | Interrupt Request Input Low     | 4.5V            | 70         |          | ns    | 1,2   |

|    |                                   | Time                            | 5.5V            | 70         |          | ns    | 1,2   |

| 9  | T <sub>W</sub> IH                 | Interrupt Request Input High    | 4.5V            | 5TpC       |          |       | 1,2   |

|    |                                   | Time                            | 5.5V            | 5TpC       |          |       | 1,2   |

| 10 | T <sub>WDT</sub>                  | Watch-Dog Timer Delay Time      | 4.5V            | 5          |          | ms    |       |

|    |                                   | before Time-out                 | 5.5V            | 5          |          | ms    |       |

| 11 | T <sub>POR</sub>                  | Power-On Reset Time             | 4.5V            | 1          | 20       | ms    |       |

|    |                                   | -                               | 5.5V            | 1          | 20       | ms    |       |

2. Interrupt request through Port 3 (P33-P31)

|    |                  |                |                 | TA = | 0°C to + | -70°C     |     |       |       |

|----|------------------|----------------|-----------------|------|----------|-----------|-----|-------|-------|

| No |                  |                | 1               |      |          | 1MHz 4MHz |     |       |       |

|    | Symbol           | Parameter      | V <sub>CC</sub> | Min  | Мах      | Min       | Max | Units | Notes |

| 11 | T <sub>POR</sub> | Power-On Reset | 3.5V            | 2    | 18       | 2         | 18  | ms    |       |

|    |                  | Time           | 5.5V            | 2    | 18       | 2         | 18  | ms    |       |

#### Table 12. AC Electrical Timing, Standard Mode at Extended Temperature (Continued)

CC

2. Interrupt request through Port 3 (P33-P31)

## LOW EMI Mode at Extended Temperature

Table 13 describes timing characteristics in LOW EMI mode at extended temperature for the timing diagram noted in Figure 8.

|    |                                   |                                                  |      | TA = |     |      |     |       |       |

|----|-----------------------------------|--------------------------------------------------|------|------|-----|------|-----|-------|-------|

|    |                                   |                                                  |      | 1M   | Hz  | 4M   | Hz  |       |       |

| No | Symbol                            | Parameter                                        | Vcc  | Min  | Max | Min  | Мах | Units | Notes |

| 1  | T <sub>P</sub> C                  | Input Clock Period                               | 4.5V | 1000 | DC  | 250  | DC  | ns    | 1     |

|    |                                   | -                                                | 5.5V | 1000 | DC  | 250  | DC  | ns    | 1     |

| 2  | T <sub>R</sub> C,T <sub>F</sub> C | T <sub>F</sub> C Clock Input Rise and Fall Times | 4.5V |      | 25  |      | 25  | ns    | 1     |

|    |                                   |                                                  | 5.5V |      | 25  |      | 25  | ns    | 1     |

| 3  | T <sub>W</sub> C                  | Input Clock Width                                | 4.5V | 500  |     | 125  |     | ns    | 1     |

|    |                                   | -                                                | 5.5V | 500  |     | 125  |     | ns    | 1     |

| 4  | T <sub>W</sub> T <sub>IN</sub> L  | Timer Input Low                                  | 4.5V | 70   |     | 70   |     | ns    | 1     |

|    |                                   | Width                                            | 5.5V | 70   |     | 70   |     | ns    | 1     |

| 5  | $T_W T_{IN} H$                    | Timer Input High                                 | 4.5V | 3TpC |     | 3TpC |     |       | 1     |

|    |                                   | Width                                            | 5.5V | 3TpC |     | 3TpC |     |       | 1     |

| 6  | T <sub>P</sub> T <sub>IN</sub>    | Timer Input Period                               | 4.5V | 4TpC |     | 4TpC |     |       | 1     |

|    |                                   | -                                                | 5.5V | 4TpC |     | 4TpC |     |       | 1     |

| 7  | $T_R T_{IN}, T_T T_{IN}$          | Timer Input Rise and                             | 4.5V |      | 100 |      | 100 | ns    | 1     |

|    |                                   | Fall Time                                        | 5.5V |      | 100 |      | 100 | ns    | 1     |

|    |                                   | -                                                |      |      |     |      |     |       |       |

#### Table 13. AC Electrical Timing, Low EMI Mode at Extended Temperature

## **Pin Functions**

#### EPROM Mode

**D7–D0 Data Bus.** Data can be read from, or written to, the EPROM through this data bus.

**V<sub>CC</sub> Power Supply.** It is typically 5V during all EPROM Read Mode and typically 6.4V during other modes (PROGRAM, PROGRAM VERIFY, etc.).

**CE Chip Enable (active Low).** This pin is active during EPROM READ mode, PROGRAM mode, and PROGRAM VERIFY mode.

**OE Output Enable (active Low).** This pin drives the Data Bus direction. When this pin is Low, the data bus is output. When High, the data bus is input. This pin must toggle for each data output read.

**EPM EPROM Program Mode.** This pin controls the selection of EPROM operation modes by applying different voltages.

$V_{PP}$  Program Voltage. This pin supplies the program voltage.

Clear (active High). This pin resets the internal address counter at the High level.

**Clock Address Clock.** This pin is a clock input. The internal address counter increases by one count with one clock cycle.

**PGM Program Mode (active Low).** A Low level at this pin programs the data to the EPROM through the data bus.

### **Pin Function Changes in EPROM Mode**

With the exception of  $V_{CC}$  and GND, the Z8<sup>®</sup> changes all <u>of</u> its pin functions in <u>EPROM</u> mode.  $X_{OUT}$  offers no function;  $X_{IN}$  functions as CE, P31 functions as OE, P32 functions as EPM, P33 functions as  $V_{PP}$  P00 functions as CLEAR, P01 functions as CLOCK, and P02 functions as PGM. Please refer to Program Memory for additional EPROM mode descriptions.

#### **Application Precaution**

The production test-mode environment may be enabled accidentally during normal operation if excessive noise surges above  $V_{CC}$  occur on the XTAL1 pin ( $\overline{OE}$ ).

In addition, processor operation of Z8<sup>®</sup> OTP devices maybe affected by excessive noise surges on the P33 ( $V_{PP}$ ), XTAL1 (CE), P32 (EPM), P31 (OE) pins while the microcontroller is in Standard Mode.

Recommendations for dampening voltage surges in both test and OTP mode include the following:

- Using a clamping diode to V<sub>CC</sub>.

- Adding a capacitor to the affected pin.

- **Note:** Programming the EPROM/Test Mode Disable option prevents accidental entry into EPROM Mode or Test Mode.

## STANDARD Mode

**XTAL1, XTAL2.** Crystal In, Crystal Out (time-based input and output, respectively). These pins connect an external parallel-resonant crystal, resonator, RC, LC, or an external single-phase clock (8 MHz max) to the on-chip clock oscillator and buffer.

**Port 0, P02–P00.** Port 0 is a 3-bit bidirectional, Schmitt-triggered CMOS-compatible I/O port. These three I/O lines can be globally configured under software control to be inputs or outputs (Figure 9).

**Auto Latch.** The Auto Latch places valid CMOS levels on all CMOS inputs (except P33, P32, P31) that are not externally driven. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer. On Power-up and Reset, the Auto Latch sets the ports to an undetermined state of 0 or 1. The default condition is AUTO LATCH ENABLED. The Auto Latch can be disabled by programming the AUTO LATCH DISABLE option bit.

ation, Port 3 data inputs, or  $T_{IN}$  through P31. Alternatively, the comparators can be disabled, freeing the reference input (P33) for use as IRQ1 and/or P33 input.

The comparator requires two NOPs to be stable after setting the enable bit. ZiLOG recommends that interrupts IRQ0, IRQ1, and IRQ2 be disabled before setting the enable bit. After enabling the comparator, IRQ0, IRQ1, and IRQ2 should be cleared prior to re-enabling the interrupts. ZiLOG also recommends clearing these interrupts when disabling the comparator.

## Hardware Work Around on the on the Z86CCP01ZEM Emulator to P32 Rising Edge Digital Interrupt

To emulate the P32 rising edge digital interrupt the emulator must be modified in the following way:

- Connect P32 by soldering a wire jumper from either emulation socket (P3, pin 17) or (P2, pin 12) to 74HCT04 U27 pin 1.

- 2. Connect 74HCT04 U27 pin 2 by soldering a wire jumper from U27 pin 2 to P30 on either emulator socket (P3, pin 25) or (P2, pin 18).

## Hardware Work Around on the on the Z86CCP01ZEM Emulator to P32 Rising Edge Analog Interrupt

To emulate the P32 rising edge analog interrupt the emulator must be modified in the following way:

- Connect P32 by soldering a wire jumper from either emulation socket (P2, pin 16) or (P1, pin 23) to 74HCT04 U27 pin 1.

- 2. Connect 74HCT04 U27 pin 2 by soldering a wire jumper from U27 pin 2 to P30 on either emulator socket (P3, pin 25) or (P2, pin 18).

The following routine must be added to the initialization of the device:

| HSWP32AFIX | Push RP      |

|------------|--------------|

|            | LD RP, #0Fh  |

|            | LD R0, #0FFh |

|            | POP RP       |

#### **Program Memory**

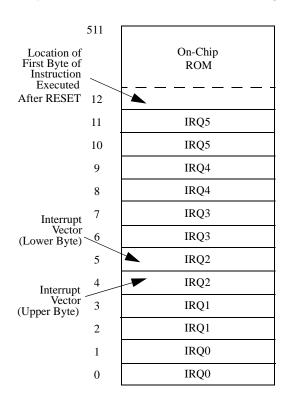

The Z86E02 SL1925 addresses up to 512B of internal program memory (Figure 13). The first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that correspond to the six available interrupts. Bytes 0–511 are on-chip one-time programmable EPROM.

Figure 13. Program Memory Map

## **Register File**

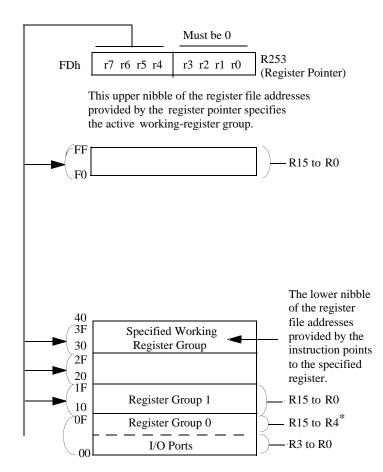

The Register File consists of three I/O port registers, 61 general-purpose registers, and 14 control and status registers R0, R2-R3, R4–R63, R254 and R241–R253, and R255, respectively (Figure 14). General-purpose registers occupy the 04h to 3Fh address space. I/O ports are mapped as per the existing CMOS Z8.

\* Expanded RegisterGroup [0] is selected in this figure by handling bits D3 to D0 as "0" in Register R253(RP).

## **Stack Pointer**

The  $Z8^{\text{(B)}}$  features an 8-bit Stack Pointer (R255) used for the internal stack that resides within the 60 general-purpose registers from 04h to 3Fh.

## **General-Purpose Registers (GPR)**

These registers are undefined after the device is powered up. The registers keep their most recent value after any reset, as long as the reset occurs in the  $V_{CC}$  volt-age-specified operating range.

**Note:** Register R254 is designated as a general-purpose register and is set to 00h after any reset or Stop-Mode Recovery.

|             |                         | Vector              |              |

|-------------|-------------------------|---------------------|--------------|

| Name        | Source                  | Location            | Comments     |

| IRQ0        | AN2(P32)                | 0,1                 | External (F) |

|             |                         |                     | Edge         |

| IRQ1        | REF(P33)                | 2,3                 | External (F) |

|             |                         |                     | Edge         |

| IRQ2        | AN1 (P31)               | 4,5                 | External (F) |

|             |                         |                     | Edge         |

| IRQ3        | AN2 (P32)               | 6,7                 | External (R) |

|             |                         |                     | Edge         |

| IRQ4        | Software                | 8,9                 | Internal     |

| IRQ5        | T1                      | 10,11               | Internal     |

| Note: Note: | F = Falling edge trigge | red: R = Rising edg | je triggered |

## IRQ0 - IRQS IRQ IRQ IRQ IRQ INR IMR Global Interrupt Enable Interrupt Priority Logic Vector Select

Figure 17. Interrupt Block Diagram

|              |      |     |     | Lo  | ad Capacit | tor  |      |       |

|--------------|------|-----|-----|-----|------------|------|------|-------|

| -            | 33   | pF  | 56  | pF  | 100        | ) pF | 0.0  | 01 μF |

| Resistor (R) | Α    | В   | Α   | В   | Α          | В    | Α    | В     |

| 5 KΩ         | 7.6  | 1.6 | 3.6 | 1.0 | 2.3        | 0.7  | 0.28 | 0.14  |

| 2 KΩ         | 12.5 | 2.3 | 8.5 | 1.7 | 4.1        | 1.3  | 0.66 | 0.27  |

| 1 KΩ         | 17   | 3.1 | 13  | 2.5 | 9.5        | 1.8  | 1.2  | 0.42  |

#### Table 16. Typical Frequency (MHz) vs. RC Values V<sub>CC</sub> = 5.0 V @ 25°C (Continued)

HALT Mode

This instruction turns off the internal CPU clock but not the crystal oscillation. The counter/timers and external interrupts IRQ0, IRQ1, IRQ2 and IRQ3 remain active. The device is recovered by interrupts, either externally or internally generated. An interrupt request must be executed (enabled) to exit HALT mode. After the interrupt service routine, the program continues from the instruction after the HALT.

• Note: On the C12 ICEBOX, the IRQ3 does not wake the device out of HALT Mode.

**Note:** The device can be recovered by a WDT timeout. The WDT reset in HALT Mode generates a full reset similar to the Normal run mode (not STOP Mode).

#### **STOP Mode**

This instruction turns off the internal clock and external crystal oscillation and reduces the standby current to 10 A. The STOP mode is released by a RESET through a Stop-Mode Recovery (pin P27). A LOW INPUT condition on P27 releases the STOP mode. Program execution begins at location 000C (Hex). Refer to the Watch Dog Timer (WDT) section for information relating to WDT wakeup out of Stop Mode. However, when P27 is used to release STOP mode, the I/O port mode registers are not reconfigured to their default POWER-ON conditions. Thus the I/O, configured as output when the STOP instruction was executed, is prevented from glitching to an unknown state. To use the P27 release approach with STOP mode, use the following instruction:

LD P2M, #1XXX XXXB NOP STOP Note: X = Dependent on user's application.

| 7                  | 6 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------|-----|---|---|---|---|---|

| w w                | W W | W | W | W | W | W |

| eset X             | х х | Х | Х | Х | Х | Х |

| te: W = Write, X = |     |   | Λ | Λ | Λ |   |

Table 21. Port 3 Mode Register, R247 P3M F7h Bank 0h: WRITE ONLY

| Bit<br>Position | Bit Field | R/W | Reset<br>Value | Description                                            |

|-----------------|-----------|-----|----------------|--------------------------------------------------------|

| 7-2             | Reserved  | W   | Х              | Reserved-must be 0                                     |

| 1               | Port 3    | W   | 0              | Port 3 Outputs<br>0: DIGITAL Mode<br>1: ANALOG Mode    |

| 0               | Port 2    | W   | 0              | <b>Port 2 Outputs</b><br>0: Open-Drain<br>1: Push-Pull |

Table 22. Port 0 and 1 Mode Register, R248 P01 F8h Bank 0h: WRITE ONLY

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|---|---|---|---|---|---|

| R/W   | W | W | W | W | W | W | W | W |

| Reset | Х | Х | Х | 0 | Х | 1 | 0 | 1 |

Note: W = Write, X = Indeterminate

| Bit<br>Position | Bit Field | R/W | Reset<br>Value | Description                                  |

|-----------------|-----------|-----|----------------|----------------------------------------------|

| 7-5, 3          | Reserved  | W   | Х              | Reserved-must be 0                           |

| 4               | Reserved  | W   | 0              | Reserved-must be 0                           |

| 2               | Reserved  | W   | Х              | Reserved-must be 1                           |

| 1-0             | P02-P00   | W   | 01             | <b>P02-P00 Mode</b><br>0: Output<br>1: Input |

#### Table 24. Interrupt Request Register, R250 IPR FAh Bank 0h: READ/WRITE

| Bit     | 7       | 6        | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|---------|----------|-----|-----|-----|-----|-----|-----|

| R/W     | R/W     | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset   | 0       | 0        | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: R | = Read, | W = Writ | е   |     |     |     |     |     |

| Bit<br>Position | Bit Field | R/W | Reset<br>Value | Description                                                                                   |

|-----------------|-----------|-----|----------------|-----------------------------------------------------------------------------------------------|

| 7-6             | Reserved  | R/W | 00             | Reserved-must be 0                                                                            |

| 5               | IRQ5      | R/W | 0              | Interrupt<br>IRQ5 = T1<br>0: No interrupt pending<br>1: Interrupt pending                     |

| 4               | IRQ4      | R/W | 0              | Interrupt<br>RQ4 = Software generated<br>0: No interrupt pending<br>1: Interrupt pending      |

| 3               | IRQ3      | R/W | 0              | Interrupt<br>RQ3 = P32 Input (rising edge)<br>0: No interrupt pending<br>1: Interrupt pending |

| 2               | IRQ2      | R/W | 0              | Interrupt<br>RQ2 = P31 Input<br>0: No interrupt pending<br>1: Interrupt pending               |

| 1               | IRQ1,     | R/W | 0              | Interrupt<br>RQ1 = P33 Input<br>0: No interrupt pending<br>1: Interrupt pending               |

| 0               | IRQ0      | R/W | 0              | Interrupt<br>RQ0 = P32 Input<br>0: No interrupt pending<br>1: Interrupt pending               |

#### Table 25. Interrupt Mask Register, R251 IMR FBh Bank 0h: READ/WRITE

| Bit     | 7       | 6        | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|---------|----------|-----|-----|-----|-----|-----|-----|

| R/W     | R/W     | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset   | 0       | 0        | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: R | = Read, | W = Writ | е   |     |     |     |     |     |

| Bit<br>Position | Bit Field                     | R/W | Reset<br>Value | Description                                                     |

|-----------------|-------------------------------|-----|----------------|-----------------------------------------------------------------|

| 7               | Master<br>Interrupt<br>Enable | R/W | 0              | 0: Disables global interrupts*<br>1: Enables global interrupts* |

| 6               | Reserved                      | R/W | Х              | Reserved-must be 0                                              |

| 5-0             | IRQ0-<br>IRQ5                 | R/W | Х              | 1: Enables IRQ0-IRQ5 (D0 = IRQ0)                                |

#### Table 26. Flag Register, R252 FCh Bank 0h: READ/WRITE

| Bit     | 7       | 6         | 5        | 4   | 3   | 2   | 1   | 0   |

|---------|---------|-----------|----------|-----|-----|-----|-----|-----|

| R/W     | R/W     | R/W       | R/W      | R/W | R/W | R/W | R/W | R/W |

| Reset   | 0       | Х         | Х        | Х   | Х   | Х   | Х   | Х   |

| Note: R | = Read, | X= Indete | erminate |     |     |     |     |     |

| Bit                           |                |     | Reset |                     |  |  |  |  |

|-------------------------------|----------------|-----|-------|---------------------|--|--|--|--|

| Position                      | Bit Field      | R/W | Value | Description         |  |  |  |  |

| 7                             | Carry          | R/W | Х     | Carry Flag          |  |  |  |  |

| 6                             | Zero           | R/W | Х     | Zero Flag           |  |  |  |  |

| 5                             | Sign           | R/W | Х     | Sign Flag           |  |  |  |  |

| 4                             | Overflow       | R/W | Х     | Overflow Flag       |  |  |  |  |

| 3                             | Decimal Adjust | R/W | Х     | Decimal Adjust Flag |  |  |  |  |

| 2                             | Half Carry     | R/W | Х     | Half Carry Flag     |  |  |  |  |

| 1                             | User           | R/W | Х     | User Flag F2*       |  |  |  |  |

| 0                             | User           | R/W | Х     | User Flag F1*       |  |  |  |  |

| Note: *Not affected by RESET. |                |     |       |                     |  |  |  |  |

| Bit             |         | 7     | 6        | 5   | 4            | 3         | 2         | 1   | 0   |

|-----------------|---------|-------|----------|-----|--------------|-----------|-----------|-----|-----|

| R/\             | N       | R/W   | R/W      | R/W | R/W          | R/W       | R/W       | R/W | R/W |

| Re              | set     | 0     | 0        | 0   | 0            | 0         | 0         | 0   | 0   |

| Not             | te: R = | Read, | W= Write |     |              |           |           |     |     |

| Bit<br>Position | Bit F   | ield  | R/W      |     | eset<br>Ilue | Descripti | on        |     |     |

| 7-0             | Stac    | k     | R/W      |     | 0            | Stack Poi | (SP0-SP7) |     |     |

#### Table 29. Stack Pointer Low, R255 SPL FFh Bank 0h: READ/WRITE