Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | Coldfire V2                                                |

| Core Size                  | 32-Bit Single-Core                                         |

| Speed                      | 60MHz                                                      |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART        |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 80                                                         |

| Program Memory Size        | 256КВ (256К х 8)                                           |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 32K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                  |

| Data Converters            | A/D 8x12b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 121-LBGA                                                   |

| Supplier Device Package    | 121-MAPBGA (12x12)                                         |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcf52234cvm60 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1 MCF52235 Family Configurations**

| Module                                                                   | 52230               | 52231               | 52232            | 52233               | 52234                     | 52235                     | 52236            |

|--------------------------------------------------------------------------|---------------------|---------------------|------------------|---------------------|---------------------------|---------------------------|------------------|

| Version 2 ColdFire Core with EMAC<br>(Enhanced Multiply-Accumulate Unit) | •                   | •                   | •                | •                   | •                         | •                         | •                |

| System Clock (MHz)                                                       | 60                  | 60                  | 50               | 60                  | 60                        | 60                        | 50               |

| Performance (Dhrystone 2.1 MIPS)                                         | 56                  | 56                  | 46               | 56                  | 56                        | 56                        | 46               |

| Flash / Static RAM (SRAM)                                                | 128/32<br>Kbytes    | 128/32<br>Kbytes    | 128/32<br>Kbytes | 256/32<br>Kbytes    | 256/32<br>Kbytes          | 256/32<br>Kbytes          | 256/32<br>Kbytes |

| Interrupt Controllers (INTC0/INTC1)                                      | •                   | •                   | •                | •                   | •                         | •                         | •                |

| Fast Analog-to-Digital Converter (ADC)                                   | •                   | •                   | •                | •                   | •                         | •                         | •                |

| Random Number Generator and Crypto<br>Acceleration Unit (CAU)            | _                   | _                   | _                |                     | _                         | •                         | —                |

| FlexCAN 2.0B Module                                                      | —                   | •                   | -                | —                   | •                         | •                         | —                |

| Fast Ethernet Controller (FEC) with on-chip interface (EPHY)             | •                   | •                   | •                | •                   | •                         | •                         | •                |

| Four-channel Direct-Memory Access (DMA)                                  | •                   | •                   | •                | •                   | •                         | •                         | •                |

| Software Watchdog Timer (WDT)                                            | •                   | •                   | •                | •                   | •                         | •                         | •                |

| Programmable Interrupt Timer                                             | 2                   | 2                   | 2                | 2                   | 2                         | 2                         | 2                |

| Four-Channel General Purpose Timer                                       | •                   | •                   | •                | •                   | •                         | •                         | •                |

| 32-bit DMA Timers                                                        | 4                   | 4                   | 4                | 4                   | 4                         | 4                         | 4                |

| QSPI                                                                     | •                   | •                   | •                | •                   | •                         | •                         | •                |

| UART(s)                                                                  | 3                   | 3                   | 3                | 3                   | 3                         | 3                         | 3                |

| I <sup>2</sup> C                                                         | •                   | •                   | •                | •                   | •                         | •                         | •                |

| Eight/Four-channel 8/16-bit PWM Timer                                    | •                   | •                   | •                | •                   | •                         | •                         | ٠                |

| General Purpose I/O Module (GPIO)                                        | •                   | •                   | •                | •                   | •                         | •                         | •                |

| Chip Configuration and Reset Controller<br>Module                        | •                   | •                   | ٠                | •                   | •                         | •                         | •                |

| Background Debug Mode (BDM)                                              | •                   | •                   | •                | •                   | •                         | •                         | ٠                |

| JTAG - IEEE 1149.1 Test Access Port <sup>1</sup>                         | •                   | •                   | •                | •                   | •                         | •                         | ٠                |

| Package                                                                  | 80 LQFP<br>112 LQFP | 80 LQFP<br>112 LQFP | 80 LQFP          | 80 LQFP<br>112 LQFP | 112 LQFP<br>121<br>MAPBGA | 112 LQFP<br>121<br>MAPBGA | 80 LQFP          |

#### Table 1. MCF52235 Family Configurations

The full debug/trace interface is available only on the 112- and 121-pin packages. A reduced debug interface is bonded on the 80-pin package.

1

### **1.2.1 Feature Overview**

The MCF52235 family includes the following features:

- Version 2 ColdFire variable-length RISC processor core

- Static operation

- 32-bit address and data paths on-chip

- Up to 60 MHz processor core frequency

- Sixteen general-purpose, 32-bit data and address registers

- Implements ColdFire ISA\_A with extensions to support the user stack pointer register and four new instructions for improved bit processing (ISA\_A+)

- Enhanced Multiply-Accumulate (EMAC) unit with 32-bit accumulator to support  $16 \times 16 \rightarrow 32$  or  $32 \times 32 \rightarrow 32$  operations

- Cryptography Acceleration Unit (CAU)

- Tightly-coupled coprocessor to accelerate software-based encryption and message digest functions

- FIPS-140 compliant random number generator

- Support for DES, 3DES, AES, MD5, and SHA-1 algorithms

- Illegal instruction decode that allows for 68K emulation support

- System debug support

- Real time trace for determining dynamic execution path

- Background debug mode (BDM) for in-circuit debugging (DEBUG\_B+)

- Real time debug support, with six hardware breakpoints (4 PC, 1 address and 1 data) that can be configured into a 1- or 2-level trigger

- On-chip memories

- Up to 32 Kbytes of dual-ported SRAM on CPU internal bus, supporting core and DMA access with standby power supply support

- Up to 256 Kbytes of interleaved Flash memory supporting 2-1-1-1 accesses

- Power management

- Fully static operation with processor sleep and whole chip stop modes

- Rapid response to interrupts from the low-power sleep mode (wake-up feature)

- Clock enable/disable for each peripheral when not used

- Fast Ethernet Controller (FEC)

- 10/100 BaseT/TX capability, half duplex or full duplex

- On-chip transmit and receive FIFOs

- Built-in dedicated DMA controller

- Memory-based flexible descriptor rings

- On-chip Ethernet Transceiver (EPHY)

- Digital adaptive equalization

- Supports auto-negotiation

- Baseline wander correction

- Full-/Half-duplex support in all modes

- Loopback modes

- Supports MDIO preamble suppression

- Jumbo packet

- FlexCAN 2.0B module

# NP

#### MCF52235 Family Configurations

- Based on and includes all existing features of the Freescale TouCAN module

- Full implementation of the CAN protocol specification version 2.0B

- Standard Data and Remote Frames (up to 109 bits long)

- Extended Data and Remote Frames (up to 127 bits long)

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Flexible Message Buffers (MBs), totalling up to 16 message buffers of 0–8 byte data length each, configurable as Rx or Tx, all supporting standard and extended messages

- Unused Message Buffer space can be used as general purpose RAM space

- Listen only mode capability

- Content-related addressing

- No read/write semaphores required

- Three programmable mask registers: global for MBs 0-13, special for MB14, and special for MB15

- Programmable transmit-first scheme: lowest ID or lowest buffer number

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Three universal asynchronous/synchronous receiver transmitters (UARTs)

- 16-bit divider for clock generation

- Interrupt control logic with maskable interrupts

- DMA support

- Data formats can be 5, 6, 7 or 8 bits with even, odd or no parity

- Up to 2 stop bits in 1/16 increments

- Error-detection capabilities

- Modem support includes request-to-send (RTS) and clear-to-send (CTS) lines for two UARTs

- Transmit and receive FIFO buffers

- I<sup>2</sup>C module

- Interchip bus interface for EEPROMs, LCD controllers, A/D converters, and keypads

- Fully compatible with industry-standard I<sup>2</sup>C bus

- Master and slave modes support multiple masters

- Automatic interrupt generation with programmable level

- Queued serial peripheral interface (QSPI)

- Full-duplex, three-wire synchronous transfers

- Up to four chip selects available

- Master mode operation only

- Programmable bit rates up to half the CPU clock frequency

- Up to 16 pre-programmed transfers

- Fast analog-to-digital converter (ADC)

- Eight analog input channels

- 12-bit resolution

- Minimum 1.125  $\mu$ s conversion time

- Simultaneous sampling of two channels for motor control applications

- Single-scan or continuous operation

- Optional interrupts on conversion complete, zero crossing (sign change), or under/over low/high limit

- Unused analog channels can be used as digital I/O

### MCF52235 Family Configurations

- Unique vector number for each interrupt source

- Ability to mask any individual interrupt source or all interrupt sources (global mask-all)

- Support for hardware and software interrupt acknowledge (IACK) cycles

- Combinatorial path to provide wake-up from low power modes

- DMA controller

- Four fully programmable channels

- Dual-address transfer support with 8-, 16-, and 32-bit data capability, along with support for 16-byte (4 x 32-bit) burst transfers

- Source/destination address pointers that can increment or remain constant

- 24-bit byte transfer counter per channel

- Auto-alignment transfers supported for efficient block movement

- Bursting and cycle steal support

- Software-programmable DMA requesters for the UARTs (3) and 32-bit timers (4)

- Reset

- Separate reset in and reset out signals

- Seven sources of reset:

- Power-on reset (POR)

- External

- Software

- Watchdog

- Loss of clock

- Loss of lock

- Low-voltage detection (LVD)

- Status flag indication of source of last reset

- Chip integration module (CIM)

- System configuration during reset

- Selects one of three clock modes

- Configures output pad drive strength

- Unique part identification number and part revision number

- General purpose I/O interface

- Up to 56 bits of general purpose I/O

- Bit manipulation supported via set/clear functions

- Programmable drive strengths

- Unused peripheral pins may be used as extra GPIO

- JTAG support for system level board testing

### 1.2.2 V2 Core Overview

The version 2 ColdFire processor core is comprised of two separate pipelines decoupled by an instruction buffer. The two-stage instruction fetch pipeline (IFP) is responsible for instruction-address generation and instruction fetch. The instruction buffer is a first-in-first-out (FIFO) buffer that holds prefetched instructions awaiting execution in the operand execution pipeline (OEP). The OEP includes two pipeline stages. The first stage decodes instructions and selects operands (DSOC); the second stage (AGEX) performs instruction execution and calculates operand effective addresses, if needed.

The V2 core implements the ColdFire instruction set architecture revision A+ with added support for a separate user stack pointer register and four new instructions to assist in bit processing. Additionally, the MCF52235 core includes the enhanced multiply-accumulate (EMAC) unit for improved signal processing capabilities. The EMAC implements a three-stage arithmetic

MCF52235 Family Configurations

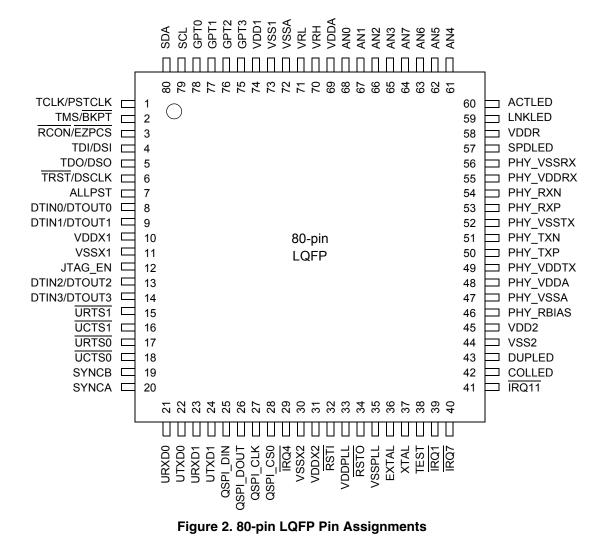

### 1.2.24 Package Pinouts

Figure 2 shows the pinout configuration for the 80-pin LQFP.

Figure 3 shows the pinout configuration for the 112-pin LQFP.

| С |

|---|

| D |

| E |

| F |

| G |

| Н |

| J |

| к |

| L |

|   |

|   |

| - | 1      | 2      | 3      | 4         | 5        | 6      | 7      | 8        | 9         | 10        | 11        |

|---|--------|--------|--------|-----------|----------|--------|--------|----------|-----------|-----------|-----------|

| A | TCLK   | SDA    | SCL    | IRQ15     | IRQ14    | IRQ13  | VSSA   | VDDA     | AN1       | AN7       | AN5       |

| В | TMS    | RCON   | GPT0   | GPT3      | PWM5     | PWM1   | VRL    | VRH      | AN2       | AN6       | AN4       |

| С | TRST   | TDO    | TDI    | GPT2      | PWM7     | PWM3   | IRQ12  | ANO      | AN3       | LNKLED    | ACTLED    |

| D | DTIN1  | DTIN0  | ALLPST | GPT1      | VDDX     | VDDX   | VDD    | VDDR     | PST2      | PST3      | SPDLED    |

| Е | DDATA3 | IRQ9   | IRQ8   | VSS       | VSS      | VDDX   | VSS    | VDD      | PST0      | PST1      | PHY_RXN   |

| F | DDATA0 | DDATA1 | DDATA2 | VSS       | VSS      | VSS    | VSS    | VSS      | PHY_VSSRX | PHY_VDDRX | PHY_RXP   |

| G | DTIN2  | IRQ5   | IRQ6   | JTAG_EN   | VDDX     | VDDX   | VDDX   | PHY_VSSA | PHY_VSSTX | PHY_VDDTX | PHY_TXP   |

| Н | DTIN3  | URTS0  | URTS1  | QSPI_DIN  | QSPI_CS1 | VDDX   | TEST   | TXLED    | RXLED     | PHY_VDDA  | PHY_TXN   |

| J | SYNCB  | UCTS0  | UCTS1  | QSPI_DOUT | QSPI_CS2 | RSTI   | XTAL   | IRQ1     | COLLED    | DUPLED    | PHY_RBIAS |

| к | SYNCA  | URXD0  | URXD1  | QSPI_CLK  | QSPI_CS3 | VDDPLL | VSSPLL | IRQ2     | IRQ11     | URTS2     | URXD2     |

| L | IRQ10  | UTXD0  | UTXD1  | QSPI_CS0  | IRQ4     | RSTO   | EXTAL  | IRQ3     | IRQ7      | UCTS2     | UTXD2     |

Figure 4. 121 MAPBGA Pin Assignments

16

| N |   |  |  |

|---|---|--|--|

|   | _ |  |  |

18

| Pin Group               | Primary<br>Function    | SecondaryF<br>unction | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength/<br>Control <sup>1</sup> | Wired OR<br>Control | Pull-up/<br>Pull-down <sup>2</sup> | Pin on 121<br>MAPBGA | Pin on 112<br>LQFP | Pin on 80<br>LQFP |

|-------------------------|------------------------|-----------------------|----------------------|------------------------|--------------------------------------------|---------------------|------------------------------------|----------------------|--------------------|-------------------|

| Ethernet                | ACTLED                 | _                     | —                    | PLD[0]                 | PDSR[32]                                   | PWOR[8]             |                                    | C11                  | 84                 | 60                |

| LEDs                    | COLLED                 | —                     | _                    | PLD[4]                 | PDSR[36]                                   | PWOR[12]            | —                                  | J9                   | 58                 | 42                |

|                         | DUPLED                 | —                     | _                    | PLD[3]                 | PDSR[35]                                   | PWOR[11]            | —                                  | J10                  | 59                 | 43                |

|                         | LNKLED                 | —                     | _                    | PLD[1]                 | PDSR[33]                                   | PWOR[9]             | —                                  | C10                  | 83                 | 59                |

|                         | SPDLED                 | —                     | _                    | PLD[2]                 | PDSR[34]                                   | PWOR[10]            | —                                  | D11                  | 81                 | 57                |

|                         | RXLED                  | —                     | _                    | PLD[5]                 | PDSR[37]                                   | PWOR[13]            | —                                  | H9                   | 52                 |                   |

|                         | TXLED                  | —                     | —                    | PLD[6]                 | PDSR[38]                                   | PWOR[14]            | —                                  | H8                   | 51                 |                   |

|                         | VDDR                   | —                     | _                    | —                      | —                                          | —                   | —                                  | D8                   | 82                 | 58                |

| Ethernet                | PHY_RBIAS              | —                     | _                    | —                      | —                                          | _                   |                                    | J11                  | 66                 | 46                |

| PHY                     | PHY_RXN                | —                     | —                    | —                      | —                                          | —                   |                                    | E11                  | 74                 | 54                |

|                         | PHY_RXP                | —                     | _                    | —                      | —                                          | —                   |                                    | F11                  | 73                 | 53                |

|                         | PHY_TXN                | —                     | —                    | —                      | —                                          |                     |                                    | H11                  | 71                 | 51                |

|                         | PHY_TXP                | —                     | —                    | —                      | —                                          | _                   |                                    | G11                  | 70                 | 50                |

|                         | PHY_VDDA <sup>5</sup>  | —                     | —                    | —                      |                                            | N/A                 |                                    | H10                  | 68                 | 48                |

|                         | PHY_VDDRX <sup>5</sup> | —                     | —                    | —                      |                                            | N/A                 |                                    | F10                  | 75                 | 55                |

|                         | PHY_VDDTX <sup>5</sup> | —                     | —                    | —                      |                                            | N/A                 |                                    | G10                  | 69                 | 49                |

|                         | PHY_VSSA               | —                     | —                    | —                      |                                            | N/A                 |                                    | G8                   | 67                 | 47                |

|                         | PHY_VSSRX              | —                     | —                    | —                      |                                            | N/A                 |                                    | F9                   | 76                 | 56                |

|                         | PHY_VSSTX              | —                     |                      | —                      |                                            | N/A                 |                                    | G9                   | 72                 | 52                |

| l <sup>2</sup> C        | SCL                    | CANTX <sup>4</sup>    | UTXD2                | PAS[0]                 | PDSR[0]                                    |                     | Pull-Up <sup>6</sup>               | A3                   | 111                | 79                |

|                         | SDA                    | CANRX <sup>4</sup>    | URXD2                | PAS[1]                 | PDSR[0]                                    |                     | Pull-Up <sup>6</sup>               | A2                   | 112                | 80                |

| Interrupts <sup>3</sup> | IRQ15                  | —                     | —                    | PGP[7]                 | PSDR[47]                                   |                     | Pull-Up <sup>6</sup>               | A4                   | 106                |                   |

|                         | IRQ14                  | —                     | —                    | PGP[6]                 | PSDR[46]                                   | —                   | Pull-Up <sup>6</sup>               | A5                   | 105                |                   |

|                         | IRQ13                  | —                     | —                    | PGP[5]                 | PSDR[45]                                   |                     | Pull-Up <sup>6</sup>               | A6                   | 98                 |                   |

|                         | IRQ12                  | —                     |                      | PGP[4]                 | PSDR[44]                                   |                     | Pull-Up <sup>6</sup>               | C7                   | 97                 |                   |

MCF52235 ColdFire Microcontroller, Rev. 10

| Pin Group               | Primary<br>Function | SecondaryF<br>unction | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength/<br>Control <sup>1</sup> | Wired OR<br>Control | Pull-up/<br>Pull-down <sup>2</sup> | Pin on 121<br>MAPBGA | Pin on 112<br>LQFP | Pin on 80<br>LQFP |

|-------------------------|---------------------|-----------------------|----------------------|------------------------|--------------------------------------------|---------------------|------------------------------------|----------------------|--------------------|-------------------|

| Continued               | IRQ11               |                       |                      | PGP[3]                 | PSDR[43]                                   | _                   | Pull-Up <sup>6</sup>               | K9                   | 57                 | 41                |

| Interrupts <sup>3</sup> | IRQ10               | —                     | —                    | PGP[2]                 | PSDR[42]                                   | _                   | Pull-Up <sup>6</sup>               | L1                   | 29                 | —                 |

|                         | IRQ9                | —                     | _                    | PGP[1]                 | PSDR[41]                                   | —                   | Pull-Up <sup>6</sup>               | E2                   | 11                 | —                 |

|                         | IRQ8                | —                     | _                    | PGP[0]                 | PSDR[40]                                   |                     | Pull-Up                            | E3                   | 10                 | —                 |

|                         | IRQ7                | —                     | _                    | PNQ[7]                 | Low                                        | —                   | Pull-Up <sup>6</sup>               | L9                   | 56                 | 40                |

|                         | IRQ6                | —                     | FEC_RXER             | PNQ[6]                 | Low                                        | —                   | Pull-Up <sup>6</sup>               | G3                   | 19                 | —                 |

| -                       | IRQ5                | —                     | FEC_RXD[1]           | PNQ[5]                 | Low                                        | —                   | Pull-Up <sup>6</sup>               | G2                   | 20                 | —                 |

|                         | IRQ4                | —                     | —                    | PNQ[4]                 | Low                                        | _                   | Pull-Up <sup>6</sup>               | L5                   | 41                 | 29                |

|                         | IRQ3                | —                     | FEC_RXD[2]           | PNQ[3]                 | Low                                        | —                   | Pull-Up <sup>6</sup>               | L8                   | 53                 | —                 |

|                         | IRQ2                | —                     | FEC_RXD[3]           | PNQ[2]                 | Low                                        | —                   | Pull-Up <sup>6</sup>               | K8                   | 54                 | —                 |

|                         | IRQ1                | SYNCA                 | PWM1                 | PNQ[1]                 | High                                       | _                   | Pull-Up <sup>6</sup>               | J8                   | 55                 | 39                |

| JTAG/BDM                | JTAG_EN             | —                     | _                    | —                      | N/A                                        | N/A                 | Pull-Down                          | G4                   | 18                 | 12                |

|                         | TCLK/<br>PSTCLK     | CLKOUT                | _                    | _                      | High                                       | —                   | Pull-Up <sup>7</sup>               | A1                   | 1                  | 1                 |

|                         | TDI/DSI             | —                     | _                    | _                      | N/A                                        | N/A                 | Pull-Up <sup>7</sup>               | C3                   | 4                  | 4                 |

|                         | TDO/DSO             | —                     | _                    | —                      | High                                       | N/A                 | —                                  | C2                   | 5                  | 5                 |

|                         | TMS/BKPT            | —                     | _                    | —                      | N/A                                        | N/A                 | Pull-Up <sup>7</sup>               | B1                   | 2                  | 2                 |

|                         | TRST/DSCLK          | —                     | _                    | —                      | N/A                                        | N/A                 | Pull-Up                            | C1                   | 6                  | 6                 |

| Mode<br>Selection       | RCON/EZPCS          | _                     | _                    | _                      | N/A                                        | N/A                 | Pull-Up                            | B2                   | 3                  | 3                 |

| PWM                     | PWM7                | —                     | _                    | PTD[3]                 | PDSR[31]                                   | _                   | —                                  | C5                   | 104                | —                 |

|                         | PWM5                | —                     | _                    | PTD[2]                 | PDSR[30]                                   | _                   | —                                  | B5                   | 103                | —                 |

|                         | PWM3                | —                     | _                    | PTD[1]                 | PDSR[29]                                   | _                   | —                                  | C6                   | 100                | —                 |

|                         | PWM1                | _                     | _                    | PTD[0]                 | PDSR[28]                                   | _                   | —                                  | B6                   | 99                 | —                 |

### Table 3. Pin Functions by Primary and Alternate Purpose (continued)

19

| Pin Group           | Primary<br>Function | SecondaryF<br>unction | Tertiary<br>Function | Quaternary<br>Function | Drive<br>Strength/<br>Control <sup>1</sup> | Wired OR<br>Control | Pull-up/<br>Pull-down <sup>2</sup> | Pin on 121<br>MAPBGA             | Pin on 112<br>LQFP | Pin on 80<br>LQFP |

|---------------------|---------------------|-----------------------|----------------------|------------------------|--------------------------------------------|---------------------|------------------------------------|----------------------------------|--------------------|-------------------|

| UART 1 <sup>3</sup> | UCTS1               | SYNCA                 | URXD2                | PUB[3]                 | PDSR[15]                                   |                     | _                                  | J3                               | 24                 | 16                |

| -                   | URTS1               | SYNCB                 | UTXD2                | PUB[2]                 | PDSR[14]                                   | —                   | —                                  | H3                               | 23                 | 15                |

| -                   | URXD1               | —                     | FEC_TXD[0]           | PUB[1]                 | PDSR[13]                                   | PWOR[2]             | —                                  | КЗ                               | 32                 | 23                |

|                     | UTXD1               | —                     | FEC_COL              | PUB[0]                 | PDSR[12]                                   | PWOR[3]             | —                                  | L3                               | 33                 | 24                |

| UART 2              | UCTS2               | —                     | —                    | PUC[3]                 | PDSR[27]                                   | —                   | —                                  | L10                              | 61                 | —                 |

| -                   | URTS2               | —                     | —                    | PUC[2]                 | PDSR[26]                                   | —                   | —                                  | K10                              | 60                 | —                 |

| -                   | URXD2               | —                     | —                    | PUC[1]                 | PDSR[25]                                   | _                   | —                                  | K11                              | 62                 | —                 |

| -                   | UTXD2               | —                     | —                    | PUC[0]                 | PDSR[24]                                   | —                   | —                                  | L11                              | 63                 | —                 |

| FlexCAN             | SYNCA               | CANTX <sup>4</sup>    | FEC_MDIO             | PAS[3]                 | PDSR[39]                                   | _                   | —                                  | —                                | 28                 | 20                |

| -                   | SYNCB               | CANRX <sup>4</sup>    | FEC_MDC              | PAS[2]                 | PDSR[39]                                   | —                   | —                                  | —                                | 27                 | 19                |

| VDD <sup>5,11</sup> | VDD                 | —                     | —                    | —                      | N/A                                        | N/A                 | —                                  | D7, E8                           | 65,102             | 45,74             |

| VDDX                | VDDX                | —                     | _                    | _                      | N/A                                        | N/A                 | _                                  | D5, D6, E6, G5,<br>G6, G7, H6    | 14, 43             | 10, 31            |

| VSS                 | VSS                 | -                     | _                    |                        | N/A                                        | N/A                 | —                                  | E4, E5, E7,F4,<br>F5, F6, F7, F8 | 64,101             | 44,73             |

| VSSX                | VSSX                | —                     | _                    |                        | N/A                                        | N/A                 | —                                  | —                                | 15, 42             | 11, 30            |

#### Table 3. Pin Functions by Primary and Alternate Purpose (continued)

<sup>1</sup> The PDSR and PSSR registers are described in Chapter 14, "General Purpose I/O Module. All programmable signals default to 2mA drive in normal (single-chip) mode.

<sup>2</sup> All signals have a pull-up in GPIO mode.

<sup>3</sup> The use of an external PHY limits ADC, interrupt, and QSPI functionality. It also disables the UART0/1 and timer pins.

<sup>4</sup> The multiplexed CANTX and CANRX signals do not have dedicated pins, but are available as muxed replacements for other signals.

<sup>5</sup> The VDD1, VDD2, VDDPLL, and PHY VDD pins are for decoupling only and should not have power directly applied to them.

<sup>6</sup> For primary and GPIO functions only.

<sup>7</sup> Only when JTAG mode is enabled.

<sup>8</sup> For secondary and GPIO functions only.

<sup>9</sup> RSTI has an internal pull-up resistor; however, the use of an external resistor is strongly recommended.

<sup>10</sup> For GPIO function. Primary Function has pull-up control within the GPT module.

<sup>11</sup> This list for power and ground does not include those dedicated power/ground pins included elsewhere, e.g. in the Ethernet PHY.

### 1.12 ADC Signals

Table 13 describes the signals of the Analog-to-Digital Converter.

Table 13. ADC Signals

| Signal Name      | Abbreviation     | Function                                          | I/O |

|------------------|------------------|---------------------------------------------------|-----|

| Analog Inputs    | AN[7:0]          | Inputs to the A-to-D converter.                   | I   |

| Analog Reference | V <sub>RH</sub>  | Reference voltage high and low inputs.            | I   |

|                  | V <sub>RL</sub>  |                                                   | I   |

| Analog Supply    | V <sub>DDA</sub> | Isolate the ADC circuitry from power supply noise | —   |

|                  | V <sub>SSA</sub> |                                                   |     |

### 1.13 General Purpose Timer Signals

Table 14 describes the General Purpose Timer Signals.

#### Table 14. GPT Signals

| Signal Name                           | Abbreviation | Function                                                    | I/O |

|---------------------------------------|--------------|-------------------------------------------------------------|-----|

| General Purpose Timer<br>Input/Output | GPT[3:0]     | Inputs to or outputs from the general purppose timer module | I/O |

### 1.14 Pulse Width Modulator Signals

Table 15 describes the PWM signals.

#### Table 15. PWM Signals

| Signal Name     | Abbreviation  | Function                                      | I/O |

|-----------------|---------------|-----------------------------------------------|-----|

| PWM Output Chan | nels PWM[7:0] | Pulse width modulated output for PWM channels | 0   |

### 1.15 Debug Support Signals

These signals are used as the interface to the on-chip JTAG controller and also to interface to the BDM logic.

#### Table 16. Debug Support Signals

| Signal Name      | Abbreviation | Function                                                                                | I/O |

|------------------|--------------|-----------------------------------------------------------------------------------------|-----|

| JTAG Enable      | JTAG_EN      | Select between debug module and JTAG signals at reset                                   | Ι   |

| Test Reset       | TRST         | This active-low signal is used to initialize the JTAG logic asynchronously.             | I   |

| Test Clock       | TCLK         | Used to synchronize the JTAG logic.                                                     | Ι   |

| Test Mode Select | TMS          | Used to sequence the JTAG state machine. TMS is sampled on the rising edge of TCLK.     | I   |

| Test Data Input  | TDI          | Serial input for test instructions and data. TDI is sampled on the rising edge of TCLK. | I   |

### 2.3 DC Electrical Specifications

Table 22. DC Electrical Specifications <sup>1</sup>

| Characteristic                                                                                                                                                                          | Symbol              | Min                   | Max                    | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------------|------|

| Supply voltage                                                                                                                                                                          | V <sub>DD</sub>     | 3.0                   | 3.6                    | V    |

| Input high voltage                                                                                                                                                                      | V <sub>IH</sub>     | $0.7 \times V_{DD}$   | 4.0                    | V    |

| Input low voltage                                                                                                                                                                       | V <sub>IL</sub>     | $V_{SS} - 0.3$        | 0.35 x V <sub>DD</sub> | V    |

| Input hysteresis                                                                                                                                                                        | V <sub>HYS</sub>    | $0.06 \times V_{DD}$  | _                      | mV   |

| Low-voltage detect trip voltage (V <sub>DD</sub> falling)                                                                                                                               | V <sub>LVD</sub>    | 2.15                  | 2.3                    | V    |

| Low-voltage detect hysteresis (V <sub>DD</sub> rising)                                                                                                                                  | V <sub>LVDHYS</sub> | 60                    | 120                    | mV   |

| Input leakage current<br>$V_{in} = V_{DD}$ or $V_{SS}$ , input-only pins                                                                                                                | l <sub>in</sub>     | -1.0                  | 1.0                    | μΑ   |

| High impedance (off-state) leakage current $V_{in} = V_{DD}$ or $V_{SS}$ , all input/output and output pins                                                                             | I <sub>OZ</sub>     | -1.0                  | 1.0                    | μA   |

| Output high voltage (all input/output and all output pins) $I_{OH} = -2.0 \text{ mA}$                                                                                                   | V <sub>OH</sub>     | V <sub>DD</sub> - 0.5 |                        | V    |

| Output low voltage (all input/output and all output pins) $I_{OL} = 2.0 \text{ mA}$                                                                                                     | V <sub>OL</sub>     |                       | 0.5                    | V    |

| Weak internal pull-up device current, tested at V <sub>IL</sub> max. <sup>2</sup>                                                                                                       | I <sub>APU</sub>    | -10                   | -130                   | μA   |

| Input capacitance <sup>3</sup><br>All input-only pins<br>All input/output (three-state) pins                                                                                            | C <sub>in</sub>     |                       | 7<br>7                 | pF   |

| Load capacitance <sup>4</sup><br>Low drive strength<br>High drive strength                                                                                                              | CL                  |                       | 25<br>50               | pF   |

| DC injection current <sup>3, 5, 6, 7</sup><br>$V_{NEGCLAMP} = V_{SS} - 0.3 V$ , $V_{POSCLAMP} = V_{DD} + 0.3$<br>Single pin limit<br>Total MCU limit, Includes sum of all stressed pins | IIC                 | -1.0<br>-10           | 1.0<br>10              | mA   |

<sup>1</sup> Refer to Table 25 for additional PLL specifications.

<sup>2</sup> Refer to Table 3 for pins with internal pull-up devices.

<sup>3</sup> This parameter is characterized before qualification rather than 100% tested.

<sup>4</sup> pF load ratings are based on DC loading and are provided as an indication of driver strength. High speed interfaces require transmission line analysis to determine proper drive strength and termination.

<sup>5</sup> All functional non-supply pins are internally clamped to V<sub>SS</sub> and their respective V<sub>DD</sub>.

<sup>6</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

<sup>7</sup> The power supply must maintain regulation within operating  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure that the external  $V_{DD}$  load shunts current greater than maximum injection current. This is the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low which would reduce overall power consumption. Also, the system clock is not present during the power-up sequence until the PLL has attained lock.

|                                                             |                                                         |                                   | Тур                                | vical                                  |                                         |            |          |

|-------------------------------------------------------------|---------------------------------------------------------|-----------------------------------|------------------------------------|----------------------------------------|-----------------------------------------|------------|----------|

| Characteristic                                              | Symbol                                                  | Running from<br>SRAM,<br>EPHY Off | Running from<br>Flash,<br>EPHY Off | Running from<br>Flash, EPHY<br>10BaseT | Running from<br>Flash, EPHY<br>100BaseT | Peak       | Unit     |

| Active current, core and I/O<br>PLL @25 MHz<br>PLL @60 MHz  | I <sub>DDR</sub> +I <sub>DDX</sub><br>+I <sub>DDA</sub> | 75<br>130                         | 82<br>138                          | 150<br>220                             | 260<br>310                              | 290<br>340 | mA       |

| Analog supply current<br>Normal operation<br>Low-power STOP | I <sub>DDA</sub>                                        | 20<br>15                          | 20<br>15                           | 20<br>15                               | 20<br>15                                | 30<br>50   | mA<br>μA |

#### **Table 23. Active Current Consumption Specifications**

#### Table 24. Current Consumption Specifications in Low-Power Modes<sup>1</sup>

| Mode <sup>2</sup>           | PLL @25 MHz<br>(typical) <sup>3</sup> | PLL @60 MHz<br>(typical) <sup>3</sup> | PLL @60 MHz<br>(peak) <sup>4</sup> | Unit |     |  |     |    |

|-----------------------------|---------------------------------------|---------------------------------------|------------------------------------|------|-----|--|-----|----|

| STOP mode 3 (STPMD[1:0]=11) | 0.2                                   |                                       | 0.2                                |      | 0.2 |  | 1.0 | mA |

| STOP mode 2 (STPMD[1:0]=10) | 7                                     |                                       | 7                                  |      | —   |  |     |    |

| STOP mode 1 (STPMD[1:0]=01) | 10                                    | 12                                    | —                                  |      |     |  |     |    |

| STOP mode 0 (STPMD[1:0]=00) | 10                                    | 12                                    | —                                  |      |     |  |     |    |

| WAIT                        | 16                                    | 27                                    | —                                  |      |     |  |     |    |

| DOZE                        | 16                                    | 27                                    | —                                  |      |     |  |     |    |

| RUN                         | 25                                    | 45                                    | —                                  |      |     |  |     |    |

<sup>1</sup> All values are measured with a 3.30 V power supply.

<sup>2</sup> Refer to the "Power Management" chapter in the *MCF52235 ColdFire<sup>®</sup> Integrated Microcontroller Reference Manual* for more information on low-power modes.

<sup>4</sup> These values were obtained with CLKOUT and all peripheral clocks enabled. All code was executed from flash memory.

<sup>&</sup>lt;sup>3</sup> These values were obtained with CLKOUT and all peripheral clocks except for the CFM clock disabled prior to entering low-power mode. The tests were performed at room temperature. All code was executed from flash memory; running code from SRAM further reduces power consumption.

- <sup>7</sup> This value has been updated

- <sup>8</sup> Load capacitance determined from crystal manufacturer specifications and include circuit board parasitics.

- <sup>9</sup> Assuming a reference is available at power up, lock time is measured from the time V<sub>DD</sub> and V<sub>DDPLL</sub> are valid to RSTO negating. If the crystal oscillator is the reference for the PLL, the crystal start up time must be added to the PLL lock time to determine the total start-up time.

- <sup>10</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>sys</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via V<sub>DDPLL</sub> and V<sub>SSPLL</sub> and variation in crystal oscillator frequency increase the C<sub>jitter</sub> percentage for a given interval

- $^{11}$  Based on slow system clock of 40 MHz measured at  $\rm f_{sys}$  max.

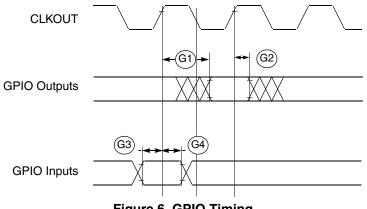

### 2.5 General Purpose I/O Timing

GPIO can be configured for certain pins of the QSPI, timers, UARTs, FEC, and interrupts. When in GPIO mode, the timing specification for these pins is given in Table 26 and Figure 6.

The GPIO timing is met under the following load test conditions:

- 50 pF / 50  $\Omega$  for high drive

- $25 \text{ pF} / 25 \Omega$  for low drive

#### Table 26. GPIO Timing

| Num | Characteristic                     | Symbol             | Min | Мах | Unit |

|-----|------------------------------------|--------------------|-----|-----|------|

| G1  | CLKOUT high to GPIO output valid   | t <sub>CHPOV</sub> | _   | 10  | ns   |

| G2  | CLKOUT high to GPIO output invalid | t <sub>CHPOI</sub> | 1.5 |     | ns   |

| G3  | GPIO input valid to CLKOUT high    | t <sub>PVCH</sub>  | 9   | —   | ns   |

| G4  | CLKOUT high to GPIO input invalid  | t <sub>CHPI</sub>  | 1.5 | —   | ns   |

Figure 6. GPIO Timing

### 2.8 EPHY Parameters

### 2.8.1 EPHY Timing

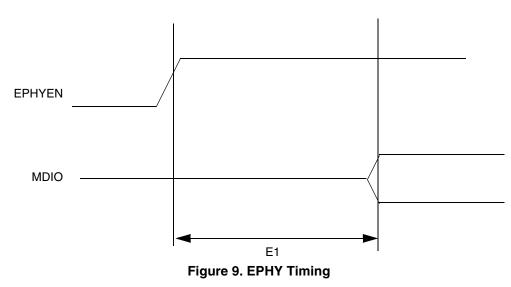

Table 30 and Figure 9 show the relevant EPHY timing parameters.

#### **Table 30. EPHY Timing Parameters**

| Num | Characteristic    | Symbol                | Value | Unit |

|-----|-------------------|-----------------------|-------|------|

| E1  | EPHY startup time | t <sub>Start-Up</sub> | 360   | μs   |

### 2.8.2 10BASE-T SQE (Heartbeat) Timing

Table 31 and Figure 10 show the relevant 10BASE-T SQE (heartbeat) timing parameters.

Table 31. 10BASE-T SQE (Heartbeat) Timing Parameters

| Characteristic                 | Symbol | Min | Typ <sup>1</sup> | Max | Units |

|--------------------------------|--------|-----|------------------|-----|-------|

| COL (SQE) delay after TXEN off | t1     | _   | 1.0              | _   | μs    |

| COL (SQE) pulse duration       | t2     |     | 1.0              | _   | μs    |

<sup>1</sup> Typical values are at 25°C.

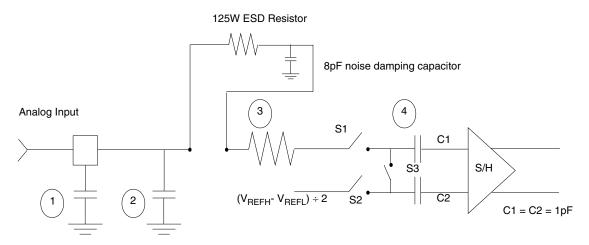

- <sup>1</sup> Parasitic capacitance due to package, pin-to-pin and pin-to-package base coupling; 1.8pF

- <sup>2</sup> Parasitic capacitance due to the chip bond pad, ESD protection devices and signal routing; 2.04pF

- <sup>3</sup> Equivalent resistance for the channel select mux; 100 ohms

- <sup>4</sup> Sampling capacitor at the sample and hold circuit. Capacitor C1 is normally disconnected from the input and is only connected to it at sampling time; 1.4pF

- <sup>5</sup> Equivalent input impedance, when the input is selected = \_\_\_\_\_\_\_ADC CL

C CLOCK RATE

$$\times (1.4 \times 10^{-12})$$

#### Figure 12. Equivalent Circuit for A/D Loading

### 2.10 DMA Timers Timing Specifications

Table 36 lists timer module AC timings.

#### **Table 36. Timer Module AC Timing Specifications**

| Name | Characteristic <sup>1</sup>               | Min                | Max | Unit |

|------|-------------------------------------------|--------------------|-----|------|

| T1   | DTIN0 / DTIN1 / DTIN2 / DTIN3 cycle time  | $3 \times t_{CYC}$ | _   | ns   |

| T2   | DTIN0 / DTIN1 / DTIN2 / DTIN3 pulse width | $1 \times t_{CYC}$ |     | ns   |

<sup>1</sup> All timing references to CLKOUT are given to its rising edge.

### 2.11 EzPort Electrical Specifications

#### **Table 37. EzPort Electrical Specifications**

| Name | Characteristic                                         | Min                | Max                  | Unit |

|------|--------------------------------------------------------|--------------------|----------------------|------|

| EP1  | EPCK frequency of operation (all commands except READ) | _                  | f <sub>sys</sub> / 2 | MHz  |

| EP1a | EPCK frequency of operation (READ command)             | _                  | f <sub>sys</sub> / 8 | MHz  |

| EP2  | EPCS_b negation to next EPCS_b assertion               | $2 \times T_{cyc}$ |                      | ns   |

| EP3  | EPCS_B input valid to EPCK high (setup)                | 5                  |                      | ns   |

| EP4  | EPCK high to EPCS_B input invalid (hold)               | 5                  |                      | ns   |

| EP5  | EPD input valid to EPCK high (setup)                   | 2                  | _                    | ns   |

| EP6  | EPCK high to EPD input invalid (hold)                  | 5                  | _                    | ns   |

| Name | Characteristic                            | Min | Max | Unit |

|------|-------------------------------------------|-----|-----|------|

| EP7  | EPCK low to EPQ output valid (out setup)  |     | 12  | ns   |

| EP8  | EPCK low to EPQ output invalid (out hold) | 0   | —   | ns   |

| EP9  | EPCS_B negation to EPQ tri-state          | _   | 12  | ns   |

#### Table 37. EzPort Electrical Specifications (continued)

### 2.12 **QSPI Electrical Specifications**

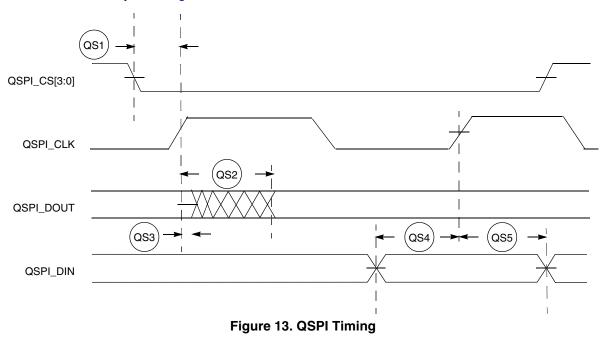

Table 38 lists QSPI timings.

| Table 38 | . QSPI Modu | les AC Timing | Specifications |

|----------|-------------|---------------|----------------|

|----------|-------------|---------------|----------------|

| Name | Characteristic                                   | Min | Max | Unit             |

|------|--------------------------------------------------|-----|-----|------------------|

| QS1  | QSPI_CS[3:0] to QSPI_CLK                         | 1   | 510 | t <sub>CYC</sub> |

| QS2  | QSPI_CLK high to QSPI_DOUT valid                 | _   | 10  | ns               |

| QS3  | QSPI_CLK high to QSPI_DOUT invalid (output hold) | 2   | _   | ns               |

| QS4  | QSPI_DIN to QSPI_CLK (input setup)               | 9   | _   | ns               |

| QS5  | QSPI_DIN to QSPI_CLK (input hold)                | 9   |     | ns               |

The values in Table 38 correspond to Figure 13.

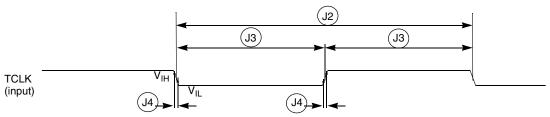

## 2.13 JTAG and Boundary Scan Timing

Table 39. JTAG and Boundary Scan Timing

| Num | Characteristics <sup>1</sup>                       | Symbol              | Min                | Max | Unit               |

|-----|----------------------------------------------------|---------------------|--------------------|-----|--------------------|

| J1  | TCLK frequency of operation                        | f <sub>JCYC</sub>   | DC                 | 1/4 | f <sub>sys/2</sub> |

| J2  | TCLK cycle period                                  | t <sub>JCYC</sub>   | $4 \times t_{CYC}$ | —   | ns                 |

| J3  | TCLK clock pulse width                             | t <sub>JCW</sub>    | 26                 | —   | ns                 |

| J4  | TCLK rise and fall times                           | t <sub>JCRF</sub>   | 0                  | 3   | ns                 |

| J5  | Boundary scan input data setup time to TCLK rise   | t <sub>BSDST</sub>  | 4                  | —   | ns                 |

| J6  | Boundary scan input data hold time after TCLK rise | t <sub>BSDHT</sub>  | 26                 | —   | ns                 |

| J7  | TCLK low to boundary scan output data valid        | t <sub>BSDV</sub>   | 0                  | 33  | ns                 |

| J8  | TCLK low to boundary scan output high Z            | t <sub>BSDZ</sub>   | 0                  | 33  | ns                 |

| J9  | TMS, TDI input data setup time to TCLK rise        | t <sub>TAPBST</sub> | 4                  | —   | ns                 |

| J10 | TMS, TDI input data hold time after TCLK rise      | t <sub>TAPBHT</sub> | 10                 | —   | ns                 |

| J11 | TCLK low to TDO data valid                         | t <sub>TDODV</sub>  | 0                  | 26  | ns                 |

| J12 | TCLK low to TDO high Z                             | t <sub>TDODZ</sub>  | 0                  | 8   | ns                 |

| J13 | TRST assert time                                   | t <sub>TRSTAT</sub> | 100                | —   | ns                 |

| J14 | TRST setup time (negation) to TCLK high            | t <sub>TRSTST</sub> | 10                 | —   | ns                 |

<sup>1</sup> JTAG\_EN is expected to be a static signal. Hence, it is not associated with any timing.

Figure 14. Test Clock Input Timing

### 2.14 Debug AC Timing Specifications

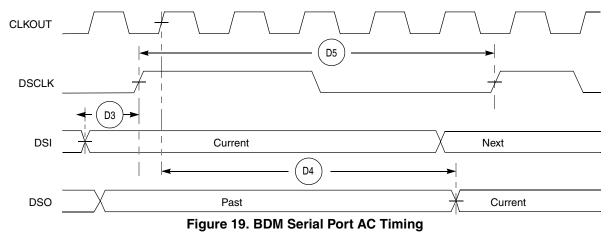

Table 40 lists specifications for the debug AC timing parameters shown in Figure 19.

| Num             | Characteristic                            | 60 MHz             |      | Units |

|-----------------|-------------------------------------------|--------------------|------|-------|

|                 |                                           | Min                | Мах  | Units |

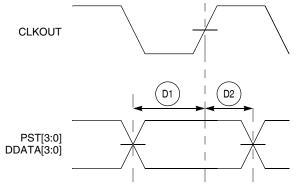

| D1              | PST, DDATA to CLKOUT setup                | 4                  |      | ns    |

| D2              | CLKOUT to PST, DDATA hold                 | 1.5                |      | ns    |

| D3              | DSI-to-DSCLK setup                        | $1 \times t_{CYC}$ | _    | ns    |

| D4 <sup>1</sup> | DSCLK-to-DSO hold                         | $4 \times t_{CYC}$ | _    | ns    |

| D5              | DSCLK cycle time                          | $5 	imes t_{CYC}$  | _    | ns    |

| D6              | BKPT input data setup time to CLKOUT Rise | 4                  | _    | ns    |

| D7              | BKPT input data hold time to CLKOUT Rise  | 1.5                | _    | ns    |

| D8              | CLKOUT high to BKPT high Z                | 0.0                | 10.0 | ns    |

#### Table 40. Debug AC Timing Specification

<sup>1</sup> DSCLK and DSI are synchronized internally. D4 is measured from the synchronized DSCLK input relative to the rising edge of CLKOUT.

Figure 18 shows real-time trace timing for the values in Table 40.

Figure 18. Real-Time Trace AC Timing

Figure 19 shows BDM serial port AC timing for the values in Table 40.

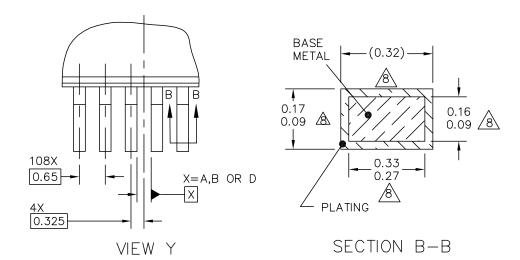

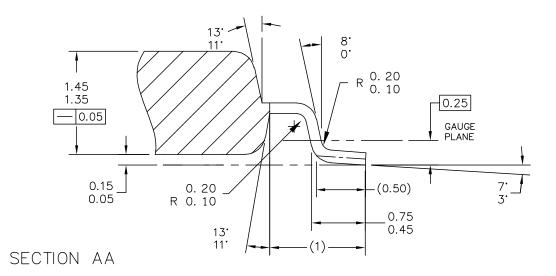

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA    | LOUTLINE       | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------|----------------|----------------------------|-------------|

| TITLE: 112LD LQFP                                       |              | DOCUMENT NO    | : 98ASS23330W              | REV: E      |

| 20 X 20 X 1.4                                           |              | CASE NUMBER    | 2: 987–02                  | 25 MAY 2005 |

| 0.65 PITCH                                              | STANDARD: JE | DEC MS-026 BFA |                            |             |

# 4 Revision History

#### Table 41. Revision History

| Revision     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2 (Jul 2006) | <ul> <li>Updated available packages.</li> <li>Inserted mechanical drawings.</li> <li>Corrected signal pinouts and table.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 3 (Feb 2007) | <ul> <li>Changed signal names TIN to DTIN and TOUT to DTOUT to match the MCF52235 ColdFire<sup>®</sup> Integrated Microcontroller Reference Manual.</li> <li>Added overbars to extend over entire UCTSn and URTSn signal name.</li> <li>Added revision history.</li> <li>Formatting, layout, spelling, and grammar corrections.</li> <li>Updated block diagram and feature information to match Revision 3 of the MCF52235 ColdFire<sup>®</sup> Integrated Microcontroller Reference Manual.</li> <li>Deleted the "PSTCLK cycle time" row from the "Debug AC Timing Specifications" table.</li> <li>Added "EPHY Timing" section.</li> <li>Deleted the "RAM standby supply voltage" entry from Table 19.</li> <li>Changed the minimum value for SNR, THD, SFDR, and SINAD in the "ADC parameters" table (was TBD, is "—").</li> <li>In the "Pin Functions by Primary and Alternate Purpose" table, changed the pin number for IRQ11 on the 80 LQFP package (was "—", is 41).</li> <li>Updated the "Thermal characteristics" table to include proper thermal resistance values.</li> <li>Added two tables, "Active Current Consumption Specifications" and "Current Consumption Specifications in Low-Power Modes", containing the latest current consumption information.</li> <li>Changed the value of T<sub>j</sub> in the "Thermal Characteristics" table (was 105 °C, is 130 °C for all packages).</li> <li>Added the following note to and above the "Thermal Characteristics" table: "The use of this device in one- or two-layer board designs is not recommended due to the limited thermal conductance provided by those boards."</li> </ul> |  |  |

| 4 (May 2007) | <ul> <li>Formatting, layout, spelling, and grammar corrections.</li> <li>Added load test condition information to the "General Purpose I/O Timing" section.</li> <li>Added specifications for V<sub>LVD</sub> and V<sub>LVDHYS</sub> to the "DC electrical specifications" table.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 5 (Sep 2007) | <ul> <li>Formatting, layout, spelling, and grammar corrections.</li> <li>Added information about the MCF52232 and MCF52236 devices.</li> <li>Revised the part number table to include full Freescale orderable part numbers.</li> <li>Synchronized the "Pin Functions by Primary and Alternate Purpose" table in the device reference manual and data sheet.</li> <li>Added specifications for V<sub>REFL</sub>, V<sub>REFH</sub>, and V<sub>DDA</sub> to the "ADC Parameters" table.</li> <li>Added several EPHY specifications.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 6 (Oct 2007) | <ul> <li>Formatting, layout, spelling, and grammar corrections.</li> <li>Changed the data sheet classification (was "Product Preview", is "Advance Information").</li> <li>Added the "EzPort Electrical Specifications" section.</li> <li>Updated the "ESD Protection" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 7 (Aug 2008) | <ul> <li>Changed document type from Advance Information to Technical Data.</li> <li>Added supported device list in subtitle.</li> <li>Removed preliminary text from electrical specifications section as device is fully characterized.</li> <li>Corrected I<sub>VREFH</sub>, VREFH current unit from "m" to "mA" in ADC specification table.</li> <li>Changed V<sub>OFFSET</sub> from TBD to — in ADC specification table.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 8 (Jun 2009) | Updated Orderable Part Number Summary table to include MCF52233CAL60A, MCF52235CAL60A, and MCF52236AF50A parts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |