Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                              |

|---------------------------------|--------------------------------------------------------------|

| Product Status                  | Active                                                       |

| Core Processor                  | PowerPC e500                                                 |

| Number of Cores/Bus Width       | 2 Core, 32-Bit                                               |

| Speed                           | 1.333GHz                                                     |

| Co-Processors/DSP               | Signal Processing; SC3850, Security; SEC 4.4                 |

| RAM Controllers                 | DDR3, DDR3L                                                  |

| Graphics Acceleration           | No                                                           |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | 10/100/1000Mbps (2)                                          |

| SATA                            | -                                                            |

| USB                             | USB 2.0 (1)                                                  |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                             |

| Operating Temperature           | 0°C ~ 105°C (TA)                                             |

| Security Features               | Boot Security, Cryptography, Random Number Generator         |

| Package / Case                  | 780-BFBGA, FCBGA                                             |

| Supplier Device Package         | 780-FCBGA (23x23)                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=bsc9132nse7mnmb |

|                                 | · · · · · · · · · · · · · · · · · · ·                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Pin A | ssignments3                                              |   | 2.22 Universal Subscriber Identity Module (USIM) 123     |

|---|-------|----------------------------------------------------------|---|----------------------------------------------------------|

|   | 1.1   | Ball Layout Diagrams                                     |   | 2.23 Timers and Timers_32b AC Timing Specifications 127  |

|   | 1.2   | Pinout Assignments                                       | 3 | 3 Hardware Design Considerations                         |

| 2 | Elect | rical Characteristics                                    |   | 3.1 Power Architecture System Clocking 128               |

|   | 2.1   | Overall DC Electrical Characteristics                    |   | 3.2 DSP System Clocking                                  |

|   | 2.2   | Power Sequencing57                                       |   | 3.3 Supply Power Default Setting                         |

|   | 2.3   | Power-Down Requirements                                  |   | 3.4 PLL Power Supply Design                              |

|   | 2.4   | RESET Initialization                                     |   | 3.5 Decoupling Recommendations                           |

|   | 2.5   | Power-on Ramp Rate                                       |   | 3.6 SerDes Block Power Supply Decoupling                 |

|   | 2.6   | Power Characteristics                                    |   | Recommendations                                          |

|   | 2.7   | Input Clocks                                             |   | 3.7 Guidelines for High-Speed Interface Termination 136  |

|   | 2.8   | DDR3 and DDR3L SDRAM Controller                          |   | 3.8 Pull-Up and Pull-Down Resistor Requirements 136      |

|   | 2.9   | eSPI                                                     |   | 3.9 Output Buffer DC Impedance                           |

|   | 2.10  | DUART75                                                  |   | 3.10 Configuration Pin Muxing                            |

|   | 2.11  | Ethernet: Enhanced Three-Speed Ethernet (eTSEC) .76      |   | 3.11 JTAG Configuration Signals                          |

|   | 2.12  | USB81                                                    |   | 3.12 Guidelines for High-Speed Interface Termination 140 |

|   | 2.13  | Integrated Flash Controller (IFC)                        |   | 3.13 Thermal140                                          |

|   | 2.14  | Enhanced Secure Digital Host Controller (eSDHC)87        |   | 3.14 Security Fuse Processor                             |

|   | 2.15  | Programmable Interrupt Controller (PIC) Specifications89 | 4 | 4 Package Information                                    |

|   | 2.16  | JTAG                                                     |   | 4.1 Package Parameters                                   |

|   | 2.17  | l <sup>2</sup> C94                                       |   | 4.2 Mechanical Dimensions of the FC-PBGA 142             |

|   | 2.18  | GPIO96                                                   | 5 | 5 Ordering Information                                   |

|   | 2.19  | TDM98                                                    |   | 5.1 Part Marking                                         |

|   | 2.20  | High-Speed Serial Interface (HSSI) DC Electrical         | 6 | 6 Product Documentation                                  |

|   |       | Characteristics                                          | 7 | 7 Revision History                                       |

|   | 2.21  | Radio Frequency (RF) Interface                           |   |                                                          |

**Pin Assignments**

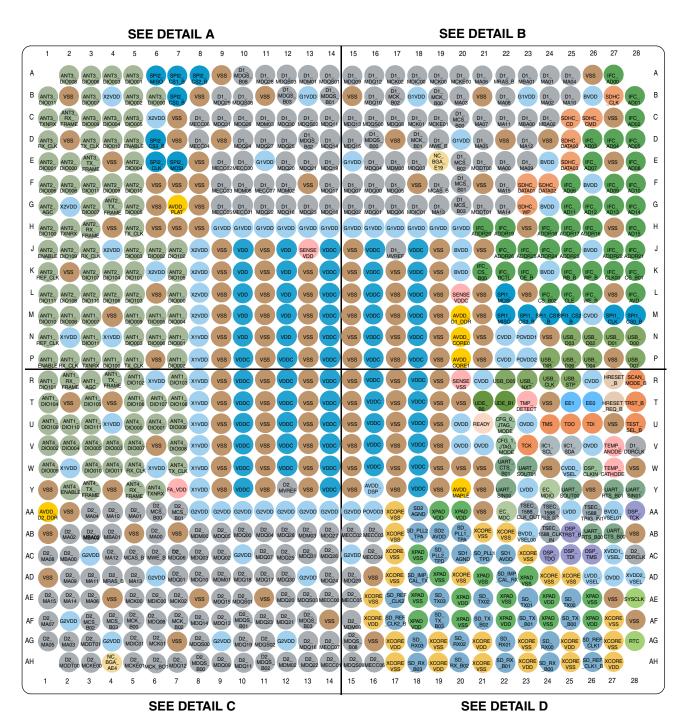

# 1.1 Ball Layout Diagrams

Figure 2. Ball Layout Diagram—Top-Level View

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1

## **Pin Assignments**

# Table 1. BSC9132 Pinout Listing (continued)

| Signal                                    | Signal Description       | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |

|-------------------------------------------|--------------------------|---------------|-------------|-----------------|------|

| ANT2_DIO104/<br>TDM1_RCK/<br>GPIO92       | TDM1 Receive Clock       | K4            | I/O         | X2VDD           | -1   |

| ANT2_DIO105/<br>TDM1_RFS/<br>TIMER08      | TDM1 Receive Frame Sync  | K7            | I/O         | X2VDD           | -1   |

| ANT2_DIO102/<br>TDM1_RXD                  | TDM1 Receive Data        | J7            | I/O         | X2VDD           | -1   |

|                                           | TDM2 over RF3            |               |             |                 |      |

| ANT3_RX_CLK/<br>TDM2_TCK/<br>GPI004       | TDM2 Clock               | D1            | I/O         | X2VDD           | -1   |

| ANT3_DIO007/<br>TDM2_TFS                  | TDM2 Transmit Frame Sync | B3            | I/O         | X2VDD           | -1   |

| ANT3_DIO011/<br>TDM2_TXD                  | TDM2 Transmit Data       | B1            | I/O         | X2VDD           | -1   |

| ANT3_DIO008/<br>TDM2_RCK/<br>CKSTP0_OUT_B | M2_RCK/                  |               | I/O         | X2VDD           | -1   |

| ANT3_DIO009/<br>TDM2_RFS/<br>CKSTP1_OUT_B | TDM2 Receive Frame Sync  | СЗ            | I/O         | X2VDD           | -1   |

| ANT3_DIO010/<br>TDM2_RXD                  | TDM2 Receive Data        | D4            | I/O         | X2VDD           | -1   |

|                                           | SerDes                   | <u> </u>      | •           |                 | •    |

| SD_TX03                                   | Tx Data out              | AE19          | 0           | XPADVDD         | _    |

| SD_TX02                                   | Tx Data out              | AE21          | 0           | XPADVDD         |      |

| SD_TX01                                   | Tx Data out              | AE23          | 0           | XPADVDD         | _    |

| SD_TX00                                   | Tx Data out              | AE25          | 0           | XPADVDD         | _    |

| SD_TX_B03                                 | Tx Data out, inverted    | AF19          | 0           | XPADVDD         | _    |

| SD_TX_B02                                 | Tx Data out, inverted    | AF21          | 0           | XPADVDD         | _    |

| SD_TX_B01                                 | Tx Data out, inverted    | AF23          | 0           | XPADVDD         | _    |

| SD_TX_B00                                 | Tx Data out, inverted    | AF25          | 0           | XPADVDD         | _    |

| SD_RX03                                   | Rx Data in               | AG18          | I           | XCOREVDD        | _    |

| SD_RX02                                   | Rx Data in               | AG20          | I           | XCOREVDD        | _    |

| SD_RX01                                   | Rx Data in               | AG22          | I           | XCOREVDD        | _    |

| SD_RX00                                   | Rx Data in               | AG24          | ı           | XCOREVDD        | _    |

| SD_RX_B03                                 | Rx Data in, Inverted     | AH18          | I           | XCOREVDD        | _    |

| SD_RX_B02                                 | Rx Data in, Inverted     | AH20          | I           | XCOREVDD        | _    |

| SD_RX_B01                                 | Rx Data in, Inverted     | AH22          | I           | XCOREVDD        | _    |

## **Pin Assignments**

# Table 1. BSC9132 Pinout Listing (continued)

| Signal                                               | Signal Description     | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note       |

|------------------------------------------------------|------------------------|---------------|-------------|-----------------|------------|

| IFC_ADDR18/<br>GPO10                                 | General Purpose Output | H24           | 0           | BVDD            | - 1        |

| IFC_ADDR19/<br>GPO11                                 |                        |               | 0           | BVDD            | <b>— I</b> |

| IFC_ADDR20/<br>GPO12                                 |                        |               | 0           | BVDD            | — I        |

| IFC_ADDR21/<br>GPO13                                 | General Purpose Output | J28           | 0           | BVDD            | — I        |

| IFC_ADDR22/<br>GPO14                                 | General Purpose Output | J27           | 0           | BVDD            | — I        |

| IFC_ADDR23/<br>GPO15                                 | General Purpose Output | J25           | 0           | BVDD            | <b>— I</b> |

| IFC_ADDR24/<br>GPO16                                 | General Purpose Output | J24           | 0           | BVDD            | - 1        |

| IFC_ADDR25/<br>GPO17                                 | General Purpose Output | J23           | 0           | BVDD            | -1         |

| IFC_ADDR26/<br>GPO18                                 | General Purpose Output | J22           | 0           | BVDD            | -1         |

| ANT1_TXNRX/<br>TSEC_1588_PULSE_OUT2/<br>GPO19        | General Purpose Output | P3            | 0           | X1VDD           | -1         |

| ANT1_TX_FRAME/<br>GPO20                              | General Purpose Output | R4            | 0           | X1VDD           | -1         |

| UART_RTS_B00/<br>PPS_LED/<br>GPO43                   | General Purpose Output | AB26          | 0           | OVDD            | -1         |

| UART_RTS_B01/<br>SYS_DMA_DONE/<br>GPO45/<br>ANT4_AGC | General Purpose Output | Y27           | 0           | OVDD            | -1         |

| IFC_CLE/<br>GPO48                                    | General Purpose Output | L25           | 0           | BVDD            | <b>— I</b> |

| IFC_OE_B/<br>GPO49                                   | General Purpose Output | K23           | 0           | BVDD            | -1         |

| IFC_RB_B/<br>GPO50                                   | General Purpose Output | K25           | 0           | BVDD            | <u> </u>   |

| IFC_WE_B/<br>GPO52                                   | General Purpose Output | L26           | 0           | BVDD            | <u> </u>   |

| IFC_AVD/<br>GPO54                                    | General Purpose Output | L28           | 0           | BVDD            | <u> </u>   |

| IFC_CS_B00/<br>GPO55                                 | General Purpose Output | K21           | 0           | BVDD            | <u> </u>   |

| UART_SOUT01/<br>GPO56                                | General Purpose Output | W23           | 0           | OVDD            | <u> </u>   |

Table 1. BSC9132 Pinout Listing (continued)

| Signal | Signal Description                            | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |

|--------|-----------------------------------------------|---------------|-------------|-----------------|------|

| BVDD   | IFC, eSDHC, USIM Supply                       | B26           | _           | BVDD            |      |

| BVDD   | IFC, eSDHC, USIM Supply                       | E24           | _           | BVDD            |      |

| BVDD   | IFC, eSDHC, USIM Supply                       | F26           | _           | BVDD            |      |

| BVDD   | IFC, eSDHC, USIM Supply                       | G24           | _           | BVDD            | _    |

| BVDD   | IFC, eSDHC, USIM Supply                       | J20           | _           | BVDD            | _    |

| BVDD   | IFC, eSDHC, USIM Supply                       | J26           | _           | BVDD            |      |

| BVDD   | IFC, eSDHC, USIM Supply                       | K20           | _           | BVDD            |      |

| BVDD   | IFC, eSDHC, USIM Supply                       | K24           | _           | BVDD            | _    |

| CVDD   | USB, eSPI, DUART, I2C, USIM Supply            | N22           | _           | CVDD            |      |

| CVDD   | USB, eSPI, DUART, I2C, USIM Supply            | P22           | _           | CVDD            |      |

| CVDD   | USB, eSPI, DUART, I2C, USIM Supply            | M26           | _           | CVDD            | _    |

| CVDD   | USB, eSPI, DUART, I2C, USIM Supply            | R21           | _           | CVDD            |      |

| CVDD   | USB, eSPI, DUART, I2C, USIM Supply            | R26           | _           | CVDD            |      |

| OVDD   | DUART, System, I2C, JTAG Supply               | U20           | _           | OVDD            | _    |

| OVDD   | DUART, System, I2C, JTAG Supply               | V20           | _           | OVDD            | _    |

| OVDD   | DUART, System, I2C, JTAG Supply               | V21           | _           | OVDD            | _    |

| OVDD   | DUART, System, I2C, JTAG Supply               | V26           | _           | OVDD            | _    |

| OVDD   | DUART, System, I2C, JTAG Supply               | U23           | _           | OVDD            | _    |

| OVDD   | DUART, System, I2C, JTAG Supply               | AD27          | _           | OVDD            | _    |

| X1VDD  | RF Supply                                     | N2            | _           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | N4            | _           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | N8            | _           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | U4            | -           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | W2            | _           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | W6            | _           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | P8            | -           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | R6            | _           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | R8            | _           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | Т8            | _           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | U8            | _           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | V8            | _           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | W8            | -           | X1VDD           | _    |

| X1VDD  | RF Supply                                     | Y8            | _           | X1VDD           | _    |

| X2VDD  | eSPI2, USB, TDM1, TDM2, RF Parallel Interface | B4            | _           | X2VDD           | _    |

| X2VDD  | eSPI2, USB, TDM1, TDM2, RF Parallel Interface | C6            | -           | X2VDD           | -    |

Table 2. Absolute Maximum Ratings<sup>1</sup> (continued)

|                           | Characteristic                                                                                                             | Symbol            | Max Value                           | Unit | Note  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------|------|-------|

| Input voltage             | DDR3/DDR3L DRAM signals                                                                                                    | MV <sub>IN</sub>  | $-0.3$ to $(GV_{DD} + 0.3)$         | ٧    | 5, 10 |

| DDR3/DDR3L DRAM reference |                                                                                                                            | MV <sub>REF</sub> | -0.3 to (GV <sub>DD</sub> /2 + 0.3) | V    | 10    |

| Ethernet signals          |                                                                                                                            | LV <sub>IN</sub>  | -0.3 to (LV <sub>DD</sub> + 0.3)    | V    | 6, 10 |

| IFC, eSDHC, USIM signals  |                                                                                                                            | BV <sub>IN</sub>  | -0.3 to (BV <sub>DD</sub> + 0.3)    | _    | 7, 10 |

|                           | DUART1, SYSCLK, system control and power management, I <sup>2</sup> C1, clocking, I/O voltage select, and JTAG I/O voltage | OV <sub>IN</sub>  | -0.3 to (OV <sub>DD</sub> + 0.3)    | V    | 8, 10 |

|                           | USB, eSPI1, DUART2, I <sup>2</sup> C2, USIM                                                                                | CV <sub>IN</sub>  | -0.3 to (CV <sub>DD</sub> + 0.3)    | V    | 4, 10 |

|                           | RF parallel interface                                                                                                      | X1V <sub>IN</sub> | -0.3 to (X1V <sub>DD</sub> + 0.3)   | V    | 9, 10 |

|                           | eSPI2, USB, TDM1, TDM2, RF parallel interface                                                                              | X2V <sub>IN</sub> | -0.3 to (X2V <sub>DD</sub> + 0.3)   | V    | 9, 10 |

| Storage tempe             | erature range                                                                                                              | T <sub>STG</sub>  | -55 to 150                          | °C   | _     |

#### Note:

- Functional operating conditions are given in Table 3. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- $^{2}$  AV<sub>DD</sub> is measured at the input to the filter and not at the pin of the device.

- <sup>3</sup> USIM pins are multiplexed with the pins of other interfaces. Check Table 3 for which power supply is used (BV<sub>DD</sub> or a CV<sub>DD</sub>) for each particular USIM pin.

- <sup>4</sup> Caution: CV<sub>IN</sub> must not exceed CV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 6 Caution: LV<sub>IN</sub> must not exceed LV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- Caution: BV<sub>IN</sub> must not exceed BV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- $^{8}$  Caution:  $OV_{IN}$  must not exceed  $OV_{DD}$  by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- Gaution: X[1-2]V<sub>IN</sub> must not exceed X[1-2]V<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- $^{10}$  (C,X,B,G,L,O,R)V<sub>DD</sub> and MV<sub>REF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 7.

# 2.1.2 Recommended Operating Conditions

This table provides the recommended operating conditions for this device. Note that the values in this table are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

**Table 3. Recommended Operating Conditions**

| Characteristic           | Symbol    | Recommended Value  | Unit | Note |

|--------------------------|-----------|--------------------|------|------|

| Platform supply voltage  | $V_{DDC}$ | 1 + 50 mV / – 30mV | ٧    | 1    |

| MAPLE-B2P supply voltage | $V_{DD}$  | 1 + 50 mV / – 30mV | ٧    | _    |

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1

**Table 3. Recommended Operating Conditions (continued)**

| Characteristic                              |                                                                                                                                        | Symbol                                                                                                                | Recommended Value                                         | Unit | Note |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|------|

| PLL supply volt                             | age                                                                                                                                    | AV <sub>DD_D[1-2]_DDR</sub> AV <sub>DD_PLAT</sub> AV <sub>DD_DSP</sub> AV <sub>DD_MAPLE</sub> SD[1-2]AV <sub>DD</sub> |                                                           | V    | 1    |

| Fuse supply vo                              | ltage                                                                                                                                  | POV <sub>DD1</sub>                                                                                                    | 1.5 V ± 75 mV                                             | V    | 1    |

| DDR3 DRAM I/                                | O voltage                                                                                                                              | G[1–2]V <sub>DD</sub>                                                                                                 | 1.5 V ± 75 mV                                             | _    | _    |

| DDR3L DRAM                                  | I/O voltage                                                                                                                            | G[1–2]V <sub>DD</sub>                                                                                                 | 1.35 V +100mV/<br>-67mV                                   | _    | _    |

| Three-speed E                               | thernet, Ethernet management (eTSEC) and 1588                                                                                          | LV <sub>DD</sub>                                                                                                      | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                          | V    |      |

|                                             | CLK, system control and power management, I <sup>2</sup> C1, Itage select, and JTAG I/O voltage                                        | OV <sub>DD</sub>                                                                                                      | 3.3 V ± 165 mV                                            | V    | _    |

| IFC, eSDHC, U                               | SIM                                                                                                                                    | BV <sub>DD</sub>                                                                                                      | 3.3 V ± 165 mV<br>2.5 V ± 125 mV<br>1.8 V ± 90 mV         | V    | 2    |

| USB, eSPI1, DUART2, I <sup>2</sup> C2, USIM |                                                                                                                                        | CV <sub>DD</sub>                                                                                                      | 3.3 V ± 165 mV<br>1.8 V ± 90 mV                           | V    | 2    |

| RF parallel inte                            | RF parallel interface                                                                                                                  |                                                                                                                       | 3.3 V ± 165 mV<br>1.8 V ± 90 mV                           | V    | _    |

| eSPI2, USB, TI                              | DM1, TDM2, RF parallel interface                                                                                                       | X2V <sub>DD</sub>                                                                                                     | 3.3 V ± 165 mV<br>1.8 V ± 90 mV                           | V    | _    |

| SerDes pad vol                              | tage                                                                                                                                   | XPADV <sub>DD</sub>                                                                                                   | 1.5 V ± 75 mV                                             | V    | _    |

| SerDes core vo                              | ltage                                                                                                                                  | XCOREV <sub>DD</sub>                                                                                                  | 1.0 V ± 50 mV                                             | V    | _    |

| Input voltage                               | DDR3/DDR3L DRAM                                                                                                                        | MV <sub>IN</sub>                                                                                                      | GND to GV <sub>DD</sub>                                   | V    | _    |

|                                             | DDR3/DDR3L DRAM reference                                                                                                              | MV <sub>REF</sub>                                                                                                     | GND to GV <sub>DD</sub> /2                                | V    | _    |

|                                             | Ethernet, USB                                                                                                                          | LV <sub>IN</sub>                                                                                                      | GND to LV <sub>DD</sub>                                   | V    | _    |

|                                             | IFC, eSDHC signals                                                                                                                     | BV <sub>IN</sub>                                                                                                      | GND to BV <sub>DD</sub>                                   | V    |      |

|                                             | DUART1, SYSCLK, system control and power management, eSPI, I <sup>2</sup> C1, USIM, clocking, I/O voltage select, and JTAG I/O voltage | OV <sub>IN</sub>                                                                                                      | GND to OV <sub>DD</sub>                                   | V    | _    |

|                                             | USB, eSPI, eSDHC, DUART2, I <sup>2</sup> C2, USIM                                                                                      | CV <sub>IN</sub>                                                                                                      | GND to CV <sub>DD</sub>                                   | V    | _    |

|                                             | RF parallel interface                                                                                                                  | X1V <sub>IN</sub>                                                                                                     | GND to X1V <sub>DD</sub>                                  | V    | _    |

|                                             | eSPI2, USB, TDM1, TDM2, RF parallel interface                                                                                          | X2V <sub>IN</sub>                                                                                                     | GND to X2V <sub>DD</sub>                                  | V    | _    |

| Maximum input                               | capacitance                                                                                                                            | C <sub>INMAX</sub>                                                                                                    | 10                                                        | pF   | 3    |

| Operating<br>Temperature                    | Standard                                                                                                                               | Ta/TJ                                                                                                                 | TA = 0 (min) to<br>TJ = 105 (max)                         | °C   | _    |

| range                                       | Extended                                                                                                                               | Ta/TJ                                                                                                                 | $T_A = -40 \text{ (min) to}$<br>$T_J = 105 \text{ (max)}$ | °C   | _    |

|                                             | Secure boot fuse programming                                                                                                           | Ta/TJ                                                                                                                 | TA = 0 (min) to<br>T <sub>J</sub> = 70 (max)              | °C   | 1    |

## BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1

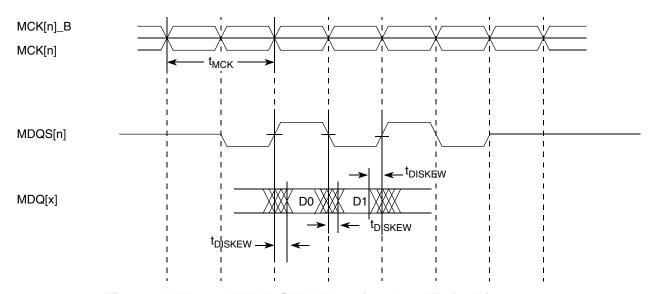

### Table 24. DDR3 and DDR3L SDRAM Interface Input AC Timing Specifications (continued)

At recommended operating conditions with GV<sub>DD</sub> of 1.5 V  $\pm$  5% for DDR3 or 1.35 V  $\pm$  5% for DDR3L.

| Parameter                        | Symbol              | Min          | Max | Unit | Note |

|----------------------------------|---------------------|--------------|-----|------|------|

| Tolerated Skew for MDQS—MDQ/MECC | t <sub>DISKEW</sub> | _            | _   | ps   | 2    |

| 1333 MHz data rate               |                     | -250         | 250 |      |      |

| 1200 MHz data rate               |                     | -275         | 275 |      |      |

| 1066 MHz data rate               |                     | -300         | 300 |      |      |

| 800 MHz data rate                |                     | -425         | 425 |      |      |

| 667 MHz data rate                |                     | <b>-</b> 510 | 510 |      |      |

#### Note:

- 1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. This should be subtracted from the total timing budget.

- 2. The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ±(T ÷ 4 abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

This figure shows the DDR3 and DDR3L SDRAM interface input timing diagram.

Figure 9. DDR3 and DDR3L SDRAM Interface Input Timing Diagram

# 2.8.2.2 DDR3 and DDR3L SDRAM Interface Output AC Timing Specifications

This table contains the output AC timing targets for the DDR3 and DDR3L SDRAM interface.

### Table 25. DDR3 and DDR3L SDRAM Interface Output AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 1.5 V  $\pm$  5% for DDR3 or 1.35 V  $\pm$  5% for DDR3L.

| Parameter         | Symbol <sup>1</sup> | Min | Max | Unit | Note |

|-------------------|---------------------|-----|-----|------|------|

| MCK[n] cycle time | t <sub>MCK</sub>    | 1.5 | 3   | ns   | 2    |

### **Table 35. MII Management DC Electrical Characteristics**

At recommended operating conditions with  $LV_{DD} = 2.5 \text{ V}$ .

| Parameter                                                                | Symbol          | Min       | Max                    | Unit | Note |

|--------------------------------------------------------------------------|-----------------|-----------|------------------------|------|------|

| Input high voltage                                                       | V <sub>IH</sub> | 1.70      | LV <sub>DD</sub> + 0.3 | V    | _    |

| Input low voltage                                                        | V <sub>IL</sub> | -0.3      | 0.70                   | V    | _    |

| Input high current (V <sub>IN</sub> = LV <sub>DD</sub> ,)                | I <sub>IH</sub> | _         | 10                     | μΑ   | 1, 2 |

| Input low current (V <sub>IN</sub> = GND)                                | I <sub>IL</sub> | -15       | _                      | μΑ   | _    |

| Output high voltage (LV <sub>DD</sub> = Min, IOH = -1.0 mA)              | V <sub>OH</sub> | 2.00      | LV <sub>DD</sub> + 0.3 | V    | _    |

| Output low voltage<br>(LV <sub>DD</sub> = Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub> | GND - 0.3 | 0.40                   | V    | _    |

#### Note:

- 1. EC1\_MDC and EC1\_MDIO operate on LV<sub>DD</sub>.

- 2. Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 3.

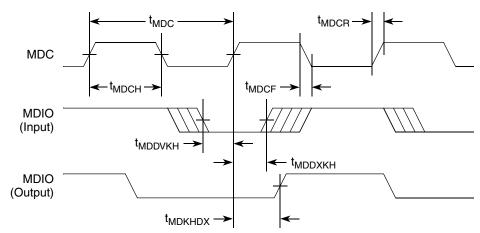

## 2.11.2.2 MII Management AC Electrical Specifications

This table provides the MII management AC timing specifications.

**Table 36. MII Management AC Timing Specifications**

| Parameter                  | Symbol <sup>1</sup> | Min                            | Тур | Max                            | Unit | Note |

|----------------------------|---------------------|--------------------------------|-----|--------------------------------|------|------|

| MDC frequency              | f <sub>MDC</sub>    | _                              | 2.5 | _                              | MHz  | 2    |

| MDC period                 | t <sub>MDC</sub>    | _                              | 400 | _                              | ns   | _    |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32                             | _   | _                              | ns   | _    |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | (16*t <sub>plb_clk</sub> ) - 3 | _   | (16*t <sub>plb_clk</sub> ) + 3 | ns   | 3, 4 |

| MDIO to MDC setup time     | t <sub>MDDVKH</sub> | 5                              | _   | _                              | ns   | _    |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0                              | _   | _                              | ns   | _    |

#### Note:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. This parameter is dependent on the platform clock frequency (MIIMCFG [MgmtClk] field determines the clock frequency of the MgmtClk Clock EC\_MDC).

- 3. This parameter is dependent on the platform clock frequency. The delay is equal to 16 platform clock periods  $\pm 3$  ns. For example, with a platform clock of 333 MHz, the min/max delay is 48 ns  $\pm 3$  ns. Similarly, if the platform clock is 400 MHz, the min/max delay is 40 ns  $\pm 3$  ns.

- 4.  $t_{\text{plb\_clk}}$  is the platform (CCB) clock.

This figure shows the MII management interface timing diagram.

Figure 16. MII Management Interface Timing Diagram

# 2.11.3 eTSEC IEEE Std 1588 Electrical Specifications

## 2.11.3.1 eTSEC IEEE Std 1588 DC Specifications

This table shows IEEE Std 1588 DC electrical characteristics when operating at  $LV_{DD} = 3.3 \text{ V}$  supply.

## Table 37. eTSEC IEEE 1588 DC Electrical Characteristics (LV<sub>DD</sub> = 3.3 V)

For recommended operating conditions with  $LV_{DD} = 3.3 \text{ V}$ .

| Parameter                                                               | Symbol          | Min  | Max | Unit | Notes |

|-------------------------------------------------------------------------|-----------------|------|-----|------|-------|

| Input high voltage                                                      | V <sub>IH</sub> | 2.0  | _   | V    | 2     |

| Input low voltage                                                       | V <sub>IL</sub> | _    | 0.9 | V    | 2     |

| Input high current (LV <sub>DD</sub> = Max, V <sub>IN</sub> = 2.1 V)    | I <sub>IH</sub> | _    | 40  | μΑ   | 1     |

| Input low current (LV <sub>DD</sub> = Max, V <sub>IN</sub> = 0.5 V)     | I <sub>IL</sub> | -600 | _   | μΑ   | 1     |

| Output high voltage (LV <sub>DD</sub> = Min, I <sub>OH</sub> = -1.0 mA) | V <sub>OH</sub> | 2.4  | _   | V    | _     |

| Output low voltage (LV <sub>DD</sub> = Min, I <sub>OL</sub> = 1.0 mA)   | V <sub>OL</sub> | _    | 0.4 | V    | _     |

#### Note:

- 1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $LV_{IN}$  values found in Table 3.

- 2. The symbol  $V_{\text{IN}}$ , in this case, represents the  $LV_{\text{IN}}$  symbols referenced in Table 2 and Table 3.

This table shows the IEEE 1588 DC electrical characteristics when operating at  $LV_{DD} = 2.5$  V supply.

## Table 38. eTSEC IEEE 1588 DC Electrical Characteristics (LV<sub>DD</sub> = 2.5 V)

For recommended operating conditions with  $LV_{DD} = 2.5 \text{ V}$

| Parameter          | Symbol          | Min  | Max  | Unit | Notes |

|--------------------|-----------------|------|------|------|-------|

| Input high voltage | V <sub>IH</sub> | 1.70 | _    | V    | _     |

| Input low voltage  | V <sub>IL</sub> | _    | 0.70 | V    | _     |

This table provides the USB clock input (USB\_CLK\_IN) AC timing specifications.

Table 43. USB\_CLK\_IN AC Timing Specifications

| Parameter/Condition                    | Conditions                                                                            | Symbol                  | Min   | Тур | Max   | Unit |

|----------------------------------------|---------------------------------------------------------------------------------------|-------------------------|-------|-----|-------|------|

| Frequency range                        | Steady state                                                                          | f <sub>USB_CLK_IN</sub> | 59.97 | 60  | 60.03 | MHz  |

| Clock frequency tolerance              | _                                                                                     | t <sub>CLK_TOL</sub>    | -0.05 | 0   | 0.05  | %    |

| Reference clock duty cycle             | Measured at 1.6 V                                                                     | t <sub>CLK_DUTY</sub>   | 40    | 50  | 60    | %    |

| Total input jitter/time interval error | Peak-to-peak value measured with a second order high-pass filter of 500 kHz bandwidth | t <sub>CLK_PJ</sub>     | _     | _   | 200   | ps   |

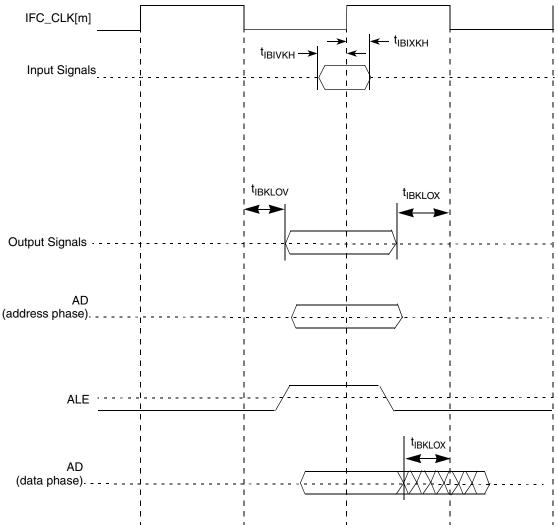

# 2.13 Integrated Flash Controller (IFC)

This section describes the DC and AC electrical specifications for the integrated flash controller.

## 2.13.1 IFC DC Electrical Characteristics

This table provides the DC electrical characteristics for the integrated flash controller when operating at  $BV_{DD} = 3.3 \text{ V}$ .

Table 44. Integrated Flash Controller DC Electrical Characteristics (3.3 V)

For recommended operating conditions, see Table 3

| Parameter                                                                | Symbol          | Min | Max | Unit | Note |

|--------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                       | V <sub>IH</sub> | 2   | _   | V    | 1    |

| Input low voltage                                                        | V <sub>IL</sub> | _   | 0.8 | V    | 1    |

| Input current $(V_{IN} = 0 \text{ V or } V_{IN} = BV_{DD})$              | I <sub>IN</sub> | _   | ±40 | μΑ   | 2    |

| Output high voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA) | V <sub>OH</sub> | 2.8 | _   | V    | _    |

| Output low voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = 2 mA)   | V <sub>OL</sub> | _   | 0.4 | V    | _    |

### Note:

- 1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $BV_{IN}$  values found in Table 3.

- 2. The symbol  $V_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Section 2.1.2, "Recommended Operating Conditions."

This table provides the DC electrical characteristics for the integrated flash controller when operating at  $BV_{DD} = 2.5 \text{ V}$ .

Table 45. Integrated Flash Controller DC Electrical Characteristics (2.5 V)

For recommended operating conditions, see Table 3

| Parameter                                                                   | Symbol          | Min | Max | Unit | Note |

|-----------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                          | V <sub>IH</sub> | 1.7 | _   | V    | 1    |

| Input low voltage                                                           | V <sub>IL</sub> | _   | 0.7 | V    | 1    |

| Input current (V <sub>IN</sub> = 0 V or V <sub>IN</sub> = BV <sub>DD)</sub> | I <sub>IN</sub> | _   | ±40 | μΑ   | 2    |

| Output high voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -1 mA)    | V <sub>OH</sub> | 2.0 | _   | V    | _    |

This figure shows the AC timing diagram.

Figure 22. Integrated Flash Controller Signals

Figure 22 applies to all the controllers that IFC supports.

For input signals, the AC timing data is used directly for all controllers. For output signals, each type of controller provides its own unique method to control the signal timing. The final signal delay value for output signals is the programmed delay plus the AC timing delay.

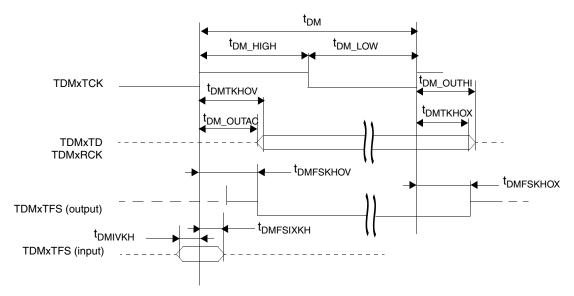

This figure shows the TDM transmit signal timing.

Figure 34. TDM Transmit Signals

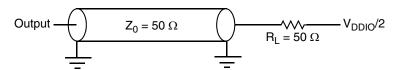

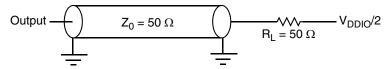

This figure provides the AC test load for the TDM.

Figure 35. TDM AC Test Load

# 2.20 High-Speed Serial Interface (HSSI) DC Electrical Characteristics

The device features an HSSI that includes one 4-channel SerDes port (lanes 0 through 3) used for high-speed serial interface applications (PCI Express, CPRI, and SGMII). This section and its subsections describe the common portion of the SerDes DC, including the DC requirements for the SerDes reference clocks and the SerDes data lane transmitter (Tx) and receiver (Rx) reference circuits. The data lane circuit specifications are specific for each supported interface, and they have individual subsections by protocol. The selection of individual data channel functionality is done via the reset configuration word. Specific AC electrical characteristics are defined in Section 2.20.3, "HSSI AC Timing Specifications."

### Table 68. PCI Express (2.5 Gbps) Differential Receiver (Rx) Input DC Specifications (continued)

| Parameter Symbol | Min | Nom | Max | Unit | Note |  |

|------------------|-----|-----|-----|------|------|--|

|------------------|-----|-----|-----|------|------|--|

#### Note:

- 1.  $V_{RX-DIFFp-p} = 2 \times |V_{RX-D+} V_{RX-D-}|$  Measured at the package pins with a test load of 50  $\Omega$  to GND on each pin.

- 2. Rx DC differential mode impedance. Impedance during all LTSSM states. When transitioning from a fundamental reset to detect (the initial state of the LTSSM), there is a 5 ms transition time before the receiver termination values must be met on all unconfigured lanes of a port.

- 3. Required Rx D+ as well as D– DC Impedance (50  $\pm$ 20% tolerance). Measured at the package pins with a test load of 50  $\Omega$  to GND on each pin. Impedance during all LTSSM states. When transitioning from a fundamental reset to detect (the initial state of the LTSSM), there is a 5 ms transition time before the receiver termination values must be met on all unconfigured lanes of a port.

- 4. Required Rx D+ as well as D- DC Impedance when the receiver terminations do not have power. The Rx DC common mode impedance that exists when no power is present or fundamental reset is asserted. This helps ensure that the receiver detect circuit does not falsely assume a receiver is powered on when it is not. This term must be measured at 300 mV above the Rx ground.

- 5.  $V_{RX-IDLE-DET-DIFFp-p} = 2 \times |V_{RX-D+} V_{RX-D-}|$ . Measured at the package pins of the receiver.

Table 69. PCI Express (5 Gbps) Differential Transmitter (Tx) Output DC Specifications

| Parameter                                                | Symbol                             | Min | Nom  | Max  | Unit | Condition                                                                                                                                                                                                                                              |

|----------------------------------------------------------|------------------------------------|-----|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Differential peak-to-peak output voltage swing           | V <sub>TX-DIFFp-p</sub>            | 800 | 1000 | 1200 | mV   | $\begin{split} &V_{TX\text{-DIFFp-p}} = 2 \times  V_{TX\text{-D+}} - V_{TX\text{-D-}} , \\ &\text{Measured at the package pins with a} \\ &\text{test load of 50 } \Omega \text{ to GND on each pin.} \end{split}$                                     |

| Low power differential peak-to-peak output voltage swing | V <sub>TX-DIFFp-p_low</sub>        | 400 | 500  | 1200 | mV   | $V_{TX\text{-DIFFp-p}} = 2 \times  V_{TX\text{-D+}} - V_{TX\text{-D-}} ,$ Measured at the package pins with a test load of 50 $\Omega$ to GND on each pin.                                                                                             |

| De-emphasized differential output voltage (ratio)        | V <sub>TX-DE-RATIO-3.5d</sub><br>B | 3.0 | 3.5  | 4.0  | dB   | Ratio of the $V_{TX\text{-DIFFp-p}}$ of the second and following bits after a transition divided by the $V_{TX\text{-DIFFp-p}}$ of the first bit after a transition.  Measured at the package pins with a test load of 50 $\Omega$ to GND on each pin. |

| De-emphasized differential output voltage (ratio)        | VTX-DE-RATIO-6.0d<br>B             | 5.5 | 6.0  | 6.5  | dB   | Ratio of the $V_{TX\text{-DIFFp-p}}$ of the second and following bits after a transition divided by the $V_{TX\text{-DIFFp-p}}$ of the first bit after a transition.  Measured at the package pins with a test load of 50 $\Omega$ to GND on each pin. |

| DC differential Tx impedance                             | Z <sub>TX-DIFF-DC</sub>            | 80  | 100  | 120  | Ω    | Tx DC differential mode low impedance                                                                                                                                                                                                                  |

| Transmitter DC impedance                                 | Z <sub>TX-DC</sub>                 | 40  | 50   | 60   | Ω    | Required Tx D+ as well as D- DC impedance during all states                                                                                                                                                                                            |

## Table 1. PCI Express (5 Gbps) Differential Receiver (Rx) Input DC Specifications

| Parameter                               | Symbol                           | Min | Nom  | Max  | Unit | Note |

|-----------------------------------------|----------------------------------|-----|------|------|------|------|

| Differential input peak-to-peak voltage | V <sub>RX-DIFFp-p</sub>          | 120 | 1000 | 1200 | mV   | 1    |

| DC differential Input Impedance         | Z <sub>RX-DIFF-DC</sub>          | 80  | 100  | 120  | Ω    | 2    |

| DC input impedance                      | Z <sub>RX-DC</sub>               | 40  | 50   | 60   | Ω    | 3    |

| Powered down DC input impedance         | Z <sub>RX-HIGH-IMP-DC</sub>      | 50  | _    | _    | ΚΩ   | 4    |

| Electrical idle detect threshold        | V <sub>RX-IDLE-DET-DIFFp-p</sub> | 65  | _    | 175  | mV   | 5    |

### Table 82. CPRI Transmitter AC Timing Specifications (LV-II: 1.2288, 2.4576, 3.072, 4.9152, and 6.144 Gbps)

For recommended operating conditions, see Table 3.

| Characteristic              | Symbol | Min               | Nom        | Max               | Unit |

|-----------------------------|--------|-------------------|------------|-------------------|------|

| Unit Interval: 4.9152 GBaud | UI     | 1/4915.2 – 100ppm | 1/4915.2.8 | 1/4915.2 + 100ppm | μs   |

| Unit Interval: 6.144 GBaud  | UI     | 1/6144.0 – 100ppm | 1/6144.0   | 1/6144.0 + 100ppm | μs   |

Table 83 defines the Receiver AC specifications for CPRI LV. The AC timing specifications do not include REF CLK jitter.

### Table 83. CPRI Receiver AC Timing Specifications (LV-I: 1.2288, 2.4576, and 3.072 Gbps)

For recommended operating conditions, see Table 3.

| Characteristic                                     | Symbol | Min               | Nom      | Max               | Unit   |

|----------------------------------------------------|--------|-------------------|----------|-------------------|--------|

| Deterministic jitter tolerance                     | JD     | _                 | _        | 0.37              | UI p-p |

| Combined deterministic and random jitter tolerance | JDR    | _                 | _        | 0.55              | UI p-p |

| Total Jitter tolerance                             | JT     | _                 | _        | 0.65              | UI p-p |

| Unit Interval: 1.2288 GBaud                        | UI     | 1/1228.8 – 100ppm | 1/1228.8 | 1/1228.8 + 100ppm | ps     |

| Unit Interval: 2.4576 GBaud                        | UI     | 1/2457.6 – 100ppm | 1/2457.6 | 1/2457.6 + 100ppm | ps     |

| Unit Interval: 3.072 GBaud                         | UI     | 1/3072.0 – 100ppm | 1/3072.0 | 1/3072.0 + 100ppm | ps     |

| Bit error ratio                                    | BER    | _                 | _        | 10 <sup>-12</sup> | _      |

Table 84 defines the Receiver AC specifications for CPRI LV-II. The AC timing specifications do not include REF CLK jitter.

## Table 84. CPRI Receiver AC Timing Specifications (LV-II: 1.2288, 2.4576, 3.072, 4.9152, and 6.144 Gbps)

For recommended operating conditions, see Table 3.

| Characteristic                                     | Symbol   | Min               | Nom        | Max               | Unit   |

|----------------------------------------------------|----------|-------------------|------------|-------------------|--------|

| Gaussian                                           | R_GJ     | _                 | _          | 0.275             | UI p-p |

| Uncorrelated bounded high probability jitter       | R_UBHPJ  |                   |            | 0.150             | UI p-p |

| Correlated bounded high probability jitter         | R_CBHPJ  | _                 |            | 0.525             | UI p-p |

| Bounded high probability jitter                    | R_BHPJ   | _                 | _          | 0.675             | UI p-p |

| Sinusoidal jitter, maximum                         | R_SJ-max | _                 | _          | 5.000             | UI p-p |

| Sinusoidal jitter, high frequency                  | R_SJ-hf  | _                 | _          | 0.050             | UI p-p |

| Total Jitter (does not include sinusoidal jitter). | R_TJ     | _                 | _          | 0.950             | UI p-p |

| Unit Interval: 1.2288 GBaud                        | UI       | 1/1228.8 – 100ppm | 1/1228.8   | 1/1228.8 + 100ppm | μs     |

| Unit Interval: 2.4576 GBaud                        | UI       | 1/2457.6 – 100ppm | 1/2457.6   | 1/2457.6 + 100ppm | μs     |

| Unit Interval: 3.072 GBaud                         | UI       | 1/3072.0 – 100ppm | 1/3072.0   | 1/3072.0 + 100ppm | μs     |

| Unit Interval: 4.9152 GBaud                        | UI       | 1/4915.2 – 100ppm | 1/4915.2.8 | 1/4915.2 + 100ppm | μs     |

| Unit Interval: 6.144 GBaud                         | UI       | 1/6144.0 – 100ppm | 1/6144.0   | 1/6144.0 + 100ppm | μs     |

**Note:** The AC specifications do not include REF\_CLK jitter. The sinusoidal jitter in the total jitter tolerance may have any amplitude and frequency in the unshaded region of Figure 46. The ISI jitter (R\_CBHPJ) and amplitude have to be correlated, for example, by a PC trace.

#### **USIM External Pull Up/Pull Down Resistor Requirements** 2.22.3

External off-chip pull up resistor of 20 K $\Omega$  is required on the SIM TRXD pin.

External off-chip pull down resistors are required on the SIM\_PD, SIM\_SVEN, SIM\_RST pins.

#### 2.22.4 **USIM Reset Sequence**

#### 2.22.4.1 SIM Cards With Internal Reset

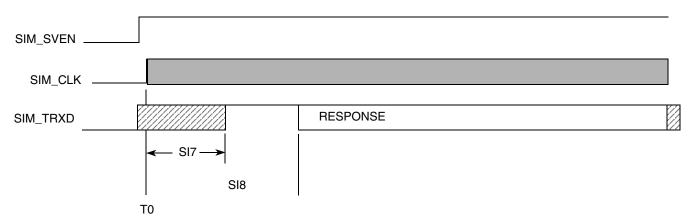

The sequence of reset for this kind of SIM cards is as follows (see Figure 51):

- After power up, the clock signal is enabled on SIM CLK (time T0).

- After 200 clock cycles, Rx must be high.

- The card must send a response on Rx acknowledging the reset between 400 and 40000 clock cycles after T0.

Figure 51. Internal-Reset Card Reset Sequence

Table 93. Parameters of Reset Sequence For Card With Internal Reset

| ID  | Parameter                     | Symbol               | Min | Max   | Unit                |

|-----|-------------------------------|----------------------|-----|-------|---------------------|

| SI7 | SIM clock to SIM TX data H    | S <sub>clk2dat</sub> | _   | 200   | SIM_CLK clock cycle |

| SI8 | SIM clock to SIM get ATR data | S <sub>clk2atr</sub> | 400 | 40000 | SIM_CLK clock cycle |

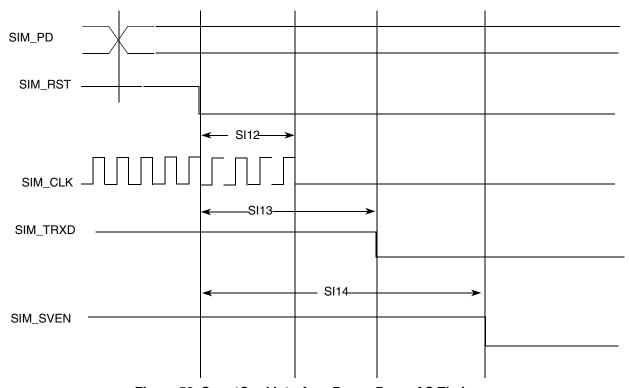

#### 2.22.4.2 SIM Cards With Active-Low Reset

The sequence of reset for this kind of card is as follows (see Figure 52):

- After powering up, the clock signal is enabled on SIM CLK (time T0).

- After 200 clock cycles, SIM TRXD must be high.

- SIM RST must remain Low for at least 40000 clock cycles after T0 (no response is to be received on Rx during those 40000 clock cycles).

- SIM RST is set High (time T1).

- SIM RST must remain High for at least 40000 clock cycles after T1 and a response must be received on SIM\_TRXD between 400 and 40000 clock cycles after T1.

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1 Freescale Semiconductor 125

Each of these steps is done in one CKIL period (typically 32 KHz). Power down is initiated by detection of a SIM card removal or is launched by the processor. See Figure 53 and Table 95 for the timing requirements for this sequence, with  $F_{CKIL} = CKIL$  frequency value.

Figure 53. SmartCard Interface Power Down AC Timing

Table 95. Timing Requirements for Power Down Sequence

| ID   | Parameter                              | Symbol               | Min           | Max                       | Unit |

|------|----------------------------------------|----------------------|---------------|---------------------------|------|

| SI12 | USIM reset to USIM clock stop          | S <sub>rst2clk</sub> | 0.9 × 1/Fckil | 1.1 × 1/F <sub>CKIL</sub> | ns   |

| SI13 | USIM reset to USIM Tx data low         | S <sub>rst2dat</sub> | 1.8 × 1/Fckil | 2.2 × 1/F <sub>CKIL</sub> | ns   |

| SI14 | USIM reset to USIM voltage enable low  | S <sub>rst2ven</sub> | 2.7 × 1/Fckil | 3.3 × 1/F <sub>CKIL</sub> | ns   |

| SI15 | USIM presence detect to USIM reset low | S <sub>pd2rst</sub>  | 0.9 × 1/Fckil | 1.1 × 1/F <sub>CKIL</sub> | ns   |

# 2.23 Timers and Timers\_32b AC Timing Specifications

This table lists the timer input AC timing specifications.

### **Table 96. Timers Input AC Timing Specifications**

For recommended operating conditions, see Table 3.

| Parameter                         | Symbol             | Minimum | Unit | Note |

|-----------------------------------|--------------------|---------|------|------|

| Timers inputs—minimum pulse width | T <sub>TIWID</sub> | 8       | ns   | 1, 2 |

#### Note:

- 1. The maximum allowed frequency of timer outputs is 125 MHz. Configure the timer modules appropriately.

- 2. Timer inputs and outputs are asynchronous to any visible clock. Timer outputs should be synchronized before use by any external synchronous logic. Timer inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation.

### BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1

#### **Hardware Design Considerations**

This figure shows the AC test load for the timers.

Figure 54. Timer AC Test Load

# 3 Hardware Design Considerations

This section discusses the hardware design considerations.

# 3.1 Power Architecture System Clocking

This section describes the PLL configuration for the Power Architecture side of the device. Note that the platform clock is identical to the internal core complex bus (CCB) clock.

This device includes 6 PLLs, as follows:

- The platform PLL generates the platform clock from the externally supplied SYSCLK input. The frequency ratio between the platform and SYSCLK is selected using the platform PLL ratio configuration bits as described in Section 3.1.2, "Power Architecture Platform to SYSCLK PLL Ratio."

- The e500 core PLL generates the core clock from the platform clock. The frequency ratio between the e500 core clock and the platform clock is selected using the e500 PLL ratio configuration bits as described in Section 3.1.3, "e500 Core to Platform Clock PLL Ratios." This device has two e500 core PLLs.

- The DDR PLL generates the clocking for the DDR SDRAM controller. The frequency ratio between DDR clock and

platform clock is selected using the DDR PLL ratio configuration bits as described in section Section 3.1.4, "Power

Architecture DDR/DDRCLK PLL Ratio."

- The SerDes block has two PLLs.

# 3.1.1 Power Architecture Clock Ranges

Table 97 provides the clocking specifications for the processor core and platform.

**Table 97. Power Architecture Processor Clocking Specifications**

| Characteristic                   | Maximum Processor Core<br>Frequency |      |     | Note    |  |

|----------------------------------|-------------------------------------|------|-----|---------|--|

|                                  | Min                                 | Max  |     |         |  |

| e500 core processor frequency    | 400                                 | 1200 | MHz | 1, 2, 3 |  |

| Platform CCB bus clock frequency | 267                                 | 600  | MHz | 1, 4, 5 |  |

### **Hardware Design Considerations**

• Binary value on IFC\_AD[0:2] at power up

These signals must be pulled to the desired values.

In asynchronous mode, the memory bus clock frequency is decoupled from the platform bus frequency.

Table 99. Power Architecture Platform/SYSCLK Clock Ratios

| Binary Value of IFC_AD[0:2] Signals | Platform: SYSCLK Ratio |

|-------------------------------------|------------------------|

| 000                                 | 4:1                    |

| 001                                 | 5:1                    |

| 010                                 | 6:1                    |

| All Others                          | Reserved               |

## 3.1.3 e500 Core to Platform Clock PLL Ratios

The clock ratio between the e500 core0 and the platform clock is determined by the binary value of IFC\_AD[3:5] signals at power up. Table 100 describes the supported ratios. There are no default values for these PLL ratios; these signals must be pulled to the desired values. Note that IFC\_AD[6] must be pulled low if the core frequency is 1001 MHz or below.

Table 100. e500 Core0 to Platform Clock Ratios

| Binary Value of IFC_AD[3:5]Signals | e500 Core0: Platform<br>Ratio |

|------------------------------------|-------------------------------|

| 010                                | 1:1                           |

| 011                                | 1.5:1                         |

| 100                                | 2:1                           |

| 101                                | 2.5:1                         |

| 110                                | 3:1                           |

| All Others                         | Reserved                      |

The clock ratio between the e500 core1 and the platform clock is determined by the binary value of the IFC\_CLE, IFC\_OE\_B, IFC\_WP\_B signals at power up. Table 101 describes the supported ratios. There are no default values for these PLL ratios; these signals must be pulled to the desired values. Note that IFC\_AD[12] must be pulled low if the core frequency is 1001 MHz or below.

Table 101. e500 Core1 to Platform Clock Ratios

| Binary Value of IFC_CLE, IFC_OE_B, IFC_WP_B Signals | e500 Core1: Platform Ratio |

|-----------------------------------------------------|----------------------------|

| 010                                                 | 1:1                        |

| 011                                                 | 1.5:1                      |

| 100                                                 | 2:1                        |

| 101                                                 | 2.5:1                      |

| 110                                                 | 3:1                        |

| All Others                                          | Reserved                   |

How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, QorlQ, and StarCore are trademarks of Freescale Semiconductor, Inc. Reg., U.S. Pat. & Tm. Off. QorlQ Qonverge is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2014 Freescale Semiconductor, Inc.

Document Number: BSC9132

Rev. 1 08/2014