Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                              |

|---------------------------------|--------------------------------------------------------------|

| Product Status                  | Active                                                       |

| Core Processor                  | -                                                            |

| Number of Cores/Bus Width       | -                                                            |

| Speed                           | -                                                            |

| Co-Processors/DSP               | -                                                            |

| RAM Controllers                 | -                                                            |

| Graphics Acceleration           | -                                                            |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | -                                                            |

| SATA                            | -                                                            |

| USB                             | -                                                            |

| Voltage - I/O                   |                                                              |

| Operating Temperature           | -                                                            |

| Security Features               | -                                                            |

| Package / Case                  | -                                                            |

| Supplier Device Package         | -                                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=bsc9132nsn7knkb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

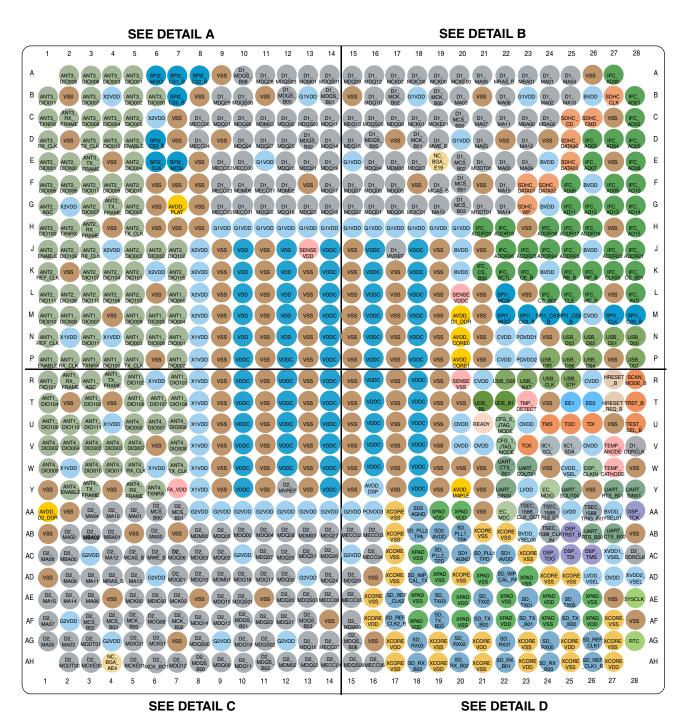

# 1.1 Ball Layout Diagrams

Figure 2. Ball Layout Diagram—Top-Level View

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1

Table 1. BSC9132 Pinout Listing (continued)

| Signal      | Signal Description | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |

|-------------|--------------------|---------------|-------------|-----------------|------|

| D2_MDQ13    | Data               | AF9           | I/O         | G2VDD           | _    |

| D2_MDQ14    | Data               | AF8           | I/O         | G2VDD           | _    |

| D2_MDQ15    | Data               | AE9           | I/O         | G2VDD           | _    |

| D2_MDQ16    | Data               | AG13          | I/O         | G2VDD           | _    |

| D2_MDQ17    | Data               | AD11          | I/O         | G2VDD           | _    |

| D2_MDQ18    | Data               | AD10          | I/O         | G2VDD           | _    |

| D2_MDQ19    | Data               | AG10          | I/O         | G2VDD           | _    |

| D2_MDQ20    | Data               | AE12          | I/O         | G2VDD           | _    |

| D2_MDQ21    | Data               | AF12          | I/O         | G2VDD           | _    |

| D2_MDQ22    | Data               | AH13          | I/O         | G2VDD           | _    |

| D2_MDQ23    | Data               | AF11          | I/O         | G2VDD           | _    |

| D2_MDQ24    | Data               | AD14          | I/O         | G2VDD           | _    |

| D2_MDQ25    | Data               | AC12          | I/O         | G2VDD           | _    |

| D2_MDQ26    | Data               | AC14          | I/O         | G2VDD           | _    |

| D2_MDQ27    | Data               | AB14          | I/O         | G2VDD           | _    |

| D2_MDQ28    | Data               | AB12          | I/O         | G2VDD           | _    |

| D2_MDQ29    | Data               | AD15          | I/O         | G2VDD           | _    |

| D2_MDQ30    | Data               | AD12          | I/O         | G2VDD           | _    |

| D2_MDQ31    | Data               | AC13          | I/O         | G2VDD           | _    |

| D2_MDM00    | Data Mask          | AB8           | 0           | G2VDD           | _    |

| D2_MDM01    | Data Mask          | AD9           | 0           | G2VDD           | _    |

| D2_MDM02    | Data Mask          | AH12          | 0           | G2VDD           | _    |

| D2_MDM03    | Data Mask          | AB13          | 0           | G2VDD           | _    |

| D2_MDQS00   | Data Strobe        | AG8           | I/O         | G2VDD           | _    |

| D2_MDQS01   | Data Strobe        | AE10          | I/O         | G2VDD           | _    |

| D2_MDQS02   | Data Strobe        | AG11          | I/O         | G2VDD           | _    |

| D2_MDQS03   | Data Strobe        | AE13          | I/O         | G2VDD           | _    |

| D2_MDQS_B00 | Data Strobe        | AH8           | I/O         | G2VDD           | _    |

| D2_MDQS_B01 | Data Strobe        | AF10          | I/O         | G2VDD           | _    |

| D2_MDQS_B02 | Data Strobe        | AH11          | I/O         | G2VDD           | _    |

| D2_MDQS_B03 | Data Strobe        | AF13          | I/O         | G2VDD           | _    |

| D2_MBA00    | Bank Select        | AC2           | 0           | G2VDD           | _    |

| D2_MBA01    | Bank Select        | AB4           | 0           | G2VDD           | _    |

| D2_MBA02    | Bank Select        | AB3           | 0           | G2VDD           | _    |

| D2_MA00     | Address            | AB6           | 0           | G2VDD           | _    |

| D2_MA01     | Address            | AA5           | 0           | G2VDD           | _    |

## Table 1. BSC9132 Pinout Listing (continued)

| Signal                                                   | Signal Description                                                                                       | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------|-------------|-----------------|-------|

| IFC_CLE/<br>GPO48                                        | NAND Command Latch Enable/GPCM Write<br>Byte Select1                                                     |               | 0           | BVDD            | 18 [  |

| IFC_OE_B/<br>GPO49                                       | NOR Output Enable/NAND Read Enable/<br>GPCM Output Enable/Generic ASIC Interface<br>Read-Write Indicator | K23           | 0           | BVDD            | 2     |

| IFC_WP_B/<br>GPO66                                       | IFC Write Protect                                                                                        | K26           | 0           | BVDD            | 18    |

| IFC_RB_B/<br>GPO50                                       | IFC Read Busy/GPCM External Transreciver/<br>Generic ASIC i/f Ready Indicator                            | K25           | I           | BVDD            | -1    |

| IFC_BCTL/<br>GPO67                                       | Data Buffer Control                                                                                      | K22           | 0           | BVDD            | 18 [  |

| IFC_CLK00/<br>GPO68                                      | IFC Clock                                                                                                | K27           | 0           | BVDD            | -1    |

|                                                          | eSDHC                                                                                                    | l             |             |                 | Ī     |

| SDHC_CLK/<br>SIM_CLK/<br>GPO52                           | SDHC Clock                                                                                               |               | 0           | BVDD            | -1    |

| SDHC_CMD/<br>SIM_RST_B/<br>GPIO48                        | SDHC Command                                                                                             | C26           | I/O         | BVDD            | 15    |

| SDHC_DATA00/<br>SIM_TRXD/<br>GPIO49                      | SDHC Data2 in all modes                                                                                  | D25           | I/O         | BVDD            | 15    |

| SDHC_DATA01/<br>SIM_SVEN/<br>GPIO50                      | SDHC Data1 in 4-bit mode                                                                                 | F23           | I/O         | BVDD            | 15    |

| SDHC_DATA02/<br>SIM_PD/<br>GPIO51                        | SDHC Data2 in 4-bit mode                                                                                 | F24           | I/O         | BVDD            | 15    |

| SDHC_DATA03/<br>DMA_DDONE_B00/<br>CKSTP1_IN_B/<br>GPIO77 | SDHC Data3 in 1-bit mode<br>SDHC Data3 in 4-bit mode                                                     | E25           | I/O         | BVDD            | 15,16 |

| SDHC_WP/<br>DMA_DREQ_B00/<br>CKSTP0_IN_B/<br>GPIO78      | SDHC Write Protect Detect                                                                                | G23           | I           | BVDD            | -1    |

| SDHC_CD/<br>DMA_DACK_B00/<br>MCP1_B/<br>GPIO79/<br>IRQ10 | DACK_B00/<br>_B/<br>'9/                                                                                  |               | ı           | BVDD            | -1    |

|                                                          | USIM                                                                                                     | I             | <u> </u>    |                 | Ī     |

# Table 1. BSC9132 Pinout Listing (continued)

| Signal                                    | Signal Description              | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |

|-------------------------------------------|---------------------------------|---------------|-------------|-----------------|------|

| USB_D06/<br>UART_CTS_B02/<br>GPIO62       | ULPI Data                       | P25           | I/O         | CVDD            | _    |

| USB_D05/<br>UART_RTS_B02/<br>GPIO63       | ULPI Data                       | R22           | I/O         | CVDD            | _    |

| USB_D04/<br>GPIO00/<br>IRQ00              | ULPI Data                       | P26           | I/O         | CVDD            | _    |

| USB_D03/<br>GPIO01/<br>IRQ01              | ULPI Data                       | N25           | I/O         | CVDD            | _    |

| USB_D02/<br>IIC2_SDA/<br>GPIO71           | ULPI Data                       | N26           | I/O         | CVDD            | _    |

| USB_D01/<br>IIC2_SCL/<br>GPIO72           | ULPI Data                       | N27           | I/O         | CVDD            | _    |

| USB_D00/<br>IRQ02/<br>GPIO53              | ULPI Data                       | N28           | I/O         | CVDD            | _    |

| USB_STP/<br>IRQ_OUT_B/<br>GPO73           | ULPI Stop                       | R25           | 0           | CVDD            | _    |

| USB_DIR/<br>GPIO02/<br>TIMER01/<br>MCP0_B | ULPI Data Direction             | P24           | I           | CVDD            | -1   |

| USB_NXT/<br>GPI003/<br>IRQ03/<br>TRIG_IN  | ULPI Next Data Throttle Control | R23           | I           | CVDD            | -1   |

|                                           | USB over ANT2                   |               |             |                 | I    |

| ANT2_DIO009/<br>USB_CLK/<br>GPIO59        | ULPI Clock                      | F4            | I           | X2VDD           | — I  |

| ANT2_DIO007/<br>USB_D07/<br>GPIO32        | ULPI Data                       | G3            | I/O         | X2VDD           | _    |

| ANT2_DIO006/<br>USB_D06/<br>GPIO31        | ULPI Data                       | F1            | I/O         | X2VDD           | _    |

| ANT2_DIO005/<br>USB_D05/<br>GPIO30        | ULPI Data                       | G5            | I/O         | X2VDD           | _    |

Table 1. BSC9132 Pinout Listing (continued)

| Signal                                               | Signal Description | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note     |

|------------------------------------------------------|--------------------|---------------|-------------|-----------------|----------|

| ANT3_RX_CLK/<br>TDM2_TCK/<br>GPI004                  | Receive Clock      | D1            | I           | X2VDD           | -1       |

| ANT3_TXNRX                                           | TX_RX Control      | C1            | 0           | X2VDD           | -1       |

| ANT3_ENABLE                                          | Antenna Enable     | D5            | 0           | X2VDD           | -1       |

| ANT3_TX_FRAME                                        | Transmit Frame     | E3            | 0           | X2VDD           | 2        |

| ANT3_RX_FRAME/<br>GPIO05                             | Receive Frame      | C2            | I           | X2VDD           | -1       |

| ANT3_DIO000/<br>CP_SYNC1                             | Data               | B6            | I/O         | X2VDD           |          |

| ANT3_DIO001/<br>CP_SYNC2                             | Data               | A5            | I/O         | X2VDD           | 4, 13    |

| ANT3_DIO002/<br>CP_LOS1                              | Data               | B5            | I/O         | X2VDD           | 4, 13    |

| ANT3_DIO003/<br>CP_LOS2                              | Data               | A4            | I/O         | X2VDD           | 4, 13    |

| ANT3_DIO004/<br>CP_TX_INT_B                          | Data               | C4            | I/O         | X2VDD           | 4, 13    |

| ANT3_DIO005/<br>CP_RCLK                              | Data               | C5            | I/O         | X2VDD           | 4, 13    |

| ANT3_DIO006/<br>CP_RX_INT_B                          | Data               | A3            | I/O         | X2VDD           | 4, 13    |

| ANT3_DIO007/<br>TDM2_TFS                             | Data               | В3            | I/O         | X2VDD           | _        |

| ANT3_DIO008/<br>TDM2_RCK/<br>CKSTP0_OUT_B            | Data               | A2            | I/O         | X2VDD           | _        |

| ANT3_DIO009/<br>TDM2_RFS/<br>CKSTP1_OUT_B            | Data               | СЗ            | I/O         | X2VDD           | 4, 13    |

| ANT3_DIO010/<br>TDM2_RXD                             | Data               | D4            | I/O         | X2VDD           | 4, 13    |

| ANT3_DIO011/<br>TDM2_TXD                             | Data               | B1            | I/O         | X2VDD           | _        |

|                                                      | RF Interface 4     | <u> </u>      | <u> </u>    |                 | Ī        |

| UART_RTS_B01/<br>SYS_DMA_DONE/<br>GPO45/<br>ANT4_AGC | AGC                | Y27           | 0           | OVDD            | -1       |

| ANT4_TX_CLK                                          | Transmit Clock     | W7            | 0           | X1VDD           | <u> </u> |

| ANT4_RX_CLK/<br>GPIO04/<br>TRIG_IN                   | Receive Clock      | W5            | I           | X1VDD           | - 1      |

Table 1. BSC9132 Pinout Listing (continued)

| Signal                                | Signal Description        | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note     |

|---------------------------------------|---------------------------|---------------|-------------|-----------------|----------|

| SPI1_CS3_B/<br>CKSTP1_OUT_B/<br>GPO76 | Checkstop Out             | M23           | 0           | CVDD            | -1       |

| READY/<br>ASLEEP/<br>READY_P1         | Ready/Trigger Out/Asleep  | U21           | 0           | OVDD            | 2        |

| UDE_B0                                | Unconditional Debug Event | T21           | I           | OVDD            | _        |

| UDE_B1                                | Unconditional Debug Event | T22           | I           | OVDD            | _        |

| EE0                                   | DSP Debug Request         | T26           | I           | OVDD            | _        |

| EE1                                   | DSP Debug Acknowledge     | T25           | 0           | OVDD            | 2        |

| TMP_DETECT                            | Tamper Detect             | T23           | I           | OVDD            | _        |

| UART_RTS_B00/<br>PPS_LED/<br>GPO43    | UART0 Ready to Send       | AB26          | 0           | OVDD            | _        |

|                                       | Clocking                  |               |             |                 |          |

| SYSCLK                                | System Clock              | AE28          | I           | OVDD            | _        |

| D1_DDRCLK                             | DDR PLL Reference Clock   | V28           | ı           | OVDD            | _        |

| D2_DDRCLK                             | DDR PLL Reference Clock   | AC28          | ı           | OVDD            | _        |

| RTC                                   | Real Time Clock           | AG28          | I           | OVDD            | _        |

| DSP_CLKIN                             | DSP PLL Reference Clock   | W26           | I           | OVDD            | _        |

| TSEC_1588_PULSE_OUT1/<br>PPS_OUT      | PPS Pulse Out             | AA24          | 0           | LVDD            | 2        |

|                                       | I/O Voltage Select        | •             |             |                 |          |

| BVDD_VSEL00                           | BVDD Voltage Selection    | AB23          | I           | OVDD            | _        |

| BVDD_VSEL01                           | BVDD Voltage Selection    | AA27          | ı           | OVDD            | _        |

| CVDD_VSEL                             | CVDD Voltage Selection    | W25           | I           | OVDD            | _        |

| LVDD_VSEL                             | LVDD Voltage Selection    | AD26          | I           | OVDD            | _        |

| XVDD1_VSEL                            | XVDD 1 Voltage Selection  | AC27          | I           | OVDD            | _        |

| XVDD2_VSEL                            | XVDD 2 Voltage Selection  | AD28          | I           | OVDD            | _        |

|                                       | Test                      | <b>'</b>      |             |                 | <b>.</b> |

| SCAN_MODE_B                           | Scan Mode                 | R28           | ı           | OVDD            | 1        |

| CFG_0_JTAG_MODE                       | JTAG mode selection 0     | U22           | I           | OVDD            | 10       |

| CFG_1_JTAG_MODE                       | JTAG mode selection 1     | V22           | ı           | OVDD            | 10       |

| TEST_SEL_B                            | Test Select               | U28           | I           | OVDD            | 11       |

|                                       | JTAG (Power Architecture) |               | 1           |                 |          |

| тск                                   | Test Clock                | V23           | ı           | OVDD            |          |

| TDI                                   | Test Data In              | U26           | I           | OVDD            | 3        |

|                                       |                           | ĺ             |             |                 |          |

## Table 1. BSC9132 Pinout Listing (continued)

| Signal                                                   | Signal Description  | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note       |

|----------------------------------------------------------|---------------------|---------------|-------------|-----------------|------------|

| ANT1_DIO108/<br>GPIO21/<br>IRQ08                         | External Interrupt  | Т7            | I           | X1VDD           | -1         |

| IFC_AD12/<br>GPIO38/<br>IRQ09                            | External Interrupt  | G26           | I           | BVDD            | -1         |

| ANT1_DIO109/<br>GPIO22/<br>IRQ09                         | External Interrupt  | U1            | -           | X1VDD           | -1         |

| SDHC_CD/<br>DMA_DACK_B00/<br>MCP1_B/<br>GPIO79/<br>IRQ10 | External Interrupt  | C25           | I           | BVDD            | -1         |

| ANT1_DIO106/<br>GPIO87/<br>IRQ10                         | External Interrupt  | T5            | I           | X1VDD           | -1         |

| USB_CLK/<br>UART_SIN02/<br>GPIO69/<br>IRQ11/<br>TIMER03  | External Interrupt  | R24           | I           | CVDD            | -1         |

| ANT1_DIO107/<br>GPIO88/<br>IRQ11                         | External Interrupt  | Т6            | ı           | X1VDD           | -1         |

| USB_STP/<br>IRQ_OUT_B/<br>GPO73                          | Interrupt Output    | R25           | 0           | CVDD            | -1         |

| ANT4_DIO006/<br>IRQ_OUT_B                                | Interrupt Output    | U7            | 0           | X1VDD           | <b>— I</b> |

|                                                          | GPIO                |               |             |                 | I          |

| USB_D04/<br>GPIO00/<br>IRQ00                             | General Purpose I/O | P26           | I/O         | CVDD            | - 1        |

| USB_D03/<br>GPIO01/<br>IRQ01                             | General Purpose I/O | N25           | I/O         | CVDD            | -1         |

| USB_DIR/<br>GPIO02/<br>TIMER01/<br>MCP0_B                | General Purpose I/O | P24           | I/O         | CVDD            | -1         |

| USB_NXT/<br>GPIO03/<br>IRQ03/<br>TRIG_IN                 | General Purpose I/O | R23           | I/O         | CVDD            | - 1        |

Table 1. BSC9132 Pinout Listing (continued)

| Signal      | Signal Description                     | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |  |

|-------------|----------------------------------------|---------------|-------------|-----------------|------|--|

| AVDD_PLAT   | Platform PLL Supply                    | G7            | _           | AVDD_PLAT       | _    |  |

| AVDD_CORE0  | Core PLL Supply                        | N20           | _           | AVDD_CORE0      | _    |  |

| AVDD_CORE1  | Core PLL Supply                        | P20           | _           | AVDD_CORE1      | _    |  |

| AVDD_D1_DDR | DDR PLL Supply                         | M20           | _           | AVDD_D1_DDR     | _    |  |

| AVDD_D2_DDR | DDR PLL Supply                         | AA1           | _           | AVDD_D2_DDR     | _    |  |

| AVDD_DSP    | DSP PLL Supply                         | Y16           | _           | AVDD_DSP        | _    |  |

| AVDD_MAPLE  | MAPLE PLL Supply                       | Y20           |             | AVDD_MAPLE      | _    |  |

| SD1AVDD     | SerDes PLL Supply                      | AC22          | _           | SD1AVDD         | _    |  |

| SD2AVDD     | SerDes PLL Supply                      | AB19          | _           | SD2AVDD         | _    |  |

| POVDD1      | Secure Fuse Programming Overdrive      | N23           |             | POVDD1          | 8    |  |

| POVDD2      | Central Fuse Programming Overdrive—DSP | P23           | _           | _               | 8    |  |

| POVDD3      | Central Fuse Programming Overdrive—DSP | AA16          | _           | _               | 8    |  |

| FA_VDD      | POSt VDD                               | Y7            | _           | _               | 7    |  |

| VDDC        | Core/Platform Supply                   | J14           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | K14           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | L14           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | M14           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | N14           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | P10           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | P12           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | P14           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | R10           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | R12           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | R14           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | T10           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | T12           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | T14           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | U10           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | U12           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | U14           |             | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | V10           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | V12           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | V14           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | W10           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | W12           | _           | VDDC            | _    |  |

| VDDC        | Core/Platform Supply                   | W14           | _           | VDDC            | _    |  |

# 2.1.3 Output Driver Characteristics

This table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

**Table 4. Output Drive Capability**

| Driver Type                                           | Output Impedance (Ω)          | Supply Voltage                                                   | Note |

|-------------------------------------------------------|-------------------------------|------------------------------------------------------------------|------|

| IFC, GPIO[0:7], eSDHC                                 | 47 ± 7                        | BV <sub>DD</sub> = 3.3/2.5/1.8 V                                 | _    |

| DDR3 (programmable)                                   | 16<br>32 (half strength mode) | GV <sub>DD</sub> = 1.5 V DDR3<br>GV <sub>DD</sub> = 1.35 V DDR3L | 1    |

| eTSEC, USB                                            | 47 ± 7                        | LV <sub>DD</sub> = 3.3/2.5 V                                     | _    |

| DUART1, system control, I <sup>2</sup> C1, USIM, JTAG | 47 ± 7                        | OV <sub>DD</sub> = 3.3 V                                         | 2    |

| USB, eSPI1, DUART2, I <sup>2</sup> C2, USIM           | 47 ± 7                        | CV <sub>DD</sub> = 3.3/1.8 V                                     | 2    |

| RF parallel interface                                 | LVCMOS                        | X1V <sub>DD</sub> = 3.3/1.8 V                                    | _    |

| eSPI2, USB, TDM1, TDM2, RF parallel interface         | _                             | X2V <sub>DD</sub> = 3.3/1.8 V                                    | _    |

### Note:

# 2.2 Power Sequencing

The device requires its power rails to be applied in a specific sequence in order to ensure proper device operation. These requirements are as follows for power up:

- 1. VDD, VDDC, AVDD (all PLL supplies), XCOREVDD

- 2. LVDD, BVDD, CVDD, OVDD, X1VDD, X2VDD, G1VDD, G2VDD, XPADVDD

- 3. For secure boot fuse programming: After deassertion of HRESET\_B, drive POV<sub>DD1</sub> = 1.5 V after a required minimum delay per Table 5. After fuse programming is completed, it is required to return POV<sub>DD1</sub> = GND before the system is power cycled (HRESET\_B assertion) or powered down (V<sub>DDC</sub> ramp down) per the required timing specified in Table 5. See Section 3.14, "Security Fuse Processor," for additional details.

### WARNING

Only 100,000 POR cycles are permitted per lifetime of a device. Only one secure boot fuse programming event is permitted per lifetime of a device.

No activity other than that required for secure boot fuse programming is permitted while  $POV_{DD1}$  driven to any voltage above GND, including the reading of the fuse block. The reading of the fuse block may only occur while  $POV_{DD1} = GND$ .

$POV_{DD2}$  and  $POV_{DD3}$  are always tied to GND.

<sup>&</sup>lt;sup>1</sup> The drive strength of the DDR3 interface in half-strength mode is at  $T_j = 125$ °C and at  $GV_{DD}$  (min).

<sup>&</sup>lt;sup>2</sup> USIM pins are multiplexed with the pins of other interfaces. Check Table 3 for which power supply is used (BV<sub>DD</sub> or a CV<sub>DD</sub>) for each particular USIM pin.

#### DDR3 and DDR3L SDRAM Interface AC Timing Specifications 2.8.2

This section provides the AC timing specifications for the DDR SDRAM controller interface. The DDR controller supports DDR3 and DDR3L memories. Note that the required GV<sub>DD</sub>(typ) voltage is 1.5 V when interfacing to DDR3 SDRAM, and the required GV<sub>DD</sub>(typ) voltage is 1.35 V when interfacing to DDR3L SDRAM.

#### 2.8.2.1 DDR3 and DDR3L SDRAM Interface Input AC Timing Specifications

This table provides the input AC timing specifications for the DDR controller when interfacing to DDR3 SDRAM.

### Table 22. DDR3 SDRAM Interface Input AC Timing Specifications

For recommended operating conditions, see Table 3.

| Parameter             |                                              | Symbol            | Min                                              | Max                              | Unit | Note |

|-----------------------|----------------------------------------------|-------------------|--------------------------------------------------|----------------------------------|------|------|

| AC input low voltage  | > 1200 MHz data rate<br>≤ 1200 MHz data rate |                   | _                                                | MVREFn – 0.150<br>MVREFn – 0.175 | V    | _    |

| AC input high voltage | > 1200 MHz data rate<br>≤ 1200 MHz data rate | V <sub>IHAC</sub> | MVREF <i>n</i> + 0.150<br>MVREF <i>n</i> + 0.175 |                                  | V    | _    |

This table provides the input AC timing specifications for the DDR controller when interfacing to DDR3L SDRAM.

### Table 23. DDR3L SDRAM Interface Input AC Timing Specifications

For recommended operating conditions, see Table 3.

| Parar                 | neter                                        | Symbol            | Min                                              | Max                                              | Unit | Note |

|-----------------------|----------------------------------------------|-------------------|--------------------------------------------------|--------------------------------------------------|------|------|

| AC input low voltage  | > 1067 MHz data rate<br>≤ 1067 MHz data rate |                   |                                                  | MVREF <i>n</i> – 0.135<br>MVREF <i>n</i> – 0.160 | ٧    |      |

| AC input high voltage | > 1067 MHz data rate<br>≤ 1067 MHz data rate | V <sub>IHAC</sub> | MVREF <i>n</i> + 0.135<br>MVREF <i>n</i> + 0.160 | 1                                                | V    |      |

This table provides the input AC timing specifications for the DDR controller when interfacing to DDR3/3L SDRAM.

### Table 24. DDR3 and DDR3L SDRAM Interface Input AC Timing Specifications

At recommended operating conditions with GV  $_{DD}$  of 1.5 V  $\pm$  5% for DDR3 or 1.35 V  $\pm$  5% for DDR3L.

| Parameter                         | Symbol              | Min    | Max   | Unit | Note |

|-----------------------------------|---------------------|--------|-------|------|------|

| Controller Skew for MDQS—MDQ/MECC | t <sub>CISKEW</sub> | _      | _     | ps   | 1    |

| 1333 MHz data rate                |                     | -125   | 125   |      |      |

| 1200 MHz data rate                |                     | -147.5 | 147.5 |      |      |

| 1066 MHz data rate                |                     | -170   | 170   |      |      |

| 800 MHz data rate                 |                     | -200   | 200   |      |      |

| 667 MHz data rate                 |                     | -240   | 240   |      |      |

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1 Freescale Semiconductor 67

## 2.18.1 GPIO DC Electrical Characteristics

This table provides the DC electrical characteristics for the GPIO interface when operating from 3.3-V supply.

### Table 59. GPIO DC Electrical Characteristics (3.3 V)

For recommended operating conditions, see Table 3

| Parameter                                                                     | Symbol          | Min | Max | Unit | Note |

|-------------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                            | V <sub>IH</sub> | 2   | _   | V    | 1    |

| Input low voltage                                                             | V <sub>IL</sub> | _   | 0.8 | V    | 1    |

| Input current (BV <sub>IN</sub> = 0 V or BV <sub>IN</sub> = BV <sub>DD)</sub> | I <sub>IN</sub> | _   | ±40 | μΑ   | 2    |

| Output high voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA)      | V <sub>OH</sub> | 2.4 | _   | V    | _    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)  | V <sub>OL</sub> | _   | 0.4 | V    | _    |

#### Note:

- 1. Note that the min  $V_{IL}$  and max  $V_{IH}$  values are based on the min and max  $BV_{IN}$  respective values found in Table 3.

- 2. Note that the symbol BV<sub>IN</sub> represents the input voltage of the supply. It is referenced in Table 3.

This table provides the DC electrical characteristics for the GPIO interface when operating from 2.5-V supply.

## Table 60. GPIO DC Electrical Characteristics (2.5 V)

For recommended operating conditions, see Table 3.

| Parameter                                                                     | Symbol          | Min | Max | Unit | Note |

|-------------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| Input high voltage                                                            | V <sub>IH</sub> | 1.7 | _   | V    | 1    |

| Input low voltage                                                             | V <sub>IL</sub> | _   | 0.7 | V    | 1    |

| Input current (BV <sub>IN</sub> = 0 V or BV <sub>IN</sub> = BV <sub>DD)</sub> | I <sub>IN</sub> | _   | ±40 | μΑ   | 2    |

| Output high voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = 2 mA)       | V <sub>OH</sub> | 1.7 | _   | V    | _    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)  | V <sub>OL</sub> | _   | 0.7 | V    | _    |

#### Note:

- 1. Note that the min  $V_{IL}$  and max  $V_{IH}$  values are based on the min and max  $BV_{IN}$  respective values found in Table 3.

- 2. Note that the symbol BV<sub>IN</sub> represents the input voltage of the supply. It is referenced in Table 3.

This table provides the DC electrical characteristics for the GPIO interface when operating from 1.8-V supply.

### Table 61. GPIO DC Electrical Characteristics (1.8 V)

For recommended operating conditions, see Table 3.

| Parameter                                                                     | Symbol          | Min  | Max | Unit | Note |

|-------------------------------------------------------------------------------|-----------------|------|-----|------|------|

| Input high voltage                                                            | V <sub>IH</sub> | 1.2  | _   | V    | 1    |

| Input low voltage                                                             | V <sub>IL</sub> | _    | 0.6 | V    | 1    |

| Input current (BV <sub>IN</sub> = 0 V or BV <sub>IN</sub> = BV <sub>DD)</sub> | I <sub>IN</sub> | _    | ±40 | μΑ   | 2    |

| Output high voltage (BV <sub>DD</sub> = min, I <sub>OH</sub> = -0.5 mA)       | V <sub>OH</sub> | 1.35 | _   | V    | _    |

| Low-level output voltage (BV <sub>DD</sub> = min, I <sub>OL</sub> = 0.5 mA)   | V <sub>OL</sub> | _    | 0.4 | V    | _    |

## BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1

#### **Electrical Characteristics**

## Table 61. GPIO DC Electrical Characteristics (1.8 V) (continued)

For recommended operating conditions, see Table 3.

| Parameter | Symbol | Min | Max | Unit | Note |

|-----------|--------|-----|-----|------|------|

|-----------|--------|-----|-----|------|------|

#### Note:

- 1. Note that the min  $V_{IL}$  and max  $V_{IH}$  values are based on the min and max  $BV_{IN}$  respective values found in Table 3.

- 2. Note that the symbol BV<sub>IN</sub> represents the input voltage of the supply. It is referenced in Table 3.

# 2.18.2 GPIO AC Timing Specifications

This table provides the GPIO input and output AC timing specifications.

## Table 62. GPIO Input AC Timing Specifications

For recommended operating conditions, see Table 3

| Parameter                       | Symbol             | Min | Unit | Note |

|---------------------------------|--------------------|-----|------|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub> | 20  | ns   | 1    |

#### Note:

1. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> to ensure proper operation.

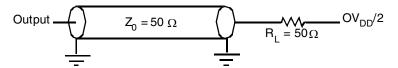

This figure provides the AC test load for the GPIO.

Figure 32. GPIO AC Test Load

## 2.19 TDM

This section describes the DC and AC electrical specifications for the TDM.

## 2.19.1 TDM DC Electrical Characteristics

This table provides the DC electrical characteristics for the TDM interface when operating at 3.3 V.

## Table 63. TDM DC Electrical Characteristics (X2V<sub>DD</sub> = 3.3 V)

For recommended operating conditions, see Table 3.

| Characteristic                                                       | Symbol          | Min  | Max | Unit | Note |

|----------------------------------------------------------------------|-----------------|------|-----|------|------|

| Input high voltage                                                   | V <sub>IH</sub> | 2.0  | _   | V    | 1    |

| Input low voltage                                                    | V <sub>IL</sub> | -0.3 | 0.8 | V    | 1    |

| Input current $(X2V_{IN} = 0 \text{ V or } X2V_{IN} = X2V_{DD})$     | I <sub>IN</sub> | _    | ±40 | μΑ   | 2    |

| Output high voltage ( $X2V_{DD} = min$ , $I_{OH} = -2 mA$ )          | V <sub>OH</sub> | 2.4  | _   | V    | _    |

| Output low voltage (X2V <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA) | V <sub>OL</sub> | _    | 0.4 | V    | _    |

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1

## Table 63. TDM DC Electrical Characteristics (X2V<sub>DD</sub> = 3.3 V) (continued)

For recommended operating conditions, see Table 3.

| Characteristic | Symbol | Min | Max | Unit | Note |  |

|----------------|--------|-----|-----|------|------|--|

|----------------|--------|-----|-----|------|------|--|

#### Note:

- 1. Note that the min  $V_{IL}$  and max  $V_{IH}$  values are based on the min and max  $X2V_{IN}$  respective values found in Table 3

- 2. Note that the symbol X2V<sub>IN</sub> represents the input voltage of the supply. It is referenced in Table 3

This table provides the DC electrical characteristics for the TDM interface when operating at 1.8 V.

## Table 64. TDM DC Electrical Characteristics (X2V<sub>DD</sub> = 1.8 V)

For recommended operating conditions, see Table 3.

| Parameter                                                            | Symbol          | Min  | Max | Unit | Note |

|----------------------------------------------------------------------|-----------------|------|-----|------|------|

| Input high voltage                                                   | V <sub>IH</sub> | 1.25 | _   | V    | 1    |

| Input low voltage                                                    | V <sub>IL</sub> | _    | 0.6 | V    | 1    |

| Input current $(X2V_{IN} = 0 \text{ V or } X2V_{IN} = X2V_{DD})$     | I <sub>IN</sub> | _    | ±40 | μΑ   | 2    |

| Output high voltage ( $X2V_{DD} = min$ , $I_{OH} = -2 mA$ )          | V <sub>OH</sub> | 1.35 | _   | V    |      |

| Output low voltage (X2V <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA) | V <sub>OL</sub> | _    | 0.4 | V    | _    |

#### Note:

- 1. Note that the min  $V_{IL}$  and max  $V_{IH}$  values are based on the min and max  $X2V_{IN}$  respective values found in Table 3

- 2. Note that the symbol X2V<sub>IN</sub> represents the input voltage of the supply. It is referenced in Table 3

## 2.19.2 TDM AC Electrical Characteristics

This table provides the input and output AC timing specifications for the TDM interface.

Table 65. TDM AC Timing Specifications for 62.5 MHz<sup>1</sup>

| Parameter                                    | Symbol <sup>2</sup>   | Min  | Max  | Unit | Note |

|----------------------------------------------|-----------------------|------|------|------|------|

| TDMxRCK/TDMxTCK                              | t <sub>DM</sub>       | 16.0 | _    | ns   | 3    |

| TDMxRCK/TDMxTCK high pulse width             | t <sub>DM_HIGH</sub>  | 7.0  | _    | ns   | 3    |

| TDMxRCK/TDMxTCK low pulse width              | t <sub>DM_LOW</sub>   | 7.0  | _    | ns   | 3    |

| TDM all input setup time                     | t <sub>DMIVKH</sub>   | 3.6  | _    | ns   | 4, 5 |

| TDMxRD input hold time                       | t <sub>DMRDIXKH</sub> | 1.9  | _    | ns   | 4, 8 |

| TDMxTFS/TDMxRFS input hold time              | t <sub>DMFSIXKH</sub> | 1.9  | _    | ns   | 5    |

| TDMxTCK high to TDMxTD output active         | t <sub>DM_OUTAC</sub> | 2.5  | _    | ns   | 7    |

| TDMxTCK high to TDMxTD output valid          | t <sub>DMTKHOV</sub>  | _    | 9.8  | ns   | 7, 9 |

| TDMxTD hold time                             | t <sub>DMTKHOX</sub>  | 2.5  | _    | ns   | 7    |

| TDMxTCK high to TDMxTD output high impedance | t <sub>DM_OUTHI</sub> | _    | 9.8  | ns   | 7    |

| TDMxTFS/TDMxRFS output valid                 | t <sub>DMFSKHOV</sub> | _    | 9.25 | ns   | 6    |

| TDMxTFS/TDMxRFS output hold time             | t <sub>DMFSKHOX</sub> | 2.0  | _    | ns   | 6    |

| Term                                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Differential Waveform                | The differential waveform is constructed by subtracting the inverting signal (SD_TX_B[0:3], for example) from the non-inverting signal (SD_TX_B[0:3], for example) within a differential pair. There is only one signal trace curve in a differential waveform. The voltage represented in the differential waveform is not referenced to ground. Refer to Figure 36 as an example for differential waveform.                                                                                                                                                                                                                           |

| Common Mode Voltage, V <sub>cm</sub> | The common mode voltage is equal to half of the sum of the voltages between each conductor of a balanced interchange circuit and ground. In this example, for SerDes output, $V_{cm\_out} = (V_{SD\_TX[0:3]} + V_{SD\_TX\_B[0:3]}) \div 2 = (A + B) \div 2$ , which is the arithmetic mean of the two complimentary output voltages within a differential pair. In a system, the common mode voltage may often differ from one component's output to the other's input. It may be different between the receiver input and driver output circuits within the same component. It is also referred to as the DC offset on some occasions. |

To illustrate these definitions using real values, consider the example of a current mode logic (CML) transmitter that has a common mode voltage of 2.25 V and outputs, TD and TD\_B. If these outputs have a swing from 2.0 V to 2.5 V, the peak-to-peak voltage swing of each signal (TD or TD\_B) is 500 mV p-p, which is referred to as the single-ended swing for each signal. Because the differential signaling environment is fully symmetrical in this example, the transmitter output differential swing ( $V_{OD}$ ) has the same amplitude as each signal single-ended swing. The differential output signal ranges between 500 mV and -500 mV. In other words,  $V_{OD}$  is 500 mV in one phase and -500 mV in the other phase. The peak differential voltage ( $V_{DIFFp}$ ) is 500 mV. The peak-to-peak differential voltage ( $V_{DIFFp-p}$ ) is 1000 mV p-p.

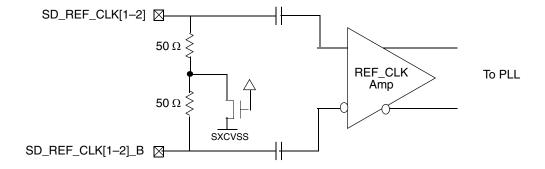

### 2.20.1.2 SerDes Reference Clock Receiver Characteristics

The SerDes reference clock inputs are applied to an internal PLL whose output creates the clock used by the corresponding SerDes lanes. The SerDes reference clock inputs are SD\_REF\_CLK1/SD\_REF\_CLK1\_B or SD\_REF\_CLK2/SD\_REF\_CLK2. B. Figure 37 shows a receiver reference diagram of the SerDes reference clocks.

Figure 37. Receiver of SerDes Reference Clocks

The characteristics of the clock signals are:

- The supply voltage requirements for XCOREV<sub>DD</sub> are as specified in Table 3.

- The SerDes reference clock receiver reference circuit structure is as follows:

- The SD\_REF\_CLK[1–2] and SD\_REF\_CLK[1–2]\_B are internally AC-coupled differential inputs as shown in Figure 37. Each differential clock input (SD\_REF\_CLK[1–2] or SD\_REF\_CLK[1–2]\_B has on-chip 50-Ω termination to XCOREVSS followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. Refer to the differential mode and single-ended mode descriptions below for detailed requirements.

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1

Table 73. CPRI Receiver DC Specifications (LV-II: 1.2288, 2.4576, 3.072, 4.9152, and 6.144 Gbps)

| Parameter                  | Symbol  | Min | Nom | Max  | Unit | Condition                                                                                                                                                                   |

|----------------------------|---------|-----|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input differential voltage | R_Vdiff | N/A |     | 1200 | mV   | It is assumed that for the R_Vdiff min specification, that the eye can be closed at the receiver after passing the signal through a CEI/CPRI Level II LR compliant channel. |

| Differential resistance    | R_Rdin  | 80  | _   | 120  | Ω    | _                                                                                                                                                                           |

Note: LV-II is CEI-6G-LR-based.

#### 2.20.2.4 **DC-Level Requirements for SGMII Configurations**

Table 74 describes the SGMII SerDes transmitter AC-coupled DC electrical characteristics. Specifications are valid at the recommended operating conditions listed in Table 3.

**Table 74. SGMII DC Transmitter Electrical Characteristics**

| Parameter                         | Symbo              | Min        | Nom | Max        | Unit | Conditions                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------|--------------------|------------|-----|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output<br>differential<br>voltage | IV <sub>OD</sub> I | 0.64 × Nom | 500 | 1.45 × Nom | mV   | <ul> <li>The IV<sub>OD</sub>I value shown in the Typ column is based on the condition of XV<sub>DD_SRDS2-Typ</sub> = 1.0 V, no common mode offset variation (V<sub>OS</sub> = 500mV), SerDes transmitter is terminated with 100-Ω differential load between SD_TXn and SD_TX_Bn.</li> <li>Amplitude setting:         L[0:3]TECR0[AMD_RED] = 0b000000     </li> </ul> |

| Output<br>differential<br>voltage | IV <sub>OD</sub> I | 0.64 × Nom | 459 | 1.45 × Nom | mV   | <ul> <li>The IV<sub>OD</sub>I value shown in the Typ column is based on the condition of XV<sub>DD_SRDS2-Typ</sub> = 1.0V, no common mode offset variation (V<sub>OS</sub> = 500mV), SerDes transmitter is terminated with 100-Ω differential load between SD_TXn and SD_TX_Bn.</li> <li>Amplitude setting:         L[0:3]TECR0[AMD_RED] = 0b000010     </li> </ul>  |

| Output<br>differential<br>voltage | IV <sub>OD</sub> I | 0.64 × Nom | 417 | 1.45 × Nom | mV   | <ul> <li>The IV<sub>OD</sub>I value shown in the Typ column is based on the condition of XV<sub>DD_SRDS2-Typ</sub> = 1.0V, no common mode offset variation (V<sub>OS</sub> = 500mV), SerDes transmitter is terminated with 100-Ω differential load between SD_TXn and SD_TX_Bn.</li> <li>Amplitude setting:         L[0:3]TECR0[AMD_RED] = 0b000101     </li> </ul>  |

| Output<br>differential<br>voltage | IV <sub>OD</sub> I | 0.64 × Nom | 376 | 1.45 × Nom | mV   | <ul> <li>The IV<sub>OD</sub>I value shown in the Typ column is based on the condition of XV<sub>DD_SRDS2-Typ</sub> = 1.0V, no common mode offset variation (V<sub>OS</sub> = 500mV), SerDes transmitter is terminated with 100-Ω differential load between SD_TXn and SD_TX_Bn.</li> <li>Amplitude setting:         L[0:3]TECR0[AMD_RED] = 0b001000     </li> </ul>  |

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1 Freescale Semiconductor 109

## Table 77. PCI Express 2.0 (2.5 Gbps) Differential Transmitter (Tx) Output AC Specifications (continued)

For recommended operating conditions, see Table 3.

| Parameter                                                             | Symbol                                    | Min  | Nom | Max   | Unit | Comments                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------|-------------------------------------------|------|-----|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tx eye width                                                          | T <sub>TX-EYE</sub>                       | 0.75 | _   | _     | UI   | The maximum transmitter jitter can be derived as $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.25$ UI. This does not include spread spectrum or REF_CLK jitter. It includes device random jitter at $10^{-12}$ . See notes 2 and 3.                                                                                                                                             |

| Time between the jitter median and maximum deviation from the median. | T <sub>TX-EYE-MEDIAN-</sub> to-MAX-JITTER |      |     | 0.125 | UI   | Jitter is defined as the measurement variation of the crossing points (V <sub>TX-DIFFp-p</sub> = 0 V) in relation to a recovered Tx UI. A recovered Tx UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the Tx UI. See notes 2 and 3. |

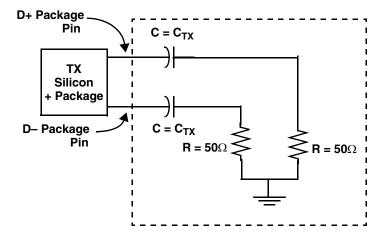

| AC coupling capacitor                                                 | C <sub>TX</sub>                           | 75   | ı   | 200   | nF   | All transmitters must be AC coupled. The AC coupling is required either within the media or within the transmitting component itself. See note 4.                                                                                                                                                                                                                         |

### Note:

- <sup>1</sup> No test load is necessarily associated with this value.

- Specified at the measurement point into a timing and voltage test load as shown in Figure 47 and measured over any 250 consecutive Tx UIs.

- <sup>3</sup> A T<sub>TX-EYE</sub> = 0.75 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-NAX-JITTER</sub> = 0.25 UI for the transmitter collected over any 250 consecutive Tx UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total Tx jitter budget collected over any 250 consecutive Tx UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

- $^4$  The DSP device SerDes transmitter does not have a built-in  $C_{TX}$ . An external AC coupling capacitor is required.

Table 78. PCI Express 2.0 (2.5 Gbps) Differential Receiver (Rx) Input AC Specifications

| Parameter                                                                     | Symbol                                       | Min    | Nom    | Max    | Unit | Comments                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------|----------------------------------------------|--------|--------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unit Interval                                                                 | UI                                           | 399.88 | 400.00 | 400.12 | ps   | Each UI is 400 ps ± 300 ppm. UI does not account for spread spectrum clock dictated variations. See note 1.                                                                                                                                                                                                                                                                    |

| Minimum receiver eye width                                                    | T <sub>RX-EYE</sub>                          | 0.4    | _      | _      | UI   | The maximum interconnect media and Transmitter jitter that can be tolerated by the Receiver can be derived as $T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$ UI. See notes 2 and 3.                                                                                                                                                                                                |

| Maximum time between the jitter median and maximum deviation from the median. | T <sub>RX-EYE-MEDIAN-</sub><br>to-MAX-JITTER | _      | _      | 0.3    | UI   | Jitter is defined as the measurement variation of the crossing points (V <sub>RX-DIFFp-p</sub> = 0 V) in relation to a recovered Tx UI. A recovered Tx UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the Tx UI.  See notes 2, 3, and 4. |

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1

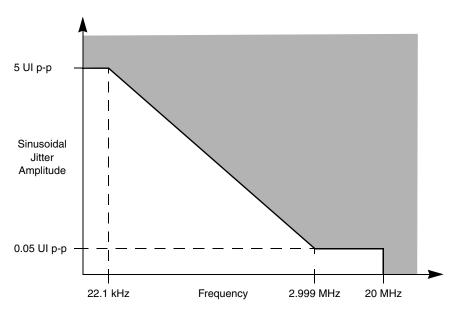

Figure 46. Single Frequency Sinusoidal Jitter Limits for Baud Rate 5.0 Gbps

## 2.20.3.6 Compliance Test and Measurement Load

Transmitter and receiver AC characteristics are measured at the transmitter outputs (SD\_TXn and SD\_TX\_Bn) or at the receiver inputs (SD\_RXn and SD\_RXn\_B). The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 47.

### NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary. If the vendor does not explicitly state where the measurement point is located, the measurement point is assumed to be the D+ and D- package pins.

Figure 47. Compliance Test/Measurement Load

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1

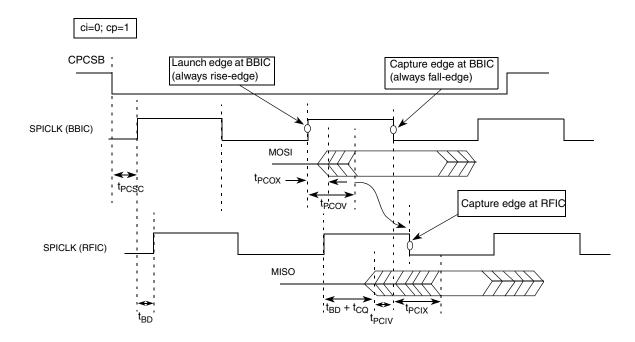

t<sub>BD</sub>: Board delay from the BSC9132 BBIC to the external RFIC or **Data timing at RF parallel interface:**

t<sub>CO</sub>: Delay in RFIC from input of SPICLK to output valid data Max permissible board skew: 100 ps Proposed frequency of SPICLK: 30 MHz

Input data setup requirement: 1 ns Input data hold requirement: 0 ns t<sub>CO</sub>: 4.5 ns-6.5 ns (6.5 ns is critical, which defines the max frequency)

Figure 49. RF Parallel Control Plane Interface AC Timing Diagram

#### 2.22 **Universal Subscriber Identity Module (USIM)**

The USIM module interface consist of a total of five pins. Only "Internal One Wire" interface mode is supported. In this mode, the Rx input of the USIM IP is connected to the TX output of the USIM, which is internal to the device. Only one bidirectional signal (Rx/Tx) is routed to the device pin, which is connected to the external SIM card.

The interface is meant to be used with synchronous SIM cards. This means that the SIM module provides a clock for the SIM card to use. The frequency of this clock is normally 372 times the data rate on the Rx/Tx pins; however, the SIM module can work with CLK equal to 16 times the data rate on Rx/Tx pins.

There is no timing relationship between the clock and the data. The clock that the SIM module provides to the SIM card will be used by the SIM card to recover the clock from the data much like a standard UART. All five pins of SIM module are asynchronous to each other.

There are no required timing relationships between the pads in normal mode, The SIM card is initiated by the interface device, whereupon the SIM card will send a response with an Answer to Reset. Although the SIM interface has no specific requirement, the ISO-7816 specifies reset and power down sequences. For detailed information, see ISO-7816.

The USIM interface pins are available at two locations. At one location, it is multiplexed with eSDHC and TDM functionality and is powered by the BVDD power supply (3.3V/2.5V/1.8V). At the other location, it is multiplexed with eSPI and UART functionality and is powered by CVDD power supply (3.3V/1.8V).

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1 Freescale Semiconductor 123

**Hardware Design Considerations**

## 3.2.1 DSP Clock Ranges

Table 104 provides the clocking specifications for the SC3850 processor core, MAPLE, and DSP memory.

**Table 104. DSP Processor Clocking Specifications**

| DSP Core           | Minimum Frequency | Maximum Frequency | Unit |

|--------------------|-------------------|-------------------|------|

| SC3850 cores       | 800               | 1200              | MHz  |

| MAPLE eVTPE        | 800               | 800               | MHz  |

| DSP DDR Controller | 800               | 1333              | MHz  |

# 3.2.2 DSPCLKIN and SC3850 Core Frequency Options

Table 105 shows the expected frequency options for DSPCLKIN and SC3850 core frequencies.

Table 105. Options for SC3850 Core0 and Core1 Clocking

| PLL_T2 MF | DSPCLKIN Frequency (MHz) |                             |      |      |  |  |  |  |

|-----------|--------------------------|-----------------------------|------|------|--|--|--|--|

|           | 66.66                    | 80                          | 100  | 133  |  |  |  |  |

|           |                          | SC3850 Core Frequency (MHz) |      |      |  |  |  |  |

| 1         | 66.66                    | 80                          | 100  | 133  |  |  |  |  |

| 6         | 400                      | 480                         | 600  | 800  |  |  |  |  |

| 7.5       | 500                      | 600                         | 750  | 1000 |  |  |  |  |

| 8         | 533                      | 640                         | 800  | 1066 |  |  |  |  |

| 9         | 600                      | 720                         | 900  | 1200 |  |  |  |  |

| 10        | 667                      | 800                         | 1000 | _    |  |  |  |  |

| 12        | 800                      | 960                         | 1200 | _    |  |  |  |  |

| 15        | 1000                     | 1200                        | _    | _    |  |  |  |  |

# 3.3 Supply Power Default Setting

This device is capable of supporting multiple power supply levels on its I/O supply. Table 106 through Table 110 shows the encoding used to select the voltage level for each I/O supply. When setting the VSEL signals, "1" is selected through a pull-up resistor to OVDD (as seen in Table 1).

Table 106. Default Voltage Level for BV<sub>DD</sub>

| BVDD_VSEL[0:1] | I/O Voltage Level |

|----------------|-------------------|

| 00             | 3.3 V             |

| 01             | 2.5 V             |

| 10             | 1.8 V             |

| 11             | Reserved          |

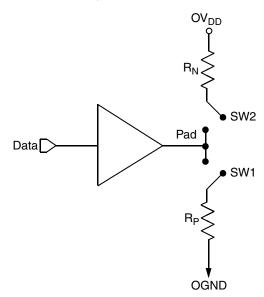

# 3.9 Output Buffer DC Impedance

The drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 58). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N) \div 2$ .

Figure 58. Driver Impedance Measurement

Table 111 summarizes the signal impedance targets. The driver impedances are targeted at minimum  $V_{DDC}$ , nominal  $OV_{DD}$ , 90°C.

| Impedance      | IFC, Ethernet, DUART, Control, Configuration, Power Management | DDR DRAM  | Symbol         | Unit |

|----------------|----------------------------------------------------------------|-----------|----------------|------|

| R <sub>N</sub> | 43 Target                                                      | 20 Target | Z <sub>0</sub> | W    |

| R <sub>P</sub> | 43 Target                                                      | 20 Target | $Z_0$          | W    |

**Table 111. Impedance Characteristics**

Note: Nominal supply voltages. See Table 2.

# 3.10 Configuration Pin Muxing

The device provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While HRESET\_B is asserted however, these pins are treated as inputs. The value presented on these pins while HRESET\_B is asserted, is latched when HRESET\_B deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Most of these sampled configuration pins are equipped with an on-chip gated resistor of approximately  $20 \text{ k}\Omega$ . This value should permit the  $4.7\text{-k}\Omega$  resistor to pull the configuration pin to a valid logic low level. The pull-up resistor is enabled only during HRESET\_B (and for platform/system clocks after HRESET\_B deassertion to ensure capture of the reset value). When the input receiver is disabled the pull-up is also, thus allowing functional operation of the pin as an output with

BSC9132 QorlQ Qonverge Baseband Processor Data Sheet, Rev. 1