#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                       |

|---------------------------------|--------------------------------------------------------------|

| Core Processor                  | -                                                            |

| Number of Cores/Bus Width       | -                                                            |

| Speed                           | -                                                            |

| Co-Processors/DSP               | -                                                            |

| RAM Controllers                 | -                                                            |

| Graphics Acceleration           | -                                                            |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | -                                                            |

| SATA                            | -                                                            |

| USB                             | -                                                            |

| Voltage - I/O                   | -                                                            |

| Operating Temperature           | -                                                            |

| Security Features               | -                                                            |

| Package / Case                  | -                                                            |

| Supplier Device Package         | -                                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=bsc9132nsn7mnmb |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

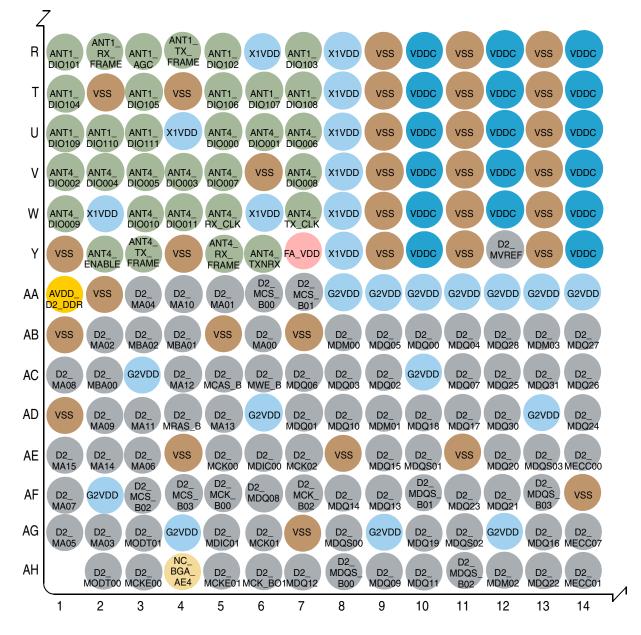

Figure 5 shows detailed view C.

DETAIL C

Figure 5. Ball Layout Diagram—Detail C

**Pin Assignments**

| Table 1 | . BSC9132 | Pinout L | isting | (continued) |

|---------|-----------|----------|--------|-------------|

|---------|-----------|----------|--------|-------------|

| Signal                                  | Signal Description                                                           | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |

|-----------------------------------------|------------------------------------------------------------------------------|---------------|-------------|-----------------|------|

| IFC_AD12/<br>GPIO38/<br>IRQ09           | IFC Muxed Address,Data                                                       | G26           | I/O         | BVDD            | -    |

| IFC_AD13/<br>GPIO39/<br>IRQ07           | IFC Muxed Address,Data                                                       | G27           | I/O         | BVDD            | -    |

| IFC_AD14/<br>GPIO40/<br>IRQ06           | IFC Muxed Address,Data                                                       | G28           | I/O         | BVDD            | -    |

| <b>IFC_AD15</b> /<br>GPIO41/<br>TIMER02 | IFC Muxed Address,Data                                                       | H28           | I/O         | BVDD            | -    |

| IFC_ADDR16/<br>GPO08                    | IFC Address                                                                  | H26           | 0           | BVDD            | 2    |

| IFC_ADDR17/<br>GPO09                    | IFC Address                                                                  | H25           | 0           | BVDD            | 2    |

| IFC_ADDR18/<br>GPO10                    | IFC Address                                                                  | H24           | 0           | BVDD            | 2    |

| IFC_ADDR19/<br>GPO11                    | IFC Address                                                                  | H22           | 0           | BVDD            | 2    |

| IFC_ADDR20/<br>GPO12                    | IFC Address                                                                  | H21           | 0           | BVDD            | 2    |

| IFC_ADDR21/<br>GPO13                    | IFC Address                                                                  | J28           | 0           | BVDD            | 2    |

| IFC_ADDR22/<br>GPO14                    | IFC Address                                                                  | J27           | 0           | BVDD            | 18   |

| IFC_ADDR23/<br>GPO15                    | IFC Address                                                                  | J25           | 0           | BVDD            | 2    |

| IFC_ADDR24/<br>GPO16                    | IFC Address                                                                  | J24           | 0           | BVDD            | 2    |

| IFC_ADDR25/<br>GPO17                    | IFC Address                                                                  | J23           | 0           | BVDD            | 2    |

| IFC_ADDR26/<br>GPO18                    | IFC Address                                                                  | J22           | 0           | BVDD            | 2    |

| IFC_AVD/<br>GPO54                       | IFC Address Valid                                                            | L28           | 0           | BVDD            | 2    |

| IFC_CS_B00/<br>GPO55                    | IFC Chip Select                                                              | K21           | 0           | BVDD            | -    |

| IFC_CS_B01/<br>GPO64                    | IFC Chip Select                                                              | K28           | 0           | BVDD            | -    |

| IFC_CS_B02/<br>GPO65                    | IFC Chip Select                                                              | L24           | 0           | BVDD            | -    |

| IFC_WE_B/<br>GPO52                      | IFC Write Enable/GPCM Write Byte Select0/<br>Generic ASIC i/f Start of Frame | L26           | 0           | BVDD            | 2    |

**Pin Assignments**

| Signal                                | Signal Description        | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |

|---------------------------------------|---------------------------|---------------|-------------|-----------------|------|

| SPI1_CS3_B/<br>CKSTP1_OUT_B/<br>GPO76 | Checkstop Out             | M23           | 0           | CVDD            | - 1  |

| READY/<br>ASLEEP/<br>READY_P1         | Ready/Trigger Out/Asleep  | U21           | 0           | OVDD            | 2    |

| UDE_B0                                | Unconditional Debug Event | T21           | I           | OVDD            |      |

| UDE_B1                                | Unconditional Debug Event | T22           | I           | OVDD            | _    |

| EE0                                   | DSP Debug Request         | T26           | I           | OVDD            | _    |

| EE1                                   | DSP Debug Acknowledge     | T25           | 0           | OVDD            | 2    |

| TMP_DETECT                            | Tamper Detect             | T23           | I           | OVDD            | —    |

| UART_RTS_B00/<br>PPS_LED/<br>GPO43    | UART0 Ready to Send       | AB26          | 0           | OVDD            | -    |

|                                       | Clocking                  |               |             |                 |      |

| SYSCLK                                | System Clock              | AE28          | I           | OVDD            |      |

| D1_DDRCLK                             | DDR PLL Reference Clock   | V28           | I           | OVDD            | _    |

| D2_DDRCLK                             | DDR PLL Reference Clock   | AC28          | I           | OVDD            | _    |

| RTC                                   | Real Time Clock           | AG28          | I           | OVDD            | —    |

| DSP_CLKIN                             | DSP PLL Reference Clock   | W26           | I           | OVDD            | —    |

| TSEC_1588_PULSE_OUT1/<br>PPS_OUT      | PPS Pulse Out             | AA24          | 0           | LVDD            | 2    |

|                                       | I/O Voltage Select        |               |             |                 |      |

| BVDD_VSEL00                           | BVDD Voltage Selection    | AB23          | I           | OVDD            | _    |

| BVDD_VSEL01                           | BVDD Voltage Selection    | AA27          | I           | OVDD            | _    |

| CVDD_VSEL                             | CVDD Voltage Selection    | W25           | I           | OVDD            | —    |

| LVDD_VSEL                             | LVDD Voltage Selection    | AD26          | I           | OVDD            | —    |

| XVDD1_VSEL                            | XVDD 1 Voltage Selection  | AC27          | I           | OVDD            | —    |

| XVDD2_VSEL                            | XVDD 2 Voltage Selection  | AD28          | I           | OVDD            | —    |

|                                       | Test                      |               |             |                 | •    |

| SCAN_MODE_B                           | Scan Mode                 | R28           | I           | OVDD            | 1    |

| CFG_0_JTAG_MODE                       | JTAG mode selection 0     | U22           | I           | OVDD            | 10   |

| CFG_1_JTAG_MODE                       | JTAG mode selection 1     | V22           | I           | OVDD            | 10   |

| TEST_SEL_B                            | Test Select               | U28           | I           | OVDD            | 11   |

|                                       | JTAG (Power Architect     | ure)          |             |                 | I    |

| тск                                   | Test Clock                | V23           | I           | OVDD            |      |

| TDI                                   | Test Data In              | U26           | I           | OVDD            | 3    |

| Dia Dia Demon                                                          |                     |               |             |                 |      |  |  |

|------------------------------------------------------------------------|---------------------|---------------|-------------|-----------------|------|--|--|

| Signal                                                                 | Signal Description  | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |  |  |

| IFC_AD09/<br>GPIO35                                                    | General Purpose I/O | F27           | I/O         | BVDD            | - 1  |  |  |

| IFC_AD10/<br>GPIO36                                                    | General Purpose I/O | F28           | I/O         | BVDD            | - 1  |  |  |

| IFC_AD11/<br><b>GPI037/</b><br>IRQ08                                   | General Purpose I/O | G25           | I/O         | BVDD            | - 1  |  |  |

| IFC_AD12/<br>GPI038/<br>IRQ09                                          | General Purpose I/O | G26           | I/O         | BVDD            | - 1  |  |  |

| IFC_AD13/<br>GPI039/<br>IRQ07                                          | General Purpose I/O | G27           | I/O         | BVDD            | - 1  |  |  |

| IFC_AD14/<br>GPIO40/<br>IRQ06                                          | General Purpose I/O | G28           | I/O         | BVDD            |      |  |  |

| IFC_AD15/<br>GPI041/<br>TIMER02                                        | General Purpose I/O | H28           | I/O         | BVDD            | - 1  |  |  |

| UART_CTS_B00/<br>SIM_PD/<br>TIMER04/<br><b>GPI042</b> /<br>IRQ04       | General Purpose I/O | AB27          | I/O         | OVDD            |      |  |  |

| UART_CTS_B01/<br>SYS_DMA_REQ/<br>SRESET_B/<br><b>GPI044</b> /<br>IRQ05 | General Purpose I/O | W22           | I/O         | OVDD            | - 1  |  |  |

| IIC1_SDA/<br>GPIO46                                                    | General Purpose I/O | V25           | I/O         | OVDD            | - 1  |  |  |

| IIC1_SCL/<br>GPIO47                                                    | General Purpose I/O | V24           | I/O         | OVDD            | - 1  |  |  |

| SDHC_CMD/<br>SIM_RST_B/<br>GPIO48                                      | General Purpose I/O | C26           | I/O         | BVDD            | - 1  |  |  |

| SDHC_DATA00/<br>SIM_TRXD/<br>GPIO49                                    | General Purpose I/O | D25           | I/O         | BVDD            | - 1  |  |  |

| SDHC_DATA01/<br>SIM_SVEN/<br>GPIO50                                    | General Purpose I/O | F23           | I/O         | BVDD            | - 1  |  |  |

| SDHC_DATA02/<br>SIM_PD/<br>GPI051                                      | General Purpose I/O | F24           | I/O         | BVDD            | - 1  |  |  |

## Table 1. BSC9132 Pinout Listing (continued)

**Pin Assignments**

| Signal | Signal Description | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |

|--------|--------------------|---------------|-------------|-----------------|------|

| G1VDD  | DDR Supply         | E11           | —           | G1VDD           |      |

| G1VDD  | DDR Supply         | H9            | —           | G1VDD           | —    |

| G1VDD  | DDR Supply         | H10           | —           | G1VDD           | _    |

| G1VDD  | DDR Supply         | H11           | —           | G1VDD           | _    |

| G1VDD  | DDR Supply         | H12           | —           | G1VDD           | —    |

| G1VDD  | DDR Supply         | H13           | —           | G1VDD           | —    |

| G1VDD  | DDR Supply         | H14           | —           | G1VDD           | —    |

| G1VDD  | DDR Supply         | H15           | —           | G1VDD           | —    |

| G1VDD  | DDR Supply         | H16           | —           | G1VDD           | —    |

| G1VDD  | DDR Supply         | H17           | —           | G1VDD           | _    |

| G1VDD  | DDR Supply         | H18           | —           | G1VDD           | —    |

| G1VDD  | DDR Supply         | H19           | —           | G1VDD           | _    |

| G1VDD  | DDR Supply         | H20           | —           | G1VDD           | _    |

| G1VDD  | DDR Supply         | B18           | —           | G1VDD           | _    |

| G1VDD  | DDR Supply         | B23           | —           | G1VDD           | _    |

| G1VDD  | DDR Supply         | D20           | —           | G1VDD           |      |

| G1VDD  | DDR Supply         | E15           | —           | G1VDD           |      |

| G2VDD  | DDR Supply         | AC3           | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AC10          | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AA8           | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AA9           | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AA10          | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AA11          | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AA12          | —           | G2VDD           | _    |

| G2VDD  | DDR Supply         | AA13          | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AA14          | —           | G2VDD           | —    |

| G2VDD  | DDR Supply         | AA15          | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AD6           | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AD13          | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AF2           | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AG4           | —           | G2VDD           |      |

| G2VDD  | DDR Supply         | AG9           |             | G2VDD           |      |

| G2VDD  | DDR Supply         | AG12          | _           | G2VDD           | —    |

| G2VDD  | DDR Supply         | AC15          |             | G2VDD           | —    |

| LVDD   | Ethernet Supply    | Y23           |             | LVDD            | - 1  |

| LVDD   | Ethernet Supply    | AA25          | _           | LVDD            | —    |

## Table 1. BSC9132 Pinout Listing (continued)

| Signal | Signal Description       | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |

|--------|--------------------------|---------------|-------------|-----------------|------|

| VSS    | Platform and Core Ground | C7            | —           | _               | _    |

| VSS    | Platform and Core Ground | D2            |             | —               |      |

| VSS    | Platform and Core Ground | D7            | —           | _               | —    |

| VSS    | Platform and Core Ground | D9            | —           | _               | _    |

| VSS    | Platform and Core Ground | E4            | —           | _               | —    |

| VSS    | Platform and Core Ground | E8            | —           | _               | —    |

| VSS    | Platform and Core Ground | F6            | —           | _               | —    |

| VSS    | Platform and Core Ground | F7            | —           | _               | —    |

| VSS    | Platform and Core Ground | F8            | —           | —               | —    |

| VSS    | Platform and Core Ground | F13           | —           | _               | —    |

| VSS    | Platform and Core Ground | G6            | —           | _               | —    |

| VSS    | Platform and Core Ground | G8            | —           | _               | —    |

| VSS    | Platform and Core Ground | H4            | —           | _               | —    |

| VSS    | Platform and Core Ground | H6            | —           | _               | —    |

| VSS    | Platform and Core Ground | H7            | —           | _               | —    |

| VSS    | Platform and Core Ground | H8            | —           | _               | —    |

| VSS    | Platform and Core Ground | J9            | —           | _               | —    |

| VSS    | Platform and Core Ground | J11           | —           | _               | —    |

| VSS    | Platform and Core Ground | K2            | —           | _               | —    |

| VSS    | Platform and Core Ground | K9            | —           | _               | —    |

| VSS    | Platform and Core Ground | K11           | —           | _               | —    |

| VSS    | Platform and Core Ground | K13           | —           | _               | —    |

| VSS    | Platform and Core Ground | L6            | —           | _               | —    |

| VSS    | Platform and Core Ground | L9            | —           | _               | —    |

| VSS    | Platform and Core Ground | L11           | —           | _               | —    |

| VSS    | Platform and Core Ground | L13           | —           | _               | —    |

| VSS    | Platform and Core Ground | M11           | —           | _               | —    |

| VSS    | Platform and Core Ground | M13           | —           | _               | _    |

| VSS    | Platform and Core Ground | M4            |             | —               |      |

| VSS    | Platform and Core Ground | M9            | —           | _               | _    |

| VSS    | Platform and Core Ground | N9            | —           | _               | _    |

| VSS    | Platform and Core Ground | N11           |             | _               | —    |

| VSS    | Platform and Core Ground | N13           |             | _               | —    |

| VSS    | Platform and Core Ground | P9            |             | _               | —    |

| VSS    | Platform and Core Ground | P11           | -           | _               | —    |

| VSS    | Platform and Core Ground | P13           |             | _               | —    |

## Table 1. BSC9132 Pinout Listing (continued)

**Pin Assignments**

#### Table 1. BSC9132 Pinout Listing (continued)

| Signal | Signal Description   | Pin<br>Number | Pin<br>Type | Power<br>Supply | Note |

|--------|----------------------|---------------|-------------|-----------------|------|

| NC     | Address Parity Error | E19           |             | _               |      |

| NC     | Address Parity Error | AH4           | _           |                 | _    |

<sup>1</sup> These are test signals for factory use only and must be pulled up (with 100  $\Omega$ -1 k $\Omega$ ) to OVDD for normal operation.

<sup>2</sup> This pin is a reset configuration pin. It has a weak internal pull-up P-FET which is enabled only when the processor is in the reset state. This pull-up is designed such that it can be overpowered by an external 4.7-k pull-down resistor. However, if the signal is intended to be high after reset, and if there is any device on the net which might pull down the value of the net at reset, then a pull up or active driver is needed.

- <sup>3</sup> These pins have weak internal pull-up P-FETs that are always enabled.

- <sup>4</sup> This pin must NOT be pulled down during power-on reset.

- <sup>5</sup> This pin is an open drain signal.

- $^{6}~$  This pin should be pulled down with 200 $\Omega$  ± 1% resistor when used in autocalibration mode.

- $^7~$  This pin should be pulled down to VSS with 10 k $\Omega$ .

- <sup>8</sup> This pin is used for fuse programming. Should be tied to VSS for normal operation (fuse read). See section Section 2.2, "Power Sequencing," for more details.

- <sup>9</sup> This pin may be connected to a temperature diode monitoring device such as the Analog Devices, ADT7461A<sup>™</sup>. If a temperature diode monitoring device will not be connected, these pins may be connected to test point or left as a no connect.

- <sup>10</sup> Pin should be pulled high or low depending on the JTAG topology selected. Refer to Section 3.11, "JTAG Configuration Signals."

- <sup>11</sup> This pin should be tied to GND/VSS when MAPLE is powered down; otherwise it should be tied to OVDD.

- <sup>12</sup> This pin is an open-drain signal if the IIC2 pin is selected.

- <sup>13</sup> It has a weak internal pull-up P-FET which is enabled only when the processor is in the reset state. This pull-up is designed such that it can be overpowered by an external 4.7-k pull-down resistor. However, if the signal is intended to be high after reset, and if there is any device on the net which might pull down the value of the net at reset, then a pull up or active driver is needed.

- <sup>14</sup> MDIC00 is grounded through an 36.5 O precision 1% resistor and MDIC01 is connected to GVDD through an 36.5 O precision 1% resistor. These pins are used for automatic calibration of the DDR3/DDR3L IOs.

- $^{15}$  This pin should be pulled up to power rail with 10 k $\Omega.$

- <sup>16</sup> Do not use this pin as CD pin.

- $^{17}$  This pin should be pulled down to GND with 10 k $\Omega.$

- <sup>18</sup> This pin is a reset configuration pin without default value.

## 2.1.3 Output Driver Characteristics

This table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                                           | Output Impedance ( $\Omega$ ) | Supply Voltage                                                   | Note |

|-------------------------------------------------------|-------------------------------|------------------------------------------------------------------|------|

| IFC, GPIO[0:7], eSDHC                                 | 47 ± 7                        | BV <sub>DD</sub> = 3.3/2.5/1.8 V                                 | —    |

| DDR3 (programmable)                                   | 16<br>32 (half strength mode) | GV <sub>DD</sub> = 1.5 V DDR3<br>GV <sub>DD</sub> = 1.35 V DDR3L | 1    |

| eTSEC, USB                                            | 47 ± 7                        | LV <sub>DD</sub> = 3.3/2.5 V                                     | _    |

| DUART1, system control, I <sup>2</sup> C1, USIM, JTAG | 47 ± 7                        | OV <sub>DD</sub> = 3.3 V                                         | 2    |

| USB, eSPI1, DUART2, I <sup>2</sup> C2, USIM           | 47 ± 7                        | CV <sub>DD</sub> = 3.3/1.8 V                                     | 2    |

| RF parallel interface                                 | LVCMOS                        | X1V <sub>DD</sub> = 3.3/1.8 V                                    | _    |

| eSPI2, USB, TDM1, TDM2, RF parallel interface         | —                             | X2V <sub>DD</sub> = 3.3/1.8 V                                    |      |

## Table 4. Output Drive Capability

Note:

- <sup>1</sup> The drive strength of the DDR3 interface in half-strength mode is at  $T_j = 125^{\circ}C$  and at  $GV_{DD}$  (min).

- <sup>2</sup> USIM pins are multiplexed with the pins of other interfaces. Check Table 3 for which power supply is used (BV<sub>DD</sub> or a CV<sub>DD</sub>) for each particular USIM pin.

# 2.2 Power Sequencing

The device requires its power rails to be applied in a specific sequence in order to ensure proper device operation. These requirements are as follows for power up:

- 1. VDD, VDDC, AVDD (all PLL supplies), XCOREVDD

- 2. LVDD, BVDD, CVDD, OVDD, X1VDD, X2VDD, G1VDD, G2VDD, XPADVDD

- 3. For secure boot fuse programming: After deassertion of HRESET\_B, drive  $POV_{DD1} = 1.5 V$  after a required minimum delay per Table 5. After fuse programming is completed, it is required to return  $POV_{DD1} = GND$  before the system is power cycled (HRESET\_B assertion) or powered down ( $V_{DDC}$  ramp down) per the required timing specified in Table 5. See Section 3.14, "Security Fuse Processor," for additional details.

## WARNING

Only 100,000 POR cycles are permitted per lifetime of a device. Only one secure boot fuse programming event is permitted per lifetime of a device.

No activity other than that required for secure boot fuse programming is permitted while  $POV_{DD1}$  driven to any voltage above GND, including the reading of the fuse block. The reading of the fuse block may only occur while  $POV_{DD1} = GND$ .

$POV_{DD2}$  and  $POV_{DD3}$  are always tied to GND.

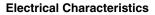

This figure provides the POV<sub>DD1</sub> timing diagram.

NOTE: POVDD must be stable at 1.5 V prior to initiating fuse programming.

### Figure 8. POV<sub>DD1</sub> Timing Diagram

This table provides information on the power-down and power-up sequence parameters for POV<sub>DD1</sub>.

Table 5. POV<sub>DD1</sub> Timing <sup>5</sup>

| Driver Type            | Min  | Мах | Unit                | Note |

|------------------------|------|-----|---------------------|------|

| tpovdd_delay           | 1500 | —   | <sup>t</sup> sysclk | 1    |

| tpovdd_prog            | 0    | —   | μs                  | 2    |

| t <sub>POVDD_VDD</sub> | 0    | —   | μS                  | 3    |

| tpovdd_rst             | 0    | —   | μs                  | 4    |

Note:

1. Delay required from the deassertion of HRESET\_B to driving POV<sub>DD1</sub> ramp up. Delay measured from HRESET\_B deassertion at 90% OV<sub>DD</sub> to 10% POV<sub>DD1</sub> ramp up.

2. Delay required from fuse programming finished to POV<sub>DD1</sub> ramp down start. Fuse programming must complete while POV<sub>DD1</sub> is stable at 1.5 V. No activity other than that required for secure boot fuse programming is permitted while POV<sub>DD1</sub> driven to any voltage above GND, including the reading of the fuse block. The reading of the fuse block may only occur while POV<sub>DD1</sub> = GND. After fuse programming is completed, it is required to return POV<sub>DD1</sub> = GND.

3. Delay required from POV<sub>DD1</sub> ramp down complete to V<sub>DDC</sub> ramp down start. POV<sub>DD1</sub> must be grounded to minimum 10% POV<sub>DD1</sub> before V<sub>DDC</sub> is at 90% V<sub>DDC</sub>.

4. Delay required from POV<sub>DD1</sub> ramp down complete to HRESET\_B assertion. POV<sub>DD1</sub> must be grounded to minimum 10% POV<sub>DD1</sub> before HRESET\_B assertion reaches 90% OV<sub>DD</sub>.

5. Only one secure boot fuse programming event is permitted per lifetime of a device.

All supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-up, the sequencing for  $GV_{DD}$  is not required.

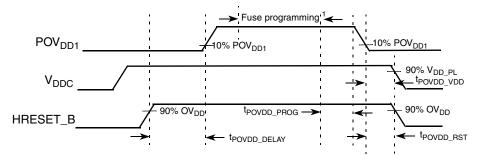

### Table 24. DDR3 and DDR3L SDRAM Interface Input AC Timing Specifications (continued)

At recommended operating conditions with  $GV_{DD}$  of 1.5 V ± 5% for DDR3 or 1.35 V ± 5% for DDR3L.

| Parameter                        | Symbol              | Min  | Мах | Unit | Note |

|----------------------------------|---------------------|------|-----|------|------|

| Tolerated Skew for MDQS—MDQ/MECC | t <sub>DISKEW</sub> | —    | —   | ps   | 2    |

| 1333 MHz data rate               |                     | -250 | 250 |      |      |

| 1200 MHz data rate               |                     | -275 | 275 |      |      |

| 1066 MHz data rate               |                     | -300 | 300 |      |      |

| 800 MHz data rate                |                     | -425 | 425 |      |      |

| 667 MHz data rate                |                     | -510 | 510 |      |      |

Note:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. This should be subtracted from the total timing budget.

The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ±(T ÷ 4 – abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

This figure shows the DDR3 and DDR3L SDRAM interface input timing diagram.

Figure 9. DDR3 and DDR3L SDRAM Interface Input Timing Diagram

## 2.8.2.2 DDR3 and DDR3L SDRAM Interface Output AC Timing Specifications

This table contains the output AC timing targets for the DDR3 and DDR3L SDRAM interface.

## Table 25. DDR3 and DDR3L SDRAM Interface Output AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 1.5 V ± 5% for DDR3 or 1.35 V ± 5% for DDR3L.

| Parameter         | Symbol <sup>1</sup> | Min | Мах | Unit | Note |

|-------------------|---------------------|-----|-----|------|------|

| MCK[n] cycle time | <sup>t</sup> мск    | 1.5 | 3   | ns   | 2    |

## Table 38. eTSEC IEEE 1588 DC Electrical Characteristics (LV<sub>DD</sub> = 2.5 V) (continued)

For recommended operating conditions with  $LV_{DD} = 2.5 V$

| Parameter                                                        | Symbol          | Min  | Мах  | Unit | Notes |

|------------------------------------------------------------------|-----------------|------|------|------|-------|

| Input current ( $LV_{IN} = 0$ V or $LV_{IN} = LV_{DD}$ )         | I <sub>IH</sub> | _    | ±40  | μA   | 2     |

| Output high voltage (LV <sub>DD</sub> = min, $I_{OH} = -1.0$ mA) | V <sub>OH</sub> | 2.00 | _    | V    | —     |

| Output low voltage (LV <sub>DD</sub> = min, $I_{OL}$ = 1.0 mA)   | V <sub>OL</sub> | _    | 0.40 | V    | _     |

#### Note:

1. The min  $V_{IL}$  and max  $V_{IH}$  values are based on the respective min and max  $LV_{IN}$  values found in Table 3.

2. The symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  symbols referenced in Table 2 and Table 3.

## 2.11.3.2 eTSEC IEEE Std 1588 AC Specifications

This table provides the IEEE Std 1588 AC timing specifications.

### Table 39. eTSEC IEEE 1588 AC Timing Specifications

For recommended operating conditions, see Table 3

| Parameter/Condition                | Symbol                                                  | Min                         | Тур | Мах                    | Unit | Note |

|------------------------------------|---------------------------------------------------------|-----------------------------|-----|------------------------|------|------|

| TSEC_1588_CLK clock period         | t <sub>T1588CLK</sub>                                   | 5                           |     | T <sub>RX_CLK</sub> *7 | ns   | 1, 3 |

| TSEC_1588_CLK duty cycle           | <sup>t</sup> т1588CLKH<br>/t <sub>T1588</sub> CLK       | 40                          | 50  | 60                     | %    | —    |

| TSEC_1588_CLK peak-to-peak jitter  | t <sub>T1588</sub> CLKINJ                               | —                           | _   | 250                    | ps   | _    |

| Rise time eTSEC_1588_CLK (20%-80%) | t <sub>T1588</sub> CLKINR                               | 1.0                         | _   | 2.0                    | ns   | _    |

| Fall time eTSEC_1588_CLK (80%-20%) | t <sub>T1588CLKINF</sub>                                | 1.0                         | _   | 2.0                    | ns   | _    |

| TSEC_1588_CLK_OUT clock period     | t <sub>T1588CLKOUT</sub>                                | 2 x t <sub>T1588CLK</sub>   | _   | —                      | ns   | _    |

| TSEC_1588_CLK_OUT duty cycle       | t <sub>T1588</sub> CLKOTH<br>/t <sub>T1588</sub> CLKOUT | 30                          | 50  | 70                     | %    | —    |

| TSEC_1588_PULSE_OUT                | t <sub>T1588OV</sub>                                    | 0.5                         | _   | 3.0                    | ns   | _    |

| TSEC_1588_TRIG_IN pulse width      | t <sub>T1588</sub> TRIGH                                | 2*t <sub>T1588CLK_MAX</sub> | _   | _                      | ns   | 2    |

#### Note:

1.T<sub>RX\_CLK</sub> is the max clock period of eTSEC receiving clock selected by TMR\_CTRL[CKSEL]. See the *BSC9132 QorlQ Qonverge Multicore Baseband Processor Reference Manual* for a description of TMR\_CTRL registers.

2. It needs to be at least two times the clock period of the clock selected by TMR\_CTRL[CKSEL]. See the *BSC9132 QorlQ Qonverge Multicore Baseband Processor Reference Manual* for a description of TMR\_CTRL registers.

The maximum value of t<sub>T1588CLK</sub> is not only defined by the value of T<sub>RX\_CLK</sub>, but also defined by the recovered clock. For example, for 10/100/1000 Mbps modes, the maximum value of t<sub>T1588CLK</sub> is 2800, 280, and 56 ns respectively.

### Table 42. USB General Timing Parameters (ULPI Mode) (continued)

For recommended operating conditions, see Table 3.

| Parameter | Symbol <sup>1</sup> | Min | Мах | Unit | Note |  |

|-----------|---------------------|-----|-----|------|------|--|

|-----------|---------------------|-----|-----|------|------|--|

#### Note:

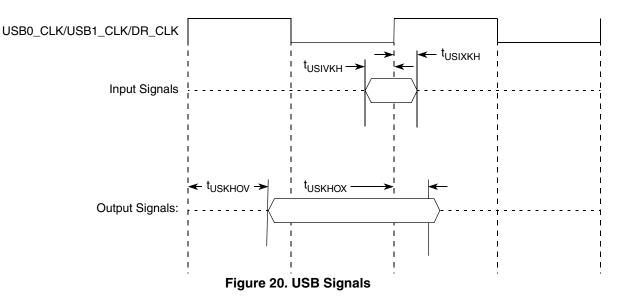

The symbols for timing specifications follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>USIXKH</sub> symbolizes USB timing (US) for the input (I) to go invalid (X) with respect to the time the USB clock reference (K) goes high (H). Also, t<sub>USKHOX</sub> symbolizes USB timing (US) for the USB timing (US) for the USB clock reference (K) to go high (H) with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to USB clock.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of the USB clock to  $0.4 \times OV_{DD}$  of the signal in question for 3.3 V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For active/float timing measurements, the high impedance or off state is defined to be when the total current delivered through the component pin is less than or equal to that of the leakage current specification.

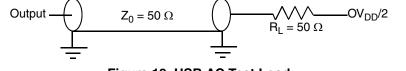

Figure 19 and Figure 20 provide the USB AC test load and signals, respectively.

Figure 19. USB AC Test Load

## Table 63. TDM DC Electrical Characteristics (X2V<sub>DD</sub> = 3.3 V) (continued)

For recommended operating conditions, see Table 3.

| Characteristic | Symbol | Min | Max | Unit | Note |

|----------------|--------|-----|-----|------|------|

|----------------|--------|-----|-----|------|------|

#### Note:

1. Note that the min  $V_{IL}$  and max  $V_{IH}$  values are based on the min and max  $X2V_{IN}$  respective values found in Table 3

2. Note that the symbol X2V<sub>IN</sub> represents the input voltage of the supply. It is referenced in Table 3

This table provides the DC electrical characteristics for the TDM interface when operating at 1.8 V.

## Table 64. TDM DC Electrical Characteristics (X2V<sub>DD</sub> = 1.8 V)

For recommended operating conditions, see Table 3.

| Parameter                                                                            | Symbol          | Min  | Max | Unit | Note |

|--------------------------------------------------------------------------------------|-----------------|------|-----|------|------|

| Input high voltage                                                                   | V <sub>IH</sub> | 1.25 | —   | V    | 1    |

| Input low voltage                                                                    | V <sub>IL</sub> | _    | 0.6 | V    | 1    |

| Input current (X2V <sub>IN</sub> = 0 V or<br>X2V <sub>IN</sub> = X2V <sub>DD</sub> ) | I <sub>IN</sub> | —    | ±40 | μΑ   | 2    |

| Output high voltage (X2V <sub>DD</sub> = min,<br>I <sub>OH</sub> = -2 mA)            | V <sub>OH</sub> | 1.35 | —   | V    | _    |

| Output low voltage (X2V <sub>DD</sub> = min, $I_{OL}$ = 2 mA)                        | V <sub>OL</sub> | —    | 0.4 | V    | —    |

#### Note:

1. Note that the min  $V_{IL}$  and max  $V_{IH}$  values are based on the min and max  $X2V_{IN}$  respective values found in Table 3

2. Note that the symbol X2V<sub>IN</sub> represents the input voltage of the supply. It is referenced in Table 3

## 2.19.2 TDM AC Electrical Characteristics

This table provides the input and output AC timing specifications for the TDM interface.

| Parameter                                    | Symbol <sup>2</sup>   | Min  | Max  | Unit | Note |

|----------------------------------------------|-----------------------|------|------|------|------|

| TDMxRCK/TDMxTCK                              | t <sub>DM</sub>       | 16.0 | —    | ns   | 3    |

| TDMxRCK/TDMxTCK high pulse width             | t <sub>DM_HIGH</sub>  | 7.0  |      | ns   | 3    |

| TDMxRCK/TDMxTCK low pulse width              | t <sub>DM_LOW</sub>   | 7.0  |      | ns   | 3    |

| TDM all input setup time                     | t <sub>DMIVKH</sub>   | 3.6  | —    | ns   | 4, 5 |

| TDMxRD input hold time                       | t <sub>DMRDIXKH</sub> | 1.9  | —    | ns   | 4, 8 |

| TDMxTFS/TDMxRFS input hold time              | t <sub>DMFSIXKH</sub> | 1.9  | _    | ns   | 5    |

| TDMxTCK high to TDMxTD output active         | <sup>t</sup> DM_OUTAC | 2.5  | —    | ns   | 7    |

| TDMxTCK high to TDMxTD output valid          | t <sub>DMTKHOV</sub>  | —    | 9.8  | ns   | 7, 9 |

| TDMxTD hold time                             | t <sub>DMTKHOX</sub>  | 2.5  | —    | ns   | 7    |

| TDMxTCK high to TDMxTD output high impedance | t <sub>DM_OUTHI</sub> | —    | 9.8  | ns   | 7    |

| TDMxTFS/TDMxRFS output valid                 | t <sub>DMFSKHOV</sub> | _    | 9.25 | ns   | 6    |

| TDMxTFS/TDMxRFS output hold time             | t <sub>DMFSKHOX</sub> | 2.0  |      | ns   | 6    |

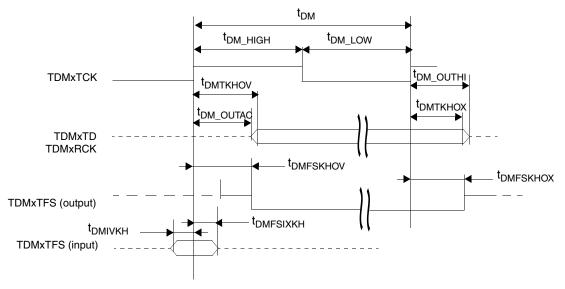

This figure shows the TDM transmit signal timing.

Figure 34. TDM Transmit Signals

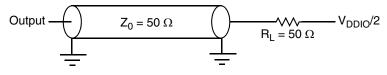

This figure provides the AC test load for the TDM.

Figure 35. TDM AC Test Load

# 2.20 High-Speed Serial Interface (HSSI) DC Electrical Characteristics

The device features an HSSI that includes one 4-channel SerDes port (lanes 0 through 3) used for high-speed serial interface applications (PCI Express, CPRI, and SGMII). This section and its subsections describe the common portion of the SerDes DC, including the DC requirements for the SerDes reference clocks and the SerDes data lane transmitter (Tx) and receiver (Rx) reference circuits. The data lane circuit specifications are specific for each supported interface, and they have individual subsections by protocol. The selection of individual data channel functionality is done via the reset configuration word. Specific AC electrical characteristics are defined in Section 2.20.3, "HSSI AC Timing Specifications."

| Parameter                  | Symbol  | Min | Nom | Max  | Unit | Condition                                                                                                                                                                               |

|----------------------------|---------|-----|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input differential voltage | R_Vdiff | N/A | _   | 1200 | mV   | It is assumed that for the R_Vdiff min<br>specification, that the eye can be<br>closed at the receiver after passing the<br>signal through a CEI/CPRI Level II LR<br>compliant channel. |

| Differential resistance    | R_Rdin  | 80  | —   | 120  | Ω    | —                                                                                                                                                                                       |

Table 73. CPRI Receiver DC Specifications (LV-II: 1.2288, 2.4576, 3.072, 4.9152, and 6.144 Gbps)

Note: LV-II is CEI-6G-LR-based.

#### 2.20.2.4 **DC-Level Requirements for SGMII Configurations**

Table 74 describes the SGMII SerDes transmitter AC-coupled DC electrical characteristics. Specifications are valid at the recommended operating conditions listed in Table 3.

| Parameter                         | Symbo<br>I         | Min        | Nom | Мах        | Unit | Conditions                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------|--------------------|------------|-----|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output<br>differential<br>voltage | IV <sub>OD</sub> I | 0.64 × Nom | 500 | 1.45 × Nom | mV   | <ul> <li>The IV<sub>OD</sub>I value shown in the Typ column is based<br/>on the condition of XV<sub>DD_SRDS2-Typ</sub> = 1.0 V, no<br/>common mode offset variation (V<sub>OS</sub> = 500mV),<br/>SerDes transmitter is terminated with 100-Ω<br/>differential load between SD_TXn and SD_TX_Bn.</li> <li>Amplitude setting:<br/>L[0:3]TECR0[AMD_RED] = 0b000000</li> </ul> |

| Output<br>differential<br>voltage | IV <sub>OD</sub> I | 0.64 × Nom | 459 | 1.45 × Nom | mV   | <ul> <li>The IV<sub>OD</sub>I value shown in the Typ column is based<br/>on the condition of XV<sub>DD_SRDS2-Typ</sub> = 1.0V, no<br/>common mode offset variation (V<sub>OS</sub> = 500mV),<br/>SerDes transmitter is terminated with 100-Ω<br/>differential load between SD_TXn and SD_TX_Bn.</li> <li>Amplitude setting:<br/>L[0:3]TECR0[AMD_RED] = 0b000010</li> </ul>  |

| Output<br>differential<br>voltage | IV <sub>OD</sub> I | 0.64 × Nom | 417 | 1.45 × Nom | mV   | <ul> <li>The IV<sub>OD</sub>I value shown in the Typ column is based<br/>on the condition of XV<sub>DD_SRDS2-Typ</sub> = 1.0V, no<br/>common mode offset variation (V<sub>OS</sub> = 500mV),<br/>SerDes transmitter is terminated with 100-Ω<br/>differential load between SD_TXn and SD_TX_Bn.</li> <li>Amplitude setting:<br/>L[0:3]TECR0[AMD_RED] = 0b000101</li> </ul>  |

| Output<br>differential<br>voltage | IV <sub>OD</sub> I | 0.64 × Nom | 376 | 1.45 × Nom | mV   | <ul> <li>The IV<sub>OD</sub>I value shown in the Typ column is based<br/>on the condition of XV<sub>DD_SRDS2-Typ</sub> = 1.0V, no<br/>common mode offset variation (V<sub>OS</sub> = 500mV),<br/>SerDes transmitter is terminated with 100-Ω<br/>differential load between SD_TXn and SD_TX_Bn.</li> <li>Amplitude setting:<br/>L[0:3]TECR0[AMD_RED] = 0b001000</li> </ul>  |

## Table 74. SGMII DC Transmitter Electrical Characteristics

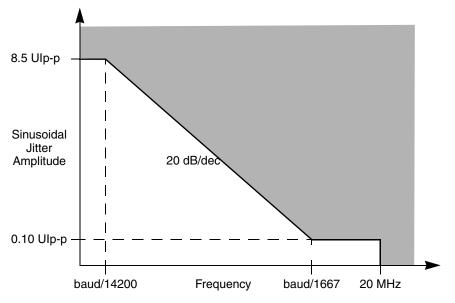

Figure 44. Single Frequency Sinusoidal Jitter Limits for Baud Rate <3.125 Gbps

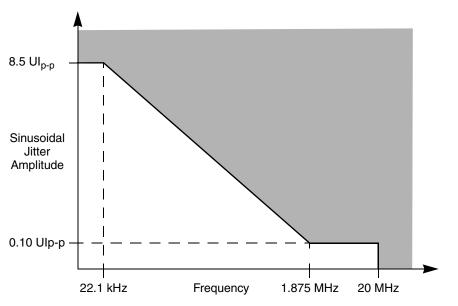

Figure 45. Single Frequency Sinusoidal Jitter Limits for Baud Rate 3.125 Gbps

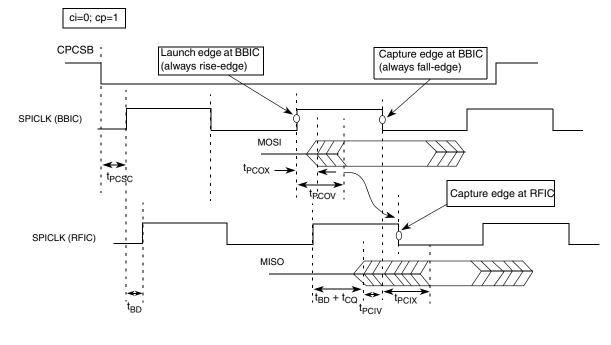

t<sub>BD</sub>: Board delay from the BSC9132 BBIC to the external RFIC or back t<sub>CO</sub>: Delay in RFIC from input of SPICLK to output valid data

Max permissible board skew: 100 ps Proposed frequency of SPICLK: 30 MHz Input data setup requirement: 1 ns Input data hold requirement: 0 ns  $t_{CQ}$ : 4.5 ns–6.5 ns (6.5 ns is critical, which defines the max frequency)

#### Figure 49. RF Parallel Control Plane Interface AC Timing Diagram

# 2.22 Universal Subscriber Identity Module (USIM)

The USIM module interface consist of a total of five pins. Only "Internal One Wire" interface mode is supported. In this mode, the Rx input of the USIM IP is connected to the TX output of the USIM, which is internal to the device. Only one bidirectional signal (Rx/Tx) is routed to the device pin, which is connected to the external SIM card.

The interface is meant to be used with synchronous SIM cards. This means that the SIM module provides a clock for the SIM card to use. The frequency of this clock is normally 372 times the data rate on the Rx/Tx pins; however, the SIM module can work with CLK equal to 16 times the data rate on Rx/Tx pins.

There is no timing relationship between the clock and the data. The clock that the SIM module provides to the SIM card will be used by the SIM card to recover the clock from the data much like a standard UART. All five pins of SIM module are asynchronous to each other.

There are no required timing relationships between the pads in normal mode, The SIM card is initiated by the interface device, whereupon the SIM card will send a response with an Answer to Reset. Although the SIM interface has no specific requirement, the ISO-7816 specifies reset and power down sequences. For detailed information, see ISO-7816.

The USIM interface pins are available at two locations. At one location, it is multiplexed with eSDHC and TDM functionality and is powered by the BVDD power supply (3.3V/2.5V/1.8V). At the other location, it is multiplexed with eSPI and UART functionality and is powered by CVDD power supply (3.3V/1.8V).

#### Hardware Design Considerations

the isolation resistor allows future access to TRST\_B in case a JTAG interface may need to be wired onto the system in future debug situations.

- TCK should be pulled down to GND through a 1 k $\Omega$  resistor. This prevents TCK from changing state and reading incorrect data into the device.

- No connection is required for TDI, TDO, or TMS.

## NOTE

In the case where the DSP JTAG is also used (as described in Table 112), DSP\_TRST and DSP\_TCK need to be handled in the same way as TRST and TCK are, as mentioned above.

# 3.12 Guidelines for High-Speed Interface Termination

If the high-speed SerDes interface is not used at all, the unused pin should be terminated as described in this section. However, the SerDes must always have power applied to its supply pins.

The following pins must be left unconnected (float):

- SD TX[3:0]

- SD TX B[3:0]

The following pins must be connected to GND:

- SD\_RX[3:0], SD\_RX\_B[3:0]

- SD\_REF\_CLK, SD\_REF\_CLK\_B

## 3.13 Thermal

This section describes the thermal specifications.

## 3.13.1 Thermal Characteristics

Table 113 provides the package thermal characteristics.

#### Table 113. Package Thermal Resistance Characteristics

| Characteristic                         | JEDEC Board             | Symbol             | Lid | Unit |

|----------------------------------------|-------------------------|--------------------|-----|------|

| Junction-to-Ambient Natural Convection | Single layer board (1s) | $R_{\thetaJA}$     | 21  | °C/W |

| Junction-to-Ambient Natural Convection | Four layer board (2s2p) | $R_{\thetaJA}$     | 14  | °C/W |

| Junction-to-Ambient (at 200 ft/min)    | Single layer board (1s) | $R_{\thetaJMA}$    | 15  | °C/W |

| Junction-to-Ambient (at 200 ft/min)    | Four layer board (2s2p) | $R_{\thetaJMA}$    | 11  | °C/W |

| Junction-to-Board                      | _                       | $R_{\theta JB}$    | 4.0 | °C/W |

| Junction-to-Case Top                   | _                       | $R_{\theta JCtop}$ | 0.7 | °C/W |

Note:

1. Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

- Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- 3. Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

Package Information

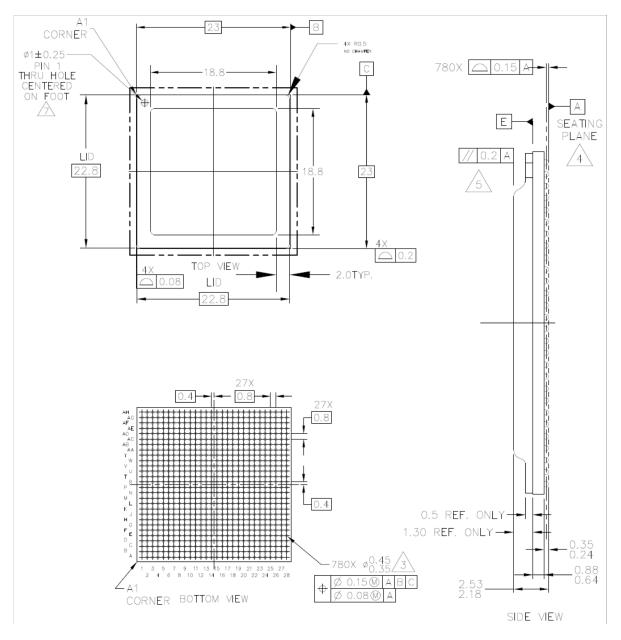

# 4.2 Mechanical Dimensions of the FC-PBGA

Figure 61 shows the package and bottom surface nomenclature.

Notes:

- 1. All dimentions are in milimeters.

- 2. Dimensions and tolerancing per ASME Y14.5-1994.

- 3. Maximum ball diameter measured parallel to Datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 6. All dimensions are symmetric across the package center lines, unless dimensioned otherwise.

- 7. Pin 1 through hole should be centered within foot area.

### Figure 61. BSC9132 Mechanical Dimensions and Package Diagram

**Ordering Information**

# 5 Ordering Information

The table below provides the Freescale part numbering nomenclature for the BSC9132. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. Each part number also contains a revision code which refers to the die mask revision number.

|              | n                  | x                         | t                                                                                      | е                                              | n                                                    | С                                                     | d               | f                                  | r               |

|--------------|--------------------|---------------------------|----------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------|-------------------------------------------------------|-----------------|------------------------------------|-----------------|

| Product Code | Part<br>Identifier | Qual<br>Status            | Temp<br>Range                                                                          | Encryp-<br>tion                                | Package<br>Type                                      | CPU<br>Freq                                           | DDR<br>Speed    | DSP<br>Freq                        | Die<br>Revision |

| BSC          | 9132               | N =<br>Industrial<br>Tier | S, L = Std<br>temp<br>$(0-105^{\circ}C)$<br>X, J = Ext<br>temp<br>$(-40-105^{\circ}C)$ | E = SEC<br>Present<br>N = No<br>SEC<br>Present | 7 =<br>FC-PBGA<br>Pb-free<br>Bumps<br>and<br>Package | K =<br>1000 MHz<br>M =<br>1200 MHz<br>P =<br>1400 MHz | N =<br>1333 MHz | K =<br>1000 MHz<br>M =<br>1200 MHz | B =<br>Rev 1.1  |

### Table 114. Part numbering nomenclature

## 5.1 Part Marking

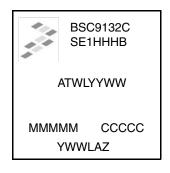

Parts are marked as the example shown in this figure.

FCPBGA

Notes: ATWLYYWW is the traceability code. CCCCC is the country code. MMMMM is the mask number. YWWLAZ is the assembly traceability code. BSC9132CSE1HHHB is the orderable part number. See Table 114 for details.

Figure 62. Part Marking for FCPBGA Device

# 6 Product Documentation

The following documents are required for a complete description of the device and are needed to design properly with the part. Some documents may require a non-disclosure agreement. Contact your local FAE for assistance.

• BSC9132 QorIQ Qonverge Multicore Baseband Processor Reference Manual (BSC9132RM)