# E·XF kenesas Electronics America Inc - <u>UPD78F9212FH-2A2-E1-A Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                               |

|----------------------------|----------------------------------------------------------------------------------------|

| Core Processor             | -                                                                                      |

| Core Size                  | -                                                                                      |

| Speed                      | -                                                                                      |

| Connectivity               | -                                                                                      |

| Peripherals                | -                                                                                      |

| Number of I/O              | -                                                                                      |

| Program Memory Size        | -                                                                                      |

| Program Memory Type        | -                                                                                      |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | -                                                                                      |

| Voltage - Supply (Vcc/Vdd) | -                                                                                      |

| Data Converters            | -                                                                                      |

| Oscillator Type            | -                                                                                      |

| Operating Temperature      | -                                                                                      |

| Mounting Type              | -                                                                                      |

| Package / Case             | -                                                                                      |

| Supplier Device Package    | •                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f9212fh-2a2-e1-a |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **ELIMINARY PRODUCT INFORMATION**

# MOS INTEGRATED CIRCUIT $\mu$ PD78F9210FH, 78F9211FH, 78F9212FH

# 8-BIT SINGLE-CHIP MICROCONTROLLER

The μ78F9210FH, 78F9211FH, and 78F9212FH are products of the 78K0S/KY1+ in the 78K/0S series. These microcontrollers feature Single-voltage and Self-programming Flash memory and peripherals that is suitable for your application.

The functions of these microcontrollers are described in the following user's manuals. Refer to these manuals when designing a system based on any of these microcontrollers.

78K0S/KY1+ User's Manual

: U16994E

78K/0S Series User's Manual, Instruction : U11047E

#### FEATURES

- 78K/0S CPU core, 8-bit CISC architecture

- ROM and RAM capacities

| Item         | Program memory | Data memory      |

|--------------|----------------|------------------|

| Product name | (Flash EEPROM) | (High-speed RAM) |

| μPD78F9210FH | 1 Kbytes       | 128 bytes        |

| μPD78F9211FH | 2 Kbytes       | 128 bytes        |

| μPD78F9212FH | 4 Kbytes       | 128 bytes        |

• Minimum instruction execution time

Minimum instruction execution time selectable from high speed (0.2  $\mu$ s) to low speed (3.2  $\mu$ s) (with CPU clock of 10 MHz)

System clock

High-speed internal oscillator: 8 MHz (TYP.) Ceramic/crystal oscillator: 1 MHz to 10 MHz

WDT clock

Low-speed internal oscillator: 240 kHz (TYP.)

Interrupt

External: 2 sources Internal: 5 sources

• I/O port: 14

CMOS I/O: 13

CMOS Input: 1 • On-chip A/D Converter

10-bit resolution A/D converter: 4 ch (2.7 to 5.5 V)

- Timer/Counter

16-bit Timer: 1 ch

8-bit Timer: 1 ch

- Watchdog Timer: 1 ch

- Operation Voltage: 2.0 V to 5.5 V

- Package: 16-pin WLCSP (1.93 x 2.24 x thickness of 0.4 mm, 0.5 mm pitch)

#### APPLICATION FIELDS

Household electrical appliances, Toys, Mobile device

The information contained in this document is being issued in advance of the production cycle for the product. The parameters for the product may change before final production or NEC Electronics Corporation, at its own discretion, may withdraw the product prior to its production. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

#### **OVERVIEW OF FUNCTIONS**

|                                        | Item                             | μPD78F9210FH                                                                                                                                                                  | μPD78F9211FH                                  | μPD78F9212FH             |  |  |  |

|----------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------|--|--|--|

| Internal memory                        | Flash memory                     | 1 KB                                                                                                                                                                          | 2 KB                                          | 4 KB                     |  |  |  |

|                                        | High-speed RAM <sup>Note 1</sup> | 128 bytes                                                                                                                                                                     |                                               |                          |  |  |  |

| Memory space                           |                                  | 64 KB                                                                                                                                                                         |                                               |                          |  |  |  |

| X1 input clock (oscillation frequency) |                                  | Crystal/ceramic oscillation                                                                                                                                                   | n, external system clock in<br>5.5 V          | put                      |  |  |  |

| Internal oscillation                   | High-speed                       | Internal oscillation: 8 MH                                                                                                                                                    | z (TYP.)                                      |                          |  |  |  |

| clock                                  | Low-speed                        | Internal oscillation: 240 kHz (TYP.)                                                                                                                                          |                                               |                          |  |  |  |

| General-purpose re                     | gisters                          | 8 bits $\times$ 8 registers                                                                                                                                                   |                                               |                          |  |  |  |

| Instruction execution                  | n time                           | 0.2 µs/0.4 µs/0.8 µs/1.6                                                                                                                                                      | <i>u</i> s/3.2 $\mu$ s/ (X1 input clock:      | @ fx = 10 MHz operation) |  |  |  |

| I/O ports                              |                                  | Total:<br>CMOS I/O:<br>CMOS Input                                                                                                                                             | CMOS I/O: 13                                  |                          |  |  |  |

| Timers                                 |                                  | <ul> <li>16-bit timer/event court</li> <li>8-bit timer(Timer H1):</li> <li>Watchdog timer:</li> </ul>                                                                         |                                               |                          |  |  |  |

|                                        | Timer outputs                    | 2 (PWM output: 1)                                                                                                                                                             |                                               |                          |  |  |  |

| A/D converter                          |                                  | 10-bit resolution $\times$ 4 channels                                                                                                                                         |                                               |                          |  |  |  |

| Vectored interrupt                     | External                         | 2                                                                                                                                                                             |                                               |                          |  |  |  |

| sources                                | Internal                         | 5                                                                                                                                                                             |                                               |                          |  |  |  |

| Reset                                  |                                  | <ul> <li>Reset using RESET pin</li> <li>Internal reset by watchdog timer</li> <li>Internal reset by power-on-clear</li> <li>Internal reset by low-voltage detector</li> </ul> |                                               |                          |  |  |  |

| Power supply voltage                   | ge                               | $V_{\text{DD}} = 2.0 \text{ to } 5.5 \text{ V}^{\text{Note}}$                                                                                                                 |                                               |                          |  |  |  |

| Operating ambient                      | temperature                      | $T_A = -40 \text{ to } +85^{\circ}\text{C}$                                                                                                                                   | $T_{A} = -40 \text{ to } +85^{\circ}\text{C}$ |                          |  |  |  |

| Package                                |                                  | 16-pin WLCSP                                                                                                                                                                  | 16-pin WLCSP                                  |                          |  |  |  |

Note Use this product in a voltage range of 2.2 to 5.5 V because the detection voltage (V<sub>POC</sub>) of the power-onclear(POC) circuit is 2.1 V  $\pm$ 0.1 V.

#### 3. PIN FUNCTIONS

#### 3.1 Port Pins

| Pin Name            | I/O   |                                                                                                                                                          | After Reset                                                                                                                   | Alternate-Function<br>Pin |                           |  |

|---------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|--|

| P20                 | I/O   | Port 2.                                                                                                                                                  |                                                                                                                               | Input                     | ANI0/TI000/TOH1           |  |

| P21                 |       | 4-bit I/O port.<br>Can be set to input or output mode in 1-bit units.                                                                                    |                                                                                                                               |                           | ANI1/TI010/<br>TO00/INTP0 |  |

| P22 <sup>Note</sup> |       | software.                                                                                                                                                | tor can be connected by setting                                                                                               |                           | X2/ANI2 <sup>Note</sup>   |  |

| P23 <sup>Note</sup> |       |                                                                                                                                                          |                                                                                                                               |                           | X1/ANI3 <sup>Note</sup>   |  |

| P32                 | I/O   | Port 3                                                                                                                                                   | Can be set to input or output mode in<br>1-bit units.<br>An on-chip pull-up resistor can be<br>connected by setting software. | Input                     | INTP1                     |  |

| P34 <sup>Note</sup> | Input |                                                                                                                                                          | Input only                                                                                                                    | Input                     | RESET                     |  |

| P40 to P47          | I/O   | Port 4.<br>8-bit I/O port.<br>Can be set to input or output mode in 1-bit units.<br>An on-chip pull-up resistor can be connected by setting<br>software. |                                                                                                                               | Input                     | -                         |  |

**Note** For the setting method for pin functions, see **5. OPTION BYTE**.

Caution The P22/X2/ANI2 and P23/X1/ANI3 pins are pulled down during reset.

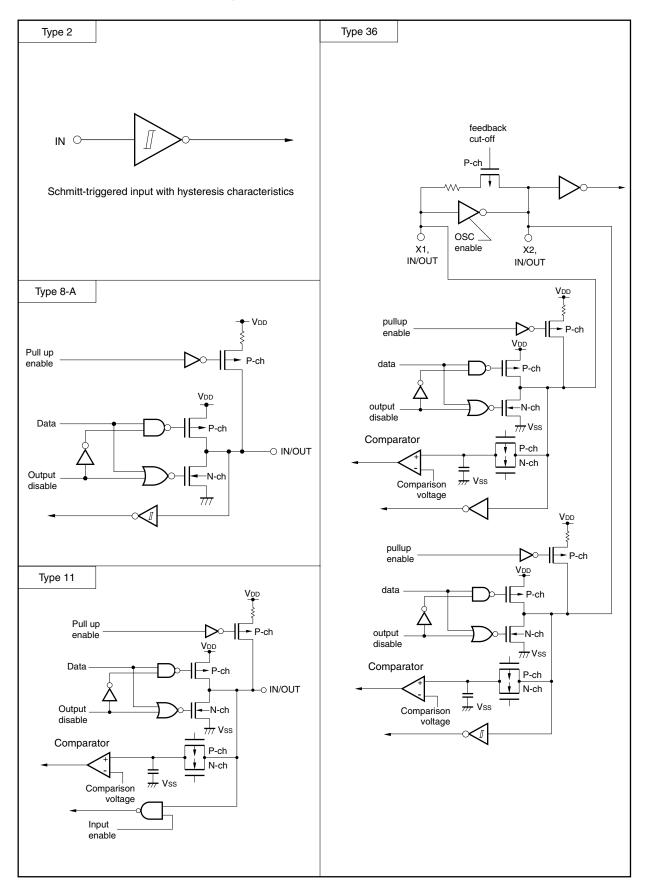

Figure 3-1. Pin Input/Output Circuits

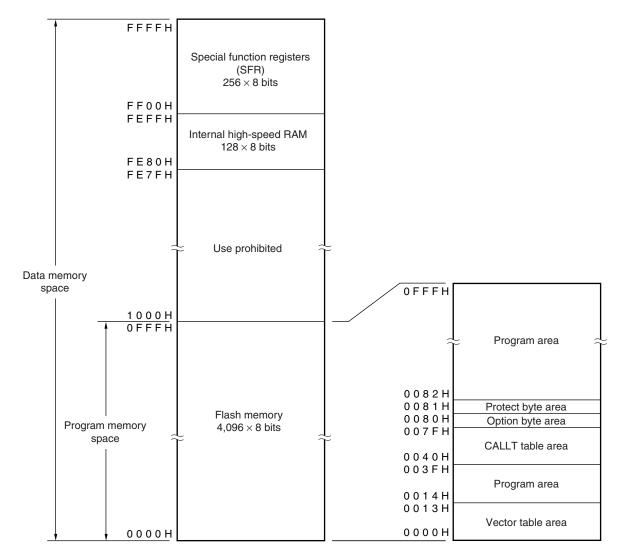

#### 4. MEMORY SPACE

#### 4.1 Memory Space

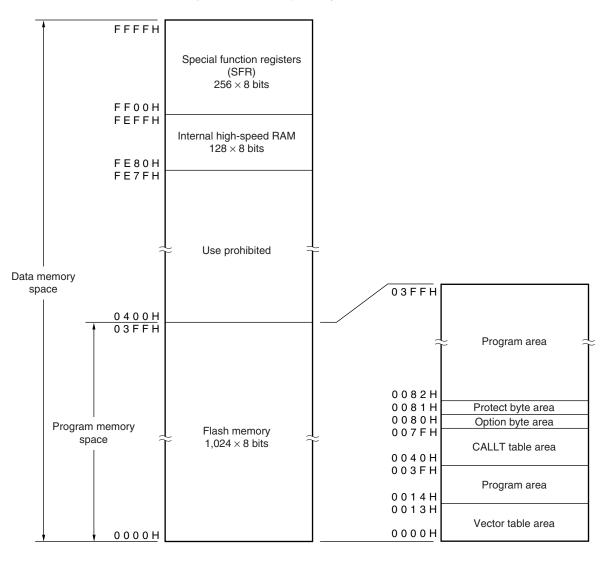

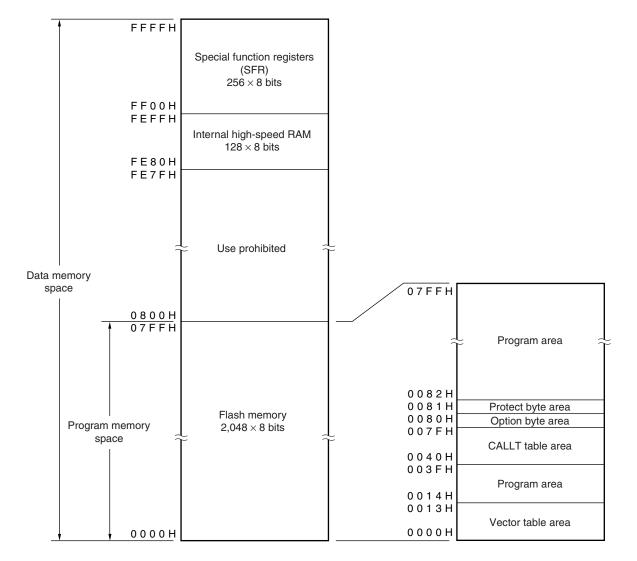

Products in the  $\mu$ PD78F9210FH, 78F9211FH, and 78F9212FH can access up to 64 Kbytes of memory space. Figures 4-1 to 4-3 show the memory maps.

#### Figure 4-1. Memory Map (µPD78F9210FH)

**Remark** The option byte and protect byte are 1 byte each.

Figure 4-2. Memory Map (µPD78F9211FH)

**Remark** The option byte and protect byte are 1 byte each.

#### Figure 4-3. Memory Map (µPD78F9212FH)

**Remark** The option byte and protect byte are 1 byte each.

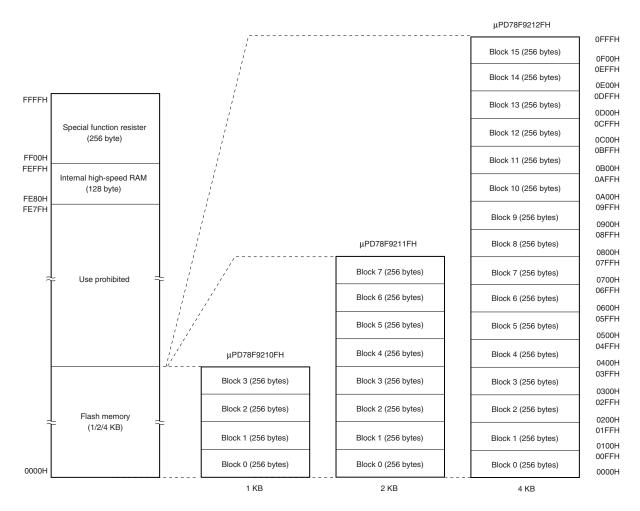

#### 4.2 Memory Configuration

The 1/2/4 KB internal flash memory area is divided into 4/8/16 blocks and can be programmed/erased in block units. All the blocks can also be erased at once, by using a dedicated flash programmer.

#### Figure 4-4. Flash Memory Mapping

#### Figure 5-2. Format of Option Byte (2/2)

| LIOCP | Low-speed internal oscillates                                                         |

|-------|---------------------------------------------------------------------------------------|

| 1     | Cannot be stopped (oscillation does not stop even if 1 is written to the LSRSTOP bit) |

| 0     | Can be stopped by software (oscillation stops when 1 is written to the LSRSTOP bit)   |

Cautions 1. If it is selected that low-speed internal oscillator cannot be stopped, the count clock to the watchdog timer (WDT) is fixed to low-speed internal oscillation clock.

2. If it is selected that low-speed internal oscillator can be stopped by software, supply of the count clock to WDT is stopped in the HALT/STOP mode, regardless of the setting of bit 0 (LSRSTOP) of the low-speed internal oscillation mode register (LSRCM). Similarly, clock supply is also stopped when a clock other than the low-speed internal oscillation clock is selected as a count clock to WDT.

While the low-speed internal oscillator is operating (LSRSTOP = 0), the clock can be supplied to the 8-bit timer H1 even in the STOP mode.

#### **Remarks 1.** (): fx = 10 MHz

2. For the oscillation stabilization time of the resonator, refer to the characteristics of the resonator to be used.

| 3. An example of software c<br>OPB CSEG AT 0080H | oding for setting the option bytes is shown below.                                                                                             |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| DB 10010001B                                     | ; Set to option byte                                                                                                                           |

|                                                  | ; Low-speed internal oscillator cannot be stopped                                                                                              |

|                                                  | ; The system clock is a crystal or ceramic resonator.                                                                                          |

|                                                  | ; The $\overline{\text{RESET}}$ pin is used as an input-only port pin (P34).<br>; Minimum oscillation stabilization time (2 <sup>10</sup> /fx) |

| 4. For details on the timing                     | at which the option byte is referenced, see the chapter of the reset                                                                           |

function 78K0S/KY1+ User's Manual (U16994E)

#### 6. SOURCE CLOCK OF EACH TIMER

- (1) Count clock selection by 16-bit timer/event counter 00 (TM00)

- fxp (10 MHz) fxp/22 (2.5 MHz) fxp/28 (39.06 kHz) T1000 pin valid edge<sup>Note</sup>

Note The external clock requires a pulse longer than two cycles of the internal count clock (fxp).

Remarks 1. fxp: Oscillation frequency of clock supplied to peripheral hardware

**2.** ( ): fxp = 10 MHz

#### (2) Count clock selection by 8-bit timer/event counter H1 (TMH1)

fxp(10 MHz) fxp/22(2.5 MHz) fxp/24(625 kHz) fxp/26(156.25 kHz) fxp/212(2.44 kHz) fRL/27(1.88 kHz (TYP.))

#### Remarks 1. fxp: Oscillation frequency of clock to peripheral hardware

- 2. fr.L: Low-speed internal oscillation clock oscillation frequency

- **3.** Figures in parentheses apply to operation at  $f_{XP} = 10$  MHz,  $f_{RL} = 240$  kHz (TYP.).

#### (3) Overflow time setting by watchdog timer

| Overflow ti                                           | ime setting                            |

|-------------------------------------------------------|----------------------------------------|

| During Low-Speed Internal oscillation Clock Operation | During System Clock Operation          |

| 2 <sup>11</sup> /f <sub>RL</sub> (4.27 ms)            | 2 <sup>13</sup> /fx (819.2 <i>µ</i> s) |

| 2 <sup>12</sup> /f <sub>RL</sub> (8.53 ms)            | 2 <sup>14</sup> /fx (1.64 ms)          |

| 2 <sup>13</sup> /f <sub>RL</sub> (17.07 ms)           | 2 <sup>15</sup> /fx (3.28 ms)          |

| 2 <sup>14</sup> /f <sub>RL</sub> (34.13 ms)           | 2 <sup>16</sup> /fx (6.55 ms)          |

| 2 <sup>15</sup> /f <sub>RL</sub> (68.27 ms)           | 2 <sup>17</sup> /fx (13.11 ms)         |

| 2 <sup>16</sup> /f <sub>RL</sub> (136.53 ms)          | 2 <sup>18</sup> /fx (26.21 ms)         |

| 2 <sup>17</sup> /f <sub>RL</sub> (273.07 ms)          | 2 <sup>19</sup> /fx (52.43 ms)         |

| 2 <sup>18</sup> /f <sub>RL</sub> (546.13 ms)          | 2 <sup>20</sup> /fx (104.86 ms)        |

Remarks 1. fr.: Low-speed internal oscillation clock oscillation frequency

- 2. fx: System clock oscillation frequency

- 3. Figures in parentheses apply to operation at  $f_{RL}$  = 480 kHz (MAX.), fx = 10 MHz.

#### 7. ELECTRICAL SPECIFICATIONS (TARGET VALUES)

Caution These specifications show target values, which may change after device evaluation. The operating voltage range may also change.

| Parameter            | Symbol | Conditions                                 | Ratings                                  | Unit |

|----------------------|--------|--------------------------------------------|------------------------------------------|------|

| Supply voltage       | VDD    |                                            | –0.3 to +6.5                             | V    |

|                      | Vss    |                                            | -0.3 to +0.3                             | V    |

| Input voltage        | Vi     | P20 to P23, P32, P34, P40 to P47           | $-0.3$ to V <sub>DD</sub> + $0.3^{Note}$ | V    |

| Output voltage       | Vo     |                                            | $-0.3$ to VDD + $0.3^{Note}$             | V    |

| Analog input voltage | Van    |                                            | $-0.3$ to VDD + $0.3^{Note}$             | V    |

| Output current, high | Іон    | Per pin                                    | -10.0                                    | mA   |

|                      |        | Total of P20 to P23, P32, P40 to P47       | -44.0                                    | mA   |

| Output current, low  | lo∟    | Per pin                                    | 20.0                                     | mA   |

|                      |        | Total of P20 to P23, P32, P40 to P47       | 44.0                                     | mA   |

| Operating ambient    | TA     | In normal operation mode                   | -40 to +85                               | °C   |

| temperature          |        | During flash memory programming            |                                          | °C   |

| Storage temperature  | Tstg   | Flash memory blank status                  | -65 to +150                              | °C   |

|                      |        | Flash memory programming already performed | -40 to +125                              | °C   |

Absolute Maximum Ratings (TA = 25°C)

Note Must be 6.5 V or lower

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

| Parameter                    | Symbol |                                                               | Conditi  | ons                                                    | MIN.                  | TYP.   | MAX.   | Unit    |

|------------------------------|--------|---------------------------------------------------------------|----------|--------------------------------------------------------|-----------------------|--------|--------|---------|

| Output current, high         | Іон    | Per pin                                                       |          | $2.0~V \leq V_{\text{DD}} \leq 5.5~V$                  |                       |        | -5     | mA      |

|                              |        | Total of all pins                                             |          | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                  |                       |        | -25    | mA      |

|                              |        |                                                               |          | $2.0~V \leq V_{\text{DD}} < 4.0~V$                     |                       |        | -15    | mA      |

| Output current, low          | lo∟    | Per pin                                                       |          | $2.0~V \leq V_{\text{DD}} \leq 5.5~V$                  |                       |        | 10     | mA      |

|                              |        | Total of all pins                                             |          | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                  |                       |        | 30     | mA      |

|                              |        |                                                               |          | $2.0~V \leq V_{\text{DD}} < 4.0~V$                     |                       |        | 15     | mA      |

| Input voltage, high          | VIH1   | P23 in external clo<br>P20 and P21                            | ock mode | e and pins other than                                  | 0.8Vdd                |        | Vdd    | V       |

|                              | VIH2   | P23 in other than external clock mode, P20 and P21            |          |                                                        | 0.7Vdd                |        | Vdd    | V       |

| Input voltage, low           | VIL1   | P23 in external clock mode and pins other than<br>P20 and P21 |          | 0                                                      |                       | 0.2Vdd | V      |         |

|                              | VIL2   | P23 in other than external clock mode, P20 and P21            |          |                                                        | 0                     |        | 0.3Vdd | V       |

| Output voltage, high         | Vон    | Total of output pin<br>Іон = –15 mA                           | S        | 4.0 V ≤ V <sub>DD</sub> ≤ 5.5 V<br>Іон = –5 mA         | Vdd - 1.0             |        |        | V       |

|                              |        |                                                               |          | 10H = -5  IIIA<br>2.0 V $\leq$ VDD < 4.0 V             | V <sub>DD</sub> – 0.5 |        |        | V       |

| Output voltage, low          | Vol    | Iон = $-100 \mu A$                                            | •        | $2.0 V \le V DD < 4.0 V$<br>$4.0 V \le V DD \le 5.5 V$ | VDD-0.5               |        | 1.3    | v       |

| Output voltage, low          | VOL    | Total of output pins<br>lo∟ = 30 mA                           |          | 4.0 v ≤ vbb ≤ 5.5 v<br>lo∟ = 10 mA                     |                       |        | 1.5    | v       |

|                              |        | 10L = 30  MA $10L = 10  MA2.0 V \leq VDD < 4.0 V$             |          |                                                        |                       | 0.4    | V      |         |

|                              |        | $I_{OL} = 400 \ \mu A$                                        | •        |                                                        |                       |        | 0.4    | v       |

| Input leakage current, high  | Іцн    | $V_{I} = V_{DD}$                                              | Pins ot  | her than X1                                            |                       |        | 3      | μA      |

| Input leakage current, low   | Ilil   | Vi = 0 V                                                      |          | her than X1                                            |                       |        | -3     | μA      |

| Output leakage current, high | Ігон   | Vo = VDD                                                      |          |                                                        |                       |        | 3      | ,<br>μA |

| Output leakage current, low  | Ilol   | $V_0 = 0 V$ Pins other than X2                                |          |                                                        |                       | -3     | μA     |         |

| Pull-up resistance value     | Rpu    | V1 = 0 V                                                      |          |                                                        | 10                    | 30     | 100    | kΩ      |

| Pull-down resistance value   | RPD    | P22, P23, reset st                                            | atus     |                                                        | 10                    | 30     | 100    | kΩ      |

#### DC Characteristics (T<sub>A</sub> = -40 to $+85^{\circ}$ C, V<sub>DD</sub> = 2.0 to 5.5 V<sup>Note</sup>, V<sub>SS</sub> = 0 V) (1/2)

Note Use this product in a voltage range of 2.2 to 5.5 V because the detection voltage (VPOC) of the power-on clear (POC) circuit is 2.1 V ±0.1 V.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

| Parameter                 | Symbol Conditions                 |                                                             |                                                          |                                                  |     | TYP. | MAX. | Unit |

|---------------------------|-----------------------------------|-------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------|-----|------|------|------|

| Supply                    | DD1 Note 3                        | Crystal/ceramic                                             | fx = 10 MHz                                              | When A/D converter is stopped                    |     | 6.1  | 12.2 | mA   |

| current <sup>Note 2</sup> |                                   | oscillation,                                                | $V_{\text{DD}}=5.0~V\pm10\%^{\text{Note 4}}$             | When A/D converter is operating                  |     | 7.6  | 15.2 |      |

|                           |                                   | external clock<br>input oscillation                         | fx = 6 MHz                                               | When A/D converter is stopped                    |     | 5.5  | 11.0 | mA   |

|                           |                                   | operating                                                   | $V_{\text{DD}} = 5.0 \text{ V} \pm 10\%^{\text{Note 4}}$ | When A/D converter is operating                  |     |      | 14.0 |      |

|                           |                                   | mode <sup>Note 6</sup>                                      | fx = 5 MHz                                               | When A/D converter is stopped                    |     | 3.0  | 6.0  | mA   |

|                           |                                   |                                                             | $V_{\text{DD}} = 3.0 \ V \pm 10\%^{\text{Note 5}}$       | When A/D converter is operating                  |     | 4.5  | 9.0  |      |

|                           | DD2                               | Crystal/ceramic                                             | fx = 10 MHz                                              | When peripheral functions are stopped            |     | 1.7  | 3.8  | mA   |

|                           | external clock                    | $V_{DD} = 5.0 \text{ V} \pm 10\%^{Note 4}$                  | When peripheral functions are operating                  |                                                  |     | 6.7  |      |      |

|                           |                                   | input HALT                                                  | -                                                        | When peripheral functions are stopped            |     | 1.3  | 3.0  | mA   |

|                           | mode <sup>Note 6</sup>            | $V_{DD} = 5.0 \text{ V} \pm 10\%^{Note 4}$                  | When peripheral functions are operating                  |                                                  |     | 6.0  |      |      |

|                           |                                   |                                                             | fx = 5 MHz                                               | When peripheral functions are stopped            |     | 0.48 | 1    | mA   |

|                           |                                   | $V_{\text{DD}}=3.0~V\pm10\%^{\text{Note 5}}$                | When peripheral functions are operating                  |                                                  |     | 2.1  |      |      |

|                           | IDD3 <sup>Note 3</sup> High-speed |                                                             | When A/D converter is stopped                            |                                                  | 5.0 | 10.0 | mA   |      |

|                           |                                   | internal oscillation<br>operating<br>mode <sup>Note 7</sup> | $V_{\text{DD}} = 5.0 \text{ V} \pm 10\%^{\text{Note 4}}$ | When A/D converter is operating                  |     | 6.5  | 13.0 |      |

|                           | IDD4                              | High-speed                                                  | fx = 8 MHz                                               | When peripheral functions are stopped            |     | 1.4  | 3.2  | mA   |

|                           |                                   | internal oscillation<br>HALT mode <sup>Note 7</sup>         | $V_{DD} = 5.0 \text{ V} \pm 10\%^{Note 4}$               | When peripheral functions are operating          |     |      | 5.9  |      |

| IDD5                      | STOP mode                         | $V_{DD} = 5.0 \text{ V} \pm 10\%$                           | When low-speed internal oscillation is stopped           |                                                  | 3.5 | 35.5 | μA   |      |

|                           |                                   |                                                             |                                                          | When low-speed internal oscillation is operating |     | 17.5 | 63.5 |      |

|                           |                                   |                                                             | $V_{DD} = 3.0 \text{ V} \pm 10\%$                        | When low-speed internal oscillation is stopped   |     | 3.5  | 15.5 | μA   |

|                           |                                   |                                                             |                                                          | When low-speed internal oscillation is operating |     | 11.0 | 30.5 |      |

| DC Characteristics (TA = - | -40 to +85°C, VDD = 2.0 to 5.5 | $5 V^{Note 1}, V_{SS} = 0 V) (2/2)$ |

|----------------------------|--------------------------------|-------------------------------------|

|----------------------------|--------------------------------|-------------------------------------|

**Notes 1.** Use this product in a voltage range of 2.2 to 5.5 V because the detection voltage (VPoc) of the power-on clear (POC) circuit is 2.1 V ±0.1 V.

- 2. Total current flowing through the internal power supply (VDD). However, the current that flows through the pull-up resistors of ports is not included.

- 3. IDD1 and IDD3 includ peripheral operation current.

- 4. When the processor clock control register (PCC) is set to 00H.

- 5. When the processor clock control register (PCC) is set to 02H.

- 6. When crystal/ceramic oscillation clock, external clock input is selected as the system clock source using the option byte.

- 7. When high-speed internal oscillation clock is selected as the system clock source using the option byte.

#### **AC Characteristics**

#### Basic operation (TA = -40 to +85°C, VDD = 2.0 to 5.5 V<sup>Note 1</sup>, VSS = 0 V)

| Parameter                                           | Symbol                                | Conditior                                                 | าร                                    | MIN.                             | TYP. | MAX. | Unit |

|-----------------------------------------------------|---------------------------------------|-----------------------------------------------------------|---------------------------------------|----------------------------------|------|------|------|

| Cycle time (minimum                                 | Тсү                                   | Crystal/ceramic oscillation                               | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ | 0.2                              |      | 16   | μs   |

| instruction execution time)                         |                                       | clock, external clock input                               | $3.0~V \leq V_{\text{DD}} < 4.0~V$    | 0.33                             |      | 16   | μs   |

|                                                     |                                       |                                                           | $2.7~V \leq V_{\text{DD}} < 3.0~V$    | 0.4                              |      | 16   | μs   |

|                                                     |                                       |                                                           | $2.0~V \leq V_{\text{DD}} < 2.7~V$    | 1                                |      | 16   | μs   |

|                                                     | High-speed internal oscillation clock | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     | 0.23                                  |                                  | 4.22 | μs   |      |

|                                                     |                                       | $2.7~V \leq V_{\text{DD}} < 4.0~V$                        | 0.47                                  |                                  | 4.22 | μs   |      |

|                                                     |                                       |                                                           | $2.0~V \leq V_{\text{DD}} < 2.7~V$    | 0.95                             |      | 4.22 | μs   |

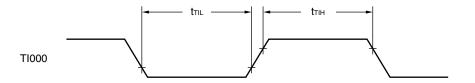

| TI000/TI010 input high-level width, low-level width | tт⊮,<br>tт⊾                           | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$                     |                                       | 2/fsam+<br>0.1 <sup>Note 2</sup> |      |      | μs   |

|                                                     |                                       | $2.0 \text{ V} \leq \text{V}_{\text{DD}} < 4.0 \text{ V}$ |                                       | 2/fsam+<br>0.2 <sup>Note 2</sup> |      |      | μs   |

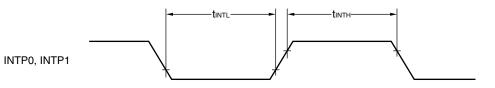

| Interrupt input high-level                          | tinth,                                |                                                           |                                       | 1                                |      |      | μs   |

| width, low-level width                              | <b>t</b> INTL                         |                                                           |                                       |                                  |      |      |      |

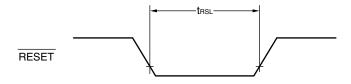

| RESET input low-level width                         | tRSL                                  |                                                           |                                       | 2                                |      |      | μs   |

**Notes 1.** Use this product in a voltage range of 2.2 to 5.5 V because the detection voltage (VPOC) of the power-on clear (POC) circuit is 2.1 V ±0.1 V.

2. Selection of fsam = fxp, fxp/4, or fxp/256 is possible using bits 0 and 1 (PRM000, PRM001) of prescaler mode register 00 (PRM00). Note that when selecting the TI000/TI010 valid edge as the count clock, fsam = fxp.

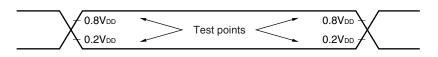

#### AC Timing Test Points (Excluding X1 Input)

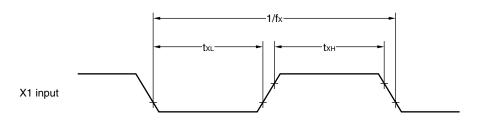

#### **Clock Timing**

#### TI000 Timing

#### Interrupt Input Timing

### RESET Input Timing

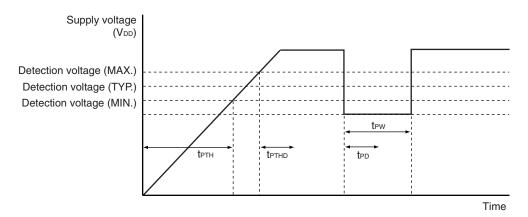

| <b>POC Circuit Characteristics</b> | (T <sub>A</sub> = -40 to +85°C) |

|------------------------------------|---------------------------------|

|------------------------------------|---------------------------------|

| Parameter                               | Symbol      | Conditions                                                       | MIN. | TYP. | MAX. | Unit |

|-----------------------------------------|-------------|------------------------------------------------------------------|------|------|------|------|

| Detection voltage                       | VPOC        |                                                                  | 2.0  | 2.1  | 2.2  | V    |

| Power supply rise time                  | tртн        | VDD: 0 V $\rightarrow$ 2.1 V                                     | 1.5  |      |      | μs   |

| Response delay time 1 <sup>Note 1</sup> | tртно       | When power supply rises, after reaching detection voltage (MAX.) |      |      | 3.0  | ms   |

| Response delay time 2 <sup>Note 2</sup> | <b>t</b> PD | When power supply falls                                          |      |      | 1.0  | ms   |

| Minimum pulse width                     | tew         |                                                                  | 0.2  |      |      | ms   |

Notes 1. Time required from voltage detection to internal reset release.

2. Time required from voltage detection to internal reset signal generation.

#### **POC Circuit Timing**

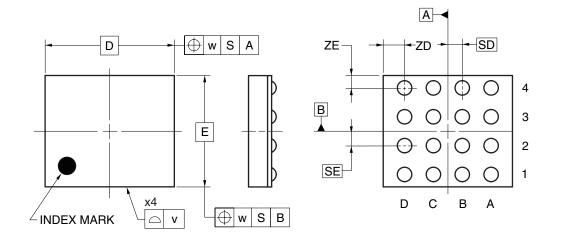

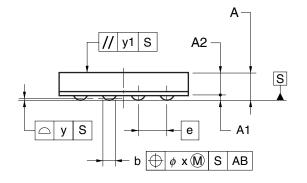

8. PACKAGE DRAWING (PRELIMINARY)

## 16-PIN FBGA (WAFER LEVEL CSP) (1.93x2.24)

|      | (UNIT:mm)    |

|------|--------------|

| ITEM | DIMENSIONS   |

| D    | 2.24         |

| E    | 1.93         |

| v    | 0.15         |

| w    | 0.20         |

| Α    | 0.48±0.04    |

| A1   | 0.08±0.02    |

| A2   | 0.40         |

| е    | 0.50         |

| SD   | 0.25         |

| SE   | 0.25         |

| b    | 0.25±0.05    |

| х    | 0.05         |

| У    | 0.08         |

| y1   | 0.20         |

| ZD   | 0.37         |

| ZE   | 0.215        |

|      | P16FH-50-2A2 |

© NEC Electronics Corporation 2005

#### APPENDIX A. RELATED DOCUMENTS

The related document indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

#### **Documents Related to Devices**

| Document Name                                                           | Document No. |

|-------------------------------------------------------------------------|--------------|

| $\mu$ PD78F9210FH, 78F9211FH, 78F9212FH Preliminary Product Information | This manual  |

| 78K0S/KY1+ User's Manual                                                | U16994E      |

| 78K/0S Series Instructions User's Manual                                | U12326E      |

#### Documents Related to Development Tools (Software) (User's Manuals)

| Document Name                            |                                                     | Document No. |

|------------------------------------------|-----------------------------------------------------|--------------|

| RA78K0S Ver. 1.50 Assembler Package      | Operation                                           | U17391E      |

|                                          | Language                                            | U17390E      |

|                                          | Structured Assembly Language                        | U17389E      |

| CC78K0S Ver. 1.60 C Compiler             | Operation                                           | U17416E      |

|                                          | Language                                            | U17415E      |

| SM+ System Simulator                     | Operation                                           | U17246E      |

|                                          | External Part User Open Interface<br>Specifications | U17247E      |

| ID78K0S-QB Ver. 2.81 Integrated Debugger | Operation                                           | U17287E      |

| PM+ Ver. 5.20                            |                                                     | U16934E      |

#### Documents Related to Development Tools (Hardware) (User's Manuals)

| Document Name                     | Document No. |  |

|-----------------------------------|--------------|--|

| IE-78K0S-NS In-Circuit Emulator   | U13549E      |  |

| IE-78K0S-NS-A In-Circuit Emulator | U15207E      |  |

| QB-78K0SKX1H In-Circuit Emulator  | U17272E      |  |

#### **Documents Related to Flash Memory Programming**

| Document Name                                 | Document No. |  |

|-----------------------------------------------|--------------|--|

| PG-FP4 Flash Memory Programmer User's Manual  | U15260E      |  |

| PG-FPL2 Flash Memory Programmer User's Manual | U17307E      |  |

# Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

#### NOTES FOR CMOS DEVICES -

#### **1** VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

#### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### **③** PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### **④** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### **5** POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### **(6)** INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

# NEC

For further information, please contact:

#### **NEC Electronics Corporation**

1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan Tel: 044-435-5111 http://www.necel.com/

#### [America]

NEC Electronics America, Inc. 2880 Scott Blvd.

Santa Clara, CA 95050-2554, U.S.A. Tel: 408-588-6000 800-366-9782 http://www.am.necel.com/

#### [Europe]

#### NEC Electronics (Europe) GmbH

Arcadiastrasse 10 40472 Düsseldorf, Germany Tel: 0211-65030 http://www.eu.necel.com/

## Hanover Office

Podbielskistrasse 164 30177 Hannover Tel: 0 511 33 40 2-0

#### **Munich Office**

Werner-Eckert-Strasse 9 81829 München Tel: 0 89 92 10 03-0

#### Stuttgart Office

Industriestrasse 3 70565 Stuttgart Tel: 0 711 99 01 0-0

#### United Kingdom Branch

Cygnus House, Sunrise Parkway Linford Wood, Milton Keynes MK14 6NP, U.K. Tel: 01908-691-133

#### Succursale Française

9, rue Paul Dautier, B.P. 52180 78142 Velizy-Villacoublay Cédex France Tel: 01-3067-5800

#### Sucursal en España

Juan Esplandiu, 15 28007 Madrid, Spain Tel: 091-504-2787

#### Tyskland Filial

Täby Centrum Entrance S (7th floor) 18322 Täby, Sweden Tel: 08 638 72 00

#### Filiale Italiana

Via Fabio Filzi, 25/A 20124 Milano, Italy Tel: 02-667541

#### **Branch The Netherlands**

Limburglaan 5 5616 HR Eindhoven The Netherlands Tel: 040 265 40 10

#### [Asia & Oceania]

NEC Electronics (China) Co., Ltd

7th Floor, Quantum Plaza, No. 27 ZhiChunLu Haidian District, Beijing 100083, P.R.China TEL: 010-8235-1155 http://www.cn.necel.com/

#### NEC Electronics Shanghai Ltd.

Room 2509-2510, Bank of China Tower, 200 Yincheng Road Central, Pudong New Area, Shanghai P.R. China P.C:200120 Tel: 021-5888-5400 http://www.cn.necel.com/

#### NEC Electronics Hong Kong Ltd.

12/F., Cityplaza 4, 12 Taikoo Wan Road, Hong Kong Tel: 2886-9318 http://www.hk.necel.com/

#### Seoul Branch

11F., Samik Lavied'or Bldg., 720-2, Yeoksam-Dong, Kangnam-Ku, Seoul, 135-080, Korea Tel: 02-558-3737

#### NEC Electronics Taiwan Ltd.

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R. O. C. Tel: 02-2719-2377

#### NEC Electronics Singapore Pte. Ltd.

238A Thomson Road, #12-08 Novena Square, Singapore 307684 Tel: 6253-8311 http://www.sg.necel.com/

G05.11-1A