# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 454MHz                                                                |

| Co-Processors/DSP               | Data; DCP                                                             |

| RAM Controllers                 | LVDDR, LVDDR2, DDR2                                                   |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | Keypad, LCD, Touchscreen                                              |

| Ethernet                        | 10/100Mbps (1)                                                        |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 + PHY (2)                                                     |

| Voltage - I/O                   | 1.8V, 3.3V                                                            |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                     |

| Security Features               | Boot Security, Cryptography, Hardware ID                              |

| Package / Case                  | 289-LFBGA                                                             |

| Supplier Device Package         | 289-MAPBGA (14x14)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx285avm4b |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

| Dia 1               | -                                   | _                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|-------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block<br>Mnemonic   | Block Name                          | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LCDIF               | LCD Interface                       | Multimedia<br>peripherals     | The LCDIF provides display data for external LCD panels from simple<br>text-only displays to WVGA, 16/18/24 bpp color TFT panels. The LCDIF<br>supports all of these different interfaces by providing fully programmable<br>functionality and sharing register space, FIFOs, and ALU resources at the<br>same time. The LCDIF supports RGB (DOTCLK) modes as well as system<br>mode including both VSYNC and WSYNC modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LRADC               | Low resolution<br>ADC module        | Connectivity<br>peripherals   | The sixteen-channel 12-bit low-resolution ADC (LRADC) block is used for voltage measurement. Channels 0 – 6 measure the voltage on the seven application-dependent LRADC pins. The auxiliary channels can be used for a variety of uses, including a resistor-divider-based wired remote control, external temperature sensing, touch-screen, and other measurement functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OCOTP<br>Controller | On-chip OTP<br>controller           | Security                      | The on-chip one-time-programmable (OCOTP) ROM serves the functions of hardware and software capability bits, Freescale operations and unique-ID, the customer-programmable cryptography key, and storage of various ROM configuration bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PINCTRL             | Pin control<br>and GPIO             | System control peripherals    | Used for general purpose input/output to external ICs. Each GPIO bank supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PMU                 | Power<br>management<br>Unit (DC-DC) | Power<br>management<br>system | <ul> <li>The i.MX28 integrates a comprehensive power supply subsystem, including the following features:</li> <li>One integrated DC-DC converter that supports Li-Ion battery.</li> <li>Four linear regulators directly power the supply rails from 5-V.</li> <li>Linear battery charger for Li-Ion cells.</li> <li>Battery voltage and brownout detection monitoring for VDDD, VDDA, VDDIO, VDD4P2 and 5-V supplies.</li> <li>Integrated current limiter from 5-V power source.</li> <li>Reset controller.</li> <li>System monitors for temperature and speed.</li> <li>Generates USB-Host 5-V from Li-Ion battery (using PWM).</li> <li>Support for on-the-fly transitioning between 5-V and battery power.</li> <li>VDD4P2, a nominal 4.2-V supply, is available when the i.MX28 is connected to a 5-V source and allows the DCDC to run from a 5-V source with a depleted battery.</li> <li>The 4.2-V regulated output also allows for programmable current limits: –Battery Charge current (which ultimately provides current to the on-chip and off-chip loads) as the priority and battery charge current is automatically reduced if the 5-V current limit is reached</li> </ul> |

| PWM(8)              | Pulse width<br>modulation           | Connectivity<br>peripherals   | There are eight PWM output controllers that can be used in place of GPIO pins. Applications include HSADC driving signals and LED & backlight brightness control. Independent output control of each phase allows 0, 1, or high-impedance to be independently selected for the active and inactive phases. Individual outputs can be run in lock step with guaranteed non-overlapping portions for differential drive applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| РХР                 | Pixel Pipeline                      | Multimedia                    | The pixel pipeline (PXP) is used to perform alpha blending of graphic or video buffers with graphics data before sending to an LCD display. The PXP also supports image rotation for hand-held devices that require both portrait and landscape image support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Table 4. i.MX28 Digital and Analog | g Modules (continued) |

|------------------------------------|-----------------------|

|------------------------------------|-----------------------|

| NO |  |

|----|--|

|    |  |

|    |  |

| Table 4. i.MX28 Digital and Ana | alog Modules (continued) |

|---------------------------------|--------------------------|

|---------------------------------|--------------------------|

| Block<br>Mnemonic | Block Name                             | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|----------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTC               | Real-time<br>clock, alarm,<br>watchdog | Clocks                      | The real-time clock (RTC) and alarm share a one-second pulse time domain.<br>The watchdog reset and millisecond counter run on a one-millisecond time<br>domain. The RTC, alarm, and persistent bits reside in a special power<br>domain (crystal domain) that remains powered up even when the rest of the<br>chip is in its powered-down state.                                                                                                                                                                                                                                                                                                                                          |

| SAIF(2)           | Serial audio<br>interface              | Connectivity<br>peripherals | SAIF provides a half-duplex serial port for communication with a variety of serial devices, including industry-standard codecs and DSPs. It supports a continuous range of sample rates from 8 kHz–192 kHz using a high-resolution fractional divider driven by the PLL. Samples are transferred to/from the FIFO through the APBX DMA interface, a FIFO service interrupt, or software polling.                                                                                                                                                                                                                                                                                           |

| SPDIF             | SPDIF                                  | Connectivity peripherals    | The Sony-Philips Digital Interface Format (SPDIF) transmitter module transmits data according to the SPDIF digital audio interface standard (IEC-60958).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SSP(4)            | Synchronous<br>serial port             | Connectivity<br>peripherals | The synchronous serial port is a flexible interface for inter-IC and removable media control and communication. The SSP supports master operation of SPI, Texas Instruments SSI; 1-bit, 4-bit, and 8-bit SD/SDIO/MMC and 1-bit and 4-bit MS modes.<br>The SPI mode has enhancements to support 1-bit legacy MMC cards. SPI master dual (2-bit) and quad (4-bit) mode reads are also supported. The SSP also supports slave operation for the SPI and SSI modes. The SSP has a dedicated DMA channel in the bridge and can also be controlled directly by the CPU through PIO registers. Each of the four SSP modules is independent of the other and can have separate SSPCLK frequencies. |

| TIMROT            | Timers and<br>Rotary<br>Decoder        | Timer<br>peripherals        | This module implements four timers and a rotary decoder. The timers and decoder can take their inputs from any of the pins defined for PWM, rotary encoders, or certain divisions from the 32-kHz clock input. Thus, the PWM pins can be inputs or outputs, depending on the application.                                                                                                                                                                                                                                                                                                                                                                                                  |

| USBOTG<br>USBHOST | High-speed<br>USB<br>on-the-go         | Connectivity<br>peripherals | The USB module provides high-performance USB On-The-Go (OTG) and<br>host functionality (up to 480 Mbps), compliant with the USB 2.0 specification<br>and the OTG supplement. The module has DMA capabilities for handling<br>data transfer between internal buffers and system memory.<br>When the OTG controller works in device mode, it can only work in FS or HS<br>mode. Two USB2.0 PHYs are also integrated (one for the OTG port, another<br>for the host port.)                                                                                                                                                                                                                    |

| USBPHY            | Integrated<br>USB PHY                  | Connectivity<br>peripherals | The integrated USB 2.0 PHY macrocells are capable of connecting to USB host/device systems at the USB low-speed (LS) rate of 1.5 Mbps, full-speed (FS) rate of 12 Mbps or at the USB 2.0 high-speed (HS) rate of 480 Mbps. The integrated PHYs provide a standard UTM interface. The USB_DP and USB_DN pins connect directly to a USB connector.                                                                                                                                                                                                                                                                                                                                           |

- Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- Table 6 gives stress ratings only—functional operation of the device is not implied beyond the conditions indicated in Table 8.

| Parameter                                                                            | Symbol                    | Min. | Max.      | Unit |

|--------------------------------------------------------------------------------------|---------------------------|------|-----------|------|

| Battery Pin                                                                          | BATT, V <sub>DD4P2V</sub> | -0.3 | 4.242     | V    |

| 5-Volt Source Pin - transient, t<30ms, duty cycle <0.05%                             | V <sub>DD5V</sub>         | -0.3 | 7.00      | V    |

| 5 Volt Source Pin - static                                                           | V <sub>DD5V</sub>         | -0.3 | 6.00      | V    |

| Analog Supply Voltage                                                                | V <sub>DDA</sub>          | -0.3 | 2.10      | V    |

| Digital Core Supply Voltage                                                          | V <sub>DDD</sub>          | -0.3 | 1.575     | V    |

| Non-EMI Digital I/O Supply                                                           | V <sub>DDIO</sub>         | -0.3 | 3.63      | V    |

| EMI Digital I/O Supply                                                               | V <sub>DDIO.EMI</sub>     | -0.3 | 3.63      | V    |

| DC-DC Converter <sup>1</sup>                                                         | DCDC_BATT                 | -0.3 | BATT      | V    |

| Input Voltage on Any Digital I/O Pin Relative to Ground                              | —                         | -0.3 | VDDIO+0.3 | V    |

| Input Voltage on USB_DP and USB_DN Pins Relative to Ground <sup>2</sup>              | —                         | -0.3 | 3.63      | V    |

| Analog I/O absolute maximum ratings (exceptions: XTALI, XTALO, RTC_XTALI, RTC_XTALO) | —                         | -0.3 | VDDIO+0.3 | V    |

| Storage Temperature                                                                  | —                         | -40  | 125       | °C   |

#### Table 6. DC Absolute Maximum Ratings

<sup>1</sup> Application should include a Schottky diode between BATT and VDD4P2.

<sup>2</sup> USB\_DN and USB\_DP can tolerate 5V for up to 24 hours. Note that while 5V is applied to USB\_DN or USB\_DP, LRADC readings can be corrupted.

Table 7 shows the electrostatic discharge immunity.

#### Table 7. Electrostatic Discharge Immunity

| 289-Pin BGA Package                    | Tested Level |

|----------------------------------------|--------------|

| Human Body Model (HBM) <sup>1</sup>    | 2 kV         |

| Charge Device Model (CDM) <sup>1</sup> | 500 V        |

<sup>1</sup> HBM and CDM pass ESD testing per AEC-Q100.

## 3.1.2 DC Operating Conditions

Table 8 provides the DC recommended operating conditions.

**Table 8. Recommended Power Supply Operating Conditions**

| Parameter                                                                            | Symbol                                                                | Min               | Тур        | Мах          | Unit |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------|------------|--------------|------|

| Analog Core Supply Voltage                                                           | V <sub>DDA</sub>                                                      | 1.62              | _          | 2.10         | V    |

| Digital Core Supply Voltage<br>Specification dependent on frequency. <sup>1, 2</sup> | V <sub>DDD</sub>                                                      | 1.35              | —          | 1.55         | V    |

| Digital Supply Voltages:<br>• VDDIO33/VDDIO33_EMI<br>• VDDIO18                       | V <sub>DDIO33</sub> /V <sub>DDIO33_EMI</sub> /V <sub>DDI</sub><br>O18 | 3.0<br>1.7        | _          | 3.6<br>1.9   | V    |

| EMI Digital I/O Supply Voltage:<br>• DDR2/mDDR<br>• LVDDR2                           | V <sub>DDIO.EMI</sub> /V <sub>DDIO_EMIQ</sub>                         | 1.7<br>1.425      | 1.8<br>1.5 | 1.9<br>1.625 | V    |

| Battery / DCDC Input Voltage—BATT, DCDC_BATT                                         | BATT<br>DCDC_BATT                                                     | 3.10 <sup>3</sup> |            | 4.242        | V    |

| VDD5V Supply Voltage                                                                 | —                                                                     | 4.75              | 5.00       | 5.25         | V    |

| Offstate Current: <sup>4</sup>                                                       |                                                                       |                   |            |              |      |

| • 32-kHz RTC off, BATT = 4.2 V                                                       | _                                                                     | —                 | 21         | 47           | μA   |

| • 32-kHz RTC on, BATT = 4.2 V                                                        | —                                                                     | —                 | 23         | 51           | μA   |

<sup>1</sup> For optimum USB jitter performance,  $V_{DDD} = 1.35$  V or greater.

$^2$  V<sub>DDD</sub> supply minimum voltage includes 75 mV guardband.

<sup>3</sup> Tested with only the i.MX28 processor loading the MX28 PMU output rails during start up. With external loadings (for example, one DDR2 device and SD Card/NAND Flash), MX28 PMU was tested at BATT/DCDC\_BATT > 3.30 V.

<sup>4</sup> When the real-time clock is enabled, the chip consumes additional current in the OFF state to keep the crystal oscillator and the real-time clock running.

### Table 9 provides the DC operating temperature conditions.

#### **Table 9. Operating Temperature Conditions**

| Parameter <sup>1, 2, 3</sup>                              | Symbol         | Min | Тур | Max | Unit |

|-----------------------------------------------------------|----------------|-----|-----|-----|------|

| Automotive/Industrial Ambient Operating Temperature Range | T <sub>A</sub> | -40 | _   | 85  | °C   |

| Automotive/Industrial Junction Temperature Range          | TJ             | -40 | _   | 105 | °C   |

In most portable systems designs, battery and display specifications limits the operating range to well within these specifications. Most battery manufacturers recommend enabling battery charge only when the ambient temperature is between 0°C and 40°C. To ensure that battery charging does not occur outside the recommended temperature range, the system ambient temperature may be monitored by connecting a thermistor to the LRADC0 or LRADC6 pin on the i.MX28.

<sup>2</sup> For applications powered by external 5V only, the Maximum Ambient Operating Temperature specified in Table 9 may not be achieved. Application developers need to do the worst-case power consumption estimation, and then calculate the Total On-chip Power Dissipation based on the equations specified in note 3 below.

1

| VDDD (V) |                              | EMICLK F | max (MHz) |

|----------|------------------------------|----------|-----------|

|          | VDDD <sub>Brownout</sub> (V) | DDR2     | mDDR      |

| 1.550    | 1.450                        | 205.71   | 205.71    |

| 1.450    | 1.350                        | 196.36   | 196.36    |

| 1.350    | 1.250                        | 196.36   | 196.36    |

Table 17. Frequency vs. Voltage for EMICLK—289-Pin BGA Package

## 3.1.3 **Fusebox Supply Current Parameters**

Table 18 lists the fusebox supply current parameters.

#### Table 18. Fusebox Supply Current Parameters

| Parameter                                                                                     | Symbol            | Min   | Тур   | Мах   | Unit |

|-----------------------------------------------------------------------------------------------|-------------------|-------|-------|-------|------|

| eFuse Program Current <sup>1</sup><br>Current to program one eFuse bit<br>efuse_vddq=2.5V     | Iprogram          | 21.39 | 25.05 | 33.54 | mA   |

| eFuse Read Current <sup>2</sup><br>Current to read an 8-bit eFuse word<br>vdd_fusebox = 3.3 V | I <sub>read</sub> | _     | _     | 4.07  | mA   |

<sup>1</sup> The current I<sub>program</sub> is during program time.

<sup>2</sup> The current I<sub>read</sub> is present for approximately 10 ns of the read access to the 8-bit word.

## 3.1.4 Interface Frequency Limits

Table 19 provides information for interface frequency limits.

#### **Table 19. Interface Frequency Limits**

| Parameter                        | Min. | Тур.        | Max. | Unit |

|----------------------------------|------|-------------|------|------|

| JTAG: TCK Frequency of Operation | —    | —           | 10   | MHz  |

| OSC24M_XTAL Oscillator           | —    | 24.000      | _    | MHz  |

| OSC32K_XTAL Oscillator           | —    | 32.768/32.0 |      | kHz  |

### 3.1.5 Power Modes

Table 20 describes the core, clock, and module settings for the different power modes of the processor.

#### Table 20. Power Mode Settings

| Core/Clock/Module     | Offstate | Standby | Run |

|-----------------------|----------|---------|-----|

| ARM Core              | Off      | Off     | On  |

| USB0 PLL (System PLL) | Off      | Off     | On  |

| OSC24M                | Off      | On      | On  |

- Core via I.D: 0.068 mm, Core via plating 0.016 mm

- Flag: trace style with ground balls under the die connected to the flag

- Die Attach: 0.033 mm non-conductive die attach, k = 0.3 W/m K

- Mold Compound: generic mold compound, k = 0.9 W/m K

#### Table 21. Thermal Resistance Data

| Rating                                              |                            |                     | Value | Unit |

|-----------------------------------------------------|----------------------------|---------------------|-------|------|

| Junction to ambient <sup>1</sup> natural convection | Single layer board<br>(1s) | R <sub>θJA</sub>    | 62    | °C/W |

| Junction to ambient <sup>1</sup> natural convection | Four layer board (2s2p)    | R <sub>θJA</sub>    | 36    | °C/W |

| Junction to ambient <sup>1</sup> (@200 ft/min)      | Single layer board<br>(1s) | R <sub>θJMA</sub>   | 53    | °C/W |

| Junction to ambient <sup>1</sup> (@200 ft/min)      | Four layer board<br>(2s2p) | R <sub>θJMA</sub>   | 33    | °C/W |

| Junction to boards <sup>2</sup>                     |                            | R <sub>θJB</sub>    | 24    | °C/W |

| Junction to case (top) <sup>3</sup>                 |                            | R <sub>0JCtop</sub> | 15    | °C/W |

| Junction to package top <sup>4</sup>                | Natural Convection         | Ψ <sub>JT</sub>     | 3     | °C/W |

<sup>1</sup> Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-2 and JESD51-6. Thermal test board meets JEDEC specification for this package.

- <sup>2</sup> Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- <sup>3</sup> Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- <sup>4</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

## 3.3 I/O DC Parameters

This section includes the DC parameters of the following I/O types:

- DDR I/O: Mobile DDR (LPDDR1), standard 1.8 V DDR2, and low-voltage 1.5 V DDR2 (LVDDR2)

- General purpose I/O (GPIO)

### 3.3.1 DDR I/O DC Parameters

Table 22 shows the EMI digital pin DC characteristics.

#### NOTE

The current values and the I-V curves of the I/O DC characteristics are estimated based on an overly conservative device model. They are updated upon the measurement results of the first silicon.

| Table 25. Digital Pin DC Characteristics for GPIO in 3.3-V Mode (contin | າued) |

|-------------------------------------------------------------------------|-------|

|-------------------------------------------------------------------------|-------|

| Parameter                            | Symbol | Min | Мах | Unit |

|--------------------------------------|--------|-----|-----|------|

| 10-K pull-up resistance <sup>2</sup> | Rpu10k | 8   | 12  | kΩ   |

| 47-K pull-up resistance              | Rpu47k | 39  | 56  | kΩ   |

<sup>1</sup> The conditions of the current measurements for all different drives are as follows:

IOL: at 0.4 V

IOH: at VDDIO \* 0.8 V

Maximum corner for 3.3 V mode: 3.6 V, -40°C, fast process.

Minimum corner for 3.3 V mode: 3.0 V, 105°C, slow process.

8 gpio pins (LCD\_D0-D7) and 2 gpio\_clk pins (LCD\_DOTCLK and LCD\_WR\_RWN) simultaneously loaded.

<sup>2</sup> See the i.MX28 reference manual for detailed pull-up configuration of each I/O.

#### Table 26 shows the digital pin DC characteristics for GPIO in 1.8 V mode. Table 26. Digital Pin DC Characteristics for GPIO in 1.8 V Mode

|                                      | Symbol       | Min           | Max               | Unit |

|--------------------------------------|--------------|---------------|-------------------|------|

| Input voltage high (DC)              | VIH          | 0.7 × VDDIO18 | VDDIO18           | V    |

| Input voltage low (DC)               | VIL          | —             | 0.3 	imes VDDIO18 | V    |

| Output voltage high (DC)             | VOH          | 0.8 * VDDIO18 | —                 | V    |

| Output voltage low (DC)              | VOL          | —             | 0.2 × VDDIO18     | V    |

| Output source current <sup>1</sup>   | IOH – Iow    | -2.2          | —                 | mA   |

| (DC)<br>gpio                         | IOH – medium | -3.5          | —                 | mA   |

|                                      | IOH – high   | -4.0          | —                 | mA   |

| Output sink current (DC)             | IOL – Iow    | 3.3           | —                 | mA   |

| gpio                                 | IOL – medium | 7.0           | —                 | mA   |

|                                      | IOL – high   | 7.5           | —                 | mA   |

| Output source current                | IOH – Iow    | -4.2          | —                 | mA   |

| (DC)<br>gpio_clk                     | IOH – high   | -6.0          | _                 | mA   |

| Output sink current (DC)             | IOL – Iow    | 6.8           | —                 | mA   |

| gpio_clk                             | IOL – high   | 11.5          | —                 | mA   |

| 10-K pull-up resistance <sup>2</sup> | Rpu10k       | 8             | 12                | kΩ   |

| 47-K pull-up resistance              | Rpu47k       | 39            | 56                | kΩ   |

<sup>1</sup> The condition of the current measurements for all different drives are as follows:

Maximum corner for 1.8 V mode: 1.9 V, -40°C, Fast process.

Minimum corner for 1.8 V mode: 1.7 V, 105°C, Slow process.

1 gpio pin (GPMI\_D0) and 1 gpio\_clk pin (GPMI\_WRN) simultaneously loaded.

<sup>2</sup> See the i.MX28 reference manual for detailed pull-up configuration of each I/O.

Table 28 shows the F-type GPIO AC timing and parameters.

| Parameters               | Symbol | Test Voltage | Test Capacitance | Min Ri | se/Fall | Max Ri | ise/Fall | Unit | Notes |

|--------------------------|--------|--------------|------------------|--------|---------|--------|----------|------|-------|

| Duty cycle               | Fduty  | —            | _                | -      | _       | -      | _        | %    |       |

| Output pad transition    | tpr    | 1.7~1.9V     | 10 pF            | 0.58   | 0.61    | 1.29   | 1.33     | ns   | _     |

| times (maximum<br>drive) |        | 1.7~1.9V     | 20 pF            | 0.89   | 0.88    | 1.94   | 1.88     |      | _     |

| ,                        |        | 1.7~1.9V     | 50 pF            | 1.83   | 1.59    | 3.88   | 3.39     |      | _     |

|                          |        | 3.0~3.6V     | 10 pF            | 0.71   | 0.68    | 1.47   | 1.34     |      |       |

|                          |        | 3.0~3.6V     | 20 pF            | 1.02   | 1.04    | 2.11   | 1.99     |      | _     |

|                          |        | 3.0~3.6V     | 50 pF            | 1.98   | 2.09    | 3.97   | 3.96     |      |       |

| Output pad transition    | tpr    | 1.7~1.9V     | 10 pF            | 0.76   | 0.76    | 1.68   | 1.61     | ns   |       |

| times (medium drive)     |        | 1.7~1.9V     | 20 pF            | 1.23   | 1.13    | 2.63   | 2.38     |      |       |

|                          |        | 1.7~1.9V     | 50 pF            | 2.66   | 2.18    | 5.61   | 4.6      |      |       |

|                          |        | 3.0~3.6V     | 10 pF            | 0.9    | 0.88    | 1.84   | 1.7      |      |       |

|                          |        | 3.0~3.6V     | 20 pF            | 1.36   | 1.4     | 2.76   | 2.67     |      | _     |

|                          |        | 3.0~3.6V     | 50 pF            | 2.85   | 3.02    | 5.59   | 5.67     |      | _     |

| Output pad transition    | tpr    | 1.7~1.9V     | 10 pF            | 1.32   | 1.26    | 2.88   | 2.72     | ns   | _     |

| times (low drive)        |        | 1.7~1.9V     | 20 pF            | 2.27   | 1.98    | 4.84   | 4.23     |      | _     |

|                          |        | 1.7~1.9V     | 50 pF            | 5.23   | 4.13    | 10.95  | 8.8      |      | _     |

|                          |        | 3.0~3.6V     | 10 pF            | 1.46   | 1.55    | 3.05   | 3        |      | _     |

|                          |        | 3.0~3.6V     | 20 pF            | 2.46   | 2.62    | 4.92   | 5.02     |      | _     |

|                          |        | 3.0~3.6V     | 50 pF            | 5.56   | 5.96    | 10.78  | 11.22    |      | _     |

| Output pad slew rate     | tps    | 1.7~1.9V     | 10 pF            | 1.97   | 1.87    | 0.79   | 0.77     | ns   | _     |

| (maximum drive)          |        | 1.7~1.9V     | 20 pF            | 1.28   | 1.30    | 0.53   | 0.54     |      | _     |

|                          |        | 1.7~1.9V     | 50 pF            | 0.62   | 0.72    | 0.26   | 0.30     |      | _     |

|                          |        | 3.0~3.6V     | 10 pF            | 3.04   | 3.18    | 1.22   | 1.34     |      | _     |

|                          |        | 3.0~3.6V     | 20 pF            | 2.12   | 2.08    | 0.85   | 0.90     |      | _     |

|                          |        | 3.0~3.6V     | 50 pF            | 1.09   | 1.03    | 0.45   | 0.45     |      | _     |

| Output pad slew rate     | tps    | 1.7~1.9V     | 10 pF            | 1.50   | 1.50    | 0.61   | 0.63     | ns   | _     |

| (medium drive)           |        | 1.7~1.9V     | 20 pF            | 0.93   | 1.01    | 0.39   | 0.43     |      | —     |

|                          |        | 1.7~1.9V     | 50 pF            | 0.43   | 0.52    | 0.18   | 0.22     |      |       |

|                          |        | 3.0~3.6V     | 10 pF            | 2.40   | 2.45    | 0.98   | 1.06     |      | —     |

|                          |        | 3.0~3.6V     | 20 pF            | 1.59   | 1.54    | 0.65   | 0.67     |      |       |

|                          |        | 3.0~3.6V     | 50 pF            | 0.76   | 0.72    | 0.32   | 0.32     |      |       |

#### Table 28. F-type GPIO

| Parameters           | Symbol            | Test Voltage | Test Capacitance | Min Ri | se/Fall | Max Ri | ise/Fall | Unit | Notes |

|----------------------|-------------------|--------------|------------------|--------|---------|--------|----------|------|-------|

| Output pad slew rate | tps               | 1.7~1.9V     | 10 pF            | 1.44   | 1.51    | 0.59   | 0.63     | ns   |       |

| (low drive)          |                   | 1.7~1.9V     | 20 pF            | 0.84   | 0.96    | 0.35   | 0.40     |      | _     |

|                      |                   | 1.7~1.9V     | 50 pF            | 0.36   | 0.46    | 0.16   | 0.19     |      | _     |

|                      |                   | 3.0~3.6V     | 10 pF            | 1.48   | 1.39    | 0.59   | 0.60     |      | _     |

|                      |                   | 3.0~3.6V     | 20 pF            | 0.88   | 0.82    | 0.37   | 0.36     |      | _     |

|                      |                   | 3.0~3.6V     | 50 pF            | 0.39   | 0.36    | 0.17   | 0.16     |      | _     |

| Input pad average    | e tih 1.7 V-1.9 V | —            | 1(               | 00     | 7       | '5     | mV       | _    |       |

| hysteresis           |                   | 3.0 V–3.6 V  | _                | 1(     | 00      | 5      | 0        |      |       |

Table 28. F-type GPIO (continued)

Table 29 shows the CLK-type GPIO AC timing and parameters.

## Table 29. CLK-Type GPIO

| Parameters               | Symbol | Test Voltage | Test Capacitance | Min Rise/Fall |      | Min Rise/Fall Max Rise/Fall |      | units | Notes |   |

|--------------------------|--------|--------------|------------------|---------------|------|-----------------------------|------|-------|-------|---|

| Duty cycle               | Fduty  | —            | —                | -             | _    | -                           | _    | %     | —     |   |

| Output pad transition    | tpr    | 1.7~1.9V     | 10 pF            | 0.48          | 0.52 | 1.08                        | 1.12 | ns    | —     |   |

| times (maximum<br>drive) |        | 1.7~1.9V     | 20 pF            | 0.72          | 0.74 | 1.56                        | 1.56 |       | —     |   |

|                          |        | 1.7~1.9V     | 50 pF            | 1.41          | 1.28 | 3.04                        | 2.7  |       | —     |   |

|                          |        | 3.0~3.6V     | 10 pF            | 0.61          | 0.57 | 1.25                        | 1.12 |       | —     |   |

|                          |        | 3.0~3.6V     | 20 pF            | 0.85          | 0.85 | 1.73                        | 1.63 |       | —     |   |

|                          |        | 3.0~3.6V     | 50 pF            | 1.56          | 1.63 | 3.13                        | 3.08 |       | —     |   |

| Output pad transition    | tpr    | 1.7~1.9V     | 10 pF            | 0.76          | 0.76 | 1.67                        | 1.62 | ns    | —     |   |

| times (medium drive)     |        | 1.7~1.9V     | 20 pF            | 1.22          | 1.14 | 2.64                        | 2.41 |       | —     |   |

|                          |        | 1.7~1.9V     | 50 pF            | 2.66          | 2.2  | 5.61                        | 4.62 |       | —     |   |

|                          |        | 3.0~3.6V     | 10 pF            | 0.9           | 0.89 | 1.83                        | 1.72 |       | —     |   |

|                          |        | 3.0~3.6V     | 20 pF            | 1.37          | 1.41 | 2.77                        | 2.69 |       | —     |   |

|                          |        | 3.0~3.6V     | 50 pF            | 2.85          | 3.03 | 5.59                        | 5.72 |       | —     |   |

| Output pad slew rate     | tps    | 1.7~1.9V     | 10 pF            | 2.38          | 2.19 | 0.94                        | 0.91 | ns    | —     |   |

| (maximum drive)          |        | 1.7~1.9V     | 20 pF            | 1.58          | 1.54 | 0.65                        | 0.65 |       | —     |   |

|                          |        | 1.7~1.9V     | 50 pF            | 0.81          | 0.89 | 0.34                        | 0.38 |       | —     |   |

|                          |        |              | 3.0~3.6V         | 10 pF         | 3.54 | 3.79                        | 1.44 | 1.61  |       | — |

|                          |        | 3.0~3.6V     | 20 pF            | 2.54          | 2.54 | 1.04                        | 1.10 |       | —     |   |

|                          |        | 3.0~3.6V     | 50 pF            | 1.38          | 1.33 | 0.58                        | 0.58 |       | —     |   |

## 3.5.6 FlexCAN AC Timing

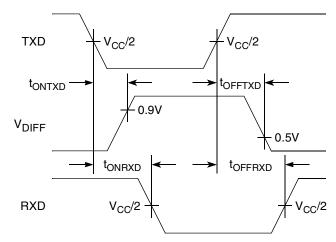

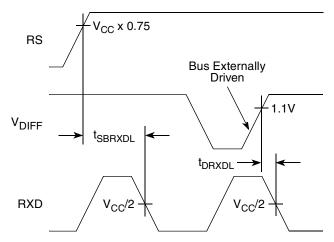

Table 45 and Table 46 show voltage requirements for the FlexCAN transceiver Tx and Rx pins.

Table 45. Tx Pin Characteristics

| Parameter                 | Symbol | Min. | Тур. | Max.                   | Unit |

|---------------------------|--------|------|------|------------------------|------|

| High-level output voltage | Voн    | 2    | _    | Vcc <sup>1</sup> + 0.3 | V    |

| Low-level output voltage  | Vol    |      | 0.8  | —                      | V    |

<sup>1</sup> Vcc =  $+3.3 V \pm 5\%$

Table 46. Rx Pin Characteristics

| Parameter                | Symbol | Min.              | Тур. | Max.             | Unit |

|--------------------------|--------|-------------------|------|------------------|------|

| High-level input voltage | Vih    | $0.8 	imes Vcc^1$ | _    | Vcc <sup>1</sup> | V    |

| Low-level input voltage  | VIL    | —                 | 0.4  | —                | V    |

<sup>1</sup> Vcc = +3.3 V  $\pm$  5%

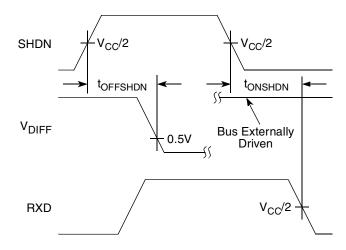

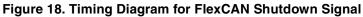

Figure 16 through Figure 19 show the FlexCAN timing, including timing of the standby and shutdown signals.

Figure 16. FlexCAN Timing Diagram

Figure 19. Timing Diagram for FlexCAN Shutdown-to-Standby Signal

**Electrical Characteristics**

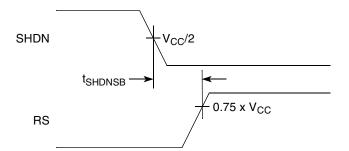

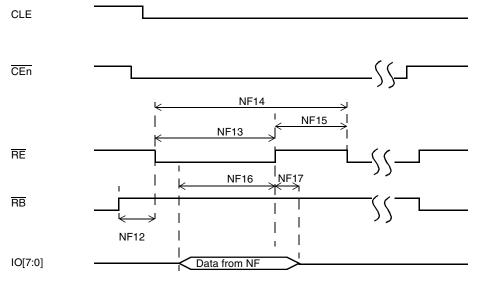

Figure 22. Write Data Latch Cycle Timing Diagram

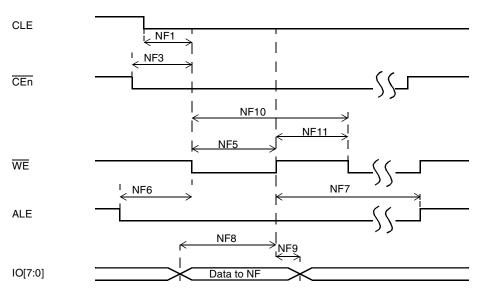

Figure 23. Read Data Latch Cycle Timing Diagram

## 3.5.8 LCD AC Output Electrical Specifications

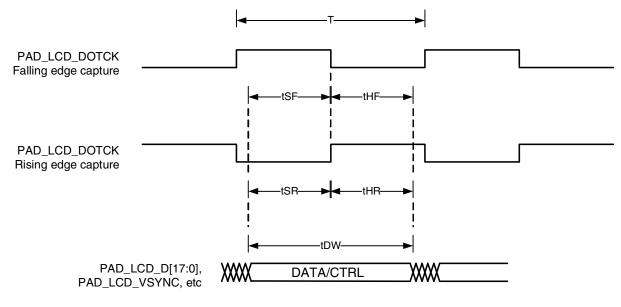

Figure 24 depicts the AC output timing for the LCD module. Table 48 lists the LCD module timing parameters.

Notes:

T = LCD interface clock period I/O Drive Strength = 4mA I/O Voltage = 3.3V Cck = Capacitance load on DOTCK pad Cd = Capacitance load on DATA/CTRL pad

Table 48. LCD AC Output Timing Parameters

| ID  | Parameter                   | Description                               |

|-----|-----------------------------|-------------------------------------------|

| tSF | Data setup for falling edge | DOTCK = T/2 - 1.97ns + 0.15*Cck - 0.19*Cd |

| tHF | Data hold for falling edge  | DOTCK = T/2 + 0.29ns + 0.09*Cd - 0.10*Cck |

| tSR | Data setup for rising edge  | DOTCK = T/2 - 2.09ns + 0.18*Cck - 0.19*Cd |

| tHR | Data hold for rising edge   | DOTCK = T/2 + 0.40ns + 0.09*Cd - 0.10*Cck |

| tDW | Data valid window           | tDW = T – 1.45ns                          |

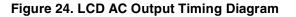

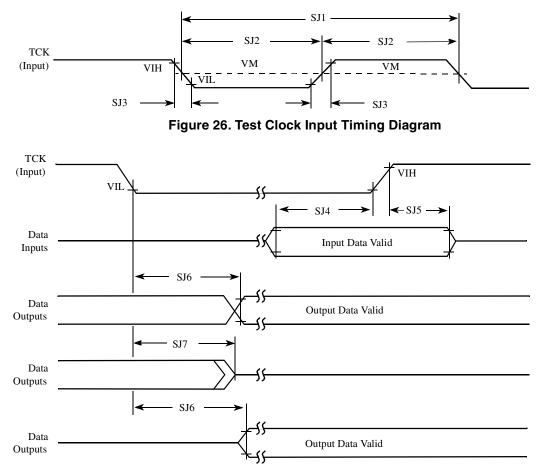

## 3.5.10 JTAG Interface Timing

Figure 26 through Figure 29 show respectively the test clock input, boundary scan, test access port, and TRST timings for the SJC. Table 50 describes the SJC timing parameters (SJ1–SJ13) indicated in the figures.

Figure 27. Boundary Scan (JTAG) Timing Diagram

| ID   | Parameter                           | Min. | Max. | Unit |

|------|-------------------------------------|------|------|------|

| SS1  | BITCLK period                       | 81.4 | _    | ns   |

| SS2  | BITCLK high period                  | 36.0 | _    | ns   |

| SS3  | BITCLK rise time                    | —    | 6.0  | ns   |

| SS4  | BITCLK low period                   | 36.0 | _    | ns   |

| SS5  | BITCLK fall time                    | —    | 6.0  | ns   |

| SS14 | BITCLK high to LRCLK high           | —    | 15.0 | ns   |

| SS15 | BITCLK high to LRCLK low            | —    | 15.0 | ns   |

| SS16 | SDATA setup time before BITCLK high | 10.0 | _    | ns   |

| SS17 | SDATA hold time after BITCLK high   | 0.0  | _    | ns   |

#### Table 55. SAIF Receiver Timing with Internal Clock

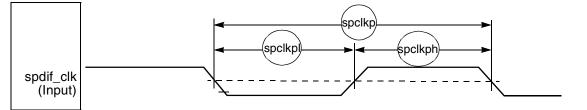

## 3.5.13 SPDIF AC Timing

SPDIF data is sent using bi-phase marking code. When encoding, the SPDIF data signal is modulated by a clock that is twice the bit rate of the data signal.

The following Table 56 shows SPDIF timing parameters, including the timing of the modulating Tx clock (spdif\_clk) in SPDIF transmitter as shown in the Figure 35.

| Oberesteristics                                                                                                   | Cumbal   | Timing Para | Unit                |        |  |

|-------------------------------------------------------------------------------------------------------------------|----------|-------------|---------------------|--------|--|

| Characteristics                                                                                                   | Symbol _ | Min         | Max                 | – Unit |  |

| <ul><li>SPDIFOUT output (Load = 30pf)</li><li>Skew</li><li>Transition Rising</li><li>Transition Falling</li></ul> |          |             | 1.5<br>13.6<br>18.0 | ns     |  |

| Modulating Tx clock (spdif_clk) period                                                                            | spclkp   | 81.4        | —                   | ns     |  |

| spdif_clk high period                                                                                             | spclkph  | 65.1        | —                   | ns     |  |

| spdif_clk low period                                                                                              | spclkpl  | 65.1        | —                   | ns     |  |

Table 56. SPDIF Timing

Figure 35. spdif\_clk Timing

Figure 44 shows the i.MX28 production package.

Figure 44. ...i.MX28 Production Package

## 4.2 Ground, Power, Sense, and Reference Contact Assignments

Table 64 shows power and ground contact assignments for the MAPBGA package.

| Contact Name | Contact Assignment                          |

|--------------|---------------------------------------------|

| VDDA1        | C13                                         |

| VDDD         | G12,G11,F10,F11,K12,F12,G10                 |

| VDDIO18      | G8,F9,F8,G9                                 |

| VDDIO33      | H8,J8,N3,G3,E6,J9,J10,A7,E16                |

| VDDIO33_EMI  | N17                                         |

| VDDIO_EMI    | P11,R13,N13,N15,G17,M12,M10,G13,M11,L13,G15 |

#### Table 64. MAPBGA Power and Ground Contact Assignments

#### Package Information and Contact Assignments

#### Table 66. 289-Pin i.MX281 MAPBGA Ball Map (continued)

#### Package Information and Contact Assignments

| в | NC         | NC         | SSP2_MISO    | SSP0_DATA7  | SSP0_DATA4 | SSP0_DATA0  | NSS          | USB1DM       | DEBUG   | USBODP      | VSSA2     | XTALO    | VSSA1      | HSADC0       | DCDC_BATT  | DCDC_VDDA | DCDC_LN1   | В |

|---|------------|------------|--------------|-------------|------------|-------------|--------------|--------------|---------|-------------|-----------|----------|------------|--------------|------------|-----------|------------|---|

| υ | NC         | NC         | SSP2_MOSI    | SSP2_SS0    | SSP0_DATA5 | SSP0_DATA1  | I2C0_SCL     | LRADC2       | LRADC1  | TESTMODE    | RTC_XTALO | VDDXTAL  | VDDA1      | LRADC6       | LRADC0     | VSS       | DCDC_VDDIO | U |

| ٥ | NC         | NC         | SSP2_SS1     | SSP2_SS2    | SSP0_DATA6 | SSP0_DATA2  | SPDIF        | I2C0_SDA     | LRADC3  | SSP0_DETECT | RTC_XTALI | JTAG_TMS | LRADC4     | JTAG_TRST    | LRADC5     | VDD1P5    | DCDC_VDDD  | D |

| ш | NC         | ENET_CLK   | ENET0_TX_CLK | ENET0_RX_EN | VSS        | VDDIO33     | SAIF0_SDATA0 | SAIF1_SDATA0 | PWM3    | PWM4        | JTAG_TCK  | JTAG_TDI | JTAG_TDO   | JTAG_RTCK    | VSS        | VDDIO33   | VDD5V      | ш |

| Ŀ | ENET0_TXD0 | ENET0_TXD1 | ENET0_RX_CLK | ENET0_TX_EN | NC         | NC          | SAIF0_BITCLK | VDDIO18      | VDDIO18 | DDD         | VDDD      | VDDD     | EMI_D14    | VSSIO_EMI    | EMI_DQM1   | VSSIO_EMI | EMI_D15    | Ŀ |

| J | ENET0_TXD2 | ENET0_TXD3 | VDDIO33      | ENETO_MDC   | AUARTO_RX  | SAIF0_LRCLK | SAIF0_MCLK   | VDDIO18      | VDDIO18 | DDD         | DDD       | DDD      | VDDIO_EMI  | EMI_D10      | VDDIO_EMI  | EMI_D08   | VDDIO_EMI  | g |

| т | ENET0_RXD0 | ENET0_RXD1 | VSS          | ENET0_MDIO  | AUARTO_TX  | NC          | NC           | VDDIO33      | NSS     | VSS         | VSS       | VSS      | EMI_D12    | VSSIO_EMI    | EMI_D09    | NSS       | EMI_D13    | т |

| 7 | ENET0_RXD2 | ENET0_RXD3 | ENET0_CRS    | ENET0_COL   | NC         | AUART0_CTS  | AUART0_RTS   | VDDIO33      | VDDIO33 | VDDIO33     | VSS       | VSS      | VDDIO_EMIQ | EMI_D11      | VSS        | EMI_DQS1N | EMI_DQS1   | J |

| ч | LCD_WR_RWN | LCD_D00    | LCD_D01      | AUART1_TX   | NC         | NC          | PWMO         | PWM2         | NSS     | NSS         | VSS       | VDDD     | EMI_VREF1  | EMI_DDR_OPEN | VDDIO_EMIQ | EMI_DQS0N | EMI_DQS0   | х |

#### Package Information and Contact Assignments

|   |         |         |         |           |         |           |           | _         | z           |           |           |           |           |           | N_FB            |           |             |   |

|---|---------|---------|---------|-----------|---------|-----------|-----------|-----------|-------------|-----------|-----------|-----------|-----------|-----------|-----------------|-----------|-------------|---|

| _ | NC      | LCD_D02 | LCD_D03 | AUART1_RX | NC      | NC        | PWM1      | GPMI_RDY3 | GPMI_RESETN | VSS       | VSS       | VSSIO_EMI | VDDIO_EMI | EMI_D06   | R_OPE           | EMI_CLKN  | EMI_CLK     | _ |

|   |         | ГС      | ГС      | AUA       |         |           |           | GPN       | GPMI        |           |           | VSS       | VDD       | Ш         | EMI_DDR_OPEN_FB | EM        | Ш           |   |

| ≥ | NC      | LCD_D04 | LCD_D05 | LCD_RS    | NC      | LCD_RESET | GPMI_CE2N | GPMI_RDY2 | GPMI_CE3N   |           |           |           | EMI_D01   | NSS       | EMI_DQM0        | VSSIO_EMI | EMI_D07     | Þ |

| z | NC      | LCD_D06 | VDDIO33 | VSS       | NC      | GPMI_RDY0 | GPMI_CE0N | GPMI_RDY1 | GPMI_CE1N   | EMI_A14   | EMI_A07   | EMI_BA2   | VDDIO_EMI | EMI_D03   | VDDIO_EMI       | EMI_D00   | VDDIO33_EMI | z |

| ٩ | LCD_D07 | LCD_D08 | LCD_D09 | LCD_RD_E  | LCD_CS  | GPMI_ALE  | GPMI_CLE  | GPML_WRN  | EMI_CE1N    | EMI_A09   | VDDIO_EMI | EMI_CEON  | EMI_D04   | VSSIO_EMI | EMI_D02         | VSSIO_EMI | EMI_D05     | ٩ |

| æ | LCD_D10 | LCD_D11 | LCD_D17 | LCD_D20   | LCD_D23 | GPMI_RDN  | GPMI_D05  | GPMI_D02  | EMI_A06     | VSSIO_EMI | EMI_A05   | VSSIO_EMI | VDDIO_EMI | EMI_VREF0 | VDDIO_EMIQ      | EMI_RASN  | EMI_ODT0    | æ |

| F | LCD_D12 | LCD_D13 | LCD_D16 | LCD_D19   | LCD_D22 | GPMI_D07  | GPMI_D04  | GPMI_D01  | EMI_A13     | EMI_A11   | EMI_A03   | EMI_BA1   | EMI_CKE   | VSSIO_EMI | EMI_WEN         | EMI_BAO   | EMI_ODT1    | F |

| 5 | NSS     | LCD_D14 | LCD_D15 | LCD_D18   | LCD_D21 | GPMI_D06  | GPMI_D03  | GPMI_D00  | EMI_A08     | EMI_A04   | EMI_A12   | EMI_A01   | EMI_A10   | EMI_A02   | EMI_A00         | EMI_CASN  | VSSIO_EMI   | Э |

|   | -       | 2       | Э       | 4         | 5       | 9         | 7         | 8         | 6           | 10        | 11        | 12        | 13        | 14        | 15              | 16        | 17          |   |

#### Table 67. 289-Pin i.MX285 MAPBGA Ball Map (continued)

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM is the registered trademark of ARM Limited. ARM9 is a trademark of ARM Limited.

© 2012 Freescale Semiconductor, Inc. All rights reserved.

Document Number: IMX28AEC Rev. 3 07/2012