Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                       |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 25MHz                                                                         |

| Connectivity               | SCI, SmartCard                                                                |

| Peripherals                | PWM, WDT                                                                      |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | -                                                                             |

| Program Memory Type        | ROMIess                                                                       |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-BFQFP                                                                     |

| Supplier Device Package    | 100-QFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d13008fbl25v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

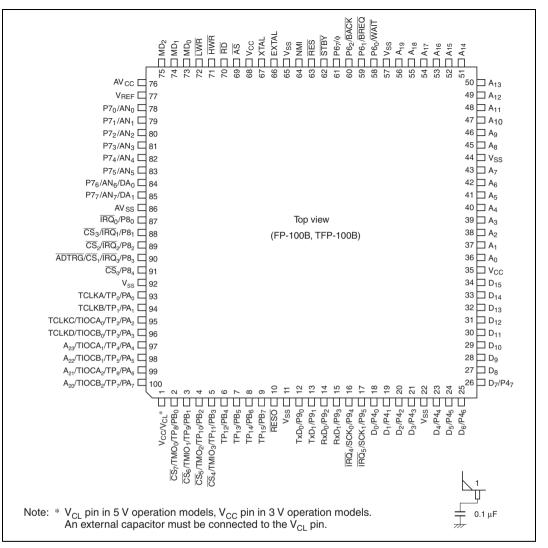

Figure 1.2 Pin Arrangement of H8/3008 (FP-100B or TFP-100B Package, Top View)

|     | ~     |        |

|-----|-------|--------|

| 1   | ()\/@ | rview  |

| ••• | 0,0   | 101000 |

| Pin No.             | Pin Name              |                       |                       |                 |  |  |  |  |  |  |

|---------------------|-----------------------|-----------------------|-----------------------|-----------------|--|--|--|--|--|--|

| FP-100B<br>TFP-100B | Mode 1                | Mode 2                | Mode 3                | Mode 4          |  |  |  |  |  |  |

| 28                  | D <sub>9</sub>        | D <sub>9</sub>        | D <sub>9</sub>        | D <sub>9</sub>  |  |  |  |  |  |  |

| 29                  | D <sub>10</sub>       | D <sub>10</sub>       | D <sub>10</sub>       | D <sub>10</sub> |  |  |  |  |  |  |

| 30                  | D <sub>11</sub>       | D <sub>11</sub>       | D <sub>11</sub>       | D <sub>11</sub> |  |  |  |  |  |  |

| 31                  | D <sub>12</sub>       | D <sub>12</sub>       | D <sub>12</sub>       | D <sub>12</sub> |  |  |  |  |  |  |

| 32                  | D <sub>13</sub>       | D <sub>13</sub>       | D <sub>13</sub>       | D <sub>13</sub> |  |  |  |  |  |  |

| 33                  | D <sub>14</sub>       | D <sub>14</sub>       | D <sub>14</sub>       | D <sub>14</sub> |  |  |  |  |  |  |

| 34                  | D <sub>15</sub>       | D <sub>15</sub>       | D <sub>15</sub>       | D <sub>15</sub> |  |  |  |  |  |  |

| 35                  | V <sub>cc</sub>       | V <sub>cc</sub>       | V <sub>cc</sub>       | V <sub>cc</sub> |  |  |  |  |  |  |

| 36                  | A <sub>o</sub>        | A <sub>o</sub>        | A <sub>o</sub>        | A <sub>o</sub>  |  |  |  |  |  |  |

| 37                  | A <sub>1</sub>        | A <sub>1</sub>        | A,                    | A <sub>1</sub>  |  |  |  |  |  |  |

| 38                  | A <sub>2</sub>        | A <sub>2</sub>        | A <sub>2</sub>        | A <sub>2</sub>  |  |  |  |  |  |  |

| 39                  | A <sub>3</sub>        | A <sub>3</sub>        | A <sub>3</sub>        | A <sub>3</sub>  |  |  |  |  |  |  |

| 40                  | A <sub>4</sub>        | $A_{_4}$              | $A_{_4}$              | $A_{_4}$        |  |  |  |  |  |  |

| 41                  | A <sub>5</sub>        | A <sub>5</sub>        | A <sub>5</sub>        | A <sub>5</sub>  |  |  |  |  |  |  |

| 42                  | A <sub>6</sub>        | $A_6$                 | A <sub>6</sub>        | A <sub>6</sub>  |  |  |  |  |  |  |

| 43                  | A <sub>7</sub>        | <b>A</b> <sub>7</sub> | A <sub>7</sub>        | A <sub>7</sub>  |  |  |  |  |  |  |

| 44                  | V <sub>ss</sub>       | V <sub>ss</sub>       | V <sub>ss</sub>       | V <sub>ss</sub> |  |  |  |  |  |  |

| 45                  | A <sub>8</sub>        | A <sub>s</sub>        | A <sub>s</sub>        | A <sub>8</sub>  |  |  |  |  |  |  |

| 46                  | A <sub>9</sub>        | A <sub>9</sub>        | A <sub>9</sub>        | A <sub>9</sub>  |  |  |  |  |  |  |

| 47                  | A <sub>10</sub>       | A <sub>10</sub>       | A <sub>10</sub>       | A <sub>10</sub> |  |  |  |  |  |  |

| 48                  | A <sub>11</sub>       | A <sub>11</sub>       | A <sub>11</sub>       | A <sub>11</sub> |  |  |  |  |  |  |

| 49                  | A <sub>12</sub>       | A <sub>12</sub>       | A <sub>12</sub>       | A <sub>12</sub> |  |  |  |  |  |  |

| 50                  | A <sub>13</sub>       | A <sub>13</sub>       | A <sub>13</sub>       | A <sub>13</sub> |  |  |  |  |  |  |

| 51                  | A <sub>14</sub>       | A <sub>14</sub>       | A <sub>14</sub>       | A <sub>14</sub> |  |  |  |  |  |  |

| 52                  | A <sub>15</sub>       | A <sub>15</sub>       | A <sub>15</sub>       | A <sub>15</sub> |  |  |  |  |  |  |

| 53                  | A <sub>16</sub>       | A <sub>16</sub>       | A <sub>16</sub>       | A <sub>16</sub> |  |  |  |  |  |  |

| 54                  | A <sub>17</sub>       | A <sub>17</sub>       | A <sub>17</sub>       | A <sub>17</sub> |  |  |  |  |  |  |

| 55                  | A <sub>18</sub>       | A <sub>18</sub>       | A <sub>18</sub>       | A <sub>18</sub> |  |  |  |  |  |  |

| 56                  | A <sub>19</sub>       | A <sub>19</sub>       | A <sub>19</sub>       | A <sub>19</sub> |  |  |  |  |  |  |

| 57                  | V <sub>ss</sub>       | V <sub>ss</sub>       | V <sub>ss</sub>       | V <sub>ss</sub> |  |  |  |  |  |  |

| 58                  | P6 <sub>0</sub> /WAIT | P6 <sub>0</sub> /WAIT | P6 <sub>0</sub> /WAIT | P6₀/WAIT        |  |  |  |  |  |  |

| Pin No.             | Pin Name                                                       |                                                          |                                                                       |                                                                       |  |  |  |  |  |  |  |

|---------------------|----------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|--|--|--|

| FP-100B<br>TFP-100B | Mode 1                                                         | Mode 2                                                   | Mode 3                                                                | Mode 4                                                                |  |  |  |  |  |  |  |

| 90                  | $P8_{3}/\overline{IRQ}_{3}/\overline{CS}_{1}/\overline{ADTRG}$ | $P8_3/\overline{IRQ}_3/\overline{CS}_1/\overline{ADTRG}$ | P8 <sub>3</sub> /IRQ <sub>3</sub> /CS <sub>1</sub> /ADTRG             | P8 <sub>3</sub> /IRQ <sub>3</sub> /CS <sub>1</sub> /ADTRG             |  |  |  |  |  |  |  |

| 91                  | P8 <sub>4</sub> / <del>CS</del> <sub>0</sub>                   | $P8_4/\overline{CS}_0$                                   | P8 <sub>4</sub> / <del>CS</del> <sub>0</sub>                          | $P8_4/\overline{CS}_0$                                                |  |  |  |  |  |  |  |

| 92                  | V <sub>ss</sub>                                                | V <sub>ss</sub>                                          | V <sub>ss</sub>                                                       | V <sub>ss</sub>                                                       |  |  |  |  |  |  |  |

| 93                  | PA <sub>0</sub> /TP <sub>0</sub> /TCLKA                        | PA <sub>0</sub> /TP <sub>0</sub> /TCLKA                  | PA <sub>0</sub> /TP <sub>0</sub> /TCLKA                               | PA <sub>0</sub> /TP <sub>0</sub> /TCLKA                               |  |  |  |  |  |  |  |

| 94                  | PA <sub>1</sub> /TP <sub>1</sub> /TCLKB                        | PA,/TP,/TCLKB                                            | PA,/TP,/TCLKB                                                         | PA,/TP,/TCLKB                                                         |  |  |  |  |  |  |  |

| 95                  | PA₂/TP₂/TIOCA₀/<br>TCLKC                                       | PA/TP/TIOCA/<br>TCLKC                                    | PA₂/TP₂/TIOCA√<br>TCLKC                                               | PA₂/TP₂/TIOCA₀/<br>TCLKC                                              |  |  |  |  |  |  |  |

| 96                  | PA,/TP,/TIOCB,/<br>TCLKD                                       | PA,/TP,/TIOCB,/<br>TCLKD                                 | PA,/TP,/TIOCB,/<br>TCLKD                                              | PA,/TP,/TIOCB,/<br>TCLKD                                              |  |  |  |  |  |  |  |

| 97                  | PA <sub>4</sub> /TP <sub>4</sub> /TIOCA <sub>1</sub>           | PA <sub>4</sub> /TP <sub>4</sub> /TIOCA <sub>1</sub>     | PA4/TP4/TIOCA1/A23                                                    | PA <sub>4</sub> /TP <sub>4</sub> /TIOCA <sub>1</sub> /A <sub>23</sub> |  |  |  |  |  |  |  |

| 98                  | PA <sub>5</sub> /TP <sub>5</sub> /TIOCB <sub>1</sub>           | PA <sub>5</sub> /TP <sub>5</sub> /TIOCB <sub>1</sub>     | PA <sub>5</sub> /TP <sub>5</sub> /TIOCB <sub>1</sub> /A <sub>22</sub> | PA <sub>5</sub> /TP <sub>5</sub> /TIOCB <sub>1</sub> /A <sub>22</sub> |  |  |  |  |  |  |  |

| 99                  | PA <sub>6</sub> /TP <sub>6</sub> /TIOCA <sub>2</sub>           | PA <sub>6</sub> /TP <sub>6</sub> /TIOCA <sub>2</sub>     | PA <sub>6</sub> /TP <sub>6</sub> /TIOCA <sub>2</sub> /A <sub>21</sub> | PA <sub>6</sub> /TP <sub>6</sub> /TIOCA <sub>2</sub> /A <sub>21</sub> |  |  |  |  |  |  |  |

| 100                 | PA <sub>7</sub> /TP <sub>7</sub> /TIOCB <sub>2</sub>           | PA <sub>7</sub> /TP <sub>7</sub> /TIOCB <sub>2</sub>     | A <sub>20</sub>                                                       | A <sub>20</sub>                                                       |  |  |  |  |  |  |  |

Notes: 1. In modes 1 and 3 the P4<sub>0</sub> to P4<sub>7</sub> functions of pins P4<sub>0</sub>/D<sub>0</sub> to P4<sub>7</sub>/D<sub>7</sub> are selected after a reset, but they can be changed by software.

2. In modes 2 and 4 the  $D_0$  to  $D_7$  functions of pins  $P4_0/D_0$  to  $P4_7/D_7$  are selected after a reset, but they can be changed by software.

3. This pin functions as  $V_{cL}$  in 5 V operation models, and as  $V_{cc}$  in 3 V operation models.

### Renesas

# 2.4 Register Configuration

### 2.4.1 Overview

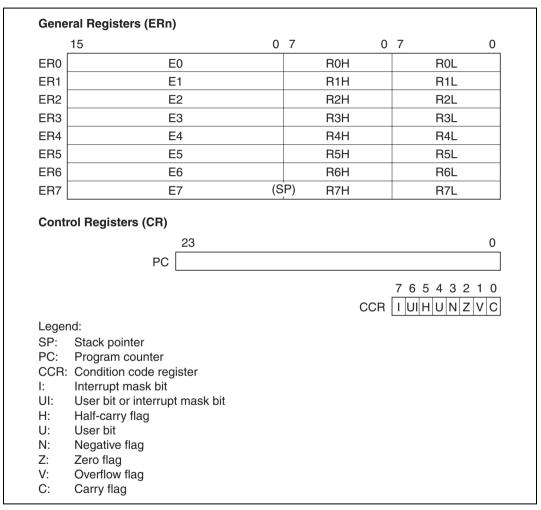

The H8/300H CPU has the internal registers shown in figure 2.3. There are two types of registers: general registers and control registers.

|       |   | Function                                                                                                                                          |

|-------|---|---------------------------------------------------------------------------------------------------------------------------------------------------|

| BOR   | В | $C \lor ( of ) \to C$                                                                                                                             |

|       |   | ORs the carry flag with a specified bit in a general register or memory operand and stores the result in the carry flag.                          |

|       |   | The bit number is specified by 3-bit immediate data.                                                                                              |

| BIOR  | В | $C \lor [\neg ( of )] \to C$                                                                                                                      |

|       |   | ORs the carry flag with the inverse of a specified bit in a general register or memory operand and stores the result in the carry flag.           |

|       |   | The bit number is specified by 3-bit immediate data.                                                                                              |

| BXOR  | В | $C \oplus (<\!bit-\!No.\!> of <\!EAd\!>) \to C$                                                                                                   |

|       |   | Exclusive-ORs the carry flag with a specified bit in a general register or<br>memory operand and stores the result in the carry flag.             |

|       |   | The bit number is specified by 3-bit immediate data.                                                                                              |

| BIXOR | В | $C \oplus [\neg (<\!bit-No.\!> of <\!EAd\!>)] \to C$                                                                                              |

|       |   | Exclusive-ORs the carry flag with the inverse of a specified bit in a general register or memory operand and stores the result in the carry flag. |

|       |   | The bit number is specified by 3-bit immediate data.                                                                                              |

| BLD   | В | $(\text{stit-No.} \text{ of } \text{}) \rightarrow C$                                                                                             |

|       |   | Transfers a specified bit in a general register or memory operand to the carry flag.                                                              |

|       |   | The bit number is specified by 3-bit immediate data.                                                                                              |

| BILD  | В | $\neg$ ( <bit-no.> of <ead>) <math>\rightarrow</math> C</ead></bit-no.>                                                                           |

|       |   | Transfers the inverse of a specified bit in a general register or memory operand to the carry flag.                                               |

|       |   | The bit number is specified by 3-bit immediate data.                                                                                              |

| BST   | В | $C \rightarrow (\text{ of })$                                                                                                                     |

|       |   | Transfers the carry flag value to a specified bit in a general register or memory operand.                                                        |

|       |   | The bit number is specified by 3-bit immediate data.                                                                                              |

| BIST  | В | $C \rightarrow \neg$ ( <bit-no.> of <ead>)</ead></bit-no.>                                                                                        |

|       |   | Transfers the inverse of the carry flag value to a specified bit in a general register or memory operand.                                         |

|       |   | The bit number is specified by 3-bit immediate data.                                                                                              |

Figure 2.17 Access Cycle for On-Chip Supporting Modules

Figure 2.18 Pin States during Access to On-Chip Supporting Modules

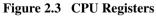

#### 2.9.4 Access to External Address Space

The external address space is divided into eight areas (areas 0 to 7). Bus-controller settings determine whether each area is accessed via an 8-bit or 16-bit data bus, and whether it is accessed in two or three states. For details see section 6, Bus Controller.

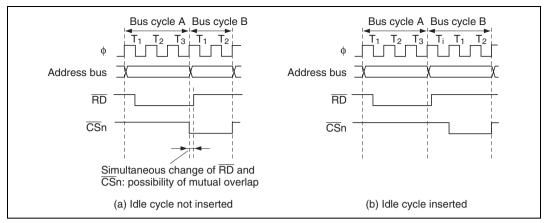

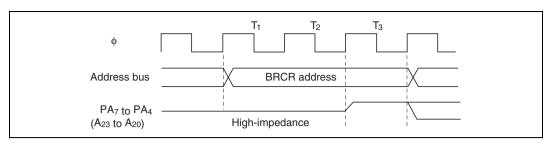

#### 6.5.2 Pin States in Idle Cycle

Table 6.5 shows the pin states in an idle cycle.

| Table 6.5 | Pin States in Idle Cycle |

|-----------|--------------------------|

|-----------|--------------------------|

| Pins                                                        | Pin State                |

|-------------------------------------------------------------|--------------------------|

| $A_{23}$ to $A_{0}$                                         | Next cycle address value |

| $\frac{A_{23} \text{ to } A_{0}}{D_{15} \text{ to } D_{0}}$ | High impedance           |

| CSn   AS                                                    | High                     |

|                                                             | High                     |

| RD                                                          | High                     |

| HWR                                                         | High                     |

| LWR                                                         | High                     |

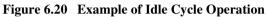

Figure 6.24 BRCR Write Timing

### 6.7.2 **BREQ** Pin Input Timing

After driving the  $\overline{BREQ}$  pin low, hold it low until  $\overline{BACK}$  goes low. If  $\overline{BREQ}$  returns to the high level before  $\overline{BACK}$  goes lows, the bus arbiter may operate incorrectly.

To terminate the external-bus-released state, hold the  $\overline{BREQ}$  signal high for at least three states. If  $\overline{BREQ}$  is high for too short an interval, the bus arbiter may operate incorrectly.

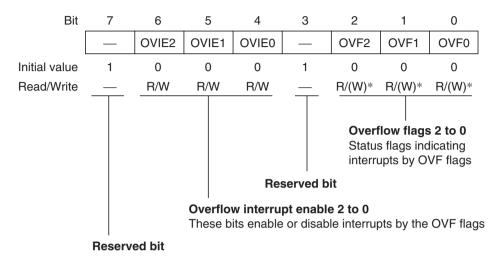

#### 8.2.6 Timer Interrupt Status Register C (TISRC)

TISRC is an 8-bit readable/writable register that indicates 16TCNT overflow or underflow and enables or disables overflow interrupt requests.

TISRC is initialized to H'88 by a reset and in standby mode.

Bit 7—Reserved: This bit cannot be modified and is always read as 1.

**Bit 6—Overflow Interrupt Enable 2 (OVIE2):** Enables or disables the interrupt requested by the OVF2 when OVF2 flag is set to 1.

| Bit 6<br>OVIE2 | Description                                       |                 |

|----------------|---------------------------------------------------|-----------------|

| 0              | OVI2 interrupt requested by OVF2 flag is disabled | (Initial value) |

| 1              | OVI2 interrupt requested by OVF2 flag is enabled  |                 |

### Renesas

# 8.3 CPU Interface

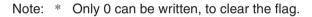

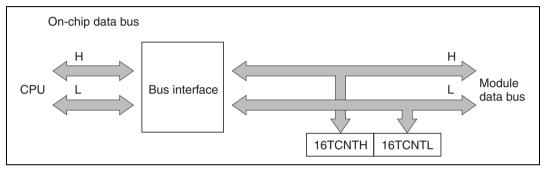

### 8.3.1 16-Bit Accessible Registers

The timer counters (16TCNTs), general registers A and B (GRAs and GRBs) are 16-bit registers, and are linked to the CPU by an internal 16-bit data bus. These registers can be written or read a word at a time, or a byte at a time.

Figures 8.4 and 8.5 show examples of word read/write access to a timer counter (16TCNT). Figures 8.6 to 8.9 show examples of byte read/write access to 16TCNTH and 16TCNTL.

Figure 8.4 16TCNT Access Operation [CPU → 16TCNT (Word)]

Figure 8.5 Access to Timer Counter (CPU Reads 16TCNT, Word)

### 9.2 **Register Descriptions**

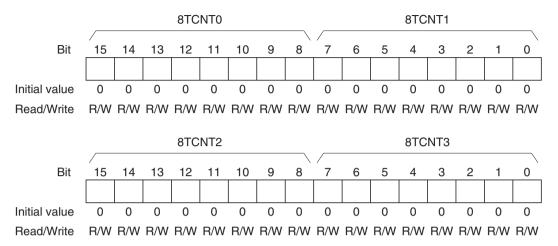

#### 9.2.1 Timer Counters (8TCNT)

The timer counters (8TCNT) are 8-bit readable/writable up-counters that increment on pulses generated from an internal or external clock source. The clock source is selected by clock select bits 2 to 0 (CKS2 to CKS0) in the timer control register (8TCR). The CPU can always read or write to the timer counters.

The 8TCNT0 and 8TCNT1 pair, and the 8TCNT2 and 8TCNT3 pair, can each be accessed as a 16-bit register by word access.

8TCNT can be cleared by an input capture signal or compare match signal. Counter clear bits 1 and 0 (CCLR1 and CCLR0) in 8TCR select the method of clearing.

When 8TCNT overflows from H'FF to H'00, the overflow flag (OVF) in the timer control/status register (8TCSR) is set to 1.

Each 8TCNT is initialized to H'00 by a reset and in standby mode.

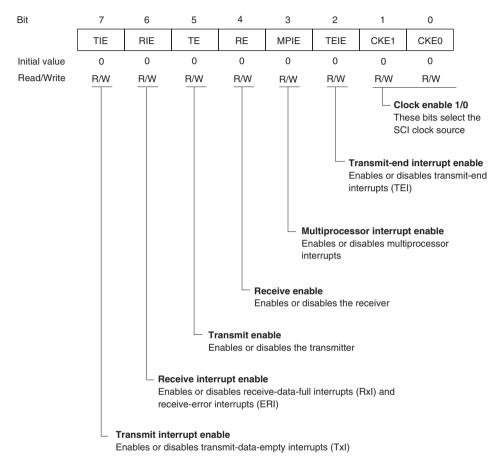

#### 12.2.6 Serial Control Register (SCR)

SCR register enables or disables the SCI transmitter and receiver, enables or disables serial clock output in asynchronous mode, enables or disables interrupts, and selects the transmit/receive clock source.

The CPU can always read and write SCR. SCR is initialized to H'00 by a reset and in standby mode.

# 13.4 Usage Notes

The following points should be noted when using the SCI as a smart card interface.

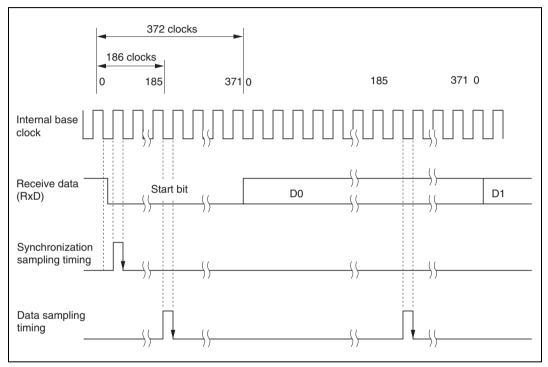

**Receive Data Sampling Timing and Receive Margin in Smart Card Interface Mode:** In smart card interface mode, the SCI operates on a base clock with a frequency of 372 times the transfer rate. In reception, the SCI synchronizes internally with the fall of the start bit, which it samples on the base clock. Receive data is latched at the rising edge of the 186th base clock pulse. The timing is shown in figure 13.11.

Figure 13.11 Receive Data Sampling Timing in Smart Card Interface Mode

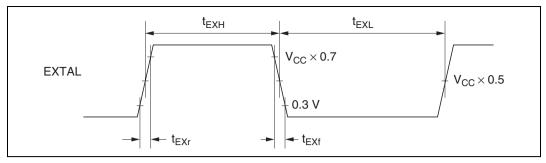

Figure 17.6 External Clock Input Timing

Figure 17.7 External Clock Output Settling Delay Timing

# Appendix A Instruction Set

# A.1 Instruction List

#### **Operand Notation**

| Symbol        | Description                                                                                                                           |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Rd            | General destination register                                                                                                          |

| Rs            | General source register                                                                                                               |

| Rn            | General register                                                                                                                      |

| ERd           | General destination register (address register or 32-bit register)                                                                    |

| ERs           | General source register (address register or 32-bit register)                                                                         |

| ERn           | General register (32-bit register)                                                                                                    |

| (EAd)         | Destination operand                                                                                                                   |

| (EAs)         | Source operand                                                                                                                        |

| PC            | Program counter                                                                                                                       |

| SP            | Stack pointer                                                                                                                         |

| CCR           | Condition code register                                                                                                               |

| N             | N (negative) flag in CCR                                                                                                              |

| Z             | Z (zero) flag in CCR                                                                                                                  |

| V             | V (overflow) flag in CCR                                                                                                              |

| С             | C (carry) flag in CCR                                                                                                                 |

| disp          | Displacement                                                                                                                          |

| $\rightarrow$ | Transfer from the operand on the left to the operand on the right, or transition from the state on the left to the state on the right |

| +             | Addition of the operands on both sides                                                                                                |

| _             | Subtraction of the operand on the right from the operand on the left                                                                  |

| ×             | Multiplication of the operands on both sides                                                                                          |

| ÷             | Division of the operand on the left by the operand on the right                                                                       |

| $\wedge$      | Logical AND of the operands on both sides                                                                                             |

| $\vee$        | Logical OR of the operands on both sides                                                                                              |

| $\oplus$      | Exclusive logical OR of the operands on both sides                                                                                    |

| 7             | NOT (logical complement)                                                                                                              |

| (), <>        | Contents of operand                                                                                                                   |

|               | neral registers include 8-bit registers (R0H to R7H and R0L to R7L) and 16-bit registers                                              |

(R0 to R7 and E0 to E7).

#### 7. System control instructions

|                          |              |     |   |      | essi<br>tion | -           |      |          |     | ) |                                                                                 |                |     |       |      |      |    | No<br>Stat |          |

|--------------------------|--------------|-----|---|------|--------------|-------------|------|----------|-----|---|---------------------------------------------------------------------------------|----------------|-----|-------|------|------|----|------------|----------|

|                          | Operand Size | ×   |   | @ERn | @(d, ERn)    | @-ERn/@ERn+ | la   | @(d, PC) | @aa |   | -                                                                               |                | Con | ditio | on C | Code | e  | Normal     | Advanced |

| Mnemonic                 | ő            | XX# | å | 0    | 0            | ø           | @ aa | 0        | ø   |   | Operation                                                                       | I              | н   | Ν     | z    | v    | С  | Ň          | Ad       |

| TRAPA #x:2               | -            |     |   |      |              |             |      |          |     | 2 | $PC \rightarrow @-SP$<br>$CCR \rightarrow @-SP$<br>$ \rightarrow PC$            | 1              |     |       |      |      |    | 14         | 16       |

| RTE                      | -            |     |   |      |              |             |      |          |     |   | $CCR \leftarrow @SP+$<br>$PC \leftarrow @SP+$                                   | \$             | \$  | \$    | \$   | \$   | \$ | 1          | 0        |

| SLEEP                    | -            |     |   |      |              |             |      |          |     |   | Transition to powerdown state                                                   | -              | -   | -     | -    | -    | -  | 2          | 2        |

| LDC #xx:8, CCR           | В            | 2   |   |      |              |             |      |          |     |   | $#xx:8 \rightarrow CCR$                                                         | €              | \$  | \$    | \$   | \$   | \$ | 2          | 2        |

| LDC Rs, CCR              | В            |     | 2 |      |              |             |      |          |     |   | $Rs8 \rightarrow CCR$                                                           | \$             | \$  | \$    | \$   | \$   | \$ | 2          | 2        |

| LDC @ERs, CCR            | w            |     |   | 4    |              |             |      |          |     |   | $@ERs\toCCR$                                                                    | \$             | \$  | \$    | \$   | \$   | \$ | 6          | 3        |

| LDC @(d:16, ERs),<br>CCR | W            |     |   |      | 6            |             |      |          |     |   | @(d:16, ERs) → CCR                                                              | \$             | \$  | \$    | \$   | \$   | \$ | 8          | 3        |

| LDC @(d:24, ERs),<br>CCR | W            |     |   |      | 10           |             |      |          |     |   | @(d:24, ERs) → CCR                                                              | \$             | \$  | \$    | \$   | \$   | \$ | 1          | 2        |

| LDC @ERs+, CCR           | W            |     |   |      |              | 4           |      |          |     |   | @ERs → CCR<br>ERs32+2 → ERs32                                                   | \$             | \$  | \$    | \$   | \$   | \$ | 8          | 3        |

| LDC @aa:16, CCR          | W            |     |   |      |              |             | 6    |          |     |   | @aa:16 → CCR                                                                    | \$             | \$  | \$    | \$   | \$   | \$ | 8          | 3        |

| LDC @aa:24, CCR          | w            |     |   |      |              |             | 8    |          |     |   | @aa:24 → CCR                                                                    | \$             | \$  | \$    | \$   | \$   | \$ | 1          | 0        |

| STC CCR, Rd              | В            |     | 2 |      |              |             |      |          |     |   | $CCR \rightarrow Rd8$                                                           |                | —   | _     |      | —    | _  | 2          | 2        |

| STC CCR, @ERd            | W            |     |   | 4    |              |             |      |          |     |   | $CCR \to @ERd$                                                                  | —              | —   | -     | _    | —    | -  | 6          | 3        |

| STC CCR, @(d:16,<br>ERd) | W            |     |   |      | 6            |             |      |          |     |   | $CCR \rightarrow @(d:16, ERd)$                                                  | -              | -   | -     | —    | -    | -  | 8          | 3        |

| STC CCR, @(d:24,<br>ERd) | W            |     |   |      | 10           |             |      |          |     |   | $CCR \rightarrow @(d:24, ERd)$                                                  | —              | —   | -     | —    | —    | -  | 1          | 2        |

| STC CCR, @-ERd           | w            |     |   |      |              | 4           |      |          |     |   | $\begin{array}{l} ERd32-2 \rightarrow ERd32\\ CCR \rightarrow @ERd \end{array}$ | _              | _   | _     | _    | _    | -  | 8          | 3        |

| STC CCR, @aa:16          | W            |     |   |      |              |             | 6    |          |     |   | $CCR \rightarrow @aa:16$                                                        |                | -   | -     | -    | -    | -  | 8          | }        |

| STC CCR, @aa:24          | w            |     |   |      |              |             | 8    |          |     |   | $CCR \rightarrow @aa:24$                                                        |                | -   | _     |      | -    | -  | 1          | 0        |

| ANDC #xx:8, CCR          | В            | 2   |   |      |              |             |      |          |     |   | $CCR \land \#xx:8 \rightarrow CCR$                                              | \$             | \$  | \$    | \$   | \$   | \$ | 2          | 2        |

| ORC #xx:8, CCR           | В            | 2   |   |      |              |             |      |          |     |   | $CCR \lor \#xx:8 \rightarrow CCR$                                               | $\updownarrow$ | \$  | \$    | \$   | \$   | \$ | 2          | 2        |

| XORC #xx:8, CCR          | В            | 2   |   |      |              |             |      |          |     |   | $CCR \oplus \#xx:8 \rightarrow CCR$                                             | \$             | \$  | \$    | \$   | \$   | \$ | 2          | 2        |

| NOP                      |              |     |   |      |              |             |      |          |     | 2 | $PC \gets PC+2$                                                                 | _              | _   | _     |      | _    | _  | 2          | 2        |

| Address | Register   | Data<br>Bus | Dit Nomeo  |        |                |                |                |                |       |       |                |  |

|---------|------------|-------------|------------|--------|----------------|----------------|----------------|----------------|-------|-------|----------------|--|

| (Low)   | Name       | Width       | Bit 7      | Bit 6  | Bit 5          | Bit 4          | Bit 3          | Bit 2          | Bit 1 | Bit 0 | Module Name    |  |

| H'EE020 | ABWCR      | 8           | ABW7       | ABW6   | ABW5           | ABW4           | ABW3           | ABW2           | ABW1  | ABW0  | Bus controller |  |

| H'EE021 | ASTCR      | 8           | AST7       | AST6   | AST5           | AST4           | AST3           | AST2           | AST1  | AST0  | _              |  |

| H'EE022 | WCRH       | 8           | W71        | W70    | W61            | W60            | W51            | W50            | W41   | W40   | _              |  |

| H'EE023 | WCRL       | 8           | W31        | W30    | W21            | W20            | W11            | W10            | W01   | W00   | _              |  |

| H'EE024 | BCR        | 8           | ICIS1      | ICIS0  | * <sup>1</sup> | * <sup>1</sup> | * <sup>1</sup> | * <sup>1</sup> | RDEA  | WAITE | _              |  |

| H'EE025 | _          |             | _          | _      |                | _              | _              | _              | _     | _     | _              |  |

| H'EE026 | Reserved a | area (aco   | cess prohi | bited) |                |                |                |                |       |       |                |  |

| H'EE027 |            |             |            |        |                |                |                |                |       |       |                |  |

| H'EE028 |            |             |            |        |                |                |                |                |       |       |                |  |

| H'EE029 |            |             |            |        |                |                |                |                |       |       |                |  |

| H'EE02A | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE02B | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE02C | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE02D | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE02E | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE02F | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE030 | Reserved a | area (aco   | cess prohi | bited) |                |                |                |                |       |       |                |  |

| H'EE031 | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE032 | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE033 | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE034 | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE035 | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE036 | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE037 |            |             |            |        |                |                |                |                |       |       |                |  |

| H'EE038 |            |             |            |        |                |                |                |                |       |       |                |  |

| H'EE039 |            |             |            |        |                |                |                |                |       |       |                |  |

| H'EE03A |            |             |            |        |                |                |                |                |       |       |                |  |

| H'EE03B |            |             |            |        |                |                |                |                |       |       |                |  |

| H'EE03C | -          |             |            |        |                |                |                |                |       |       |                |  |

| H'EE03D | -          |             |            |        |                |                |                |                |       |       |                |  |

| TELOOD  |            |             |            |        |                |                |                |                |       |       |                |  |

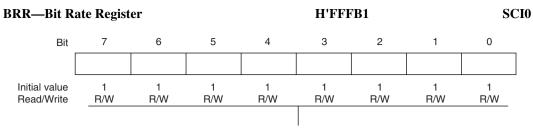

Serial communication bit rate setting

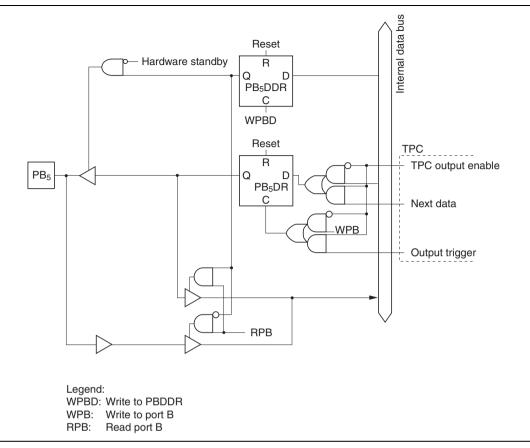

Figure C.7 (d) Port B Block Diagram (Pin PB<sub>5</sub>)

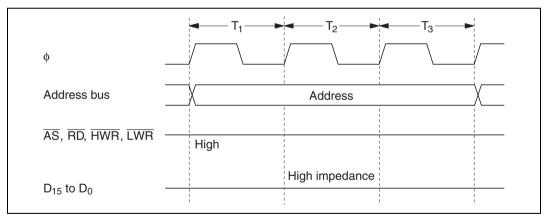

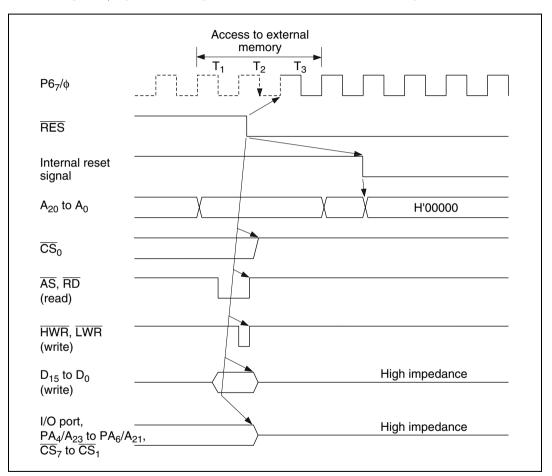

**Modes 3 and 4:** Figure D.2 is a timing diagram for the case in which  $\overline{\text{RES}}$  goes low during an external memory access in mode 3 or 4. As soon as  $\overline{\text{RES}}$  goes low, all ports are initialized to the input state.  $\overline{\text{AS}}$ ,  $\overline{\text{RD}}$ ,  $\overline{\text{HWR}}$ ,  $\overline{\text{LWR}}$ , and  $\overline{\text{CS}}_0$  go high, and  $D_{15}$  to  $D_0$  go to the high-impedance state. The address bus is initialized to the low output level 2.5  $\phi$  clock cycles after the low level of  $\overline{\text{RES}}$  is sampled. However, when PA<sub>4</sub> to PA<sub>6</sub> are used as address bus pins, or when P8<sub>3</sub> to P8<sub>1</sub> and PB<sub>0</sub> to PB<sub>3</sub> are used as CS output pins, they go to the high-impedance state at the same time as  $\overline{\text{RES}}$  goes low. Clock pin P6<sub>4</sub>/ $\phi$  goes to the output state at the next rise of  $\phi$  after  $\overline{\text{RES}}$  goes low.

Figure D.2 Reset during Memory Access (Modes 3 and 4)