Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 25MHz                                                                        |

| Connectivity               | SCI, SmartCard                                                               |

| Peripherals                | PWM, WDT                                                                     |

| Number of I/O              | 35                                                                           |

| Program Memory Size        | -                                                                            |

| Program Memory Type        | ROMIess                                                                      |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                    |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-BFQFP                                                                    |

| Supplier Device Package    | 100-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d13008vf25v |

|                            |                                                                              |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Appe | endix G  | Package Dimensions                                                  | 630 |

|------|----------|---------------------------------------------------------------------|-----|

| Appe | endix H  | Comparison of H8/300H Series Product Specifications                 | 632 |

|      |          | es between H8/3067 and H8/3062 Group, H8/3048 Group,                |     |

|      | H8/3006  | and H8/3007, and H8/3008                                            | 632 |

| H.2  | Comparis | on of Pin Functions of 100-Pin Package Products (FP-100B, TFP-100B) | 635 |

# Section 14 A/D Converter

| Table 14.1 | A/D Converter Pins                                            | 413 |

|------------|---------------------------------------------------------------|-----|

| Table 14.2 | A/D Converter Registers                                       | 414 |

| Table 14.3 | Analog Input Channels and A/D Data Registers (ADDRA to ADDRD) | 415 |

| Table 14.4 | A/D Conversion Time (Single Mode)                             | 426 |

| Table 14.5 | Analog Input Pin Ratings                                      | 429 |

# Section 15 D/A Converter

| Table 15.1 | D/A Converter Pins      | 437 |

|------------|-------------------------|-----|

| Table 15.2 | D/A Converter Registers | 437 |

# Section 16 RAM

| Table 16.1 | H8/3008 On-Chip RAM Specifications | 443 |

|------------|------------------------------------|-----|

| Table 16.2 | System Control Register            | 444 |

# Section 17 Clock Pulse Generator

| Table 17.1 (1) | Damping Resistance Value     | 449 |

|----------------|------------------------------|-----|

| Table 17.1 (2) | External Capacitance Values  | 450 |

| Table 17.2     | Crystal Resonator Parameters | 450 |

| Table 17.3     | Clock Timing (Preliminary)   | 452 |

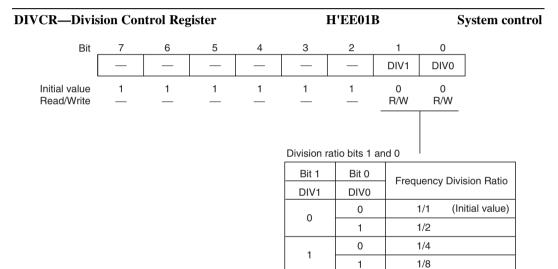

| Table 17.4     | Frequency Division Register  | 454 |

## Section 18 Power-Down State

| Table 18.1 | Power-Down State and Module Standby Function         | 458 |

|------------|------------------------------------------------------|-----|

| Table 18.2 | Control Register                                     | 459 |

| Table 18.3 | Clock Frequency and Waiting Time for Clock to Settle | 466 |

| Table 18.4 | $\phi$ Pin State in Various Operating States         | 470 |

## Section 19 Electrical Characteristics

| Table 19.1 | Absolute Maximum Ratings             | 471 |

|------------|--------------------------------------|-----|

| Table 19.2 | DC Characteristics (1)               | 472 |

| Table 19.2 | DC Characteristics (2)               | 475 |

| Table 19.3 | Permissible Output Currents          | 477 |

| Table 19.4 | Clock Timing                         | 479 |

| Table 19.5 | Control Signal Timing                | 480 |

| Table 19.6 | Bus Timing                           | 481 |

| Table 19.7 | Timing of On-Chip Supporting Modules | 483 |

| Table 19.8 | A/D Conversion Characteristics       | 485 |

| Table 19.9 | D/A Conversion Characteristics       | 487 |

# Table 2.4 Arithmetic Operation Instructions

| Instruction | Size* | Function                                                                                                                                                                                                                             |

|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD,SUB     | B/W/L | $Rd \pm Rs \rightarrow Rd,  Rd \pm \#IMM \rightarrow Rd$                                                                                                                                                                             |

|             |       | Performs addition or subtraction on data in two general registers, or on immediate data and data in a general register. (Immediate byte data cannot be subtracted from data in a general register. Use the SUBX or ADD instruction.) |

| ADDX,       | В     | $Rd \pm Rs \pm C \to Rd,  Rd \pm \#IMM \pm C \to Rd$                                                                                                                                                                                 |

| SUBX        |       | Performs addition or subtraction with carry or borrow on data in two general registers, or on immediate data and data in a general register.                                                                                         |

| INC,        | B/W/L | $Rd \pm 1 \rightarrow Rd,  Rd \pm 2 \rightarrow Rd$                                                                                                                                                                                  |

| DEC         |       | Increments or decrements a general register by 1 or 2. (Byte operands can be incremented or decremented by 1 only.)                                                                                                                  |

| ADDS,       | L     | $Rd \pm 1 \to Rd,  Rd \pm 2 \to Rd,  Rd \pm 4 \to Rd$                                                                                                                                                                                |

| SUBS        |       | Adds or subtracts the value 1, 2, or 4 to or from data in a 32-bit register.                                                                                                                                                         |

| DAA,        | В     | Rd decimal adjust $\rightarrow$ Rd                                                                                                                                                                                                   |

| DAS         |       | Decimal-adjusts an addition or subtraction result in a general register by referring to CCR to produce 4-bit BCD data.                                                                                                               |

| MULXU       | B/W   | $Rd \times Rs \to Rd$                                                                                                                                                                                                                |

|             |       | Performs unsigned multiplication on data in two general registers:<br>either 8 bits $\times$ 8 bits $\rightarrow$ 16 bits or 16 bits $\times$ 16 bits $\rightarrow$ 32 bits.                                                         |

| MULXS       | B/W   | $Rd \times Rs \rightarrow Rd$                                                                                                                                                                                                        |

|             |       | Performs signed multiplication on data in two general registers:<br>either 8 bits $\times$ 8 bits $\rightarrow$ 16 bits or 16 bits $\times$ 16 bits $\rightarrow$ 32 bits.                                                           |

#### . . ...... <u>.</u>... . ... ... -

| Bit           | 7      | 6       | 5      | 4      | 3      | 2                                                       | 1                      | 0                    |

|---------------|--------|---------|--------|--------|--------|---------------------------------------------------------|------------------------|----------------------|

|               |        |         | IRQ5F  | IRQ4F  | IRQ3F  | IRQ2F                                                   | IRQ1F                  | IRQ0F                |

| Initial value | 0      | 0       | 0      | 0      | 0      | 0                                                       | 0                      | 0                    |

| Read/Write    |        |         | R/(W)* | R/(W)* | R/(W)* | R/(W)*                                                  | R/(W)*                 | R/(W)*               |

|               | Reserv | ed bits |        |        |        | <b>RQ<sub>0</sub> flags</b><br>s indicate<br>equest sta | IRQ <sub>5</sub> to IF | ≀Q <sub>0</sub> flag |

ISR is initialized to H'00 by a reset and in hardware standby mode.

Bits 7 and 6—Reserved: These bits can not be modified and are always read as 0.

**Bits 5 to 0—IRQ**<sub>5</sub> **to IRQ**<sub>0</sub> **Flags (IRQ5F to IRQ0F):** These bits indicate the status of IRQ<sub>5</sub> to IRQ<sub>0</sub> interrupt requests.

| Bits 5 to 0    |             |

|----------------|-------------|

| IRQ5F to IRQ0F | Description |

| 0 | [Clearing conditions]<br>0 is written in IRQnF after reading the IRQnF flag when IRQnF = 1<br>IRQnSC = 0, IRQn input is high, and interrupt exception handling is<br>IRQnSC = 1 and IRQn interrupt exception handling is carried out. |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1 | [Setting conditions]<br>IRQnSC = 0 and $\overline{IRQn}$ input is low.<br>IRQnSC = 1 and $\overline{IRQn}$ input changes from high to low.                                                                                            |  |

Note: n = 5 to 0

#### 5.2.4 IRQ Enable Register (IER)

IER is an 8-bit readable/writable register that enables or disables IRQ<sub>5</sub> to IRQ<sub>0</sub> interrupt requests.

| Bit           | 7                                                                                                                                                      | 6   | 5     | 4     | 3     | 2     | 1     | 0     | _ |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|-------|-------|-------|-------|---|--|

|               |                                                                                                                                                        |     | IRQ5E | IRQ4E | IRQ3E | IRQ2E | IRQ1E | IRQ0E |   |  |

| Initial value | 0                                                                                                                                                      | 0   | 0     | 0     | 0     | 0     | 0     | 0     | - |  |

| Read/Write    | R/W                                                                                                                                                    | R/W | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |   |  |

|               | Reserved bits       IRQ <sub>5</sub> to IRQ <sub>0</sub> enable         These bits enable or disable IRQ <sub>5</sub> to IRQ <sub>0</sub> interruption |     |       |       |       |       |       |       |   |  |

IER is initialized to H'00 by a reset and in hardware standby mode.

# 5.4.3 Interrupt Response Time

Table 5.5 indicates the interrupt response time from the occurrence of an interrupt request until the first instruction of the interrupt service routine is executed.

#### Table 5.5 Interrupt Response Time

|      |                                                                 |                 |                 | Extern           | al Memory       |                       |

|------|-----------------------------------------------------------------|-----------------|-----------------|------------------|-----------------|-----------------------|

|      |                                                                 | On-Chip         | 8-1             | Bit Bus          | 16-             | Bit Bus               |

| No.  | Item                                                            | Memory          | 2 States        | 3 States         | 2 States        | 3 States              |

| 1    | Interrupt priority decision                                     | 2* <sup>1</sup> | 2* <sup>1</sup> | 2* <sup>1</sup>  | 2* <sup>1</sup> | 2* <sup>1</sup>       |

| 2    | Maximum number<br>of states until end of<br>current instruction | 1 to 23         | 1 to 27         | 1 to 31*4        | 1 to 23         | 1 to 25* <sup>4</sup> |

| 3    | Saving PC and CCR to stack                                      | 4               | 8               | 12* <sup>4</sup> | 4               | 6* <sup>4</sup>       |

| 4    | Vector fetch                                                    | 4               | 8               | 12* <sup>4</sup> | 4               | 6* <sup>4</sup>       |

| 5    | Instruction fetch* <sup>2</sup>                                 | 4               | 8               | 12* <sup>4</sup> | 4               | 6* <sup>4</sup>       |

| 6    | Internal processing*3                                           | 4               | 4               | 4                | 4               | 4                     |

| Tota |                                                                 | 19 to 41        | 31 to 57        | 43 to 73         | 19 to 41        | 25 to 49              |

Notes: 1. 1 state for internal interrupts.

2. Prefetch after the interrupt is accepted and prefetch of the first instruction in the interrupt service routine.

3. Internal processing after the interrupt is accepted and internal processing after vector fetch.

4. The number of states increases if wait states are inserted in external memory access.

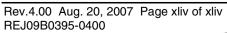

#### 6.2.7 Address Control Register (ADRCR)

ADRCR is an 8-bit readable/writable register that selects either address update mode 1 or address update mode 2 as the address output method.

ADRCR is initialized to H'FF by a reset and in hardware standby mode. It is not initialized in software standby mode.

Bits 7 to 1—Reserved: Read-only bits, always read as 1.

Bit 0—Address Control (ADRCTL): Selects the address output method.

| Bit 0<br>ADRCTL | Description                       |                 |

|-----------------|-----------------------------------|-----------------|

| 0               | Address update mode 2 is selected |                 |

| 1               | Address update mode 1 is selected | (Initial value) |

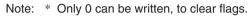

#### 6. Bus Controller

**16-Bit, Two-State-Access Areas:** Figures 6.14 to 6.16 show the timing of bus control signals for a 16-bit, two-state-access area. In these areas, the upper data bus ( $D_{15}$  to  $D_8$ ) is used in accesses to even addresses and the lower data bus ( $D_7$  to  $D_0$ ) in accesses to odd addresses. Wait states cannot be inserted.

Figure 6.14 Bus Control Signal Timing for 16-Bit, Two-State-Access Area (1) (Byte Access to Even Address)

# 7.7 Port A

# 7.7.1 Overview

Port A is an 8-bit input/output port that is also used for output ( $TP_7$  to  $TP_0$ ) from the programmable timing pattern controller (TPC), input and output (TIOCB<sub>2</sub>, TIOCA<sub>2</sub>, TIOCB<sub>1</sub>, TIOCA<sub>1</sub>, TIOCB<sub>0</sub>, TIOCA<sub>0</sub>, TCLKD, TCLKC, TCLKB, TCLKA) by the 16-bit timer, clock input (TCLKD, TCLKC, TCLKB, TCLKB, TCLKA) to the 8-bit timer, and address output ( $A_{23}$  to  $A_{20}$ ). A reset or hardware standby transition leaves port A as an input port, except that in modes 3 and 4, one pin is always used for  $A_{20}$  output. See tables 7.12 to 7.14 for the selection of pin functions.

Usage of pins for TPC, 16-bit timer, and 8-bit timer input and output is described in the sections on those modules. For output of address bits  $A_{23}$  to  $A_{20}$  in modes 3 and 4, see section 6.2.4, Bus Release Control Register (BRCR). Pins not assigned to any of these functions are available for generic input/output. Figure 7.6 shows the pin configuration of port A.

Pins in port A can drive one TTL load and a 30-pF capacitive load. They can also drive a darlington transistor pair. Port A has Schmitt-trigger inputs.

## Table 7.13 Port A Pin Functions (Modes 3 and 4)

# Pin Pin Functions and Selection Method A<sub>20</sub> Always used as A<sub>20</sub> output. Pin function A<sub>20</sub> output

| PA <sub>6</sub> /TP <sub>6</sub> /<br>TIOCA <sub>2</sub> /A <sub>21</sub> |                                                 | Bit PWM2 in TMDR, bits IOA2 to IOA0 in TIOR2, bit NDER6 in NDERA, bit A21E in BRCR, and bit PA <sub>6</sub> DDR select the pin function as follows. |                           |            |     |                           |                           |  |  |

|---------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------|-----|---------------------------|---------------------------|--|--|

|                                                                           | A21E                                            |                                                                                                                                                     | 1                         |            |     |                           | 0                         |  |  |

|                                                                           | 16-bit timer<br>channel 2 settings              | (1) in table below                                                                                                                                  | (2) in table below        |            |     |                           |                           |  |  |

|                                                                           | PA₀DDR                                          |                                                                                                                                                     | 0                         | 1          |     | 1                         |                           |  |  |

|                                                                           | NDER6                                           |                                                                                                                                                     |                           | 0          |     | 1                         |                           |  |  |

|                                                                           | Pin function                                    | TIOCA <sub>2</sub> output                                                                                                                           | PA <sub>6</sub><br>input  | PA<br>outp | 0   | TP <sub>6</sub><br>output | A <sub>21</sub><br>output |  |  |

|                                                                           |                                                 |                                                                                                                                                     | TIOCA <sub>2</sub> input* |            |     |                           |                           |  |  |

|                                                                           | Note: * TIOCA <sub>2</sub> input when IOA2 = 1. |                                                                                                                                                     |                           |            |     |                           |                           |  |  |

|                                                                           | 16-bit timer channe                             | (2) (1) (2                                                                                                                                          |                           | (2)        | (1) |                           |                           |  |  |

|                                                                           | PWM2                                            | 0                                                                                                                                                   |                           |            |     | 1                         |                           |  |  |

|                                                                           | IOA2                                            |                                                                                                                                                     | 0                         |            | 1   | —                         |                           |  |  |

|                                                                           | IOA1                                            | 0                                                                                                                                                   | 0                         | 1          | _   |                           |                           |  |  |

|                                                                           | IOA0                                            | 0                                                                                                                                                   | 1                         | _          |     | —                         |                           |  |  |

When bit PWM1 is set to 1 to select PWM mode, pin  $TIOCA_1$  becomes a PWM output pin. The output goes to 1 at compare match with GRA1, and to 0 at compare match with GRB1.

Bit 0—PWM Mode 0 (PWM0): Selects whether channel 0 operates normally or in PWM mode.

| Bit 0<br>PWM0 | Description                    |                 |

|---------------|--------------------------------|-----------------|

| 0             | Channel 0 operates normally    | (Initial value) |

| 1             | Channel 0 operates in PWM mode |                 |

When bit PWM0 is set to 1 to select PWM mode, pin  $TIOCA_0$  becomes a PWM output pin. The output goes to 1 at compare match with GRA0, and to 0 at compare match with GRB0.

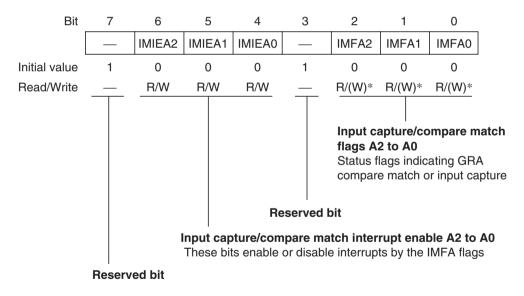

#### 8.2.4 Timer Interrupt Status Register A (TISRA)

TISRA is an 8-bit readable/writable register that indicates GRA compare match or input capture and enables or disables GRA compare match and input capture interrupt requests.

Note: \* Only 0 can be written, to clear the flag.

TISRA is initialized to H'88 by a reset and in standby mode.

Bit 7—Reserved: This bit cannot be modified and is always read as 1.

#### 10.2.6 Next Data Register B (NDRB)

NDRB is an 8-bit readable/writable register that stores the next output data for TPC output groups 3 and 2 (pins  $TP_{15}$  to  $TP_8$ ). During TPC output, when an 16-bit timer compare match event specified in TPCR occurs, NDRB contents are transferred to the corresponding bits in PBDR. The address of NDRB differs depending on whether TPC output groups 2 and 3 have the same output trigger or different output triggers.

NDRB is initialized to H'00 by a reset and in hardware standby mode. It is not initialized in software standby mode.

**Same Trigger for TPC Output Groups 2 and 3:** If TPC output groups 2 and 3 are triggered by the same compare match event, the NDRB address is H'FFFA4. The upper 4 bits belong to group 3 and the lower 4 bits to group 2. Address H'FFFA6 consists entirely of reserved bits that cannot be modified and always read 1.

#### Address H'FFFA4

| Bit            | 7                                                                 | 6           | 5         | 4       | 3     | 2           | 1         | 0       |

|----------------|-------------------------------------------------------------------|-------------|-----------|---------|-------|-------------|-----------|---------|

| Bit            |                                                                   | -           | -         | -       | -     |             |           | _       |

|                | NDR15                                                             | NDR14       | NDR13     | NDR12   | NDR11 | NDR10       | NDR9      | NDR8    |

| Initial value  | 0                                                                 | 0           | 0         | 0       | 0     | 0           | 0         | 0       |

| Read/Write     | R/W                                                               | R/W         | R/W       | R/W     | R/W   | R/W         | R/W       | R/W     |

|                |                                                                   |             |           |         |       |             |           |         |

|                |                                                                   | Next data   | 15 to 12  |         |       | Next data   | 11 to 8   |         |

|                | These bits store the next output These bits store the next output |             |           |         |       |             |           |         |

|                |                                                                   | data for TF | PC output | group 3 |       | data for TI | PC output | group 2 |

|                |                                                                   |             |           |         |       |             |           |         |

| Address H'FFFA | 46                                                                |             |           |         |       |             |           |         |

| Bit            | 7                                                                 | 6           | 5         | 4       | 0     | 0           | 4         | 0       |

| DIL            | /                                                                 | 0           | 5         | 4       | 3     | 2           | , I       | 0       |

|                | _                                                                 | —           | —         | _       | _     | _           | _         | _       |

| Initial value  | 1                                                                 | 1           | 1         | 1       | 1     | 1           | 1         | 1       |

| Read/Write     | _                                                                 | _           | _         | _       | _     |             |           | _       |

|                |                                                                   |             |           |         |       |             |           |         |

|                |                                                                   |             |           | Deeer   |       |             |           |         |

**Reserved bits**

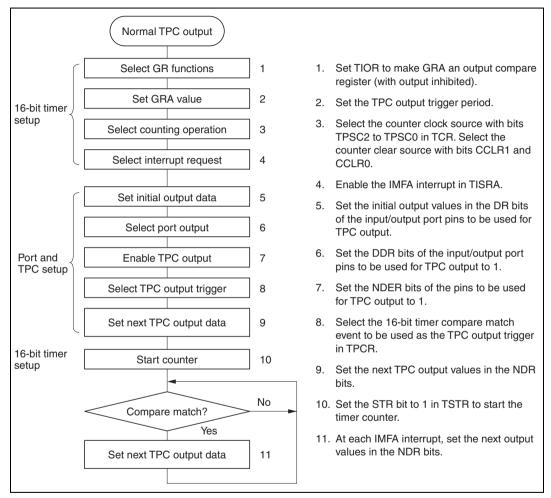

# 10.3.3 Normal TPC Output

**Sample Setup Procedure for Normal TPC Output:** Figure 10.4 shows a sample procedure for setting up normal TPC output.

Figure 10.4 Setup Procedure for Normal TPC Output (Example)

# 12.1.3 Pin Configuration

The SCI has serial pins for each channel as listed in table 12.1.

# Table 12.1 SCI Pins

| Channel | Name              | Abbreviation     | I/O          | Function                              |

|---------|-------------------|------------------|--------------|---------------------------------------|

| 0       | Serial clock pin  | SCK₀             | Input/output | SCI <sub>0</sub> clock input/output   |

|         | Receive data pin  | $RxD_{0}$        | Input        | $SCI_0$ receive data input            |

|         | Transmit data pin | TxD₀             | Output       | SCI <sub>0</sub> transmit data output |

| 1       | Serial clock pin  | SCK              | Input/output | SCI, clock input/output               |

|         | Receive data pin  | RxD <sub>1</sub> | Input        | SCI, receive data input               |

|         | Transmit data pin | TxD <sub>1</sub> | Output       | SCI, transmit data output             |

**Bits 2 to 0—Channel Select 2 to 0 (CH2 to CH0):** These bits and the SCAN bit select the analog input channels. Clear the ADST bit to 0 before changing the channel selection.

| Group<br>Selection | Cha | nnel Selection | Description              |                                    |  |  |  |

|--------------------|-----|----------------|--------------------------|------------------------------------|--|--|--|

| CH2                | CH1 | CH0            | Single Mode              | Scan Mode                          |  |  |  |

| 0                  | 0   | 0              | $AN_{o}$ (Initial value) | AN <sub>o</sub>                    |  |  |  |

|                    |     | 1              | AN <sub>1</sub>          | AN <sub>0</sub> , AN <sub>1</sub>  |  |  |  |

|                    | 1   | 0              | AN <sub>2</sub>          | AN <sub>0</sub> to AN <sub>2</sub> |  |  |  |

|                    |     | 1              | AN <sub>3</sub>          | AN <sub>0</sub> to AN <sub>3</sub> |  |  |  |

| 1                  | 0   | 0              | AN <sub>4</sub>          | AN <sub>4</sub>                    |  |  |  |

|                    |     | 1              | AN <sub>5</sub>          | AN <sub>4</sub> , AN <sub>5</sub>  |  |  |  |

|                    | 1   | 0              | AN <sub>6</sub>          | AN <sub>4</sub> to AN <sub>6</sub> |  |  |  |

|                    |     | 1              | AN <sub>7</sub>          | AN <sub>4</sub> to AN <sub>7</sub> |  |  |  |

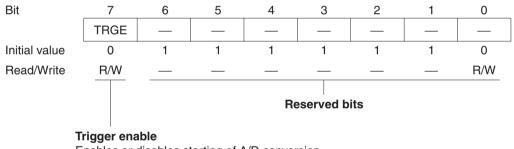

# 14.2.3 A/D Control Register (ADCR)

Enables or disables starting of A/D conversion by an external trigger or 8-bit timer compare match

ADCR is an 8-bit readable/writable register that enables or disables starting of A/D conversion by external trigger input or an 8-bit timer compare match signal. ADCR is initialized to H'7F by a reset and in standby mode.

# **19.4** A/D Conversion Characteristics

Table 19.8 lists the A/D conversion characteristics.

#### Table 19.8 A/D Conversion Characteristics

Condition:  $T_a = -20^{\circ}C$  to +75°C (regular specifications),  $T_a = -40^{\circ}C$  to +85°C (wide-range specifications)

Condition A:  $V_{cc} = 3.0$  to 3.6 V,  $AV_{cc} = 3.0$  to 3.6 V,  $V_{REF} = 3.0$  to  $AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0$  V, fmax = 25 MHz

- Condition B:  $V_{cc} = 5.0 \text{ V} \pm 10\%$ ,  $AV_{cc} = 5.0 \text{ V} \pm 10\%$ ,  $V_{REF} = 4.5 \text{ to } AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0 \text{ V}$ , fmax = 25 MHz

- Condition C:  $V_{cc} = 5.0 \text{ V} \pm 10\%$ ,  $AV_{cc} = 5.0 \text{ V} \pm 10\%$ ,  $V_{REF} = 4.5$  to  $AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0 \text{ V}$ , fmax = 25 MHz

|                     |                                                             |      |     | Cond | dition |       |      |      |

|---------------------|-------------------------------------------------------------|------|-----|------|--------|-------|------|------|

|                     |                                                             |      | Α   |      |        | B and | С    | -    |

| Item                |                                                             | Min  | Тур | Max  | Min    | Тур   | Max  | Unit |

| Conversion          | Resolution                                                  | 10   | 10  | 10   | 10     | 10    | 10   | bits |

| time: 134<br>states | Conversion time (single mode)                               | 5.36 |     | _    | 5.36   |       | —    | μS   |

| olaloo              | Analog input capacitance                                    |      | _   | 20   | _      | _     | 20   | pF   |

|                     | $\label{eq:permissible} Permissible  \varphi \leq 13 \ MHz$ | _    | _   | 10   | _      | _     | 10   | kΩ   |

|                     | signal-source $\phi > 13 \text{ MHz}$ impedance             | —    | —   | 5    | —      | —     | 5    | kΩ   |

|                     | Nonlinearity error                                          |      | _   | ±3.5 | _      | _     | ±3.5 | LSB  |

|                     | Offset error                                                |      | _   | ±3.5 |        | _     | ±3.5 | LSB  |

|                     | Full-scale error                                            |      |     | ±3.5 |        | —     | ±3.5 | LSB  |

|                     | Quantization error                                          |      |     | ±0.5 |        |       | ±0.5 | LSB  |

|                     | Absolute accuracy                                           | _    | _   | ±4.0 | _      | _     | ±4.0 | LSB  |

# P4PCR—Port 4 Input Pull-Up MOS Control Register H'EE03E

| Bit                         | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|-----------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

|                             | P47PCR   | P46PCR   | P4₅PCR   | P44PCR   | P43PCR   | P42PCR   | P41PCR   | P40PCR   |

| Initial value<br>Read/Write | 0<br>R/W |

|                             |          |          |          |          |          |          |          |          |

Port 4 input pull-up MOS control 7 to 0

| 0 | Input pull-up transistor is off |

|---|---------------------------------|

| 1 | Input pull-up transistor is on  |

Note: Valid when the corresponding P4DDR bit is cleared to 0 (designating generic input).

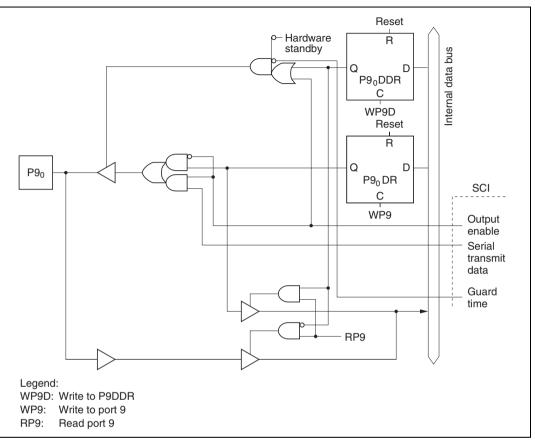

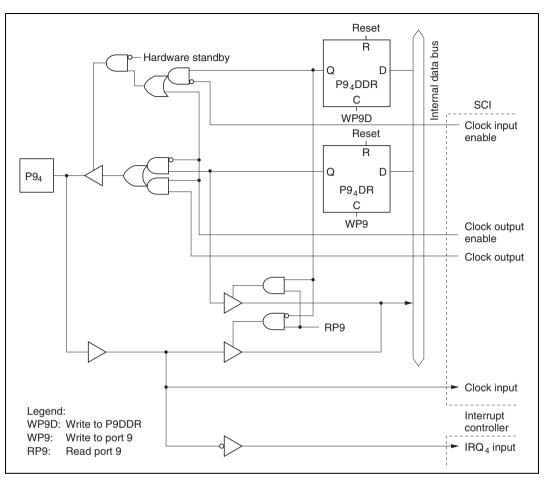

# C.5 Port 9 Block Diagrams

Figure C.5 (a) Port 9 Block Diagram (Pin P9<sub>0</sub>)

Figure C.5 (e) Port 9 Block Diagram (Pin P9<sub>4</sub>)