# Infineon Technologies - CY7C68013A-56BAXC Datasheet

Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

## Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are angineered to

### Details

$\mathbf{X}$ F

| Details                 |                                                                              |

|-------------------------|------------------------------------------------------------------------------|

| Product Status          | Active                                                                       |

| Applications            | USB Microcontroller                                                          |

| Core Processor          | 8051                                                                         |

| Program Memory Type     | ROMIess                                                                      |

| Controller Series       | CY7C680xx                                                                    |

| RAM Size                | 16K x 8                                                                      |

| Interface               | I <sup>2</sup> C, USB, USART                                                 |

| Number of I/O           | 24                                                                           |

| Voltage - Supply        | 3V ~ 3.6V                                                                    |

| Operating Temperature   | 0°C ~ 70°C                                                                   |

| Mounting Type           | Surface Mount                                                                |

| Package / Case          | 56-VFBGA                                                                     |

| Supplier Device Package | 56-VFBGA (5x5)                                                               |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy7c68013a-56baxc |

|                         |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the application note AN65209 - Getting Started with FX2LP.

- Overview: USB Portfolio, USB Roadmap

- USB 2.0 Product Selectors: FX2LP, AT2LP, NX2LP-Flex, SX2

- Application notes: Cypress offers a large number of USB application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with FX2LP are:

- AN65209 Getting Started with FX2LP

- □ AN15456 Guide to Successful EZ-USB<sup>®</sup> FX2LP<sup>™</sup> and EZ-USB FX1<sup>™</sup> Hardware Design and Debug

- □ AN50963 EZ-USB<sup>®</sup> FX1<sup>™</sup>/FX2LP<sup>™</sup> Boot Options

- □ AN66806 EZ-USB<sup>®</sup> FX2LP<sup>™</sup> GPIF Design Guide

- □ AN61345 Implementing an FX2LP<sup>TM</sup>- FPGA Interface

- □ AN57322 Interfacing SRAM with FX2LP over GPIF

- AN4053 Streaming Data through Isochronous/Bulk Endpoints on EZ-USB<sup>®</sup> FX2 and EZUSB FX2LP

- □ AN63787 EZ-USB<sup>®</sup> FX2LP<sup>™</sup> GPIF and Slave FIFO Configuration Examples using 8-bit Asynchronous Interface

For complete list of Application notes, click here.

- Code Examples: USB Hi-Speed

- Technical Reference Manual (TRM):

EZ-USB FX2LP Technical Reference Manual

- Reference Designs:

- CY4661 External USB Hard Disk Drives (HDD) with Fingerprint Authentication Security

- FX2LP DMB-T/H TV Dongle reference design

- Models: IBIS

### **EZ-USB FX2LP Development Kit**

The CY3684 EZ-USB FX2LP Development Kit is a complete development resource for FX2LP. It provides a platform to develop and test custom projects using FX2LP. The development kit contains collateral materials for the firmware, hardware, and software aspects of a design using FX2LP.

#### **GPIF™** Designer

FX2LP<sup>™</sup> General Programmable Interface (GPIF) provides an independent hardware unit, which creates the data and control signals required by an external interface. FX2LP GPIF Designer allows users to create and modify GPIF waveform descriptors for EZ-USB FX2/ FX2LP family of chips using a graphical user interface. Extensive discussion of general GPIF discussion and programming using GPIF Designer is included in *FX2LP Technical Reference Manual* and *GPIF Designer User Guide*, distributed with GPIF Designer. *AN66806* - *Getting Started with EZ-USB*<sup>®</sup> *FX2LP*<sup>™</sup> *GPIF* can be a good starting point.

#### Table 4. Individual FIFO/GPIF Interrupt Sources

| Priority | INT4VEC Value | Source   | Notes                                |  |  |  |

|----------|---------------|----------|--------------------------------------|--|--|--|

| 1        | 80            | EP2PF    | Endpoint 2 programmable flag         |  |  |  |

| 2        | 84            | EP4PF    | Endpoint 4 programmable flag         |  |  |  |

| 3        | 88            | EP6PF    | Endpoint 6 programmable flag         |  |  |  |

| 4        | 8C            | EP8PF    | Endpoint 8 programmable flag         |  |  |  |

| 5        | 90            | EP2EF    | Endpoint 2 empty flag <sup>[3]</sup> |  |  |  |

| 6        | 94            | EP4EF    | Endpoint 4 empty flag                |  |  |  |

| 7        | 98            | EP6EF    | Endpoint 6 empty flag                |  |  |  |

| 8        | 9C            | EP8EF    | Endpoint 8 empty flag                |  |  |  |

| 9        | A0            | EP2FF    | Endpoint 2 full flag                 |  |  |  |

| 10       | A4            | EP4FF    | Endpoint 4 full flag                 |  |  |  |

| 11       | A8            | EP6FF    | Endpoint 6 full flag                 |  |  |  |

| 12       | AC            | EP8FF    | Endpoint 8 full flag                 |  |  |  |

| 13       | B0            | GPIFDONE | GPIF operation complete              |  |  |  |

| 14       | B4            | GPIFWF   | GPIF waveform                        |  |  |  |

If Autovectoring is enabled (AV4EN = 1 in the INTSET-UP register), the FX 2LP substitutes its INT4VEC byte. Therefore, if the high byte ("page") of a jump-table address is preloaded at location 0x0054, the automatically inserted INT4VEC byte at 0x0055 directs the jump to the correct address out of the 14 addresses within the page. When the ISR occurs, the FX2LP pushes the program counter to its stack then jumps to address 0x0053, where it expects to find a "jump" instruction to the interrupt service routine (ISR).

Note

Errata: In Slave FIFO Asynchronous Word Wide mode, if a single word data is transferred from the USB host to EP2, configured as OUT Endpoint (EP) in the first transaction, then the Empty flag behaves incorrectly. This does not happen if the data size is more than one word in the first transaction. For more information, see the "Errata" on page 65.

# **Reset and Wakeup**

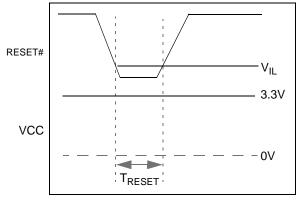

#### Reset Pin

The input pin, RESET#, resets the FX2LP when asserted. This pin has hysteresis and is active LOW. When a crystal is used with the CY7C680xxA, the reset period must enable stabilization of the crystal and the PLL. This reset period must be approximately 5 ms after VCC reaches 3.0 V. If the crystal input pin is driven by a clock signal, the internal PLL stabilizes in 200  $\mu$ s after VCC has reached 3.0 V<sup>[4]</sup>.

RESET# VCC VCC Power on Reset

#### Table 5. Reset Timing Values

| Condition                             | T <sub>RESET</sub>                 |  |  |  |  |

|---------------------------------------|------------------------------------|--|--|--|--|

| Power-on reset with crystal           | 5 ms                               |  |  |  |  |

| Power-on reset with external<br>clock | 200 $\mu$ s + clock stability time |  |  |  |  |

| Powered reset                         | 200 μs                             |  |  |  |  |

Figure 2 on page 9 shows a power-on reset condition and a reset applied during operation. A power-on reset is defined as the time reset that is asserted while power is being applied to the circuit. A powered reset is when the FX2LP is powered on and operating and the RESET# pin is asserted.

n is driven by after VCC has Cypress provides an application note which describes and recommends power-on reset implementation. For more information about reset implementation for the FX2 family of products, visit http://www.cypress.com. Figure 2. Reset Timing Plots

Powered Reset

#### Wakeup Pins

The 8051 puts itself and the rest of the chip into a power-down mode by setting PCON.0 = 1. This stops the oscillator and PLL. When WAKEUP is asserted by external logic, the oscillator restarts after the PLL stabilizes, and the 8051 receives a wakeup interrupt. This applies irrespective of whether FX2LP is connected to the USB.

The FX2LP exits the power-down (USB suspend) state by using one of the following methods:

- USB bus activity (if D+/D- lines are left floating, noise on these lines may indicate activity to the FX2LP and initiate a wakeup)

- External logic asserts the WAKEUP pin

- External logic asserts the PA3/WU2 pin

The second wakeup pin, WU2, can also be configured as a general-purpose I/O pin. This enables a simple external R-C network to be used as a periodic wakeup source. WAKEUP is by default active LOW.

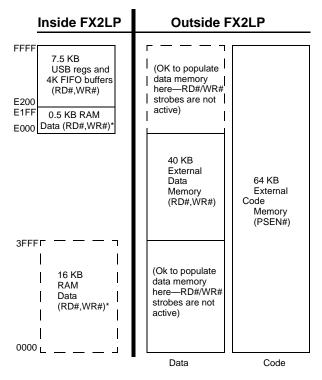

Figure 4. External Code Memory, EA = 1

# **Register Addresses**

| FFFF         |                                     |  |  |  |  |  |

|--------------|-------------------------------------|--|--|--|--|--|

|              | 4 KB EP2-EP8                        |  |  |  |  |  |

|              | buffers                             |  |  |  |  |  |

|              | (8 x 512)                           |  |  |  |  |  |

|              | (8 X 512)                           |  |  |  |  |  |

|              |                                     |  |  |  |  |  |

|              |                                     |  |  |  |  |  |

| F000<br>EFFF |                                     |  |  |  |  |  |

| FFFF         |                                     |  |  |  |  |  |

|              | 2 KB RESERVED                       |  |  |  |  |  |

| E800         |                                     |  |  |  |  |  |

| E7FF         |                                     |  |  |  |  |  |

| E7C0         | 64 BEP1IN                           |  |  |  |  |  |

| E7BF         |                                     |  |  |  |  |  |

| E780         | 64 Bytes EP1OUT                     |  |  |  |  |  |

| E77F         |                                     |  |  |  |  |  |

| E740         | 64 Bytes EP0 IN/OUT                 |  |  |  |  |  |

| E73F         |                                     |  |  |  |  |  |

| E700         | 64 Bytes RESERVED                   |  |  |  |  |  |

| E6FF         | 2051 Addresseeble Degisters         |  |  |  |  |  |

|              | 8051 Addressable Registers<br>(512) |  |  |  |  |  |

| E500         | (312)                               |  |  |  |  |  |

| E4FF         | <b>D</b>                            |  |  |  |  |  |

| E480         | Reserved (128)                      |  |  |  |  |  |

| E47F         |                                     |  |  |  |  |  |

| E400         | 128 Bytes GPIF Waveforms            |  |  |  |  |  |

| E3FF         | December 1 (540)                    |  |  |  |  |  |

| E200         | Reserved (512)                      |  |  |  |  |  |

| E1FF         |                                     |  |  |  |  |  |

|              | 512 Bytes                           |  |  |  |  |  |

|              | ,                                   |  |  |  |  |  |

| <b>F</b> 000 | 8051 xdata RAM                      |  |  |  |  |  |

| E000         |                                     |  |  |  |  |  |

In the Slave (S) mode, FX2LP accepts either an internally derived clock or externally supplied clock (IFCLK, max frequency 48 MHz) and SLCS#, SLRD, SLWR, SLOE, PKTEND signals from external logic. When using an external IFCLK, the external clock must be present before switching to the external clock with the IFCLKSRC bit. Each endpoint can individually be selected for byte or word operation by an internal configuration bit and a Slave FIFO Output Enable signal (SLOE) that enables data of the selected width. External logic must ensure that the output enable signal is inactive when writing data to a slave FIFO. The slave interface can also operate asynchronously, where the SLRD and SLWR signals act directly as strobes, rather than a clock qualifier as in synchronous mode. The signal SLCS#.

### GPIF and FIFO Clock Rates

An 8051 register bit selects one of two frequencies for the internally supplied interface clock: 30 MHz and 48 MHz. Alternatively, an externally supplied clock of 5 MHz–48 MHz feeding the IFCLK pin can be used as the interface clock. IFCLK can be configured to function as an output clock when the GPIF and FIFOs are internally clocked. An output enable bit in the IFCONFIG register turns this clock output off, if desired. Another bit within the IFCONFIG register inverts the IFCLK signal whether internally or externally sourced.

### GPIF

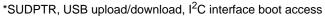

The GPIF is a flexible 8-bit or 16-bit parallel interface driven by a user-programmable finite state machine. It enables the CY7C68013A/15A to perform local bus mastering and can implement a wide variety of protocols such as ATA interface, printer parallel port, and Utopia.

The GPIF has six programmable control outputs (CTL), nine address outputs (GPIFADRx), and six general-purpose ready inputs (RDY). The data bus width can be 8 or 16 bits. Each GPIF vector defines the state of the control outputs, and determines what state a ready input (or multiple inputs) must be before proceeding. The GPIF vector can be programmed to advance a FIFO to the next data value, advance an address, etc. A sequence of the GPIF vectors make up a single waveform that is executed to perform the desired data move between the FX2LP and the external device.

#### Six Control OUT Signals

The 100-pin and 128-pin packages bring out all six Control Output pins (CTL0-CTL5). The 8051 programs the GPIF unit to define the CTL waveforms. The 56-pin package brings out three of these signals, CTL0–CTL2. CTLx waveform edges can be programmed to make transitions as fast as once per clock (20.8 ns using a 48-MHz clock).

#### Six Ready IN Signals

The 100-pin and 128-pin packages bring out all six Ready inputs (RDY0–RDY5). The 8051 programs the GPIF unit to test the RDY pins for GPIF branching. The 56-pin package brings out two of these signals, RDY0–1.

### Nine GPIF Address OUT Signals

Nine GPIF address lines are available in the 100-pin and 128-pin packages, GPIFADR[8..0]. The GPIF address lines enable indexing through up to a 512-byte block of RAM. If more address lines are needed, then I/O port pins are used.

#### Long Transfer Mode

In the master mode, the 8051 appropriately sets GPIF transaction count registers (GPIFTCB3, GPIFTCB2, GPIFTCB1, or GPIFTCB0) for unattended transfers of up to 2<sup>32</sup> transactions. The GPIF automatically throttles data flow to prevent under or overflow until the full number of requested transactions complete. The GPIF decrements the value in these registers to represent the current status of the transaction.

# ECC Generation<sup>[8]</sup>

The EZ-USB can calculate ECCs (Error Correcting Codes) on data that passes across its GPIF or Slave FIFO interfaces. There are two ECC configurations: Two ECCs, each calculated over 256 bytes (SmartMedia Standard); and one ECC calculated over 512 bytes.

The ECC can correct any one-bit error or detect any two-bit error.

ECC Implementation

The two ECC configurations are selected by the ECCM bit:

# ECCM = 0

Two 3-byte ECCs, each calculated over a 256-byte block of data. This configuration conforms to the SmartMedia Standard.

Write any value to ECCRESET, then pass data across the GPIF or Slave FIFO interface. The ECC for the first 256 bytes of data is calculated and stored in ECC1. The ECC for the next 256 bytes is stored in ECC2. After the second ECC is calculated, the values in the ECCx registers do not change until ECCRESET is written again, even if more data is subsequently passed across the interface.

# ECCM = 1

One 3-byte ECC calculated over a 512-byte block of data.

Write any value to ECCRESET then pass data across the GPIF or Slave FIFO interface. The ECC for the first 512 bytes of data is calculated and stored in ECC1; ECC2 is unused. After the ECC is calculated, the values in ECC1 do not change even if more data is subsequently passed across the interface, till ECCRESET is written again.

# **USB Uploads and Downloads**

The core has the ability to directly edit the data contents of the internal 16-KB RAM and of the internal 512-byte scratch pad RAM via a vendor-specific command. This capability is normally used when soft downloading the user code and is available only to and from the internal RAM, only when the 8051 is held in reset. The available RAM spaces are 16 KB from 0x0000–0x3FFF (code/data) and 512 bytes from 0xE000–0xE1FF (scratch pad data RAM)<sup>[9]</sup>.

#### Notes

8. To use the ECC logic, the GPIF or Slave FIFO interface must be configured for byte-wide operation.

<sup>9.</sup> After the data is downloaded from the host, a "loader" can execute from internal RAM to transfer downloaded data to external memory.

\* denotes programmable polarity

Table 11. FX2LP Pin Descriptions<sup>[11]</sup> (continued)

| 128<br>TQFP | 100<br>TQFP | 56<br>SSOP | 56<br>QFN | 56<br>VFBGA | Name                        | Туре  | Default    | Reset <sup>[12]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-------------|------------|-----------|-------------|-----------------------------|-------|------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 84          | 69          | 42         | 35        | 8F          | PA2 or<br>SLOE              | I/O/Z | I<br>(PA2) | Z<br>(PA2)            | Multiplexed pin whose function is selected by two<br>bits:<br>IFCONFIG[1:0].<br><b>PA2</b> is a bidirectional I/O port pin.<br><b>SLOE</b> is an input-only output enable with program-<br>mable polarity (FIFOPINPOLAR.4) for the slave<br>FIFOs connected to FD[70] or FD[150].                                                                                                                                                                                                                      |

| 85          | 70          | 43         | 36        | 7F          | PA3 or<br>WU2               | I/O/Z | l<br>(PA3) | Z<br>(PA3)            | Multiplexed pin whose function is selected by:<br>WAKEUP.7 and OEA.3<br><b>PA3</b> is a bidirectional I/O port pin.<br><b>WU2</b> is an alternate source for <b>USB Wakeup</b> ,<br>enabled by WU2EN bit (WAKEUP.1) and polarity<br>set by WU2POL (WAKEUP.4). If the 8051 is in<br>suspend and WU2EN = 1, a transition on this pin<br>starts up the oscillator and interrupts the 8051 to<br>enable it to exit the suspend mode. Asserting this<br>pin inhibits the chip from suspending if WU2EN = 1. |

| 89          | 71          | 44         | 37        | 6F          | PA4 or<br>FIFOADR0          | I/O/Z | l<br>(PA4) | Z<br>(PA4)            | Multiplexed pin whose function is selected by:<br>IFCONFIG[10].<br><b>PA4</b> is a bidirectional I/O port pin.<br><b>FIFOADR0</b> is an input-only address select for the<br>slave FIFOs connected to FD[70] or FD[150].                                                                                                                                                                                                                                                                               |

| 90          | 72          | 45         | 38        | 8C          | PA5 or<br>FIFOADR1          | I/O/Z | l<br>(PA5) | Z<br>(PA5)            | Multiplexed pin whose function is selected by:<br>IFCONFIG[10].<br><b>PA5</b> is a bidirectional I/O port pin.<br><b>FIFOADR1</b> is an input-only address select for the<br>slave FIFOs connected to FD[70] or FD[150].                                                                                                                                                                                                                                                                               |

| 91          | 73          | 46         | 39        | 7C          | PA6 or<br>PKTEND            | I/O/Z | l<br>(PA6) | Z<br>(PA6)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[1:0] bits.<br><b>PA6</b> is a bidirectional I/O port pin.<br><b>PKTEND</b> is an input used to commit the FIFO<br>packet data to the endpoint and whose polarity is<br>programmable via FIFOPINPOLAR.5.                                                                                                                                                                                                                                  |

| 92          | 74          | 47         | 40        | 6C          | PA7 or<br>FLAGD or<br>SLCS# | I/O/Z | l<br>(PA7) | Z<br>(PA7)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[1:0] and PORTACFG.7 bits.<br><b>PA7</b> is a bidirectional I/O port pin.<br><b>FLAGD</b> is a programmable slave-FIFO output<br>status flag signal.<br><b>SLCS#</b> gates all other slave FIFO enable/strobes                                                                                                                                                                                                                            |

| Port        | В           |            |           |             |                             |       |            |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 44          | 34          | 25         | 18        | ЗH          | PB0 or<br>FD[0]             | I/O/Z | І<br>(РВ0) | Z<br>(PB0)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB0</b> is a bidirectional I/O port pin.<br><b>FD[0]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                                                                                |

| 45          | 35          | 26         | 19        | 4F          | PB1 or<br>FD[1]             | I/O/Z | І<br>(РВ1) | Z<br>(PB1)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB1</b> is a bidirectional I/O port pin.<br><b>FD[1]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                                                                                |

| 46          | 36          | 27         | 20        | 4H          | PB2 or<br>FD[2]             | I/O/Z | l<br>(PB2) | Z<br>(PB2)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB2</b> is a bidirectional I/O port pin.<br><b>FD[2]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                                                                                |

Table 11. FX2LP Pin Descriptions<sup>[11]</sup> (continued)

| 128<br>TQFP | 100<br>TQFP | 56<br>SSOP | 56<br>QFN | 56<br>VFBGA | Name               | Туре  | Default    | Reset <sup>[12]</sup> | Description                                                                                                                                                                             |

|-------------|-------------|------------|-----------|-------------|--------------------|-------|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47          | 37          | 28         | 21        | 4G          | PB3 or<br>FD[3]    | I/O/Z | І<br>(РВЗ) | Z<br>(PB3)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB3</b> is a bidirectional I/O port pin.<br><b>FD[3]</b> is the bidirectional FIFO/GPIF data bus. |

| 54          | 44          | 29         | 22        | 5H          | PB4 or<br>FD[4]    | I/O/Z | І<br>(РВ4) | Z<br>(PB4)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB4</b> is a bidirectional I/O port pin.<br><b>FD[4]</b> is the bidirectional FIFO/GPIF data bus. |

| 55          | 45          | 30         | 23        | 5G          | PB5 or<br>FD[5]    | I/O/Z | l<br>(PB5) | Z<br>(PB5)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB5</b> is a bidirectional I/O port pin.<br><b>FD[5]</b> is the bidirectional FIFO/GPIF data bus. |

| 56          | 46          | 31         | 24        | 5F          | PB6 or<br>FD[6]    | I/O/Z | І<br>(РВ6) | Z<br>(PB6)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB6</b> is a bidirectional I/O port pin.<br><b>FD[6]</b> is the bidirectional FIFO/GPIF data bus. |

| 57          | 47          | 32         | 25        | 6H          | PB7 or<br>FD[7]    | I/O/Z | І<br>(РВ7) | Z<br>(PB7)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB7</b> is a bidirectional I/O port pin.<br><b>FD[7]</b> is the bidirectional FIFO/GPIF data bus. |

| POR         | ГС          |            |           |             |                    |       |            |                       |                                                                                                                                                                                         |

| 72          | 57          | _          | _         | -           | PC0 or<br>GPIFADR0 | I/O/Z | l<br>(PC0) | Z<br>(PC0)            | Multiplexed pin whose function is selected by<br>PORTCCFG.0<br><b>PC0</b> is a bidirectional I/O port pin.<br><b>GPIFADR0</b> is a GPIF address output pin.                             |

| 73          | 58          | _          | _         | _           | PC1 or<br>GPIFADR1 | I/O/Z | l<br>(PC1) | Z<br>(PC1)            | Multiplexed pin whose function is selected by<br>PORTCCFG.1<br><b>PC1</b> is a bidirectional I/O port pin.<br><b>GPIFADR1</b> is a GPIF address output pin.                             |

| 74          | 59          | -          | Ι         | -           | PC2 or<br>GPIFADR2 | I/O/Z | l<br>(PC2) | Z<br>(PC2)            | Multiplexed pin whose function is selected by<br>PORTCCFG.2<br><b>PC2</b> is a bidirectional I/O port pin.<br><b>GPIFADR2</b> is a GPIF address output pin.                             |

| 75          | 60          | -          | Ι         | _           | PC3 or<br>GPIFADR3 | I/O/Z | l<br>(PC3) | Z<br>(PC3)            | Multiplexed pin whose function is selected by<br>PORTCCFG.3<br><b>PC3</b> is a bidirectional I/O port pin.<br><b>GPIFADR3</b> is a GPIF address output pin.                             |

| 76          | 61          | Ι          | Ι         | Ι           | PC4 or<br>GPIFADR4 | I/O/Z | l<br>(PC4) | Z<br>(PC4)            | Multiplexed pin whose function is selected by<br>PORTCCFG.4<br><b>PC4</b> is a bidirectional I/O port pin.<br><b>GPIFADR4</b> is a GPIF address output pin.                             |

| 77          | 62          | -          | _         | -           | PC5 or<br>GPIFADR5 | I/O/Z | l<br>(PC5) | Z<br>(PC5)            | Multiplexed pin whose function is selected by<br>PORTCCFG.5<br><b>PC5</b> is a bidirectional I/O port pin.<br><b>GPIFADR5</b> is a GPIF address output pin.                             |

| 78          | 63          | _          | _         | _           | PC6 or<br>GPIFADR6 | I/O/Z | l<br>(PC6) | Z<br>(PC6)            | Multiplexed pin whose function is selected by<br>PORTCCFG.6<br><b>PC6</b> is a bidirectional I/O port pin.<br><b>GPIFADR6</b> is a GPIF address output pin.                             |

| 79          | 64          | _          | _         | _           | PC7 or<br>GPIFADR7 | I/O/Z | l<br>(PC7) | Z<br>(PC7)            | Multiplexed pin whose function is selected by<br>PORTCCFG.7<br><b>PC7</b> is a bidirectional I/O port pin.<br><b>GPIFADR7</b> is a GPIF address output pin.                             |

| 128<br>TQFP | 100<br>TQFP | 56<br>SSOP | 56<br>QFN | 56<br>VFBGA | Name | Туре   | Default | Reset <sup>[12]</sup> | Description                             |

|-------------|-------------|------------|-----------|-------------|------|--------|---------|-----------------------|-----------------------------------------|

| 100         | 78          | 50         | 43        | 5B          | VCC  | Power  | N/A     | N/A                   | VCC. Connect to the 3.3-V power source. |

| 107         | 85          | -          | _         | -           | VCC  | Power  | N/A     | N/A                   | VCC. Connect to the 3.3-V power source. |

|             |             |            |           |             |      |        |         |                       |                                         |

| 3           | 2           | 7          | 56        | 4B          | GND  | Ground | N/A     | N/A                   | Ground                                  |

| 27          | 21          | 19         | 12        | 1H          | GND  | Ground | N/A     | N/A                   | Ground                                  |

| 49          | 39          | -          | _         | _           | GND  | Ground | N/A     | N/A                   | Ground                                  |

| 58          | 48          | 33         | 26        | 7D          | GND  | Ground | N/A     | N/A                   | Ground                                  |

| 65          | 50          | 35         | 28        | 8D          | GND  | Ground | N/A     | N/A                   | Ground                                  |

| 80          | 65          | -          | _         | _           | GND  | Ground | N/A     | N/A                   | Ground                                  |

| 93          | 75          | 48         | 41        | 4C          | GND  | Ground | N/A     | N/A                   | Ground                                  |

| 116         | 94          | -          | -         | -           | GND  | Ground | N/A     | N/A                   | Ground                                  |

| 125         | 99          | 4          | 53        | 4A          | GND  | Ground | N/A     | N/A                   | Ground                                  |

|             |             |            |           |             | •    |        |         |                       |                                         |

| 14          | 13          | -          | _         | -           | NC   | N/A    | N/A     | N/A                   | No Connect. This pin must be left open. |

| 15          | 14          | -          | -         | -           | NC   | N/A    | N/A     | N/A                   | No Connect. This pin must be left open. |

| 16          | 15          | -          | -         | _           | NC   | N/A    | N/A     | N/A                   | No Connect. This pin must be left open. |

# Table 11. FX2LP Pin Descriptions<sup>[11]</sup> (continued)

# Table 12. FX2LP Register Summary (continued)

|              |        | -                          |                                                                   |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|--------------|--------|----------------------------|-------------------------------------------------------------------|--------------------|-----------------------|----------------------|----------------------|---------|-----------------|-----------------|--------------------|----------------------|----------|

| Hex          | Size   |                            | Description                                                       | b7                 | b6                    | b5                   | b4                   | b3      | b2              | b1              | b0                 | Default              | Access   |

| E6A0         | 1      | EP0CS                      | Endpoint 0 Control and Sta-<br>tus                                | HSNAK              | 0                     | 0                    | 0                    | 0       | 0               | BUSY            | STALL              | 10000000             | bbbbbbrb |

| E6A1         | 1      | EP1OUTCS                   | Endpoint 1 OUT Control<br>and Status                              | 0                  | 0                     | 0                    | 0                    | 0       | 0               | BUSY            | STALL              | 00000000             | bbbbbbrb |

| E6A2         | 1      | EP1INCS                    | Endpoint 1 IN Control and Status                                  | 0                  | 0                     | 0                    | 0                    | 0       | 0               | BUSY            | STALL              | 00000000             | bbbbbbrb |

| E6A3         | 1      | EP2CS                      | Endpoint 2 Control and Sta-<br>tus                                | 0                  | NPAK2                 | NPAK1                | NPAK0                | FULL    | EMPTY           | 0               | STALL              | 00101000             | rrrrrb   |

| E6A4         | 1      | EP4CS                      | Endpoint 4 Control and Sta-<br>tus                                | 0                  | 0                     | NPAK1                | NPAK0                | FULL    | EMPTY           | 0               | STALL              | 00101000             | rrrrrb   |

| E6A5         | 1      | EP6CS                      | Endpoint 6 Control and Sta-<br>tus                                | 0                  | NPAK2                 | NPAK1                | NPAK0                | FULL    | EMPTY           | 0               | STALL              | 00000100             | rrrrrb   |

| E6A6         | 1      | EP8CS                      | Endpoint 8 Control and Sta-<br>tus                                | 0                  | 0                     | NPAK1                | NPAK0                | FULL    | EMPTY           | 0               | STALL              | 00000100             | rrrrrb   |

| E6A7         | 1      | EP2FIFOFLGS                | Endpoint 2 slave FIFO<br>Flags                                    | 0                  | 0                     | 0                    | 0                    | 0       | PF              | EF              | FF                 | 00000010             | R        |

| E6A8         | 1      | EP4FIFOFLGS                | Endpoint 4 slave FIFO<br>Flags                                    | 0                  | 0                     | 0                    | 0                    | 0       | PF              | EF              | FF                 | 00000010             | R        |

| E6A9         | 1      | EP6FIFOFLGS                | Endpoint 6 slave FIFO<br>Flags                                    | 0                  | 0                     | 0                    | 0                    | 0       | PF              | EF              | FF                 | 00000110             | R        |

| E6AA         | 1      | EP8FIFOFLGS                | Endpoint 8 slave FIFO<br>Flags                                    | 0                  | 0                     | 0                    | 0                    | 0       | PF              | EF              | FF                 | 00000110             | R        |

| E6AB         | 1      | EP2FIFOBCH                 | Endpoint 2 slave FIFO<br>total byte count H                       | 0                  | 0                     | 0                    | BC12                 | BC11    | BC10            | BC9             | BC8                | 00000000             | R        |

| E6AC         | 1      | EP2FIFOBCL                 | Endpoint 2 slave FIFO                                             | BC7                | BC6                   | BC5                  | BC4                  | BC3     | BC2             | BC1             | BC0                | 00000000             | R        |

| E6AD         | 1      | EP4FIFOBCH                 | total byte count L<br>Endpoint 4 slave FIFO<br>total byte count H | 0                  | 0                     | 0                    | 0                    | 0       | BC10            | BC9             | BC8                | 00000000             | R        |

| E6AE         | 1      | EP4FIFOBCL                 | Endpoint 4 slave FIFO                                             | BC7                | BC6                   | BC5                  | BC4                  | BC3     | BC2             | BC1             | BC0                | 00000000             | R        |

| E6AF         | 1      | EP6FIFOBCH                 | total byte count L<br>Endpoint 6 slave FIFO<br>total byte count H | 0                  | 0                     | 0                    | 0                    | BC11    | BC10            | BC9             | BC8                | 00000000             | R        |

| E6B0         | 1      | EP6FIFOBCL                 | Endpoint 6 slave FIFO                                             | BC7                | BC6                   | BC5                  | BC4                  | BC3     | BC2             | BC1             | BC0                | 00000000             | R        |

| E6B1         | 1      | EP8FIFOBCH                 | total byte count L<br>Endpoint 8 slave FIFO                       | 0                  | 0                     | 0                    | 0                    | 0       | BC10            | BC9             | BC8                | 00000000             | R        |

| E6B2         | 1      | EP8FIFOBCL                 | total byte count H<br>Endpoint 8 slave FIFO                       | BC7                | BC6                   | BC5                  | BC4                  | BC3     | BC2             | BC1             | BC0                | 00000000             | R        |

| E6B3         | 1      | SUDPTRH                    | total byte count L<br>Setup Data Pointer high                     | A15                | A14                   | A13                  | A12                  | A11     | A10             | A9              | A8                 | xxxxxxx              | RW       |

| E6B4         | 1      | SUDPTRL                    | address byte<br>Setup Data Pointer low ad-                        | A7                 | A6                    | A5                   | A4                   | A3      | A2              | A1              | 0                  | xxxxxx0              | bbbbbbbr |

| E6B5         | 1      | SUDPTRCTL                  | dress byte<br>Setup Data Pointer Auto                             | 0                  | 0                     | 0                    | 0                    | 0       | 0               | 0               | SDPAUTO            | 00000001             | RW       |

|              |        |                            | Mode                                                              |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

| E6B8         | 2      | reserved<br>SET-UPDAT      | 8 bytes of setup data                                             | D7                 | D6                    | D5                   | D4                   | D3      | D2              | D1              | D0                 | xxxxxxxx             | R        |

| EODO         | 0      | SET-OFDAT                  | SET-UPDAT[0] =                                                    | Di                 | 00                    | D5                   | D4                   | 03      | DZ              |                 | DU                 | ******               | ĸ        |

|              |        |                            | bmRequestType                                                     |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        |                            | SET-UPDAT[1] =<br>bmRequest                                       |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        |                            | SET-UPDAT[2:3] = wValue                                           |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        |                            | SET-UPDAT[4:5] = wIndex                                           |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        |                            | SET-UPDAT[6:7] =                                                  |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        |                            | wLength                                                           |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        | GPIF                       |                                                                   |                    |                       |                      |                      |         | FIFOLUDA        | 5150004         | 5150000            | 44400400             | 514/     |

| E6C0<br>E6C1 | 1<br>1 | GPIFWFSELECT<br>GPIFIDLECS | Waveform Selector<br>GPIF Done, GPIF IDLE                         | SINGLEWR1<br>DONE  | SINGLEWR0<br>0        | 0                    | SINGLERD0            | FIFOWR1 | FIFOWR0<br>0    | FIFORD1<br>0    | FIFORD0<br>IDLEDRV | 11100100<br>10000000 | RW<br>RW |

|              |        |                            | drive mode                                                        |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

| E6C2         | 1      | GPIFIDLECTL                | Inactive Bus, CTL states                                          | 0                  | 0                     | CTL5                 | CTL4                 | CTL3    | CTL2            | CTL1            | CTL0               | 11111111             |          |

| E6C3         | 1      | GPIFCTLCFG                 | CTL Drive Type                                                    | TRICTL             | 0                     | CTL5                 | CTL4                 | CTL3    | CTL2            | CTL1            | CTL0               | 00000000             |          |

| E6C4         | 1      | GPIFADRH <sup>[13]</sup>   | GPIF Address H                                                    | 0                  | 0                     | 0                    | 0                    | 0       | 0               | 0               | GPIFA8             | 00000000             |          |

| E6C5         | 1      |                            | GPIF Address L                                                    | GPIFA7             | GPIFA6                | GPIFA5               | GPIFA4               | GPIFA3  | GPIFA2          | GPIFA1          | GPIFA0             | 00000000             | RW       |

| E6C6         | 1      | FLOWSTATE<br>FLOWSTATE     | Flowstate Enable and                                              | FSE                | 0                     | 0                    | 0                    | 0       | FS2             | FS1             | FS0                | 00000000             | brrrrbbb |

| E6C7         | 1      | FLOWLOGIC                  | Selector<br>Flowstate Logic                                       | LFUNC1             | LFUNC0                | TERMA2               | TERMA1               | TERMA0  | TERMB2          | TERMB1          | TERMB0             | 00000000             | RW       |

| E6C8         | 1      | FLOWEQ0CTL                 | CTL-Pin States in<br>Flowstate                                    | CTL0E3             | CTL0E2                | CTL0E1/<br>CTL5      | CTL0E0/<br>CTL4      | CTL3    | CTL2            | CTL1            | CTL0               | 00000000             |          |

| E6C9         | 1      | FLOWEQ1CTL                 | (when Logic = 0)<br>CTL-Pin States in Flow-                       | CTL0E3             | CTL0E2                | CTL0E1/<br>CTL5      | CTLOE0/              | CTL3    | CTL2            | CTL1            | CTL0               | 00000000             | RW       |

| F            | 4      |                            | state (when Logic = 1)                                            |                    |                       |                      | CTL4                 |         |                 |                 |                    | 00010010             | DW/      |

| E6CA<br>E6CB | 1      | FLOWHOLDOFF<br>FLOWSTB     | Holdoff Configuration<br>Flowstate Strobe                         | HOPERIOD3<br>SLAVE | HOPERIOD2<br>RDYASYNC | HOPERIOD1<br>CTLTOGL | HOPERIOD0<br>SUSTAIN |         | HOCTL2<br>MSTB2 | HOCTL1<br>MSTB1 | HOCTL0<br>MSTB0    | 00010010             |          |

| -000         | Ľ      |                            | Configuration                                                     |                    | ND ING ING            | SILIUGL              | SUCIAIN              | 3       |                 |                 |                    | 00000                |          |

| E6CC         |        | FLOWSTBEDGE                | Flowstate Rising/Falling<br>Edge Configuration                    | 0                  | 0                     | 0                    | 0                    | 0       | 0               | FALLING         | RISING             | 00000001             | rrrrrbb  |

| E6CD         |        | FLOWSTBPERIOD              | Master-Strobe Half-Period                                         |                    | D6                    | D5                   | D4                   | D3      | D2              | D1              | D0                 | 00000010             |          |

| E6CE         | 1      | GPIFTCB3 <sup>[13]</sup>   | GPIF Transaction Count<br>Byte 3                                  | TC31               | TC30                  | TC29                 | TC28                 | TC27    | TC26            | TC25            | TC24               | 00000000             | RW       |

|              |        |                            | 5,10 5                                                            | 1                  |                       | 1                    | 1                    |         | 1               | 1               | 1                  | I                    | 1        |

# Table 12. FX2LP Register Summary (continued)

| Hex | Size | Name                                | Description                                       | b7    | b6    | b5    | b4    | b3    | b2    | b1                | b0    | Default  | Access |

|-----|------|-------------------------------------|---------------------------------------------------|-------|-------|-------|-------|-------|-------|-------------------|-------|----------|--------|

| BE  | 1    | GPIFSGLDATLX <sup>[15]</sup>        | GPIF Data L w/ Trigger                            | D7    | D6    | D5    | D4    | D3    | D2    | D1                | D0    | XXXXXXXX | RW     |

| BF  | 1    | GPIFSGLDATL-<br>NOX <sup>[15]</sup> | GPIF Data L w/ No Trigger                         | D7    | D6    | D5    | D4    | D3    | D2    | D1                | D0    | xxxxxxxx | R      |

| C0  | 1    | SCON1 <sup>[15]</sup>               | Serial Port 1 Control (bit addressable)           | SM0_1 | SM1_1 | SM2_1 | REN_1 | TB8_1 | RB8_1 | TI_1              | RI_1  | 0000000  | RW     |

| C1  | 1    | SBUF1 <sup>[15]</sup>               | Serial Port 1 Data Buffer                         | D7    | D6    | D5    | D4    | D3    | D2    | D1                | D0    | 00000000 | RW     |

| C2  | 6    | reserved                            |                                                   |       |       |       |       |       |       |                   |       |          |        |

| C8  | 1    | T2CON                               | Timer/Counter 2 Control<br>(bit addressable)      | TF2   | EXF2  | RCLK  | TCLK  | EXEN2 | TR2   | CT2               | CPRL2 | 00000000 | RW     |

| C9  | 1    | reserved                            |                                                   |       |       |       |       |       |       |                   |       |          |        |

| CA  | 1    | RCAP2L                              | Capture for Timer 2, au-<br>to-reload, up-counter | D7    | D6    | D5    | D4    | D3    | D2    | D1                | D0    | 00000000 | RW     |

| СВ  | 1    | RCAP2H                              | Capture for Timer 2, au-<br>to-reload, up-counter | D7    | D6    | D5    | D4    | D3    | D2    | D1                | D0    | 00000000 | RW     |

| CC  | 1    | TL2                                 | Timer 2 reload L                                  | D7    | D6    | D5    | D4    | D3    | D2    | D1                | D0    | 00000000 | RW     |

| CD  | 1    | TH2                                 | Timer 2 reload H                                  | D15   | D14   | D13   | D12   | D11   | D10   | D9                | D8    | 00000000 | RW     |

| CE  | 2    | reserved                            |                                                   |       |       |       |       |       |       |                   |       |          |        |

| D0  | 1    | PSW                                 | Program Status Word (bit addressable)             | CY    | AC    | F0    | RS1   | RS0   | OV    | F1                | Р     | 00000000 | RW     |

| D1  | 7    | reserved                            |                                                   |       |       |       |       |       |       |                   |       |          |        |

| D8  | 1    | EICON <sup>[15]</sup>               | External Interrupt Control                        | SMOD1 | 1     | ERESI | RESI  | INT6  | 0     | 0                 | 0     | 01000000 | RW     |

| D9  | 7    | reserved                            |                                                   |       |       |       |       |       |       |                   |       |          |        |

| E0  | 1    | ACC                                 | Accumulator (bit address-<br>able)                | D7    | D6    | D5    | D4    | D3    | D2    | D1                | D0    | 0000000  | RW     |

| E1  | 7    | reserved                            |                                                   |       |       |       |       |       |       |                   |       |          |        |

| E8  | 1    | EIE <sup>[15]</sup>                 | External Interrupt En-<br>able(s)                 | 1     | 1     | 1     | EX6   | EX5   | EX4   | EI <sup>2</sup> C | EUSB  | 11100000 | RW     |

| E9  | 7    | reserved                            |                                                   |       |       |       |       |       |       |                   |       |          |        |

| F0  | 1    | В                                   | B (bit addressable)                               | D7    | D6    | D5    | D4    | D3    | D2    | D1                | D0    | 00000000 | RW     |

| F1  | 7    | reserved                            |                                                   |       |       |       |       |       |       |                   |       |          |        |

| F8  | 1    | EIP <sup>[15]</sup>                 | External Interrupt Priority<br>Control            | 1     | 1     | 1     | PX6   | PX5   | PX4   | PI <sup>2</sup> C | PUSB  | 11100000 | RW     |

| F9  | 7    | reserved                            |                                                   |       |       |       |       |       |       | 1                 | 1     | 1        |        |

R = all bits read-only

W = all bits write-only

r = read-only bit

w = write-only bit b = both read/write bit

Document Number: 38-08032 Rev. \*Y

# Data Memory Read<sup>[21]</sup>

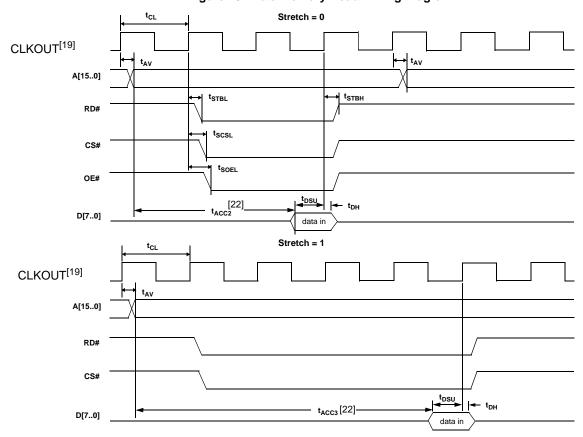

Figure 13. Data Memory Read Timing Diagram

#### Table 16. Data Memory Read Parameters

| Parameter         | Description                       | Min | Тур   | Max  | Unit | Notes  |

|-------------------|-----------------------------------|-----|-------|------|------|--------|

|                   |                                   | -   | 20.83 | -    | ns   | 48 MHz |

| t <sub>CL</sub>   | 1/CLKOUT frequency                | _   | 41.66 | -    | ns   | 24 MHz |

|                   |                                   | _   | 83.2  | -    | ns   | 12 MHz |

| t <sub>AV</sub>   | Delay from clock to valid address | -   | -     | 10.7 | ns   | -      |

| t <sub>STBL</sub> | Clock to RD LOW                   | -   | -     | 11   | ns   | -      |

| t <sub>STBH</sub> | Clock to RD HIGH                  | -   | -     | 11   | ns   | -      |

| t <sub>SCSL</sub> | Clock to CS LOW                   | -   | -     | 13   | ns   | -      |

| t <sub>SOEL</sub> | Clock to OE LOW                   | -   | -     | 11.1 | ns   | -      |

| t <sub>DSU</sub>  | Data setup to clock               | 9.6 | -     | -    | ns   | -      |

| t <sub>DH</sub>   | Data hold time                    | 0   | -     | -    | ns   | -      |

When using the AUTPOPTR1 or AUTOPTR2 to address external memory, the address of AUTOPTR1 is only active while either RD# or WR# is active. The address of AUTOPTR2 is active throughout the cycle and meets the address valid time for which is based on the stretch value.

Notes

21. The stretch memory cycle feature enables EZ-USB firmware to adjust the speed of data memory accesses not the program memory accesses. Details including typical strobe width timings can be found in the section 12.1.2 of the Technical Reference Manual. The address cycle width can be interpreted from these.

22.  $t_{ACC2}$  and  $t_{ACC3}$  are computed from these parameters as follows:  $t_{ACC2}(24 \text{ MHz}) = 3^* t_{CL} - t_{AV} - t_{DSU} = 106 \text{ ns}$   $t_{ACC2}(24 \text{ MHz}) = 3^* t_{CL} - t_{AV} - t_{DSU} = 43 \text{ ns}$   $t_{ACC3}(24 \text{ MHz}) = 5^* t_{CL} - t_{AV} - t_{DSU} = 190 \text{ ns}$   $t_{ACC3}(48 \text{ MHz}) = 5^* t_{CL} - t_{AV} - t_{DSU} = 86 \text{ ns}$

# Data Memory Write<sup>[23]</sup>

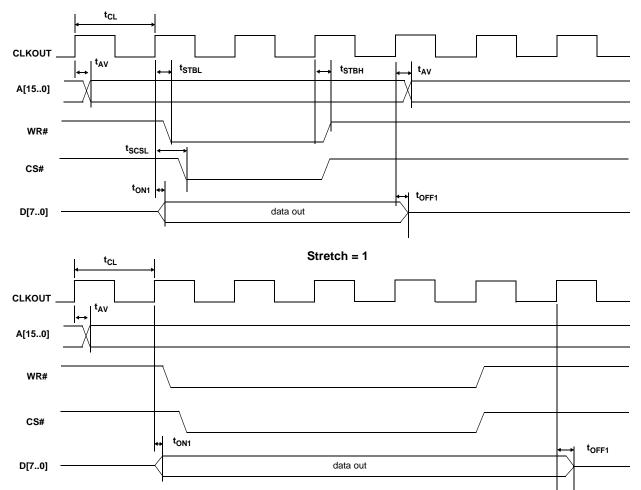

Figure 14. Data Memory Write Timing Diagram

### Table 17. Data Memory Write Parameters

| Parameter         | Description                       | Min | Max  | Unit | Notes |

|-------------------|-----------------------------------|-----|------|------|-------|

| t <sub>AV</sub>   | Delay from clock to valid address | 0   | 10.7 | ns   | -     |

| t <sub>STBL</sub> | Clock to WR pulse LOW             | 0   | 11.2 | ns   | -     |

| t <sub>STBH</sub> | Clock to WR pulse HIGH            | 0   | 11.2 | ns   | -     |

| t <sub>SCSL</sub> | Clock to CS pulse LOW             | -   | 13.0 | ns   | -     |

| t <sub>ON1</sub>  | Clock to data turn-on             | 0   | 13.1 | ns   | -     |

| t <sub>OFF1</sub> | Clock to data hold time           | 0   | 13.1 | ns   | -     |

When using the AUTPOPTR1 or AUTOPTR2 to address external memory, the address of AUTOPTR1 is only active while either RD# or WR# are active. The address of AUTOPTR2 is active throughout the cycle and meets the address valid time for which is based on the stretch value.

Note

<sup>23.</sup> The stretch memory cycle feature enables EZ-USB firmware to adjust the speed of data memory accesses not the program memory accesses. Details including typical strobe width timings can be found in the section 12.1.2 of the Technical Reference Manual. The address cycle width can be interpreted from these.

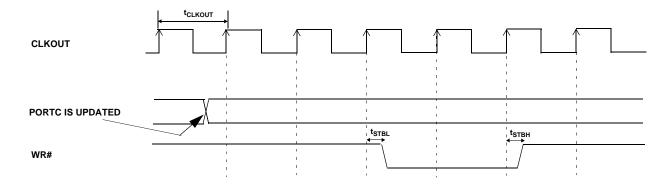

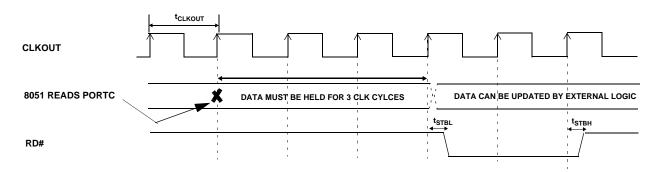

# **PORTC Strobe Feature Timings**

The RD# and WR# are present in the 100-pin version and the 128-pin package. In these 100-pin and 128-pin versions, an 8051 control bit can be set to pulse the RD# and WR# pins when the 8051 reads from or writes to PORTC. This feature is enabled by setting PORTCSTB bit in CPUCS register.

The RD# and WR# strobes are asserted for two CLKOUT cycles when PORTC is accessed.

The WR# strobe is asserted two clock cycles after PORTC is updated and is active for two clock cycles after that, as shown in Figure 16.

As for read, the value of PORTC three clock cycles before the assertion of RD# is the value that the 8051 reads in. The RD# is pulsed for two clock cycles after three clock cycles from the point when the 8051 has performed a read function on PORTC.

The RD# signal prompts the external logic to prepare the next data byte. Nothing gets sampled internally on assertion of the RD# signal itself; it is just a prefetch type signal to get the next data byte prepared. So, using it with that in mind easily meets the setup time to the next read.

The purpose of this pulsing of RD# is to allow the external peripheral to know that the 8051 is done reading PORTC and the data was latched into PORTC three CLKOUT cycles before asserting the RD# signal. After the RD# is pulsed, the external logic can update the data on PORTC.

Following is the timing diagram of the read and write strobing function on accessing PORTC. Refer to Data Memory Read<sup>[21]</sup> and Data Memory Write<sup>[23]</sup> for details on propagation delay of RD# and WR# signals.

#### Figure 16. WR# Strobe Function when PORTC is Accessed by 8051

#### Figure 17. RD# Strobe Function when PORTC is Accessed by 8051

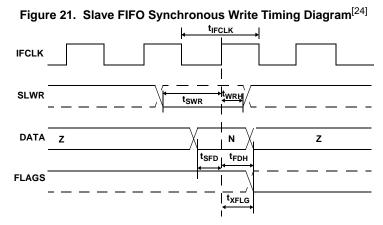

# **Slave FIFO Synchronous Write**

# Table 23. Slave FIFO Synchronous Write Parameters with Internally Sourced IFCLK<sup>[25]</sup>

| Parameter          | Description                            | Min   | Max | Unit |

|--------------------|----------------------------------------|-------|-----|------|

| t <sub>IFCLK</sub> | IFCLK period                           | 20.83 | -   | ns   |

| t <sub>SWR</sub>   | SLWR to clock setup time               | 10.4  | -   | ns   |

| t <sub>WRH</sub>   | Clock to SLWR hold time                | 0     | -   | ns   |

| t <sub>SFD</sub>   | FIFO data to clock setup time          | 9.2   | -   | ns   |

| t <sub>FDH</sub>   | Clock to FIFO data hold time           | 0     | _   | ns   |

| t <sub>XFLG</sub>  | Clock to FLAGS output propagation time | _     | 9.5 | ns   |

## Table 24. Slave FIFO Synchronous Write Parameters with Externally Sourced IFCLK<sup>[25]</sup>

| Parameter          | Description                            | Min   | Max  | Unit |

|--------------------|----------------------------------------|-------|------|------|

| t <sub>IFCLK</sub> | IFCLK Period                           | 20.83 | 200  | ns   |

| t <sub>SWR</sub>   | SLWR to clock setup time               | 12.1  | _    | ns   |

| t <sub>WRH</sub>   | Clock to SLWR hold time                | 3.6   | _    | ns   |

| t <sub>SFD</sub>   | FIFO data to clock setup time          | 3.2   | _    | ns   |

| t <sub>FDH</sub>   | Clock to FIFO data hold time           | 4.5   | _    | ns   |

| t <sub>XFLG</sub>  | Clock to FLAGS output propagation time | _     | 13.5 | ns   |

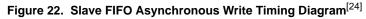

# **Slave FIFO Asynchronous Write**

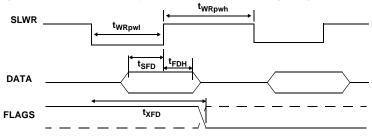

# Slave FIFO Address to Flags/Data

#### Table 30. Slave FIFO Address to Flags/Data Parameters

| Parameter         | Description                                       | Min | Max  | Unit |

|-------------------|---------------------------------------------------|-----|------|------|

| t <sub>XFLG</sub> | FIFOADR[1:0] to FLAGS output propagation delay    | -   | 10.7 | ns   |

| t <sub>XFD</sub>  | FIFOADR[1:0] to FIFODATA output propagation delay | _   | 14.3 | ns   |

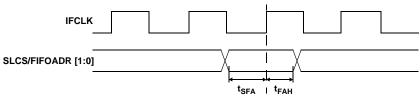

## **Slave FIFO Synchronous Address**

# Figure 28. Slave FIFO Synchronous Address Timing Diagram<sup>[24]</sup>

#### Table 31. Slave FIFO Synchronous Address Parameters<sup>[25]</sup>

| Parameter          | Description                      | Min   | Max | Unit |

|--------------------|----------------------------------|-------|-----|------|

| t <sub>IFCLK</sub> | Interface clock period           | 20.83 | 200 | ns   |

| t <sub>SFA</sub>   | FIFOADR[1:0] to clock setup time | 25    | _   | ns   |

| t <sub>FAH</sub>   | Clock to FIFOADR[1:0] hold time  | 10    | -   | ns   |

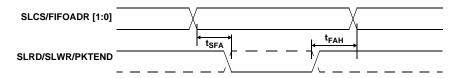

### Slave FIFO Asynchronous Address

# Figure 29. Slave FIFO Asynchronous Address Timing Diagram<sup>[24]</sup>

# Table 32. Slave FIFO Asynchronous Address Parameters<sup>[27]</sup>

| Parameter        | Description                                 | Min | Max | Unit |

|------------------|---------------------------------------------|-----|-----|------|

| t <sub>SFA</sub> | FIFOADR[1:0] to SLRD/SLWR/PKTEND setup time | 10  | -   | ns   |

| t <sub>FAH</sub> | RD/WR/PKTEND to FIFOADR[1:0] hold time      | 10  | -   | ns   |

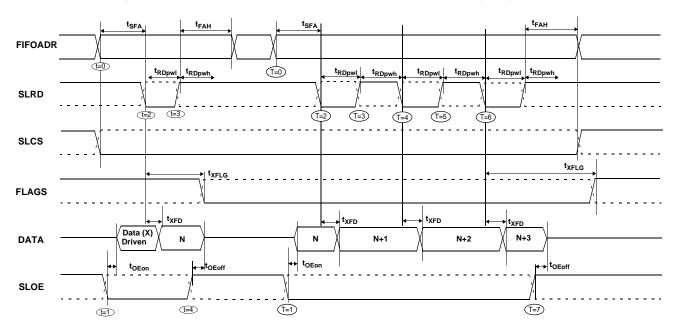

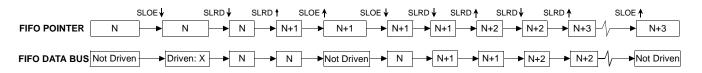

Sequence Diagram of a Single and Burst Asynchronous Read

Figure 33. Slave FIFO Asynchronous Read Sequence and Timing Diagram<sup>[24]</sup>

Figure 34. Slave FIFO Asynchronous Read Sequence of Events Diagram

Figure 33 shows the timing relationship of the SLAVE FIFO signals during an asynchronous FIFO read. It shows a single read followed by a burst read.

- At t = 0, the FIFO address is stable and the SLCS signal is asserted.

- At t = 1, SLOE is asserted. This results in the data bus being driven. The data that is driven on to the bus is the previous data, the data that was in the FIFO from an earlier read cycle.

- At t = 2, SLRD is asserted. The SLRD must meet the minimum active pulse of t<sub>RDpwl</sub> and minimum de-active pulse width of t<sub>RDpwh</sub>. If SLCS is used, then SLCS must be asserted before SLRD is asserted (The SLCS and SLRD signals must both be asserted to start a valid read condition.)

- The data that is driven, after asserting SLRD, is the updated data from the FIFO. This data is valid after a propagation delay of t<sub>XFD</sub> from the activating edge of SLRD. In Figure 33, data N is the first valid data read from the FIFO. For data to appear on the data bus during the read cycle (SLRD is asserted), SLOE must be in an asserted state. SLRD and SLOE can also be tied together.

The same sequence of events is also shown for a burst read marked with T = 0 through 5.

**Note** In the burst read mode, during SLOE is asserted, the data bus is in a driven state and outputs the previous data. After SLRD is asserted, the data from the FIFO is driven on the data bus (SLOE must also be asserted) and then the FIFO pointer is incremented.

TOP VIEW BOTTOM VIEW SIDE VIEW -8.00±0.10 56 43 PIN# 1 ID 42 10000000000000000 42 ()1 0.50±0.05 υυυυυυυ PIN 1 DOT 5.20±0.10 8.00±0.10 29 L<sub>0.25±0.05</sub> 14 29 d14 n n h n n n n n n n h n h-0.05 MAX 15 28 15 -1.00 MAX NOTES: 0.40±0.10 0.08 1. 🗱 HATCH AREA IS SOLDERABLE EXPOSED METAL. 4.50±0.10 2. REFERENCE JEDEC#: MO-220 001-53450 \*D 3. PACKAGE WEIGHT: 162  $\pm$  16 mg 4. ALL DIMENSIONS ARE IN MILLIMETERS

Figure 37. 56-Pin QFN 8 × 8 mm Sawn Version (001-53450)

#### 128 Lead Thin Plastic Quad Flatpack 14 X 20 X 1.4mm - A128 16.00±0.20 1.40±0.05 14.00±0.10 128 0.22±0.05 22.00±0.20 20.00±0.10 12°±1° SEE DETAIL A (8X) 0.50 1 TYP. ſ 0.20 MAX. 1.60 MAX. R 0.08 MIN. ~ 0° MIN. 0.20 MAX 0.08 SEATING PLANE STAND-DFF D 0.05 MIN. 0.15 MAX. NDTE: 0.25 1. JEDEC STD REF MS-026 GAUGE PLANE 2. BODY LENGTH DIMENSION DOES NOT INCLUDE MOLD PROTRUSION/END FLASH MOLD PROTRUSION/END FLASH SHALL NOT EXCEED 0.0098 in (0.25 mm) PER SIDE R 0.08 MIN. 0.20 MAX. BODY LENGTH DIMENSIONS ARE MAX PLASTIC BODY SIZE INCLUDING MOLD MISMATCH **∩**•–7 3. DIMENSIONS IN MILLIMETERS 0.60±0.15 -51-85101 \*F DETAILA

# Sales, Solutions, and Legal Information

# Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

# Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Lighting & Power Control                              | cypress.com/powerpsoc  |

| Memory                                                | cypress.com/memory     |

| PSoC                                                  | cypress.com/psoc       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless/RF                                           | cypress.com/wireless   |

# PSoC<sup>®</sup>Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Forums | Projects | Video | Blogs | Training | Components

Technical Support cypress.com/support

© Cypress Semiconductor Corporation, 2003-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

#### Document Number: 38-08032 Rev. \*Y Revise FX2LP is a trademark and EZ-USB is a registered trademark of Cypress Semiconductor Corporation.

#### Revised June 28, 2016

Purchase of I<sup>2</sup>C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips. As from October 1st, 2006 Philips Semiconductors has a new trade name - NXP Semiconductors.