Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are angineered to

### Details

| Details                 |                                                                              |

|-------------------------|------------------------------------------------------------------------------|

| Product Status          | Active                                                                       |

| Applications            | USB Microcontroller                                                          |

| Core Processor          | 8051                                                                         |

| Program Memory Type     | ROMIess                                                                      |

| Controller Series       | CY7C680xx                                                                    |

| RAM Size                | 16K x 8                                                                      |

| Interface               | I <sup>2</sup> C, USB, USART                                                 |

| Number of I/O           | 24                                                                           |

| Voltage - Supply        | 3V ~ 3.6V                                                                    |

| Operating Temperature   | 0°C ~ 70°C                                                                   |

| Mounting Type           | Surface Mount                                                                |

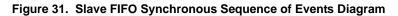

| Package / Case          | 56-BSSOP (0.295", 7.50mm Width)                                              |

| Supplier Device Package | 56-SSOP                                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy7c68013a-56pvxc |

|                         |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

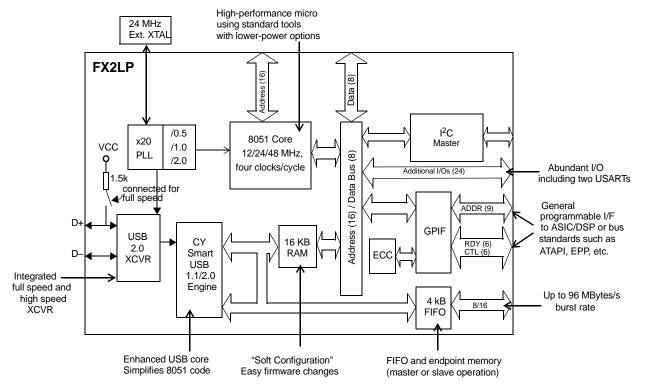

### Logic Block Diagram

Cypress's EZ-USB<sup>®</sup> FX2LP<sup>™</sup> (CY7C68013A/14A) is a low-power version of the EZ-USB FX2<sup>™</sup> (CY7C68013), which is a highly integrated, low-power USB 2.0 microcontroller. By integrating the USB 2.0 transceiver, serial interface engine (SIE), enhanced 8051 microcontroller, and a programmable peripheral interface in a single chip, Cypress has created a cost-effective solution that provides superior time-to-market advantages with low power to enable bus-powered applications.

The ingenious architecture of FX2LP results in data transfer rates of over 53 Mbytes per second (the maximum allowable USB 2.0 bandwidth), while still using a low-cost 8051 microcontroller in a package as small as a 56 VFBGA (5 mm x 5 mm). Because it incorporates the USB 2.0 transceiver, the FX2LP is more economical, providing a smaller-footprint solution than a USB 2.0 SIE or external transceiver implementations. With EZ-USB FX2LP, the Cypress Smart SIE handles most of the USB 1.1 and 2.0 protocol in hardware, freeing the embedded microcontroller for application-specific functions and decreasing the development time to ensure USB compatibility.

The general programmable interface (GPIF) and Master/Slave Endpoint FIFO (8-bit or 16-bit data bus) provide an easy and glueless interface to popular interfaces such as ATA, UTOPIA, EPP, PCMCIA, and most DSP/processors.

The FX2LP draws less current than the FX2 (CY7C68013), has double the on-chip code/data RAM, and is fit, form, and function compatible with the 56-, 100-, and 128-pin FX2.

Five packages are defined for the family: 56 VFBGA, 56 SSOP, 56 QFN, 100 TQFP, and 128 TQFP.

# CY7C68013A, CY7C68014A CY7C68015A, CY7C68016A

### Contents

| Applications                   | 5  |

|--------------------------------|----|

| Functional Overview            | 5  |

| USB Signaling Speed            | 5  |

| 8051 Microprocessor            | 5  |

| I <sup>2</sup> C Bus           | 5  |

| Buses                          | 5  |

| Reset and Wakeup               | 9  |

| Program/Data RAM               | 10 |

| External FIFO Interface        |    |

| GPIF                           | 14 |

| ECC Generation <sup>[8]</sup>  | 14 |

| USB Uploads and Downloads      | 14 |

| Autopointer Access             | 15 |

| I <sup>2</sup> C Controller    |    |

| CY7C68013A/14A and CY7C68015A/ |    |

| 16A Differences                | 15 |

| Register Summary               | 32 |

| Absolute Maximum Ratings       | 39 |

| Operating Conditions           | 39 |

| Thermal Characteristics        |    |

| DC Characteristics             | 40 |

| AC Electrical Characteristics           | 41 |

|-----------------------------------------|----|

| USB Transceiver                         | 41 |

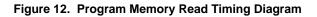

| Program Memory Read                     | 41 |

| Data Memory Read                        | 42 |

| Data Memory Write                       | 43 |

| PORTC Strobe Feature Timings            |    |

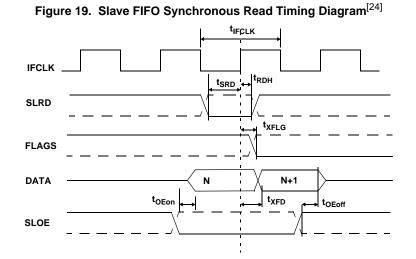

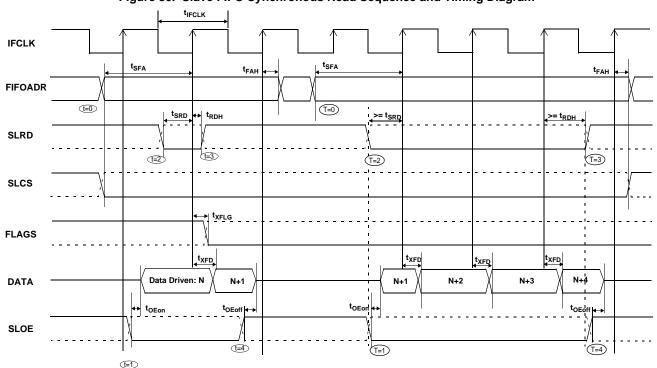

| Slave FIFO Synchronous Read             |    |

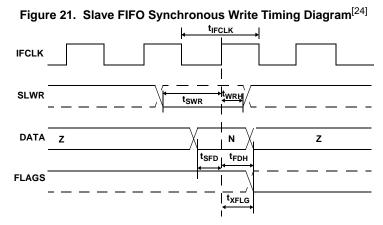

| Slave FIFO Synchronous Write            |    |

| Ordering Information                    |    |

| Ordering Code Definitions               | 56 |

| Package Diagrams                        |    |

| Quad Flat Package No Leads (QFN)        |    |

| Package Design Notes                    | 63 |

| Acronyms                                | 64 |

| Document Conventions                    | 64 |

| Units of Measure                        | 64 |

| Errata                                  | 65 |

| Document History Page                   | 66 |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      | 69 |

| Products                                |    |

| PSoC® Solutions                         | 69 |

| Cypress Developer Community             | 69 |

| Technical Support                       |    |

### Table 4. Individual FIFO/GPIF Interrupt Sources

| Priority | INT4VEC Value | Source   | Notes                                |

|----------|---------------|----------|--------------------------------------|

| 1        | 80            | EP2PF    | Endpoint 2 programmable flag         |

| 2        | 84            | EP4PF    | Endpoint 4 programmable flag         |

| 3        | 88            | EP6PF    | Endpoint 6 programmable flag         |

| 4        | 8C            | EP8PF    | Endpoint 8 programmable flag         |

| 5        | 90            | EP2EF    | Endpoint 2 empty flag <sup>[3]</sup> |

| 6        | 94            | EP4EF    | Endpoint 4 empty flag                |

| 7        | 98            | EP6EF    | Endpoint 6 empty flag                |

| 8        | 9C            | EP8EF    | Endpoint 8 empty flag                |

| 9        | A0            | EP2FF    | Endpoint 2 full flag                 |

| 10       | A4            | EP4FF    | Endpoint 4 full flag                 |

| 11       | A8            | EP6FF    | Endpoint 6 full flag                 |

| 12       | AC            | EP8FF    | Endpoint 8 full flag                 |

| 13       | B0            | GPIFDONE | GPIF operation complete              |

| 14       | B4            | GPIFWF   | GPIF waveform                        |

If Autovectoring is enabled (AV4EN = 1 in the INTSET-UP register), the FX 2LP substitutes its INT4VEC byte. Therefore, if the high byte ("page") of a jump-table address is preloaded at location 0x0054, the automatically inserted INT4VEC byte at 0x0055 directs the jump to the correct address out of the 14 addresses within the page. When the ISR occurs, the FX2LP pushes the program counter to its stack then jumps to address 0x0053, where it expects to find a "jump" instruction to the interrupt service routine (ISR).

Note

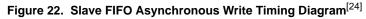

Errata: In Slave FIFO Asynchronous Word Wide mode, if a single word data is transferred from the USB host to EP2, configured as OUT Endpoint (EP) in the first transaction, then the Empty flag behaves incorrectly. This does not happen if the data size is more than one word in the first transaction. For more information, see the "Errata" on page 65.

### **Endpoint RAM**

Size

- 3 × 64 bytes (Endpoints 0 and 1)

- 8 × 512 bytes (Endpoints 2, 4, 6, 8)

Organization

- EP0

- Bidirectional endpoint zero, 64-byte buffer

- EP1IN, EP1OUT

- 64 byte buffers, bulk or interrupt

- EP2, 4, 6, 8

- Eight 512-byte buffers, bulk, interrupt, or isochronous. EP4 and EP8 can be double buffered; EP2 and 6 can be either double, triple, or quad buffered. For Hi-Speed endpoint configuration options, see Figure 5.

Setup Data Buffer

A separate 8-byte buffer at 0xE6B8-0xE6BF holds the setup data from a CONTROL transfer.

Endpoint Configurations (Hi-Speed Mode)

Endpoints 0 and 1 are the same for every configuration. Endpoint 0 is the only CONTROL endpoint, and endpoint 1 can be either BULK or INTERRUPT.

The endpoint buffers can be configured in any 1 of the 12 configurations shown in the vertical columns. When operating in the Full-Speed BULK mode, only the first 64 bytes of each buffer are used. For example, in Hi-Speed mode, the max packet size is 512 bytes, but in Full-Speed mode, it is 64 bytes. Even though a buffer is configured to a 512-byte buffer, in Full-Speed mode, only the first 64 bytes are used. The unused endpoint buffer space is not available for other operations. An example endpoint configuration is the EP2–1024 double-buffered; EP6–512 quad-buffered (column 8).

### Figure 5. Endpoint Configuration

| EP0 IN&OUT 64   64  <br>EP1 IN 64   64  <br>EP1 OUT 64   64                                                                                                                                                                                                                                                                                                                   | 64<br>64<br>64                                        | 64<br>64<br>64                                                            | 64<br>64<br>64                                                     | 64<br>64<br>64                                 | 64<br>64<br>64                                         | 64<br>64<br>64                                         | 64<br>64<br>64                     | 64<br>64<br>64                                                            | 64<br>64<br>64                                           | 64<br>64<br>64       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------|----------------------|

| EP2       EP2         512       512         512       512         512       512         EP4       512         512       512         512       512         512       512         512       512         512       512         EP6       EP6         512       512         512       512         512       512         512       512         512       512         512       512 | EP2<br>512<br>512<br>EP4<br>512<br>512<br>EP6<br>1024 | EP2<br>512<br>512<br>512<br>512<br>512<br>512<br>512<br>EP8<br>512<br>512 | EP2<br>512<br>512<br>512<br>512<br>512<br>512<br>512<br>512<br>512 | EP2<br>512<br>512<br>512<br>512<br>EP6<br>1024 | EP2<br>1024<br>1024<br>512<br>512<br>512<br>512<br>512 | EP2<br>1024<br>1024<br>EP6<br>512<br>512<br>512<br>512 | EP2<br>1024<br>1024<br>EP6<br>1024 | EP2<br>512<br>512<br>512<br>EP6<br>512<br>512<br>512<br>512<br>512<br>512 | EP2<br>1024<br>1024<br>1024<br>1024<br>EP8<br>512<br>512 | 1024<br>1024<br>1024 |

|                                                                                                                                                                                                                                                                                                                                                                               | 3                                                     | 4                                                                         | 5                                                                  | 6                                              | 7                                                      | 8                                                      | 9                                  | 10                                                                        | 11                                                       | 12                   |

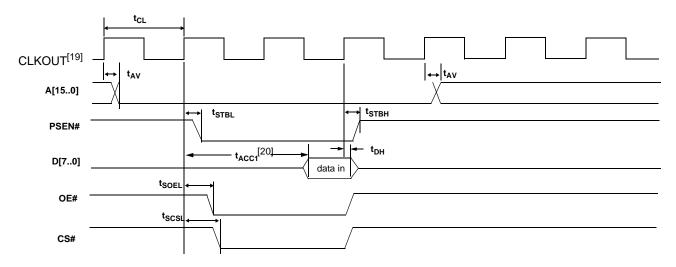

In the Slave (S) mode, FX2LP accepts either an internally derived clock or externally supplied clock (IFCLK, max frequency 48 MHz) and SLCS#, SLRD, SLWR, SLOE, PKTEND signals from external logic. When using an external IFCLK, the external clock must be present before switching to the external clock with the IFCLKSRC bit. Each endpoint can individually be selected for byte or word operation by an internal configuration bit and a Slave FIFO Output Enable signal (SLOE) that enables data of the selected width. External logic must ensure that the output enable signal is inactive when writing data to a slave FIFO. The slave interface can also operate asynchronously, where the SLRD and SLWR signals act directly as strobes, rather than a clock qualifier as in synchronous mode. The signal SLCS#.

### GPIF and FIFO Clock Rates

An 8051 register bit selects one of two frequencies for the internally supplied interface clock: 30 MHz and 48 MHz. Alternatively, an externally supplied clock of 5 MHz–48 MHz feeding the IFCLK pin can be used as the interface clock. IFCLK can be configured to function as an output clock when the GPIF and FIFOs are internally clocked. An output enable bit in the IFCONFIG register turns this clock output off, if desired. Another bit within the IFCONFIG register inverts the IFCLK signal whether internally or externally sourced.

### GPIF

The GPIF is a flexible 8-bit or 16-bit parallel interface driven by a user-programmable finite state machine. It enables the CY7C68013A/15A to perform local bus mastering and can implement a wide variety of protocols such as ATA interface, printer parallel port, and Utopia.

The GPIF has six programmable control outputs (CTL), nine address outputs (GPIFADRx), and six general-purpose ready inputs (RDY). The data bus width can be 8 or 16 bits. Each GPIF vector defines the state of the control outputs, and determines what state a ready input (or multiple inputs) must be before proceeding. The GPIF vector can be programmed to advance a FIFO to the next data value, advance an address, etc. A sequence of the GPIF vectors make up a single waveform that is executed to perform the desired data move between the FX2LP and the external device.

#### Six Control OUT Signals

The 100-pin and 128-pin packages bring out all six Control Output pins (CTL0-CTL5). The 8051 programs the GPIF unit to define the CTL waveforms. The 56-pin package brings out three of these signals, CTL0–CTL2. CTLx waveform edges can be programmed to make transitions as fast as once per clock (20.8 ns using a 48-MHz clock).

#### Six Ready IN Signals

The 100-pin and 128-pin packages bring out all six Ready inputs (RDY0–RDY5). The 8051 programs the GPIF unit to test the RDY pins for GPIF branching. The 56-pin package brings out two of these signals, RDY0–1.

### Nine GPIF Address OUT Signals

Nine GPIF address lines are available in the 100-pin and 128-pin packages, GPIFADR[8..0]. The GPIF address lines enable indexing through up to a 512-byte block of RAM. If more address lines are needed, then I/O port pins are used.

#### Long Transfer Mode

In the master mode, the 8051 appropriately sets GPIF transaction count registers (GPIFTCB3, GPIFTCB2, GPIFTCB1, or GPIFTCB0) for unattended transfers of up to 2<sup>32</sup> transactions. The GPIF automatically throttles data flow to prevent under or overflow until the full number of requested transactions complete. The GPIF decrements the value in these registers to represent the current status of the transaction.

### ECC Generation<sup>[8]</sup>

The EZ-USB can calculate ECCs (Error Correcting Codes) on data that passes across its GPIF or Slave FIFO interfaces. There are two ECC configurations: Two ECCs, each calculated over 256 bytes (SmartMedia Standard); and one ECC calculated over 512 bytes.

The ECC can correct any one-bit error or detect any two-bit error.

ECC Implementation

The two ECC configurations are selected by the ECCM bit:

### ECCM = 0

Two 3-byte ECCs, each calculated over a 256-byte block of data. This configuration conforms to the SmartMedia Standard.

Write any value to ECCRESET, then pass data across the GPIF or Slave FIFO interface. The ECC for the first 256 bytes of data is calculated and stored in ECC1. The ECC for the next 256 bytes is stored in ECC2. After the second ECC is calculated, the values in the ECCx registers do not change until ECCRESET is written again, even if more data is subsequently passed across the interface.

### ECCM = 1

One 3-byte ECC calculated over a 512-byte block of data.

Write any value to ECCRESET then pass data across the GPIF or Slave FIFO interface. The ECC for the first 512 bytes of data is calculated and stored in ECC1; ECC2 is unused. After the ECC is calculated, the values in ECC1 do not change even if more data is subsequently passed across the interface, till ECCRESET is written again.

### **USB Uploads and Downloads**

The core has the ability to directly edit the data contents of the internal 16-KB RAM and of the internal 512-byte scratch pad RAM via a vendor-specific command. This capability is normally used when soft downloading the user code and is available only to and from the internal RAM, only when the 8051 is held in reset. The available RAM spaces are 16 KB from 0x0000–0x3FFF (code/data) and 512 bytes from 0xE000–0xE1FF (scratch pad data RAM)<sup>[9]</sup>.

#### Notes

8. To use the ECC logic, the GPIF or Slave FIFO interface must be configured for byte-wide operation.

<sup>9.</sup> After the data is downloaded from the host, a "loader" can execute from internal RAM to transfer downloaded data to external memory.

### **Autopointer Access**

FX2LP provides two identical autopointers. They are similar to the internal 8051 data pointers but with an additional feature: they can optionally increment after every memory access. This capability is available to and from both internal and external RAM. Autopointers are available in external FX2LP registers under the control of a mode bit (AUTOPTRSET-UP.0). Using the external FX2LP autopointer access (at 0xE67B – 0xE67C) enables the autopointer to access all internal and external RAM to the part.

Also, autopointers can point to any FX2LP register or endpoint buffer space. When the autopointer access to external memory is enabled, locations 0xE67B and 0xE67C in XDATA and code space cannot be used.

### I<sup>2</sup>C Controller

FX2LP has one I<sup>2</sup>C port that is driven by two internal controllers, the one that automatically operates at boot time to load VID/PID/DID and configuration information, and another that the 8051 uses when running to control external I<sup>2</sup>C devices. The I<sup>2</sup>C port operates in master mode only.

### <sup>2</sup>C Port Pins

The I<sup>2</sup>C pins SCL and SDA must have external 2.2-k $\Omega$  pull-up resistors even if no EEPROM is connected to the FX2LP. External EEPROM device address pins must be configured properly. See Table 8 for configuring the device address pins.

#### Table 8. Strap Boot EEPROM Address Lines to These Values

| Bytes | Example EEPROM         | A2  | A1  | A0  |

|-------|------------------------|-----|-----|-----|

| 16    | 24LC00 <sup>[10]</sup> | N/A | N/A | N/A |

| 128   | 24LC01                 | 0   | 0   | 0   |

| 256   | 24LC02                 | 0   | 0   | 0   |

| 4K    | 24LC32                 | 0   | 0   | 1   |

| 8K    | 24LC64                 | 0   | 0   | 1   |

| 16K   | 24LC128                | 0   | 0   | 1   |

### $P^2C$ Interface Boot Load Access

At power-on reset, the  $I^2C$  interface boot loader loads the VID/PID/DID configuration bytes and up to 16 KB of program/data. The available RAM spaces are 16 KB from 0x0000–0x3FFF and 512 bytes from 0xE000–0xE1FF. The 8051 is in reset.  $I^2C$  interface boot loads only occur after power-on reset.

#### PC Interface General-Purpose Access

The 8051 can control peripherals connected to the  $I^2C$  bus using the I2CTL and I2DAT registers. FX2LP provides  $I^2C$  master control only; it is never an  $I^2C$  slave.

### **Compatible with Previous Generation EZ-USB FX2**

The EZ-USB FX2LP is form-, fit-, and with minor exceptions, functionally-compatible with its predecessor, the EZ-USB FX2.

This makes for an easy transition for designers wanting to upgrade their systems from the FX2 to the FX2LP. The pinout and package selection are identical and a vast majority of firmware previously developed for the FX2 functions in the FX2LP.

For designers migrating from the FX2 to the FX2LP, a change in the bill of material and review of the memory allocation (due to increased internal memory) is required. For more information about migrating from EZ-USB FX2 to EZ-USB FX2LP, see the application note titled *Migrating from EZ-USB FX2 to EZ-USB FX2 to EZ-USB FX2LP* available in the Cypress web site.

#### Table 9. Part Number Conversion Table

| EZ-USB FX2<br>Part Number | EZ-USB FX2LP<br>Part Number                 | Package<br>Description               |

|---------------------------|---------------------------------------------|--------------------------------------|

| CY7C68013-56PVC           | CY7C68013A-56PVXC or<br>CY7C68014A-56PVXC   | 56-pin<br>SSOP                       |

| CY7C68013-56PVCT          | CY7C68013A-56PVXCT or<br>CY7C68014A-56PVXCT | 56-pin<br>SSOP –<br>Tape and<br>Reel |

| CY7C68013-56LFC           | CY7C68013A-56LFXC or<br>CY7C68014A-56LFXC   | 56-pin QFN                           |

| CY7C68013-100AC           | CY7C68013A-100AXC or<br>CY7C68014A-100AXC   | 100-pin<br>TQFP                      |

| CY7C68013-128AC           | CY7C68013A-128AXC or<br>CY7C68014A-128AXC   | 128-pin<br>TQFP                      |

### CY7C68013A/14A and CY7C68015A/16A Differences

CY7C68013A is identical to CY7C68014A in form, fit, and functionality. CY7C68015A is identical to CY7C68016A in form, fit, and functionality. CY7C68014A and CY7C68016A have a lower suspend current than CY7C68013A and CY7C68015A respectively and are ideal for power-sensitive battery applications.

CY7C68015A and CY7C68016A are available in 56-pin QFN package only. Two additional GPIO signals are available on the CY7C68015A and CY7C68016A to provide more flexibility when neither IFCLK or CLKOUT are needed in the 56-pin package.

USB developers wanting to convert their FX2 56-pin application to a bus-powered system directly benefit from these additional signals. The two GPIOs give developers the signals they need for the power-control circuitry of their bus-powered application without pushing them to a high-pincount version of FX2LP.

The CY7C68015A is only available in the 56-pin QFN package

# Table 10. CY7C68013A/14A and CY7C68015A/16A Pin Differences

| CY7C68013A/CY7C68014A | CY7C68015A/CY7C68016A |

|-----------------------|-----------------------|

| IFCLK                 | PE0                   |

| CLKOUT                | PE1                   |

### **Pin Assignments**

Figure 6 on page 17 identifies all signals for the five package types. The following pages illustrate the individual pin diagrams, plus a combination diagram showing which of the full set of signals are available in the 128-pin, 100-pin, and 56-pin packages.

The signals on the left edge of the 56-pin package in Figure 6 are common to all versions in the FX2LP family with the noted differences between the CY7C68013A/14A and the CY7C68015A/16A.

Three modes are available in all package versions: Port, GPIF master, and Slave FIFO. These modes define the signals on the right edge of the diagram. The 8051 selects the interface mode using the IFCONFIG[1:0] register bits. Port mode is the power on default configuration.

The 100-pin package adds functionality to the 56-pin package by adding these pins:

- PORTC or alternate GPIFADR[7:0] address signals

- PORTE or alternate GPIFADR[8] address signal and seven additional 8051 signals

- Three GPIF Control signals

- Four GPIF Ready signals

- Nine 8051 signals (two USARTs, three timer inputs, INT4, and INT5#)

- BKPT, RD#, WR#.

The 128-pin package adds the 8051 address and data buses plus control signals. Note that two of the required signals, RD# and WR#, are present in the 100-pin version.

In the 100-pin and 128-pin versions, an 8051 control bit can be set to pulse the RD# and WR# pins when the 8051 reads from/writes to PORTC. This feature is enabled by setting the PORTCSTB bit in the CPUCS register.

PORTC Strobe Feature Timings displays the timing diagram of the read and write strobing function on accessing PORTC.

|                       | <b>Fig</b><br>Port                                  | jure 6. Sig                                                                                                                                                                                                                                   | gnal<br>GPIF Master                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Slave FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | XTALIN<br>XTALOUT<br>RESET#<br>WAKEUP#<br>SCL 56    | PD7<br>PD6<br>PD5<br>PD4<br>PD3<br>PD2<br>PD1<br>PD0<br>PB7<br>PB6<br>PB5<br>PB4<br>PB3<br>PB2<br>PB1<br>PB0                                                                                                                                  | $ \begin{array}{c} \Leftrightarrow \ FD[15] \\ \Leftrightarrow \ FD[14] \\ \Leftrightarrow \ FD[13] \\ \Leftrightarrow \ FD[12] \\ \Leftrightarrow \ FD[10] \\ \Leftrightarrow \ FD[10] \\ \Leftrightarrow \ FD[9] \\ \Leftrightarrow \ FD[9] \\ \Leftrightarrow \ FD[6] \\ \Leftrightarrow \ FD[5] \\ \Leftrightarrow \ FD[6] \\ \Leftrightarrow \ FD[2] \\ \Leftrightarrow \ FD[2] \\ \Leftrightarrow \ FD[2] \\ \Leftrightarrow \ FD[2] \\ \Leftrightarrow \ FD[0] \\ \end{array} $ | $ \begin{array}{c} & \label{eq:constraint} \\ & c$ |

| $\longleftrightarrow$ | SDA<br>**PE0 replaces IFCLK                         |                                                                                                                                                                                                                                               | RDY0 ←<br>RDY1 ←                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ← SLRD<br>← SLWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                       | & PE1 replaces CLKOUT<br>on CY7C68015A/16A<br>**PE0 |                                                                                                                                                                                                                                               | $\begin{array}{c} \text{CTL0} \rightarrow \\ \text{CTL1} \rightarrow \\ \text{CTL2} \rightarrow \end{array}$                                                                                                                                                                                                                                                                                                                                                                           | $\rightarrow$ FLAGA<br>$\rightarrow$ FLAGB<br>$\rightarrow$ FLAGC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       | **PE1<br>IFCLK<br>CLKOUT<br>DPLUS<br>DMINUS         | INT0#/PA0<br>INT1#/PA1<br>PA2<br>WU2/PA3<br>PA4<br>PA5<br>PA6<br>PA7                                                                                                                                                                          | INT0#/PA0<br>INT1#/PA1<br>PA2<br>WU2/PA3<br>PA4<br>PA5<br>PA6<br>PA7                                                                                                                                                                                                                                                                                                                                                                                                                   | INT0#/ PA0<br>INT1#/ PA1<br>← SLOE<br>WU2/PA3<br>← FIFOADR0<br>← FIFOADR1<br>← PKTEND<br>PA7/FLAGD/SLCS#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | D7<br>D6                                            | RxD0<br>TxD0<br>RxD1<br>INT4<br>INT5#<br>T2<br>T1<br>T0<br>I RD#<br>I OE#<br>I PSEN#<br>I OE#<br>I PSEN#<br>I OE#<br>I PSEN#<br>I OE#<br>I A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | $ \begin{array}{c} \rightarrow \text{CTL3} \\ \rightarrow \text{CTL4} \\ \rightarrow \text{CTL5} \\ \leftarrow \text{RDY2} \\ \leftarrow \text{RDY3} \\ \leftarrow \text{RDY4} \\ \leftarrow \text{RDY5} \end{array} $                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### Table 11. FX2LP Pin Descriptions<sup>[11]</sup> (continued)

| 128<br>TQFP | 100<br>TQFP | 56<br>SSOP | 56<br>QFN | 56<br>VFBGA | Name             | Туре  | Default    | Reset <sup>[12]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-------------|------------|-----------|-------------|------------------|-------|------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POR         | ΓD          |            |           |             |                  |       |            |                       |                                                                                                                                                                                                                                                                                                                                                                                                              |

| 102         | 80          | 52         | 45        | 8A          | PD0 or<br>FD[8]  | I/O/Z | l<br>(PD0) | Z<br>(PD0)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[8]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                              |

| 103         | 81          | 53         | 46        | 7A          | PD1 or<br>FD[9]  | I/O/Z | l<br>(PD1) | Z<br>(PD1)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[9]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                              |

| 104         | 82          | 54         | 47        | 6B          | PD2 or<br>FD[10] | I/O/Z | l<br>(PD2) | Z<br>(PD2)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[10]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                             |

| 105         | 83          | 55         | 48        | 6A          | PD3 or<br>FD[11] | I/O/Z | l<br>(PD3) | Z<br>(PD3)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[11]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                             |

| 121         | 95          | 56         | 49        | 3B          | PD4 or<br>FD[12] | I/O/Z | l<br>(PD4) | Z<br>(PD4)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[12]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                             |

| 122         | 96          | 1          | 50        | ЗA          | PD5 or<br>FD[13] | I/O/Z | l<br>(PD5) | Z<br>(PD5)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br>FD[13] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                    |

| 123         | 97          | 2          | 51        | 3C          | PD6 or<br>FD[14] | I/O/Z | l<br>(PD6) | Z<br>(PD6)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br>FD[14] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                    |

| 124         | 98          | 3          | 52        | 2A          | PD7 or<br>FD[15] | I/O/Z | l<br>(PD7) | Z<br>(PD7)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[15]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                             |

| Port        | E           |            |           |             |                  |       |            |                       |                                                                                                                                                                                                                                                                                                                                                                                                              |

| 108         | 86          | _          | _         | _           | PE0 or<br>T0OUT  | I/O/Z | l<br>(PE0) | Z<br>(PE0)            | Multiplexed pin whose function is selected by the<br>PORTECFG.0 bit.<br><b>PE0</b> is a bidirectional I/O port pin.<br><b>TOOUT</b> is an active-HIGH signal from 8051<br>Timer-counter0. TOOUT outputs a high level for<br>one CLKOUT clock cycle when Timer0 overflows.<br>If Timer0 is operated in Mode 3 (two separate<br>timer/counters), TOOUT is active when the low byte<br>timer/counter overflows. |

| 109         | 87          | _          | _         | _           | PE1 or<br>T1OUT  | I/O/Z | l<br>(PE1) | Z<br>(PE1)            | Multiplexed pin whose function is selected by the<br>PORTECFG.1 bit.<br><b>PE1</b> is a bidirectional I/O port pin.<br><b>T10UT</b> is an active HIGH signal from 8051<br>Timer-counter1. T10UT outputs a high level for<br>one CLKOUT clock cycle when Timer1 overflows.<br>If Timer1 is operated in Mode 3 (two separate<br>timer/counters), T10UT is active when the low byte<br>timer/counter overflows. |

### Table 11. FX2LP Pin Descriptions<sup>[11]</sup> (continued)

| 128<br>TQFP | 100<br>TQFP | 56<br>SSOP | 56<br>QFN | 56<br>VFBGA | Name                                        | Туре       | Default | Reset <sup>[12]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-------------|------------|-----------|-------------|---------------------------------------------|------------|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7           | 6           | -          | -         | -           | RDY3                                        | Input      | N/A     | N/A                   | RDY3 is a GPIF input signal.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8           | 7           | -          | -         | —           | RDY4                                        | Input      | N/A     | N/A                   | RDY4 is a GPIF input signal.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9           | 8           | -          |           | -           | RDY5                                        | Input      | N/A     | N/A                   | RDY5 is a GPIF input signal.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 69          | 54          | 36         | 29        | 7H          | CTL0 or<br>FLAGA                            | O/Z        | н       | L                     | Multiplexed pin whose function is selected by the<br>following bits:<br>IFCONFIG[10].<br><b>CTL0</b> is a GPIF control output.<br><b>FLAGA</b> is a programmable slave-FIFO output<br>status flag signal.<br>Defaults to programmable for the FIFO selected by<br>the FIFOADR[1:0] pins.                                                                                                                                                     |

| 70          | 55          | 37         | 30        | 7G          | CTL1 or<br>FLAGB                            | O/Z        | н       | L                     | Multiplexed pin whose function is selected by the<br>following bits:<br>IFCONFIG[10].<br><b>CTL1</b> is a GPIF control output.<br><b>FLAGB</b> is a programmable slave-FIFO output<br>status flag signal.<br>Defaults to FULL for the FIFO selected by the<br>FIFOADR[1:0] pins.                                                                                                                                                             |

| 71          | 56          | 38         | 31        | 8H          | CTL2 or<br>FLAGC                            | O/Z        | н       | L                     | Multiplexed pin whose function is selected by the<br>following bits:<br>IFCONFIG[10].<br><b>CTL2</b> is a GPIF control output.<br><b>FLAGC</b> is a programmable slave-FIFO output<br>status flag signal.<br>Defaults to EMPTY for the FIFO selected by the<br>FIFOADR[1:0] pins.                                                                                                                                                            |

| 66          | 51          | -          | _         | —           | CTL3                                        | O/Z        | Н       | L                     | CTL3 is a GPIF control output.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 67          | 52          | -          | -         | —           | CTL4                                        | Output     | Н       | L                     | CTL4 is a GPIF control output.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 98          | 76          | -          | Ι         | -           | CTL5                                        | Output     | Н       | L                     | CTL5 is a GPIF control output.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 32          | 26          | 20         | 13        | 2G          | IFCLK on<br>CY7C68013A<br>and<br>CY7C68014A | I/O/Z      | Z       | Z                     | Interface Clock, used for synchronously clocking<br>data into or out of the slave FIFOs. IFCLK also<br>serves as a timing reference for all slave FIFO<br>control signals and GPIF. When internal clocking is<br>used (IFCONFIG.7 = 1) the IFCLK pin can be<br>configured to output 30/48 MHz by bits<br>IFCONFIG.5 and IFCONFIG.6. IFCLK may be<br>inverted, whether internally or externally sourced,<br>by setting the bit IFCONFIG.4 =1. |

|             |             |            |           |             | PE0 on<br>CY7C68015A<br>and<br>CY7C68016A   | -<br>I/O/Z | <br>I   | Z                     | PE0 is a bidirectional I/O port pin.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 28          | 22          | _          | _         | _           | INT4                                        | Input      | N/A     | N/A                   | <b>INT4</b> is the 8051 INT4 interrupt request input signal. The INT4 pin is edge-sensitive, active HIGH.                                                                                                                                                                                                                                                                                                                                    |

| 106         | 84          | -          | _         | _           | INT5#                                       | Input      | N/A     | N/A                   | <b>INT5#</b> is the 8051 INT5 interrupt request input signal. The INT5 pin is edge-sensitive, active LOW.                                                                                                                                                                                                                                                                                                                                    |

| 31          | 25          | -          | _         | _           | T2                                          | Input      | N/A     | N/A                   | <b>T2</b> is the active HIGH T2 input signal to 8051<br>Timer2, which provides the input to Timer2 when<br>C/T2 = 1. When $C/T2 = 0$ , Timer2 does not use this<br>pin.                                                                                                                                                                                                                                                                      |

# CY7C68013A, CY7C68014A CY7C68015A, CY7C68016A

### Table 12. FX2LP Register Summary (continued)

| Hex      | Size | Name                                    | Description                                 | b7        | b6         | b5                  | b4         | b3         | b2         | b1          | b0     | Default           | Access   |

|----------|------|-----------------------------------------|---------------------------------------------|-----------|------------|---------------------|------------|------------|------------|-------------|--------|-------------------|----------|

| xxxx     |      | I <sup>2</sup> C Configuration Byte     |                                             | 0         | DISCON     | 0                   | 0          | 0          | 0          | 0           | 400KHZ | XXXXXXXXX<br>[16] | n/a      |

|          |      | On a sight Franchism, Datai             |                                             |           | -          | -                   | -          |            | -          |             |        | [10]              |          |

|          |      | Special Function Regis                  |                                             | D-7       | <b>D</b> 0 | 0.5                 | <b>D</b> ( | <b>D</b> 0 | <b>D</b> 0 | <b>D</b> .1 |        |                   | D14/     |

| 80       | 1    | IOA <sup>[15]</sup>                     | Port A (bit addressable)                    | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | XXXXXXXX          |          |

| 81       | 1    | SP                                      | Stack Pointer                               | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | 00000111          |          |

| 82       | 1    | DPL0                                    | Data Pointer 0 L                            | A7        | A6         | A5                  | A4         | A3         | A2         | A1          | A0     | 00000000          |          |

| 83       | 1    | DPH0                                    | Data Pointer 0 H                            | A15       | A14        | A13                 | A12        | A11        | A10        | A9          | A8     | 00000000          |          |

| 84       | 1    | DPL1 <sup>[15]</sup>                    | Data Pointer 1 L                            | A7        | A6         | A5                  | A4         | A3         | A2         | A1          | A0     | 00000000          |          |

| 85       | 1    | DPH1 <sup>[15]</sup>                    | Data Pointer 1 H                            | A15       | A14        | A13                 | A12        | A11        | A10        | A9          | A8     | 00000000          |          |

| 86       | 1    | DPS <sup>[15]</sup>                     | Data Pointer 0/1 select                     | 0         | 0          | 0                   | 0          | 0          | 0          | 0           | SEL    | 00000000          |          |

| 87       | 1    | PCON                                    | Power Control                               | SMOD0     | x          | 1                   | 1          | x          | х          | х           | IDLE   | 00110000          |          |

| 88       | 1    | TCON                                    | Timer/Counter Control<br>(bit addressable)  | TF1       | TR1        | TF0                 | TR0        | IE1        | IT1        | IE0         | IT0    | 0000000           | RW       |

| 89       | 1    | TMOD                                    | Timer/Counter Mode<br>Control               | GATE      | СТ         | M1                  | MO         | GATE       | СТ         | M1          | MO     | 0000000           | RW       |

| 3A       | 1    | TL0                                     | Timer 0 reload L                            | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | 00000000          | RW       |

| 8B       | 1    | TL1                                     | Timer 1 reload L                            | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | 00000000          | RW       |

| BC       | 1    | TH0                                     | Timer 0 reload H                            | D15       | D14        | D13                 | D12        | D11        | D10        | D9          | D8     | 00000000          | RW       |

| 8D       | 1    | TH1                                     | Timer 1 reload H                            | D15       | D14        | D13                 | D12        | D11        | D10        | D9          | D8     | 00000000          | RW       |

| BE       | 1    | CKCON <sup>[15]</sup>                   | Clock Control                               | х         | x          | T2M                 | T1M        | TOM        | MD2        | MD1         | MD0    | 00000001          | RW       |

| 3F       | 1    | reserved                                |                                             |           |            |                     |            |            | -          | 1           |        |                   |          |

| 90       | 1    | IOB <sup>[15]</sup>                     | Port B (bit addressable)                    | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | xxxxxxx           | RW       |

| 90<br>91 | 1    | EXIF <sup>[15]</sup>                    | External Interrupt Flag(s)                  | IE5       | IE4        | I <sup>2</sup> CINT | USBNT      | 1          | 0          | 0           | 0      | 00001000          |          |

| 92       | 1    | MPAGE <sup>[15]</sup>                   | Upper Addr Byte of MOVX<br>using @R0 / @R1  |           | A14        | A13                 | A12        | A11        | A10        | A9          | A8     | 00000000          |          |

| 93       | 5    | reserved                                | <u> </u>                                    |           |            |                     | 1          |            | 1          | 1           |        | 1                 |          |

|          | 1    | SCON0                                   | Serial Port 0 Control<br>(bit addressable)  | SM0_0     | SM1_0      | SM2_0               | REN_0      | TB8_0      | RB8_0      | TI_0        | RI_0   | 00000000          | RW       |

| 99       | 1    | SBUF0                                   | Serial Port 0 Data Buffer                   | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | 00000000          | RW       |

| 9A       | 1    | AUTOPTRH1 <sup>[15]</sup>               | Autopointer 1 Address H                     | A15       | A14        | A13                 | A12        | A11        | A10        | A9          | A8     | 00000000          |          |

| 9B       | 1    | AUTOPTRL1 <sup>[15]</sup>               | Autopointer 1 Address L                     | A13<br>A7 | A14<br>A6  | A13<br>A5           | A12<br>A4  | A3         | A10<br>A2  | A3<br>A1    | A0     | 00000000          |          |

|          | 1    |                                         | Autopointer T Address L                     | A7        | Ab         | Ab                  | A4         | A3         | AZ         | AT          | AU     | 0000000           | RVV      |

| 9C       | 1    | reserved                                |                                             |           |            | 4.40                | 4.4.0      |            |            | 10          | 10     |                   | D14/     |

| 9D       | 1    | AUTOPTRH2 <sup>[15]</sup>               |                                             | A15       | A14        | A13                 | A12        | A11        | A10        | A9          | A8     | 00000000          |          |

| 9E       | 1    | AUTOPTRL2 <sup>[15]</sup>               | Autopointer 2 Address L                     | A7        | A6         | A5                  | A4         | A3         | A2         | A1          | A0     | 00000000          | RW       |

| 9F       | 1    | reserved                                |                                             | _         |            | _                   | -          |            |            |             |        |                   |          |

| A0       | 1    | IOC <sup>[15]</sup>                     | Port C (bit addressable)                    | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | XXXXXXXX          | RW       |

| A1       | 1    | INT2CLR <sup>[15]</sup>                 | Interrupt 2 clear                           | x         | x          | х                   | x          | x          | х          | x           | x      | XXXXXXXX          | W        |

| A2       | 1    | INT4CLR <sup>[15]</sup>                 | Interrupt 4 clear                           | х         | x          | х                   | x          | x          | х          | x           | x      | XXXXXXXX          | W        |

| A3       | 5    | reserved                                |                                             |           |            |                     |            |            |            |             |        |                   |          |

| A8       | 1    | IE                                      | Interrupt Enable<br>(bit addressable)       | EA        | ES1        | ET2                 | ES0        | ET1        | EX1        | ET0         | EX0    | 00000000          | RW       |

| A9       | 1    | reserved                                |                                             |           |            |                     |            |            |            |             |        |                   |          |

| AA       | 1    | EP2468STAT <sup>[15]</sup>              | Endpoint 2,4,6,8 status<br>flags            | EP8F      | EP8E       | EP6F                | EP6E       | EP4F       | EP4E       | EP2F        | EP2E   | 01011010          | R        |

| AB       | 1    | EP24FIFOFLGS                            | status flags                                | 0         | EP4PF      | EP4EF               | EP4FF      | 0          | EP2PF      | EP2EF       | EP2FF  | 00100010          | R        |

| AC       | 1    | EP68FIFOFLGS<br><sup>[15]</sup>         | Endpoint 6,8 slave FIFO status flags        | 0         | EP8PF      | EP8EF               | EP8FF      | 0          | EP6PF      | EP6EF       | EP6FF  | 01100110          | R        |

| AD       | 2    | reserved                                |                                             |           |            |                     |            |            |            |             |        |                   |          |

| AF       | 1    |                                         | Autopointer 1&2 setup                       | 0         | 0          | 0                   | 0          | 0          | APTR2INC   | APTR1INC    | APTREN | 00000110          | RW       |

| B0       | 1    | IOD <sup>[15]</sup>                     | Port D (bit addressable)                    | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | XXXXXXXX          | RW       |

| B1       | 1    | IOE <sup>[15]</sup>                     | Port E<br>(NOT bit addressable)             | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | XXXXXXXX          | RW       |

| B2       | 1    | OEA <sup>[15]</sup>                     | Port A Output Enable                        | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | 00000000          | RW       |

| B3       | 1    | OEB <sup>[15]</sup>                     | Port B Output Enable                        | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | 00000000          | RW       |

| B4       | 1    | OEC <sup>[15]</sup>                     | Port C Output Enable                        | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | 00000000          |          |

| 35       | 1    | OED <sup>[15]</sup>                     | Port D Output Enable                        | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | 00000000          |          |

| 36       | 1    | OEE <sup>[15]</sup>                     | Port E Output Enable                        | D7        | D6         | D5                  | D4         | D3         | D2         | D1          | D0     | 00000000          |          |

| 37       | 1    | reserved                                |                                             |           | 1          | 1                   | 1          | 1          | 1          | 1           |        |                   |          |

| 38       | 1    | IP                                      | Interrupt Priority (bit ad-<br>dressable)   | 1         | PS1        | PT2                 | PS0        | PT1        | PX1        | PT0         | PX0    | 1000000           | RW       |

| 39       | 1    | reserved                                |                                             |           | +          | 1                   | 1          | 1          | 1          | 1           | 1      | 1                 | 1        |

| BA       |      | EP01STAT <sup>[15]</sup>                | Endpoint 0&1 Status                         | 0         | 0          | 0                   | 0          | 0          | EP1INBSY   | EP1OUTBS    | EP0BSY | 00000000          | R        |

| BB<br>BB | 1    | GPIFTRIG <sup>[15, 13]</sup>            |                                             | DONE      | 0          | 0                   | 0          | 0          | RW         | EP1001B3    | EP0B31 | 10000xxx          |          |

|          | 1    |                                         | Endpoint 2,4,6,8 GPIF<br>slave FIFO Trigger | DONE      | 0          | 0                   | 0          | 3          | 1.1.1      | -F 1        | LFU    | 10000xXX          | מממוווים |

|          | 1    | reconved                                |                                             |           |            |                     |            |            |            |             |        |                   |          |

| BC<br>BD | 1    | reserved<br>GPIFSGLDATH <sup>[15]</sup> | GPIF Data H (16-bit mode                    | D15       | D14        | D13                 | D12        | D11        | D10        | D9          | D8     | xxxxxxx           | DW/      |

Notes

15. SFRs not part of the standard 8051 architecture.16. If no EEPROM is detected by the SIE then the default is 00000000.

### **DC Characteristics**

### Table 14. DC Characteristics

| Parameter          | Description                  | Conditions                        | Min  | Тур | Max                 | Unit |

|--------------------|------------------------------|-----------------------------------|------|-----|---------------------|------|

| VCC                | Supply voltage               | -                                 | 3.00 | 3.3 | 3.60                | V    |

| VCC Ramp Up        | 0 to 3.3 V                   | -                                 | 200  | -   | -                   | μS   |

| V <sub>IH</sub>    | Input HIGH voltage           | _                                 | 2    | -   | 5.25                | V    |

| V <sub>IL</sub>    | Input LOW voltage            | -                                 | -0.5 | -   | 0.8                 | V    |

| V <sub>IH_X</sub>  | Crystal input HIGH voltage   | -                                 | 2    | -   | 5.25                | V    |

| V <sub>IL_X</sub>  | Crystal input LOW voltage    | -                                 | -0.5 | -   | 0.8                 | V    |

| l <sub>l</sub>     | Input leakage current        | $0 < V_{IN} < V_{CC}$             | -    | -   | ±10                 | μA   |

| V <sub>OH</sub>    | Output voltage HIGH          | I <sub>OUT</sub> = 4 mA           | 2.4  | -   | -                   | V    |