Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are analyzared to

### Details

| Detalls                 |                                                                               |

|-------------------------|-------------------------------------------------------------------------------|

| Product Status          | Active                                                                        |

| Applications            | USB Microcontroller                                                           |

| Core Processor          | 8051                                                                          |

| Program Memory Type     | ROMIess                                                                       |

| Controller Series       | CY7C680xx                                                                     |

| RAM Size                | 16K x 8                                                                       |

| Interface               | I²C, USB, USART                                                               |

| Number of I/O           | 24                                                                            |

| Voltage - Supply        | 3V ~ 3.6V                                                                     |

| Operating Temperature   | 0°C ~ 70°C                                                                    |

| Mounting Type           | Surface Mount                                                                 |

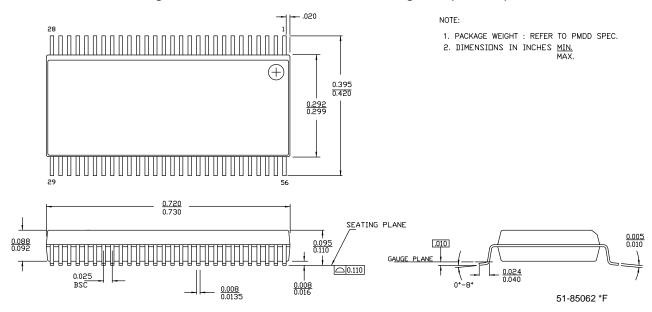

| Package / Case          | 56-BSSOP (0.295", 7.50mm Width)                                               |

| Supplier Device Package | 56-SSOP                                                                       |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy7c68013a-56pvxct |

|                         |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# CY7C68013A, CY7C68014A CY7C68015A, CY7C68016A

# Contents

| Applications                   | 5  |

|--------------------------------|----|

| Functional Overview            | 5  |

| USB Signaling Speed            | 5  |

| 8051 Microprocessor            | 5  |

| I <sup>2</sup> C Bus           | 5  |

| Buses                          | 5  |

| Reset and Wakeup               | 9  |

| Program/Data RAM               | 10 |

| External FIFO Interface        |    |

| GPIF                           | 14 |

| ECC Generation <sup>[8]</sup>  | 14 |

| USB Uploads and Downloads      | 14 |

| Autopointer Access             | 15 |

| I <sup>2</sup> C Controller    |    |

| CY7C68013A/14A and CY7C68015A/ |    |

| 16A Differences                | 15 |

| Register Summary               | 32 |

| Absolute Maximum Ratings       | 39 |

| Operating Conditions           | 39 |

| Thermal Characteristics        |    |

| DC Characteristics             | 40 |

| AC Electrical Characteristics           | 41 |

|-----------------------------------------|----|

| USB Transceiver                         | 41 |

| Program Memory Read                     | 41 |

| Data Memory Read                        | 42 |

| Data Memory Write                       | 43 |

| PORTC Strobe Feature Timings            |    |

| Slave FIFO Synchronous Read             |    |

| Slave FIFO Synchronous Write            |    |

| Ordering Information                    |    |

| Ordering Code Definitions               | 56 |

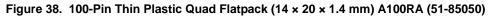

| Package Diagrams                        |    |

| Quad Flat Package No Leads (QFN)        |    |

| Package Design Notes                    | 63 |

| Acronyms                                | 64 |

| Document Conventions                    | 64 |

| Units of Measure                        | 64 |

| Errata                                  | 65 |

| Document History Page                   | 66 |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      | 69 |

| Products                                |    |

| PSoC® Solutions                         | 69 |

| Cypress Developer Community             | 69 |

| Technical Support                       |    |

# Applications

- Portable video recorder

- MPEG/TV conversion

- DSL modems

- ATA interface

- Memory card readers

- Legacy conversion devices

- Cameras

- Scanners

- Wireless LAN

- MP3 players

- Networking

The "Reference Designs" section of the Cypress web site provides additional tools for typical USB 2.0 applications. Each reference design comes complete with firmware source and object code, schematics, and documentation. Visit www.cypress.com for more information.

# **Functional Overview**

## **USB Signaling Speed**

FX2LP operates at two of the three rates defined in the USB Specification Revision 2.0, dated April 27, 2000:

- Full speed, with a signaling bit rate of 12 Mbps

- High speed, with a signaling bit rate of 480 Mbps

FX2LP does not support the Low Speed signaling mode of 1.5 Mbps.

### 8051 Microprocessor

The 8051 microprocessor embedded in the FX2LP family has 256 bytes of register RAM, an expanded interrupt system, three timer/counters, and two USARTs.

### 8051 Clock Frequency

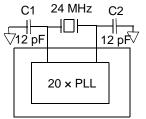

FX2LP has an on-chip oscillator circuit that uses an external 24-MHz (±100 ppm) crystal with the following characteristics:

- Parallel resonant

- Fundamental mode

- 500-µW drive level

- 12-pF (5% tolerance) load capacitors

An on-chip PLL multiplies the 24-MHz oscillator up to 480 MHz, as required by the transceiver/PHY; internal counters divide it down for use as the 8051 clock. The default 8051 clock frequency is 12 MHz. The clock frequency of the 8051 can be changed by the 8051 through the CPUCS register, dynamically.

### Figure 1. Crystal Configuration

12-pF capacitor values assume a trace capacitance of 3 pF per side on a four-layer FR4 PCA

The CLKOUT pin, which can be three-stated and inverted using internal control bits, outputs the 50% duty cycle 8051 clock, at the selected 8051 clock frequency: 48 MHz, 24 MHz, or 12 MHz.

### USARTs

FX2LP contains two standard 8051 USARTs, addressed through Special Function Register (SFR) bits. The USART interface pins are available on separate I/O pins, and are not multiplexed with port pins.

UART0 and UART1 can operate using an internal clock at 230 KBaud with no more than 1% baud rate error. 230 KBaud operation is achieved by an internally derived clock source that generates overflow pulses at the appropriate time. The internal clock adjusts for the 8051 clock rate (48 MHz, 24 MHz, and 12 MHz) such that it always presents the correct frequency for the 230-KBaud operation.<sup>[1]</sup>

### Special Function Registers

Certain 8051 SFR addresses are populated to provide fast access to critical FX2LP functions. These SFR additions are shown in Table 1 on page 6. Bold type indicates nonstandard, enhanced 8051 registers. The two SFR rows that end with "0" and "8" contain bit-addressable registers. The four I/O ports A to D use the SFR addresses used in the standard 8051 for ports 0 to 3, which are not implemented in FX2LP. Because of the faster and more efficient SFR addressing, the FX2LP I/O ports are not addressable in external RAM space (using the MOVX instruction).

## I<sup>2</sup>C Bus

FX2LP supports the I<sup>2</sup>C bus as a master only at 100/400 kHz. SCL and SDA pins have open-drain outputs and hysteresis inputs. These signals must be pulled up to 3.3 V, even if no I<sup>2</sup>C device is connected.

### Buses

All packages, 8-bit or 16-bit "FIFO" bidirectional data bus, multiplexed on I/O ports B and D. 128-pin package: adds 16-bit output-only 8051 address bus, 8-bit bidirectional data bus.

Note

1. 115-KBaud operation is also possible by programming the 8051 SMOD0 or SMOD1 bits to a "1" for UART0, UART1, or both respectively.

### Table 4. Individual FIFO/GPIF Interrupt Sources

| Priority | INT4VEC Value | Source   | Notes                                |

|----------|---------------|----------|--------------------------------------|

| 1        | 80            | EP2PF    | Endpoint 2 programmable flag         |

| 2        | 84            | EP4PF    | Endpoint 4 programmable flag         |

| 3        | 88            | EP6PF    | Endpoint 6 programmable flag         |

| 4        | 8C            | EP8PF    | Endpoint 8 programmable flag         |

| 5        | 90            | EP2EF    | Endpoint 2 empty flag <sup>[3]</sup> |

| 6        | 94            | EP4EF    | Endpoint 4 empty flag                |

| 7        | 98            | EP6EF    | Endpoint 6 empty flag                |

| 8        | 9C            | EP8EF    | Endpoint 8 empty flag                |

| 9        | A0            | EP2FF    | Endpoint 2 full flag                 |

| 10       | A4            | EP4FF    | Endpoint 4 full flag                 |

| 11       | A8            | EP6FF    | Endpoint 6 full flag                 |

| 12       | AC            | EP8FF    | Endpoint 8 full flag                 |

| 13       | B0            | GPIFDONE | GPIF operation complete              |

| 14       | B4            | GPIFWF   | GPIF waveform                        |

If Autovectoring is enabled (AV4EN = 1 in the INTSET-UP register), the FX 2LP substitutes its INT4VEC byte. Therefore, if the high byte ("page") of a jump-table address is preloaded at location 0x0054, the automatically inserted INT4VEC byte at 0x0055 directs the jump to the correct address out of the 14 addresses within the page. When the ISR occurs, the FX2LP pushes the program counter to its stack then jumps to address 0x0053, where it expects to find a "jump" instruction to the interrupt service routine (ISR).

Note

Errata: In Slave FIFO Asynchronous Word Wide mode, if a single word data is transferred from the USB host to EP2, configured as OUT Endpoint (EP) in the first transaction, then the Empty flag behaves incorrectly. This does not happen if the data size is more than one word in the first transaction. For more information, see the "Errata" on page 65.

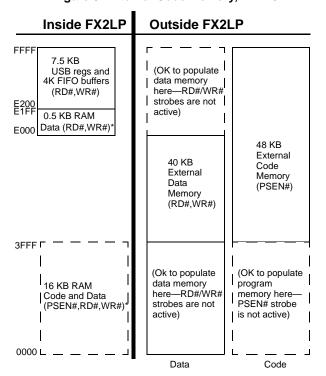

## Program/Data RAM

SizeThe FX2LP has 16 KB of internal program/data RAM, where PSEN#/RD# signals are internally ORed to enable the 8051 to access it as both program and data memory. No USB control registers appears in this space.

Two memory maps are shown in the following diagrams:

Figure 3 on page 10 shows the Internal Code Memory, EA = 0.

Figure 4 on page 11 shows the External Code Memory, EA = 1.

Internal Code Memory, EA = 0

This mode implements the internal 16 KB block of RAM (starting at 0) as combined code and data memory. When external RAM or ROM is added, the external read and write strobes are suppressed for memory spaces that exist inside the chip. This enables the user to connect a 64 KB memory without requiring address decodes to keep clear of internal memory spaces. Only the internal 16 KB and scratch pad 0.5 KB RAM spaces have the following access:

- USB download

- USB upload

- Setup data pointer

- I<sup>2</sup>C interface boot load

### External Code Memory, EA = 1

The bottom 16 KB of program memory is external and therefore the bottom 16 KB of internal RAM is accessible only as a data memory.

### Figure 3. Internal Code Memory, EA = 0

\*SUDPTR, USB upload/download, I<sup>2</sup>C interface boot access

4. If the external clock is powered at the same time as the CY7C680xxA and has a stabilization wait period, it must be added to the 200 µs.

### Default Full-Speed Alternate Settings

### Table 6. Default Full Speed Alternate Settings<sup>[5, 6]</sup>

| Alternate Setting | 0  | 1                | 2                | 3                |

|-------------------|----|------------------|------------------|------------------|

| ep0               | 64 | 64               | 64               | 64               |

| ep1out            | 0  | 64 bulk          | 64 int           | 64 int           |

| ep1in             | 0  | 64 bulk          | 64 int           | 64 int           |

| ep2               | 0  | 64 bulk out (2x) | 64 int out (2×)  | 64 iso out (2×)  |

| ep4               | 0  | 64 bulk out (2x) | 64 bulk out (2x) | 64 bulk out (2x) |

| ep6               | 0  | 64 bulk in (2×)  | 64 int in (2x)   | 64 iso in (2x)   |

| ep8               | 0  | 64 bulk in (2×)  | 64 bulk in (2×)  | 64 bulk in (2×)  |

### Default High Speed Alternate Settings

### Table 7. Default Hi-Speed Alternate Settings<sup>[5, 6]</sup>

| Alternate Setting | 0  | 1                       | 2                 | 3                 |

|-------------------|----|-------------------------|-------------------|-------------------|

| ep0               | 64 | 64                      | 64                | 64                |

| ep1out            | 0  | 512 bulk <sup>[7]</sup> | 64 int            | 64 int            |

| ep1in             | 0  | 512 bulk <sup>[7]</sup> | 64 int            | 64 int            |

| ep2               | 0  | 512 bulk out (2x)       | 512 int out (2x)  | 512 iso out (2x)  |

| ep4               | 0  | 512 bulk out (2x)       | 512 bulk out (2x) | 512 bulk out (2x) |

| ep6               | 0  | 512 bulk in (2x)        | 512 int in (2x)   | 512 iso in (2x)   |

| ep8               | 0  | 512 bulk in (2x)        | 512 bulk in (2×)  | 512 bulk in (2×)  |

### **External FIFO Interface**

### Architecture

The FX2LP slave FIFO architecture has eight 512-byte blocks in the endpoint RAM that directly serve as FIFO memories and are controlled by FIFO control signals (such as IFCLK, SLCS#, SLRD, SLWR, SLOE, PKTEND, and flags).

In operation, some of the eight RAM blocks fill or empty from the SIE, while the others are connected to the I/O transfer logic. The transfer logic takes two forms: the GPIF for internally generated control signals and the slave FIFO interface for externally controlled transfers.

### Master/Slave Control Signals

The FX2LP endpoint FIFOs are implemented as eight physically distinct 256×16 RAM blocks. The 8051/SIE can switch any of the RAM blocks between two domains, the USB (SIE) domain and the 8051-I/O Unit domain. This switching is done virtually instantaneously, giving essentially zero transfer time between

"USB FIFOs" and "Slave FIFOs." Because they are physically the same memory, no bytes are actually transferred between buffers.

At any time, some RAM blocks are filling/emptying with the USB data under SIE control, while other RAM blocks are available to the 8051, the I/O control unit, or both. The RAM blocks operates as single-port in the USB domain, and dual-port in the 8051-I/O domain. The blocks can be configured as single-, double-, triple-, or quad-buffered as previously shown.

The I/O control unit implements either an internal master (M for Master) or external master (S for Slave) interface.

In Master (M) mode, the GPIF internally controls FIFOADR[1..0] to select a FIFO. The RDY pins (two in the 56-pin package, six in the 100-pin and 128-pin packages) can be used as flag inputs from an external FIFO or other logic if desired. The GPIF can be run from either an internally derived clock or externally supplied clock (IFCLK), at a rate that transfers data up to 96 MBytes/s (48

#### Notes

5. "0" means "not implemented."

6. "2x" means "double buffered."

<sup>7.</sup> Even though these buffers are 64 bytes, they are reported as 512 for USB 2.0 compliance. The user must never transfer packets larger than 64 bytes to EP1.

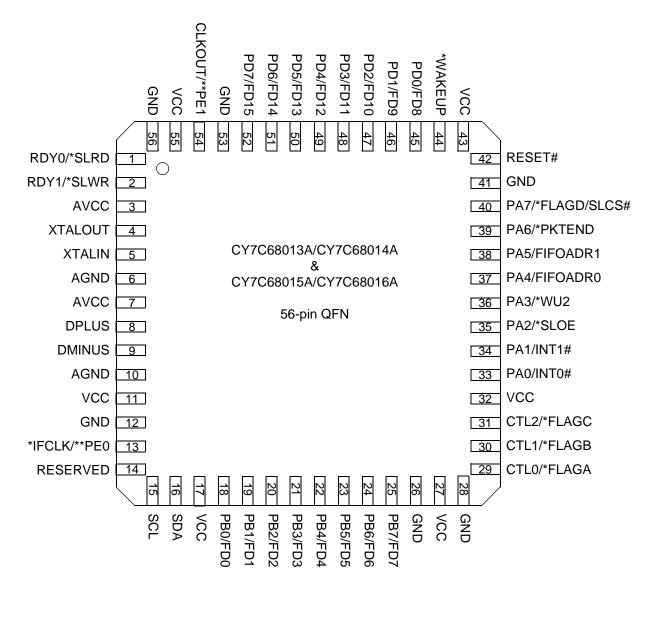

Figure 10. CY7C68013A/14A/15A/16A 56-Pin QFN Pin Assignment

\* denotes programmable polarity \*\* denotes CY7C68015A/CY7C68016A pinout

## CY7C68013A/15A Pin Descriptions

# Table 11. FX2LP Pin Descriptions<sup>[11]</sup>

| 128<br>TQFP | 100<br>TQFP | 56<br>SSOP | 56<br>QFN | 56<br>VFBGA | Name   | Туре   | Default | Reset <sup>[12]</sup> | Description                                                                                                                                                                                                                                           |  |  |  |

|-------------|-------------|------------|-----------|-------------|--------|--------|---------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 10          | 9           | 10         | 3         | 2D          | AVCC   | Power  | N/A     | N/A                   | <b>Analog VCC</b> . Connect this pin to the 3.3 V power source. This signal provides power to the analog section of the chip.                                                                                                                         |  |  |  |

| 17          | 16          | 14         | 7         | 1D          | AVCC   | Power  | N/A     | N/A                   | <b>Analog VCC</b> . Connect this pin to the 3.3 V powe source. This signal provides power to the analog section of the chip.                                                                                                                          |  |  |  |

| 13          | 12          | 13         | 6         | 2F          | AGND   | Ground | N/A     | N/A                   | Analog Ground. Connect to ground with as short a path as possible.                                                                                                                                                                                    |  |  |  |

| 20          | 19          | 17         | 10        | 1F          | AGND   | Ground | N/A     | N/A                   | Analog Ground. Connect to ground with as short a path as possible.                                                                                                                                                                                    |  |  |  |

| 19          | 18          | 16         | 9         | 1E          | DMINUS | I/O/Z  | Z       | N/A                   | USB D- Signal. Connect to the USB D- signal.                                                                                                                                                                                                          |  |  |  |

| 18          | 17          | 15         | 8         | 2E          | DPLUS  | I/O/Z  | Z       | N/A                   | USB D+ Signal. Connect to the USB D+ signal.                                                                                                                                                                                                          |  |  |  |

| 94          | _           | -          | _         | _           | A0     | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 95          | -           | -          | -         | -           | A1     | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 96          | _           | -          | _         | _           | A2     | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 97          | _           | -          | _         | _           | A3     | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 117         | _           | -          | _         | _           | A4     | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 118         | -           | -          | _         | -           | A5     | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 119         | -           | -          | _         | -           | A6     | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 120         | -           | -          | _         | -           | A7     | Output | L       | L                     | <b>8051 Address Bus</b> . This bus is driven at all times. When the 8051 is addressing internal RAM it                                                                                                                                                |  |  |  |

| 126         | -           | -          | _         | -           | A8     | Output | L       | L                     | reflects the internal address.                                                                                                                                                                                                                        |  |  |  |

| 127         | -           | -          | _         | -           | A9     | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 128         | -           | -          | _         | -           | A10    | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 21          | -           | -          | _         | -           | A11    | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 22          | -           | -          | _         | -           | A12    | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 23          | _           | -          | _         | -           | A13    | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 24          | -           | -          | _         | -           | A14    | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 25          | -           | -          | -         | -           | A15    | Output | L       | L                     |                                                                                                                                                                                                                                                       |  |  |  |

| 59          | -           | -          | _         | -           | D0     | I/O/Z  | Z       | Z                     |                                                                                                                                                                                                                                                       |  |  |  |

| 60          | -           | -          | -         | -           | D1     | I/O/Z  | Z       | Z                     |                                                                                                                                                                                                                                                       |  |  |  |

| 61          | -           | -          | -         | -           | D2     | I/O/Z  | Z       | Z                     | <b>8051 Data Bus</b> . This bidirectional bus is high impedance when inactive, input for bus reads,                                                                                                                                                   |  |  |  |

| 62          | -           | -          | -         | -           | D3     | I/O/Z  | Z       | Z                     | and output for bus writes. The data bus is used for                                                                                                                                                                                                   |  |  |  |

| 63          | -           | -          | -         | -           | D4     | I/O/Z  | Z       | Z                     | external 8051 program and data memory. The data                                                                                                                                                                                                       |  |  |  |

| 86          | -           | -          | -         | -           | D5     | I/O/Z  | Z       | Z                     | bus is active only for external bus accesses, and is driven LOW in suspend.                                                                                                                                                                           |  |  |  |

| 87          | -           | -          | _         | —           | D6     | I/O/Z  | Z       | Z                     |                                                                                                                                                                                                                                                       |  |  |  |

| 88          | -           | -          | -         | -           | D7     | I/O/Z  | Z       | Z                     |                                                                                                                                                                                                                                                       |  |  |  |

| 39          | _           | _          | _         | _           | PSEN#  | Output | Н       | Н                     | <b>Program Store Enable</b> . This active LOW signal<br>indicates an 8051 code fetch from external<br>memory. It is active for program memory fetches<br>from 0x4000–0xFFFF when the EA pin is LOW, of<br>from 0x0000–0xFFFF when the EA pin is HIGH. |  |  |  |

Notes

11. Unused inputs must not be left floating. Tie either HIGH or LOW as appropriate. Outputs should only be pulled up or down to ensure signals at power up and in standby. Note also that no pins should be driven while the device is powered down.

12. The Reset column indicates the state of signals during reset (RESET# asserted) or during Power on Reset (POR).

Table 11. FX2LP Pin Descriptions<sup>[11]</sup> (continued)

| 128<br>TQFP | 100<br>TQFP | 56<br>SSOP | 56<br>QFN | 56<br>VFBGA | Name               | Туре  | Default    | Reset <sup>[12]</sup> | Description                                                                                                                                                                             |

|-------------|-------------|------------|-----------|-------------|--------------------|-------|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47          | 37          | 28         | 21        | 4G          | PB3 or<br>FD[3]    | I/O/Z | І<br>(РВЗ) | Z<br>(PB3)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB3</b> is a bidirectional I/O port pin.<br><b>FD[3]</b> is the bidirectional FIFO/GPIF data bus. |

| 54          | 44          | 29         | 22        | 5H          | PB4 or<br>FD[4]    | I/O/Z | І<br>(РВ4) | Z<br>(PB4)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB4</b> is a bidirectional I/O port pin.<br><b>FD[4]</b> is the bidirectional FIFO/GPIF data bus. |

| 55          | 45          | 30         | 23        | 5G          | PB5 or<br>FD[5]    | I/O/Z | l<br>(PB5) | Z<br>(PB5)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB5</b> is a bidirectional I/O port pin.<br><b>FD[5]</b> is the bidirectional FIFO/GPIF data bus. |

| 56          | 46          | 31         | 24        | 5F          | PB6 or<br>FD[6]    | I/O/Z | І<br>(РВ6) | Z<br>(PB6)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB6</b> is a bidirectional I/O port pin.<br><b>FD[6]</b> is the bidirectional FIFO/GPIF data bus. |

| 57          | 47          | 32         | 25        | 6H          | PB7 or<br>FD[7]    | I/O/Z | І<br>(РВ7) | Z<br>(PB7)            | Multiplexed pin whose function is selected by the following bits: IFCONFIG[10].<br><b>PB7</b> is a bidirectional I/O port pin.<br><b>FD[7]</b> is the bidirectional FIFO/GPIF data bus. |

| POR         | ГС          |            |           |             |                    |       |            |                       |                                                                                                                                                                                         |

| 72          | 57          | _          | _         | -           | PC0 or<br>GPIFADR0 | I/O/Z | l<br>(PC0) | Z<br>(PC0)            | Multiplexed pin whose function is selected by<br>PORTCCFG.0<br><b>PC0</b> is a bidirectional I/O port pin.<br><b>GPIFADR0</b> is a GPIF address output pin.                             |

| 73          | 58          | _          | _         | _           | PC1 or<br>GPIFADR1 | I/O/Z | l<br>(PC1) | Z<br>(PC1)            | Multiplexed pin whose function is selected by<br>PORTCCFG.1<br><b>PC1</b> is a bidirectional I/O port pin.<br><b>GPIFADR1</b> is a GPIF address output pin.                             |

| 74          | 59          | 1          | Ι         | -           | PC2 or<br>GPIFADR2 | I/O/Z | l<br>(PC2) | Z<br>(PC2)            | Multiplexed pin whose function is selected by<br>PORTCCFG.2<br><b>PC2</b> is a bidirectional I/O port pin.<br><b>GPIFADR2</b> is a GPIF address output pin.                             |

| 75          | 60          | -          | Ι         | _           | PC3 or<br>GPIFADR3 | I/O/Z | l<br>(PC3) | Z<br>(PC3)            | Multiplexed pin whose function is selected by<br>PORTCCFG.3<br><b>PC3</b> is a bidirectional I/O port pin.<br><b>GPIFADR3</b> is a GPIF address output pin.                             |

| 76          | 61          | Ι          | Ι         | Ι           | PC4 or<br>GPIFADR4 | I/O/Z | l<br>(PC4) | Z<br>(PC4)            | Multiplexed pin whose function is selected by<br>PORTCCFG.4<br><b>PC4</b> is a bidirectional I/O port pin.<br><b>GPIFADR4</b> is a GPIF address output pin.                             |

| 77          | 62          | -          | _         | -           | PC5 or<br>GPIFADR5 | I/O/Z | l<br>(PC5) | Z<br>(PC5)            | Multiplexed pin whose function is selected by<br>PORTCCFG.5<br><b>PC5</b> is a bidirectional I/O port pin.<br><b>GPIFADR5</b> is a GPIF address output pin.                             |

| 78          | 63          | _          | _         | _           | PC6 or<br>GPIFADR6 | I/O/Z | l<br>(PC6) | Z<br>(PC6)            | Multiplexed pin whose function is selected by<br>PORTCCFG.6<br><b>PC6</b> is a bidirectional I/O port pin.<br><b>GPIFADR6</b> is a GPIF address output pin.                             |

| 79          | 64          | _          | _         | _           | PC7 or<br>GPIFADR7 | I/O/Z | l<br>(PC7) | Z<br>(PC7)            | Multiplexed pin whose function is selected by<br>PORTCCFG.7<br><b>PC7</b> is a bidirectional I/O port pin.<br><b>GPIFADR7</b> is a GPIF address output pin.                             |

# Table 11. FX2LP Pin Descriptions<sup>[11]</sup> (continued)

| 128<br>TQFP | 100<br>TQFP | 56<br>SSOP | 56<br>QFN | 56<br>VFBGA | Name             | Туре  | Default    | Reset <sup>[12]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-------------|------------|-----------|-------------|------------------|-------|------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POR         | ΓD          |            |           |             |                  |       |            |                       |                                                                                                                                                                                                                                                                                                                                                                                                              |

| 102         | 80          | 52         | 45        | 8A          | PD0 or<br>FD[8]  | I/O/Z | l<br>(PD0) | Z<br>(PD0)            | Multiplexed pin whose function is selected by the IFCONFIG[10] and EPxFIFOCFG.0 (wordwide) bits.<br><b>FD[8]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                    |

| 103         | 81          | 53         | 46        | 7A          | PD1 or<br>FD[9]  | I/O/Z | l<br>(PD1) | Z<br>(PD1)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[9]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                              |

| 104         | 82          | 54         | 47        | 6B          | PD2 or<br>FD[10] | I/O/Z | l<br>(PD2) | Z<br>(PD2)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[10]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                             |

| 105         | 83          | 55         | 48        | 6A          | PD3 or<br>FD[11] | I/O/Z | l<br>(PD3) | Z<br>(PD3)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[11]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                             |

| 121         | 95          | 56         | 49        | 3B          | PD4 or<br>FD[12] | I/O/Z | l<br>(PD4) | Z<br>(PD4)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[12]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                             |

| 122         | 96          | 1          | 50        | ЗA          | PD5 or<br>FD[13] | I/O/Z | l<br>(PD5) | Z<br>(PD5)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br>FD[13] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                    |

| 123         | 97          | 2          | 51        | 3C          | PD6 or<br>FD[14] | I/O/Z | l<br>(PD6) | Z<br>(PD6)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br>FD[14] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                    |

| 124         | 98          | 3          | 52        | 2A          | PD7 or<br>FD[15] | I/O/Z | l<br>(PD7) | Z<br>(PD7)            | Multiplexed pin whose function is selected by the<br>IFCONFIG[10] and EPxFIFOCFG.0 (wordwide)<br>bits.<br><b>FD[15]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                             |

| Port        | E           |            |           |             |                  |       |            |                       |                                                                                                                                                                                                                                                                                                                                                                                                              |

| 108         | 86          | _          | _         | _           | PE0 or<br>T0OUT  | I/O/Z | l<br>(PE0) | Z<br>(PE0)            | Multiplexed pin whose function is selected by the<br>PORTECFG.0 bit.<br><b>PE0</b> is a bidirectional I/O port pin.<br><b>TOOUT</b> is an active-HIGH signal from 8051<br>Timer-counter0. TOOUT outputs a high level for<br>one CLKOUT clock cycle when Timer0 overflows.<br>If Timer0 is operated in Mode 3 (two separate<br>timer/counters), TOOUT is active when the low byte<br>timer/counter overflows. |

| 109         | 87          | _          | _         | _           | PE1 or<br>T1OUT  | I/O/Z | l<br>(PE1) | Z<br>(PE1)            | Multiplexed pin whose function is selected by the<br>PORTECFG.1 bit.<br><b>PE1</b> is a bidirectional I/O port pin.<br><b>T10UT</b> is an active HIGH signal from 8051<br>Timer-counter1. T10UT outputs a high level for<br>one CLKOUT clock cycle when Timer1 overflows.<br>If Timer1 is operated in Mode 3 (two separate<br>timer/counters), T10UT is active when the low byte<br>timer/counter overflows. |

# Table 11. FX2LP Pin Descriptions<sup>[11]</sup> (continued)

| 128<br>TQFP | 100<br>TQFP | 56<br>SSOP | 56<br>QFN | 56<br>VFBGA | Name                                        | Туре       | Default | Reset <sup>[12]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|-------------|------------|-----------|-------------|---------------------------------------------|------------|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7           | 6           | -          | -         | -           | RDY3                                        | Input      | N/A     | N/A                   | RDY3 is a GPIF input signal.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8           | 7           | -          | -         | —           | RDY4                                        | Input      | N/A     | N/A                   | RDY4 is a GPIF input signal.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9           | 8           | -          |           | -           | RDY5                                        | Input      | N/A     | N/A                   | RDY5 is a GPIF input signal.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 69          | 54          | 36         | 29        | 7H          | CTL0 or<br>FLAGA                            | O/Z        | н       | L                     | Multiplexed pin whose function is selected by the<br>following bits:<br>IFCONFIG[10].<br><b>CTL0</b> is a GPIF control output.<br><b>FLAGA</b> is a programmable slave-FIFO output<br>status flag signal.<br>Defaults to programmable for the FIFO selected by<br>the FIFOADR[1:0] pins.                                                                                                                                                     |

| 70          | 55          | 37         | 30        | 7G          | CTL1 or<br>FLAGB                            | O/Z        | н       | L                     | Multiplexed pin whose function is selected by the<br>following bits:<br>IFCONFIG[10].<br><b>CTL1</b> is a GPIF control output.<br><b>FLAGB</b> is a programmable slave-FIFO output<br>status flag signal.<br>Defaults to FULL for the FIFO selected by the<br>FIFOADR[1:0] pins.                                                                                                                                                             |

| 71          | 56          | 38         | 31        | 8H          | CTL2 or<br>FLAGC                            | O/Z        | н       | L                     | Multiplexed pin whose function is selected by the<br>following bits:<br>IFCONFIG[10].<br><b>CTL2</b> is a GPIF control output.<br><b>FLAGC</b> is a programmable slave-FIFO output<br>status flag signal.<br>Defaults to EMPTY for the FIFO selected by the<br>FIFOADR[1:0] pins.                                                                                                                                                            |

| 66          | 51          | -          | _         | —           | CTL3                                        | O/Z        | Н       | L                     | CTL3 is a GPIF control output.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 67          | 52          | -          | -         | —           | CTL4                                        | Output     | Н       | L                     | CTL4 is a GPIF control output.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 98          | 76          | -          | Ι         | -           | CTL5                                        | Output     | Н       | L                     | CTL5 is a GPIF control output.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 32          | 26          | 20         | 13        | 2G          | IFCLK on<br>CY7C68013A<br>and<br>CY7C68014A | I/O/Z      | Z       | Z                     | Interface Clock, used for synchronously clocking<br>data into or out of the slave FIFOs. IFCLK also<br>serves as a timing reference for all slave FIFO<br>control signals and GPIF. When internal clocking is<br>used (IFCONFIG.7 = 1) the IFCLK pin can be<br>configured to output 30/48 MHz by bits<br>IFCONFIG.5 and IFCONFIG.6. IFCLK may be<br>inverted, whether internally or externally sourced,<br>by setting the bit IFCONFIG.4 =1. |

|             |             |            |           |             | PE0 on<br>CY7C68015A<br>and<br>CY7C68016A   | -<br>I/O/Z | <br>I   | Z                     | PE0 is a bidirectional I/O port pin.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 28          | 22          | _          | _         | _           | INT4                                        | Input      | N/A     | N/A                   | <b>INT4</b> is the 8051 INT4 interrupt request input signal. The INT4 pin is edge-sensitive, active HIGH.                                                                                                                                                                                                                                                                                                                                    |

| 106         | 84          | _          | _         | _           | INT5#                                       | Input      | N/A     | N/A                   | <b>INT5#</b> is the 8051 INT5 interrupt request input signal. The INT5 pin is edge-sensitive, active LOW.                                                                                                                                                                                                                                                                                                                                    |

| 31          | 25          | -          | _         | _           | T2                                          | Input      | N/A     | N/A                   | <b>T2</b> is the active HIGH T2 input signal to 8051<br>Timer2, which provides the input to Timer2 when<br>C/T2 = 1. When $C/T2 = 0$ , Timer2 does not use this<br>pin.                                                                                                                                                                                                                                                                      |

Table 11. FX2LP Pin Descriptions<sup>[11]</sup> (continued)

| 128<br>TQFP | 100<br>TQFP | 56<br>SSOP | 56<br>QFN | 56<br>VFBGA | Name     | Туре   | Default | Reset <sup>[12]</sup>           | Description                                                                                                                                                                                                                                                                |

|-------------|-------------|------------|-----------|-------------|----------|--------|---------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30          | 24          | -          | _         | _           | T1       | Input  | N/A     | N/A                             | <b>T1</b> is the active HIGH T1 signal for 8051 Timer1, which provides the input to Timer1 when C/T1 is 1. When C/T1 is 0, Timer1 does not use this bit.                                                                                                                   |

| 29          | 23          | _          | _         | -           | ТО       | Input  | N/A     | N/A                             | <b>T0</b> is the active HIGH T0 signal for 8051 Timer0, which provides the input to Timer0 when C/T0 is 1. When C/T0 is 0, Timer0 does not use this bit.                                                                                                                   |

| 53          | 43          | _          | _         | Ι           | RXD1     | Input  | N/A     | N/A                             | <b>RXD1</b> is an active HIGH input signal for 8051<br>UART1, which provides data to the UART in all<br>modes.                                                                                                                                                             |

| 52          | 42          | Ι          | Ι         | -           | TXD1     | Output | н       | L                               | <b>TXD1</b> is an active HIGH output pin from 8051<br>UART1, which provides the output clock in sync<br>mode, and the output data in async mode.                                                                                                                           |

| 51          | 41          | -          | -         | _           | RXD0     | Input  | N/A     | N/A                             | <b>RXD0</b> is the active HIGH RXD0 input to 8051<br>UART0, which provides data to the UART in all<br>modes.                                                                                                                                                               |

| 50          | 40          | _          | _         | _           | TXD0     | Output | Н       | L                               | <b>TXD0</b> is the active HIGH TXD0 output from 8051<br>UART0, which provides the output clock in sync<br>mode, and the output data in async mode.                                                                                                                         |

| 42          |             | _          | _         | _           | CS#      | Output | н       | Н                               | <b>CS#</b> is the active LOW chip select for external memory.                                                                                                                                                                                                              |

| 41          | 32          | _          | _         | -           | WR#      | Output | Н       | Н                               | WR# is the active LOW write strobe output for external memory.                                                                                                                                                                                                             |

| 40          | 31          | _          | _         | _           | RD#      | Output | Н       | Н                               | <b>RD#</b> is the active LOW read strobe output for external memory.                                                                                                                                                                                                       |

| 38          |             | _          | -         | -           | OE#      | Output | Н       | Н                               | <b>OE#</b> is the active LOW output enable for external memory.                                                                                                                                                                                                            |

| 33          | 27          | 21         | 14        | 2H          | Reserved | Input  | N/A     | N/A                             | Reserved. Connect to ground.                                                                                                                                                                                                                                               |

| 101         | 79          | 51         | 44        | 7B          | WAKEUP   | Input  | N/A     | N/A                             | <b>USB Wakeup</b> . If the 8051 is in suspend, asserting this pin starts up the oscillator and interrupts the 8051 to enable it to exit the suspend mode. Holding WAKEUP asserted inhibits the EZ-USB chip from suspending. This pin has programmable polarity (WAKEUP.4). |

| 36          | 29          | 22         | 15        | 3F          | SCL      | OD     | Z       | Z<br>(if<br>booting<br>is done) | <b>Clock</b> for the $I^2C$ interface. Connect to VCC with a 2.2-k $\Omega$ resistor, even if no $I^2C$ peripheral is attached.                                                                                                                                            |

| 37          | 30          | 23         | 16        | 3G          | SDA      | OD     | Z       | Z<br>(if<br>booting<br>is done) | Data for I <sup>2</sup> C compatible interface. Connect to VCC with a 2.2-k $\Omega$ resistor, even if no I <sup>2</sup> C compatible peripheral is attached.                                                                                                              |

| 2           | 1           | 6          | 55        | 5A          | VCC      | Power  | N/A     | N/A                             | VCC. Connect to the 3.3-V power source.                                                                                                                                                                                                                                    |

| 26          | 20          | 18         | 11        | 1G          | VCC      | Power  | N/A     | N/A                             | VCC. Connect to the 3.3-V power source.                                                                                                                                                                                                                                    |

| 43          | 33          | 24         | 17        | 7E          | VCC      | Power  | N/A     | N/A                             | VCC. Connect to the 3.3-V power source.                                                                                                                                                                                                                                    |

| 48          | 38          | -          | -         | _           | VCC      | Power  | N/A     | N/A                             | VCC. Connect to 3.3-V power source.                                                                                                                                                                                                                                        |

| 64          | 49          | 34         | 27        | 8E          | VCC      | Power  | N/A     | N/A                             | VCC. Connect to the 3.3-V power source.                                                                                                                                                                                                                                    |

| 68          | 53          | -          | -         | _           | VCC      | Power  | N/A     | N/A                             | VCC. Connect to the 3.3-V power source.                                                                                                                                                                                                                                    |

| 81          | 66          | 39         | 32        | 5C          | VCC      | Power  | N/A     | N/A                             | VCC. Connect to the 3.3-V power source.                                                                                                                                                                                                                                    |

# CY7C68013A, CY7C68014A CY7C68015A, CY7C68016A

### Table 12. FX2LP Register Summary (continued)

|              |        | -                          |                                                                   |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|--------------|--------|----------------------------|-------------------------------------------------------------------|--------------------|-----------------------|----------------------|----------------------|---------|-----------------|-----------------|--------------------|----------------------|----------|

| Hex          | Size   |                            | Description                                                       | b7                 | b6                    | b5                   | b4                   | b3      | b2              | b1              | b0                 | Default              | Access   |

| E6A0         | 1      | EP0CS                      | Endpoint 0 Control and Sta-<br>tus                                | HSNAK              | 0                     | 0                    | 0                    | 0       | 0               | BUSY            | STALL              | 10000000             | bbbbbbrb |

| E6A1         | 1      | EP1OUTCS                   | Endpoint 1 OUT Control<br>and Status                              | 0                  | 0                     | 0                    | 0                    | 0       | 0               | BUSY            | STALL              | 00000000             | bbbbbbrb |

| E6A2         | 1      | EP1INCS                    | Endpoint 1 IN Control and Status                                  | 0                  | 0                     | 0                    | 0                    | 0       | 0               | BUSY            | STALL              | 00000000             | bbbbbbrb |

| E6A3         | 1      | EP2CS                      | Endpoint 2 Control and Sta-<br>tus                                | 0                  | NPAK2                 | NPAK1                | NPAK0                | FULL    | EMPTY           | 0               | STALL              | 00101000             | rrrrrb   |

| E6A4         | 1      | EP4CS                      | Endpoint 4 Control and Sta-<br>tus                                | 0                  | 0                     | NPAK1                | NPAK0                | FULL    | EMPTY           | 0               | STALL              | 00101000             | rrrrrb   |

| E6A5         | 1      | EP6CS                      | Endpoint 6 Control and Sta-<br>tus                                | 0                  | NPAK2                 | NPAK1                | NPAK0                | FULL    | EMPTY           | 0               | STALL              | 00000100             | rrrrrb   |

| E6A6         | 1      | EP8CS                      | Endpoint 8 Control and Sta-<br>tus                                | 0                  | 0                     | NPAK1                | NPAK0                | FULL    | EMPTY           | 0               | STALL              | 00000100             | rrrrrb   |

| E6A7         | 1      | EP2FIFOFLGS                | Endpoint 2 slave FIFO<br>Flags                                    | 0                  | 0                     | 0                    | 0                    | 0       | PF              | EF              | FF                 | 00000010             | R        |

| E6A8         | 1      | EP4FIFOFLGS                | Endpoint 4 slave FIFO<br>Flags                                    | 0                  | 0                     | 0                    | 0                    | 0       | PF              | EF              | FF                 | 00000010             | R        |

| E6A9         | 1      | EP6FIFOFLGS                | Endpoint 6 slave FIFO<br>Flags                                    | 0                  | 0                     | 0                    | 0                    | 0       | PF              | EF              | FF                 | 00000110             | R        |

| E6AA         | 1      | EP8FIFOFLGS                | Endpoint 8 slave FIFO<br>Flags                                    | 0                  | 0                     | 0                    | 0                    | 0       | PF              | EF              | FF                 | 00000110             | R        |

| E6AB         | 1      | EP2FIFOBCH                 | Endpoint 2 slave FIFO<br>total byte count H                       | 0                  | 0                     | 0                    | BC12                 | BC11    | BC10            | BC9             | BC8                | 00000000             | R        |

| E6AC         | 1      | EP2FIFOBCL                 | Endpoint 2 slave FIFO                                             | BC7                | BC6                   | BC5                  | BC4                  | BC3     | BC2             | BC1             | BC0                | 00000000             | R        |

| E6AD         | 1      | EP4FIFOBCH                 | total byte count L<br>Endpoint 4 slave FIFO<br>total byte count H | 0                  | 0                     | 0                    | 0                    | 0       | BC10            | BC9             | BC8                | 00000000             | R        |

| E6AE         | 1      | EP4FIFOBCL                 | Endpoint 4 slave FIFO                                             | BC7                | BC6                   | BC5                  | BC4                  | BC3     | BC2             | BC1             | BC0                | 00000000             | R        |

| E6AF         | 1      | EP6FIFOBCH                 | total byte count L<br>Endpoint 6 slave FIFO<br>total byte count H | 0                  | 0                     | 0                    | 0                    | BC11    | BC10            | BC9             | BC8                | 00000000             | R        |

| E6B0         | 1      | EP6FIFOBCL                 | Endpoint 6 slave FIFO                                             | BC7                | BC6                   | BC5                  | BC4                  | BC3     | BC2             | BC1             | BC0                | 00000000             | R        |

| E6B1         | 1      | EP8FIFOBCH                 | total byte count L<br>Endpoint 8 slave FIFO                       | 0                  | 0                     | 0                    | 0                    | 0       | BC10            | BC9             | BC8                | 00000000             | R        |

| E6B2         | 1      | EP8FIFOBCL                 | total byte count H<br>Endpoint 8 slave FIFO                       | BC7                | BC6                   | BC5                  | BC4                  | BC3     | BC2             | BC1             | BC0                | 00000000             | R        |

| E6B3         | 1      | SUDPTRH                    | total byte count L<br>Setup Data Pointer high                     | A15                | A14                   | A13                  | A12                  | A11     | A10             | A9              | A8                 | xxxxxxx              | RW       |

| E6B4         | 1      | SUDPTRL                    | address byte<br>Setup Data Pointer low ad-                        | A7                 | A6                    | A5                   | A4                   | A3      | A2              | A1              | 0                  | xxxxxx0              | bbbbbbbr |

| E6B5         | 1      | SUDPTRCTL                  | dress byte<br>Setup Data Pointer Auto                             | 0                  | 0                     | 0                    | 0                    | 0       | 0               | 0               | SDPAUTO            | 00000001             | RW       |

|              |        |                            | Mode                                                              |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

| E6B8         | 2      | reserved<br>SET-UPDAT      | 8 bytes of setup data                                             | D7                 | D6                    | D5                   | D4                   | D3      | D2              | D1              | D0                 | xxxxxxxx             | R        |

| EODO         | 0      | SET-OFDAT                  | SET-UPDAT[0] =                                                    | Di                 | 00                    | D5                   | D4                   | 03      | DZ              |                 | DU                 | ******               | ĸ        |

|              |        |                            | bmRequestType                                                     |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        |                            | SET-UPDAT[1] =<br>bmRequest                                       |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        |                            | SET-UPDAT[2:3] = wValue                                           |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        |                            | SET-UPDAT[4:5] = wIndex                                           |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        |                            | SET-UPDAT[6:7] =                                                  |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        |                            | wLength                                                           |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

|              |        | GPIF                       |                                                                   |                    |                       |                      |                      |         | FIFOLUDA        | 5150004         | 5150000            | 44400400             | 514/     |

| E6C0<br>E6C1 | 1<br>1 | GPIFWFSELECT<br>GPIFIDLECS | Waveform Selector<br>GPIF Done, GPIF IDLE                         | SINGLEWR1<br>DONE  | SINGLEWR0<br>0        | 0                    | SINGLERD0            | FIFOWR1 | FIFOWR0<br>0    | FIFORD1<br>0    | FIFORD0<br>IDLEDRV | 11100100<br>10000000 | RW<br>RW |

|              |        |                            | drive mode                                                        |                    |                       |                      |                      |         |                 |                 |                    |                      |          |

| E6C2         | 1      | GPIFIDLECTL                | Inactive Bus, CTL states                                          | 0                  | 0                     | CTL5                 | CTL4                 | CTL3    | CTL2            | CTL1            | CTL0               | 11111111             |          |

| E6C3         | 1      | GPIFCTLCFG                 | CTL Drive Type                                                    | TRICTL             | 0                     | CTL5                 | CTL4                 | CTL3    | CTL2            | CTL1            | CTL0               | 00000000             |          |

| E6C4         | 1      | GPIFADRH <sup>[13]</sup>   | GPIF Address H                                                    | 0                  | 0                     | 0                    | 0                    | 0       | 0               | 0               | GPIFA8             | 00000000             |          |

| E6C5         | 1      |                            | GPIF Address L                                                    | GPIFA7             | GPIFA6                | GPIFA5               | GPIFA4               | GPIFA3  | GPIFA2          | GPIFA1          | GPIFA0             | 00000000             | RW       |

| E6C6         | 1      | FLOWSTATE<br>FLOWSTATE     | Flowstate Enable and                                              | FSE                | 0                     | 0                    | 0                    | 0       | FS2             | FS1             | FS0                | 00000000             | brrrrbbb |

| E6C7         | 1      | FLOWLOGIC                  | Selector<br>Flowstate Logic                                       | LFUNC1             | LFUNC0                | TERMA2               | TERMA1               | TERMA0  | TERMB2          | TERMB1          | TERMB0             | 00000000             | RW       |

| E6C8         | 1      | FLOWEQ0CTL                 | CTL-Pin States in<br>Flowstate                                    | CTL0E3             | CTL0E2                | CTL0E1/<br>CTL5      | CTL0E0/<br>CTL4      | CTL3    | CTL2            | CTL1            | CTL0               | 00000000             |          |

| E6C9         | 1      | FLOWEQ1CTL                 | (when Logic = 0)<br>CTL-Pin States in Flow-                       | CTL0E3             | CTL0E2                | CTL0E1/<br>CTL5      | CTLOE0/              | CTL3    | CTL2            | CTL1            | CTL0               | 00000000             | RW       |

| F            | 4      |                            | state (when Logic = 1)                                            |                    |                       |                      | CTL4                 |         |                 |                 |                    | 00010010             | DW/      |

| E6CA<br>E6CB | 1      | FLOWHOLDOFF<br>FLOWSTB     | Holdoff Configuration<br>Flowstate Strobe                         | HOPERIOD3<br>SLAVE | HOPERIOD2<br>RDYASYNC | HOPERIOD1<br>CTLTOGL | HOPERIOD0<br>SUSTAIN |         | HOCTL2<br>MSTB2 | HOCTL1<br>MSTB1 | HOCTL0<br>MSTB0    | 00010010             |          |

| -000         | Ľ      |                            | Configuration                                                     |                    | ND ING ING            | SILIUGL              | SUCIAIN              | 3       |                 |                 |                    | 00000                |          |

| E6CC         |        | FLOWSTBEDGE                | Flowstate Rising/Falling<br>Edge Configuration                    | 0                  | 0                     | 0                    | 0                    | 0       | 0               | FALLING         | RISING             | 00000001             | rrrrrbb  |

| E6CD         |        | FLOWSTBPERIOD              | Master-Strobe Half-Period                                         |                    | D6                    | D5                   | D4                   | D3      | D2              | D1              | D0                 | 00000010             |          |

| E6CE         | 1      | GPIFTCB3 <sup>[13]</sup>   | GPIF Transaction Count<br>Byte 3                                  | TC31               | TC30                  | TC29                 | TC28                 | TC27    | TC26            | TC25            | TC24               | 00000000             | RW       |

|              |        |                            | 5,100                                                             | 1                  |                       | 1                    | 1                    |         | 1               | 1               | 1                  | I                    | 1        |

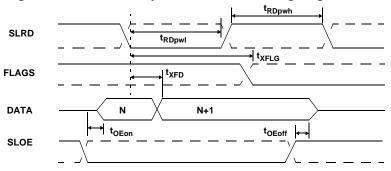

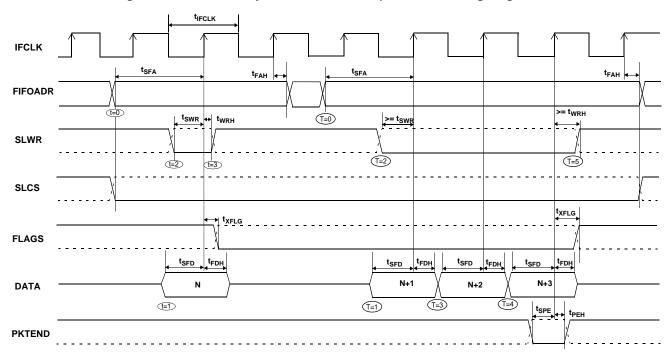

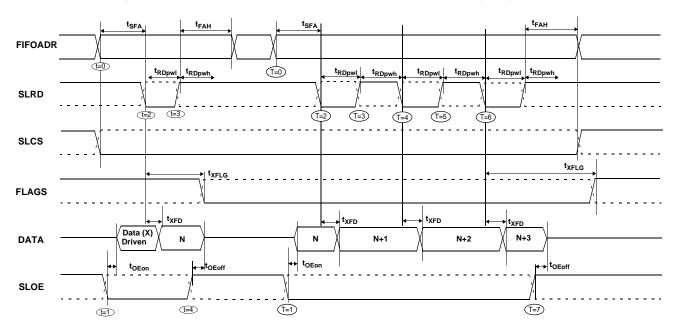

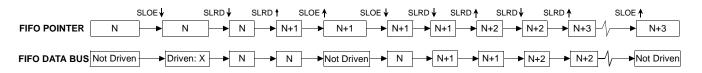

| Parameter          | Description                                 | Min   | Max  | Unit |

|--------------------|---------------------------------------------|-------|------|------|

| t <sub>IFCLK</sub> | IFCLK period                                | 20.83 | 200  | ns   |

| t <sub>SRD</sub>   | SLRD to clock setup time                    | 12.7  | -    | ns   |

| t <sub>RDH</sub>   | Clock to SLRD hold time                     | 3.7   | -    | ns   |

| t <sub>OEon</sub>  | SLOE turn on to FIFO data valid             | _     | 10.5 | ns   |

| t <sub>OEoff</sub> | SLOE turn off to FIFO data hold             | -     | 10.5 | ns   |

| t <sub>XFLG</sub>  | Clock to FLAGS output propagation delay     | -     | 13.5 | ns   |

| t <sub>XFD</sub>   | Clock to FIFO data output propagation delay | _     | 15   | ns   |