Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                                       |

|---------------------------------|---------------------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                              |

| Core Processor                  | MIPS-II                                                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                                        |

| Speed                           | 150MHz                                                                                |

| Co-Processors/DSP               | -                                                                                     |

| RAM Controllers                 | SDRAM                                                                                 |

| Graphics Acceleration           | No                                                                                    |

| Display & Interface Controllers | •                                                                                     |

| Ethernet                        | -                                                                                     |

| SATA                            | -                                                                                     |

| USB                             | -                                                                                     |

| Voltage - I/O                   | 3.3V                                                                                  |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                                       |

| Security Features               | -                                                                                     |

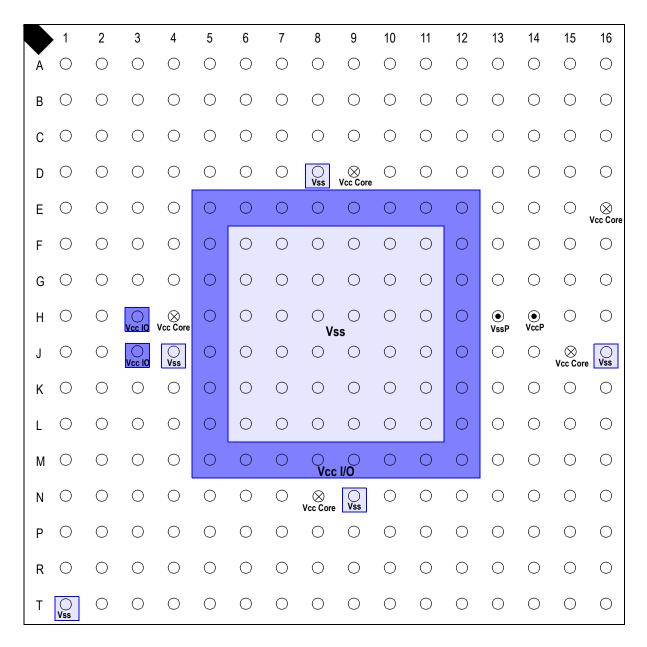

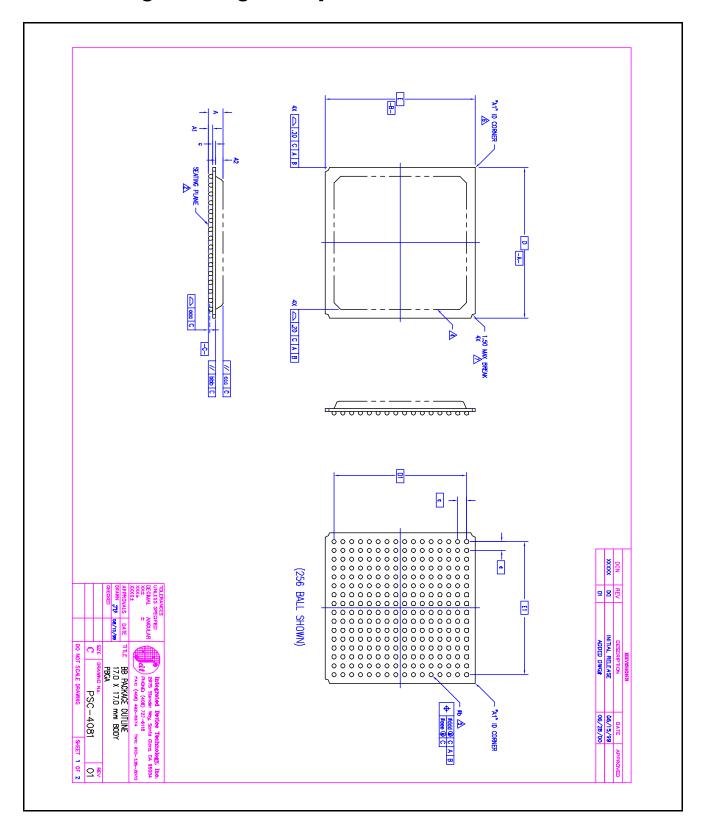

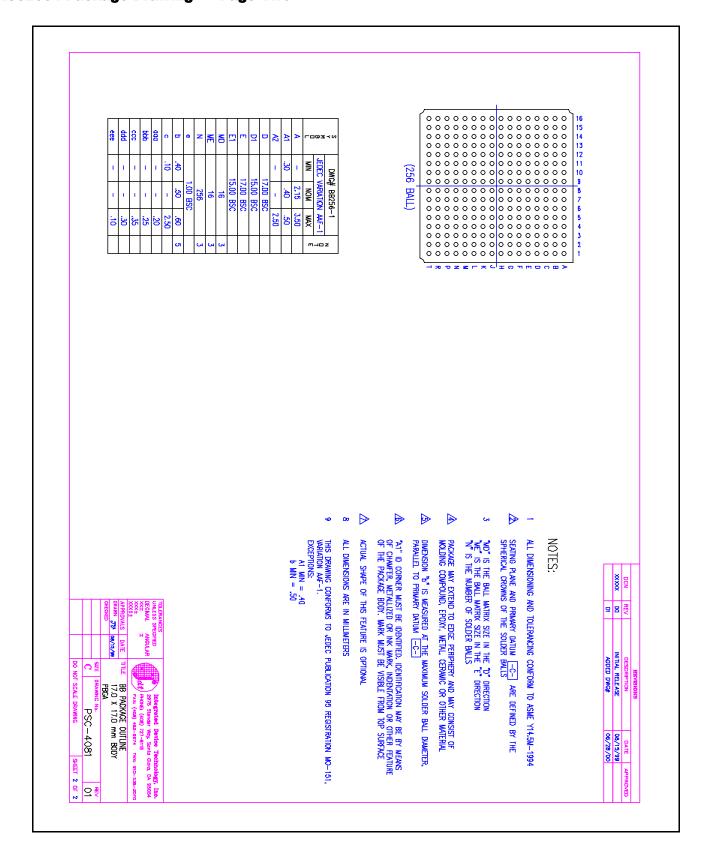

| Package / Case                  | 256-BGA                                                                               |

| Supplier Device Package         | 256-PBGA (17x17)                                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/renesas-electronics-america/idt79rc32v334-150bbg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4 DMA Channels

- 4 general purpose DMA, each with endianess swappers and byte lane data alignment

- Supports scatter/gather, chaining via linked lists of records

- Supports memory-to-memory, memory-to-I/O, memory-to-PCI, PCI-to-PCI, and I/O-to-I/O transfers

- Supports unaligned transfers

- Supports burst transfers

- Programmable DMA bus transactions burst size (up to 16 bytes)

### PCI Bus Interface

- 32-bit PCI, up to 66 MHz

- Revision 2.2 compatible

- Target or master

- Host or satellite

- Three slot PCI arbiter

- Serial EEPROM support, for loading configuration registers

- Off-the-shelf development tools

- JTAG Interface (IEEE Std. 1149.1 compatible)

- 256-ball BGA (1.0mm spacing)

- 3.3V operation with 5V tolerant I/O

- EJTAG in-circuit emulator interface

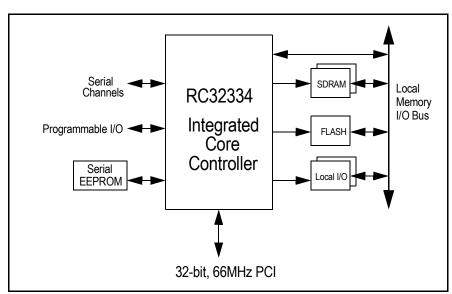

### **Device Overview**

The IDT RC32334 device is an integrated processor based on the RC32300 CPU core. This product incorporates a high-performance, low-cost 32-bit CPU core with functionality common to a large number of embedded applications. The RC32334 integrates these functions to enable the use of low-cost PC commodity market memory and I/O devices, allowing the aggressive price/performance characteristics of the CPU to be realized quickly into low-cost systems.

#### **CPU Execution Core**

The RC32334 integrates the RISCore32300, the same CPU core found in the award-winning RC32364 microprocessor.

The RISCore32300 implements the Enhanced MIPS-II ISA. Thus, it is upwardly compatible with applications written for a wide variety of MIPS architecture processors, and it is kernel compatible with the modern operating systems that support IDT's 64-bit RISController product family.

The RISCore32300 was explicitly defined and designed for integrated processor products such as the RC32334. Key attributes of the execution core found within this product include:

- High-speed, 5-stage scalar pipeline executes to 150MHz. This high performance enables the RC32334 to perform a variety of performance intensive tasks, such as routing, DSP algorithms, etc.

- 32-bit architecture with enhancements of key capabilities. Thus, the RC32334 can execute existing 32-bit programs, while enabling designers to take advantage of recent advances in CPU architecture.

- Count leading-zeroes/ones. These instructions are common to a wide variety of tasks, including modem emulation, voice over IP compression and decompression, etc.

- Cache PREFetch instruction support, including a specialized form intended to help memory coherency. System programmers can allocate and stage the use of memory bandwidth to achieve maximum performance.

- 8kB of 2-way set associative instruction cache

Figure 2 RC32334 Based System Diagram

- 2KB of 2-way set associative data cache, capable of write-back and write-through operation.

- Cache locking per line to speed real-time systems and critical system functions

- On-chip TLB to enable multi-tasking in modern operating systems

- EJTAG interface to enable sophisticated low-cost in-circuit emulation.

### **Synchronous-DRAM Interface**

The RC32334 integrates a SDRAM controller which provides direct control of system SyncDRAM running at speeds to 75MHz.

Key capabilities of the SDRAM controller include:

- Direct control of 4 banks of SDRAM (up to 2 64-bit wide DIMMs)

- On-chip page comparators optimize access latency.

- ◆ Speeds to 75MHz

- Programmable address map.

- Supports 16, 64, 128, 256, or 512Mb SDRAM devices

- Automatic refresh generation driven by on-chip timer

- Support for discrete devices, SODIMM, or DIMM modules.

Thus, systems can take advantage of the full range of commodity memory that is available, enabling system optimization for cost, realestate, or other attributes.

### Local Memory and I/O Controller

The local memory and I/O controller implements direct control of external memory devices, including the boot ROM as well as other memory areas, and also implements direct control of external peripherals.

The local memory controller is highly flexible, allowing a wide range of devices to be directly controlled by the RC32334 processor. For example, a system can be built using an 8-bit boot ROM, 16-bit FLASH cards (possibly on PCMCIA), a 32-bit SRAM or dual-port memory, and a variety of low-cost peripherals.

Key capabilities include:

- Direct control of EPROM, FLASH, RAM, and dual-port memories

- 6 chip-select outputs, supporting up to 64MB per memory space

- ◆ Supports mixture of 8-, 16-, and 32-bit wide memory regions

- Flexible timing protocols allow direct control of a wide variety of devices

- Programmable address map for 2 chip selects

- Automatic wait state generation.

# **PCI Bus Bridge**

In order to leverage the wide availability of low-cost peripherals for the PC market as well as to simplify the design of add-in functions, the RC32334 integrates a full 32-bit PCI bus bridge. Key attributes of this bridge include:

- 66 MHz operation

- PCI revision 2.2 compliant

- Programmable address mappings between CPU/Local memory and PCI memory and I/O

- On-chip PCI arbiter

- Extensive buffering allows PCI to operate concurrently with local memory transfers

- Selectable byte-ordering swapper

- ◆ 5V tolerant I/O.

### **On-Chip DMA Controller**

To minimize CPU exception handling and maximize the efficiency of system bandwidth, the RC32334 integrates a very sophisticated 4-channel DMA controller on chip.

The RC32334 DMA controller is capable of:

- Chaining and scatter/gather support through the use of a flexible, linked list of DMA transaction descriptors

- Capable of memory<->memory, memory<->I/O, and PCI<->memory DMA

- Unaligned transfer support

- Byte, halfword, word, quadword DMA support.

### **On-Chip Peripherals**

The RC32334 also integrates peripherals that are common to a wide variety of embedded systems.

- Dual channel 16550 compatible UARTs, with modem control interface on one channel.

- SPI master mode interface for direct interface to EEPROM, A/D, etc.

- Interrupt Controller to speed interrupt decode and management

- Four 32-bit on-chip Timer/Counters

- Programmable I/O module

# **Debug Support**

To facilitate rapid time to market, the RC32334 provides extensive support for system debug.

First and foremost, this product integrates an EJTAG in-circuit emulation module, allowing a low-cost emulator to interoperate with programs executing on the controller. By using an augmented JTAG interface, the RC32334 is able to reuse the same low-cost emulators developed around the RC32364 CPU.

Secondly, the RC32334 implements additional reporting signals intended to simplify the task of system debugging when using a logic analyzer. This product allows the logic analyzer to differentiate transactions initiated by DMA from those initiated by the CPU and further allows CPU transactions to be sorted into instruction fetches vs. data fetches.

Finally, the RC32334 implements a full boundary scan capability, allowing board manufacturing diagnostics and debug.

# **Pin Description Table**

The following table lists the pins provided on the RC32334. Note that those pin names followed by "\_n" are active-low signals. All external pull-ups and pull-downs require  $10 \text{ k}\Omega$  resistor.

| Name               | Туре   | Reset<br>State<br>Status | Drive<br>Strength<br>Capability |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                  | Descripti          | on                    |                          |  |  |  |  |

|--------------------|--------|--------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|--------------------------|--|--|--|--|

| Local System Inter | face   |                          |                                 | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                  |                    |                       |                          |  |  |  |  |

| mem_data[31:0]     | I/O    | Z                        | High                            | Local System I<br>Primary data bu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>Data Bus</b><br>s for memory. I/O and SD                                                                                                                                                                                                                                                                                                                      | DRAM.              |                       |                          |  |  |  |  |

| mem_addr[25:2]     | I/O    | [25:10] Z<br>[9:2] L     | [25:17] Low<br>[16:2] High      | These signals p<br>each word data,<br>tion type. The ta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>lemory Address Bus</b> These signals provide the Memory or DRAM address, during a Memory or DRAM bus transaction. During ach word data, the address increments either in linear or sub-block ordering, depending on the transaction type. The table below indicates how the memory write enable signals are used to address discreet nemory port width types. |                    |                       |                          |  |  |  |  |

|                    |        |                          |                                 | Port Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pin Signals<br>mem_we_n[3]                                                                                                                                                                                                                                                                                                                                       | mem_we_n[2]        | mem_we_n[1]           | mem_we_n[0]              |  |  |  |  |

|                    |        |                          |                                 | DMA (32-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | mem_we_n[3]                                                                                                                                                                                                                                                                                                                                                      | mem_we_n[2]        | mem_we_n[1]           | mem_we_n[0]              |  |  |  |  |

|                    |        |                          |                                 | 32-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | mem_we_n[3]                                                                                                                                                                                                                                                                                                                                                      | mem_we_n[2]        | mem_we_n[1]           | mem_we_n[0]              |  |  |  |  |

|                    |        |                          |                                 | 16-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Byte High Write Enable                                                                                                                                                                                                                                                                                                                                           | mem_addr[1]        | Not Used (Driven Low) | Byte Low Write<br>Enable |  |  |  |  |

|                    |        |                          |                                 | 8-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Not Used (Driven High)                                                                                                                                                                                                                                                                                                                                           | mem_addr[1]        | mem_addr[0]           | Byte Write Enable        |  |  |  |  |

|                    |        |                          |                                 | mem_addr[22] Alternate function: reset_boot_mode[1]. mem_addr[20] Alternate function: reset_boot_mode[0]. mem_addr[19] Alternate function: modebit [9]. mem_addr[18] Alternate function: modebit [8]. mem_addr[17] Alternate function: modebit [7]. mem_addr[16] Alternate function: sdram_addr[16]. mem_addr[15] Alternate function: sdram_addr[15]. mem_addr[14] Alternate function: sdram_addr[14]. mem_addr[13] Alternate function: sdram_addr[13]. mem_addr[10] Alternate function: sdram_addr[10]. mem_addr[9] Alternate function: sdram_addr[9]. mem_addr[7] Alternate function: sdram_addr[8]. mem_addr[6] Alternate function: sdram_addr[6]. mem_addr[5] Alternate function: sdram_addr[6]. mem_addr[4] Alternate function: sdram_addr[6]. mem_addr[4] Alternate function: sdram_addr[6]. mem_addr[4] Alternate function: sdram_addr[4]. mem_addr[3] Alternate function: sdram_addr[4]. mem_addr[3] Alternate function: sdram_addr[3]. |                                                                                                                                                                                                                                                                                                                                                                  |                    |                       |                          |  |  |  |  |

| mem_cs_n[5:0]      | Output | Н                        | Low with internal pull-up       | Memory Chip S<br>Recommend ex<br>Signals that a M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                  | elected.           |                       |                          |  |  |  |  |

| mem_oe_n           | Output | Н                        | High                            | Recommend ex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>t Enable Negated</b><br>ternal pull-up.<br>lemory Bank can output it                                                                                                                                                                                                                                                                                          | ts data lines onto | the cpu_ad bus.       |                          |  |  |  |  |

Table 1 Pin Description (Part 1 of 7)

| Name           | Туре                      | Reset<br>State<br>Status | Drive<br>Strength<br>Capability | Description                                                                                                                                                                                                                                                                 |

|----------------|---------------------------|--------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mem_we_n[3:0]  | Output                    | Н                        | High                            | Memory Write Enable Negated Bus Signals which bytes are to be written during a memory transaction. Bits act as Byte Enable and mem_addr[1:0] signals for 8-bit or 16-bit wide addressing.                                                                                   |

| mem_wait_n     | Input                     |                          | -                               | Memory Wait Negated Requires external pull-up. SRAM/IOI/IOM modes: Allows external wait-states to be injected during last cycle before data is sampled. DPM (dual-port) mode: Allows dual-port busy signal to restart memory transaction. Alternate function: sdram_wait_n. |

| mem_245_oe_n   | Output                    | Н                        | Low                             | Memory FCT245 Output Enable Negated Controls output enable to optional FCT245 transceiver bank by asserting during both reads and writes to a memory or I/O bank.                                                                                                           |

| mem_245_dt_r_n | Output                    | Z                        | High                            | Memory FCT245 Direction Xmit/Rcv Negated Recommend external pull-up. Alternate function: cpu_dt_r_n. See CPU Core Specific Signals below.                                                                                                                                   |

| output_clk     | Output                    | cpu_mas<br>terclk        | High                            | Output Clock Optional clock output.                                                                                                                                                                                                                                         |

| PCI Interface  | 1                         |                          |                                 |                                                                                                                                                                                                                                                                             |

| pci_ad[31:0]   | I/O                       | Z                        | PCI                             | PCI Multiplexed Address/Data Bus Address driven by Bus Master during initial frame_n assertion, and then the Data is driven by the Bus Master during writes; or the Data is driven by the Bus Slave during reads.                                                           |

| pci_cbe_n[3:0] | I/O                       | Z                        | PCI                             | PCI Multiplexed Command/Byte Enable Bus Command (not negated) Bus driven by the Bus Master during the initial frame_n assertion. Byte Enable Negated Bus driven by the Bus Master during the data phase(s).                                                                 |

| pci_par        | I/O                       | Z                        | PCI                             | PCI Parity Even parity of the pci_ad[31:0] bus. Driven by Bus Master during Address and Write Data phases. Driven by the Bus Slave during the Read Data phase.                                                                                                              |

| pci_frame_n    | I/O                       | Z                        | PCI                             | PCI Frame Negated Driven by the Bus Master. Assertion indicates the beginning of a bus transaction. De-assertion indicates the last datum.                                                                                                                                  |

| pci_trdy_n     | I/O                       | Z                        | PCI                             | PCI Target Ready Negated Driven by the Bus Slave to indicate the current datum can complete.                                                                                                                                                                                |

| pci_irdy_n     | I/O                       | Z                        | PCI                             | PCI Initiator Ready Negated Driven by the Bus Master to indicate that the current datum can complete.                                                                                                                                                                       |

| pci_stop_n     | I/O                       | Z                        | PCI                             | PCI Stop Negated Driven by the Bus Slave to terminate the current bus transaction.                                                                                                                                                                                          |

| pci_idsel_n    | Input                     |                          | _                               | PCI Initialization Device Select Uses pci_req_n[2] pin. See the PCI subsection.                                                                                                                                                                                             |

| pci_perr_n     | I/O                       | Z                        | PCI                             | PCI Parity Error Negated Driven by the receiving Bus Agent 2 clocks after the data is received, if a parity error occurs.                                                                                                                                                   |

| pci_serr_n     | I/O<br>Open-<br>collector | Z                        | PCI                             | System Error External pull-up resistor is required. Driven by any agent to indicate an address parity error, data parity during a Special Cycle command, or any other system error.                                                                                         |

| pci_clk        | Input                     |                          | ı                               | PCI Clock Clock for PCI Bus transactions. Uses the rising edge for all timing references.                                                                                                                                                                                   |

Table 1 Pin Description (Part 2 of 7)

| Name                                  | Туре   | Reset<br>State<br>Status | Drive<br>Strength<br>Capability | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------|--------|--------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sdram_cas_n                           | Output | Н                        | High                            | SDRAM CAS Negated SDRAM mode: Provides SDRAM CAS control signal to all SDRAM banks.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| sdram_we_n                            | Output | Н                        | High                            | SDRAM WE Negated SDRAM mode: Provides SDRAM WE control signal to all SDRAM banks.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| sdram_cke                             | Output | Н                        | High                            | SDRAM Clock Enable SDRAM mode: Provides clock enable to all SDRAM banks.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| sdram_cs_n[3:0]                       | Output | Н                        | High                            | SDRAM Chip Select Negated Bus Recommend external pull-up. SDRAM mode: Provides chip select to each SDRAM bank. SODIMM mode: Provides upper select byte enables [7:4].                                                                                                                                                                                                                                                                                                                                                          |

| sdram_s_n[1:0]                        | Output | Н                        | High                            | SDRAM SODIMM Select Negated Bus SDRAM mode: Not used. SDRAM SODIMM mode: Upper and lower chip selects.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| sdram_bemask_n<br>[3:0]               | Output | Н                        | High                            | SDRAM Byte Enable Mask Negated Bus (DQM) SDRAM mode: Provides byte enables for each byte lane of all DRAM banks. SODIMM mode: Provides lower select byte enables [3:0].                                                                                                                                                                                                                                                                                                                                                        |

| sdram_245_oe_n                        | Output | Н                        | Low                             | SDRAM FCT245 Output Enable Negated Recommend external pull-up. SDRAM mode: Controls output enable to optional FCT245 transceiver bank by asserting during both reads and writes to any DRAM bank.                                                                                                                                                                                                                                                                                                                              |

| sdram_245_dt_r_n                      | Output | Z                        | High                            | SDRAM FCT245 Direction Transmit/Receive Recommend external pull-up. Uses cpu_dt_r_n. See CPU Core Specific Signals below.                                                                                                                                                                                                                                                                                                                                                                                                      |

| On-Chip Peripheral                    | s      |                          |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| dma_ready_n[1:0] /<br>dma_done_n[1:0] | I/O    | Z                        | Low                             | DMA Ready Negated Bus Requires external pull-up. Ready mode: Input pin for each general purpose DMA channel that can initiate the next datum in the current DMA descriptor frame. Done mode: Input pin for each general purpose DMA channel that can terminate the current DMA descriptor frame. dma_ready_n[0] 1st Alternate function PIO[1]; 2nd Alternate function: dma_done_n[0]. dma_ready_n[1] 1st Alternate function PIO[0]; 2nd Alternate function: dma_done_n[1].                                                     |

| pio[15:0]                             | I/O    | See<br>related<br>pins   | Low                             | Programmable Input/Output  General purpose pins that can each be configured as a general purpose input or general purpose output. These pins are multiplexed with other pin functions: uart_cts_n[0], uart_dsr_n[0], uart_dtr_n[0], uart_rts_n[0], pci_gnt_n[1], spi_mosi, spi_miso, spi_sck, spi_ss_n, uart_rx[0], uart_tx[0], uart_rx[1], uart_tx[1], timer_tc_n[0], dma_ready_n[0], dma_ready_n[1]. Note that pci_gnt_n[1], spi_mosi, spi_sck, and spi_ss_n default to outputs at reset time. The others default to inputs. |

| timer_tc_n[0] /<br>timer_gate_n[0]    | I/O    | Z                        | Low                             | Timer Terminal Count Overflow Negated  Terminal count mode (timer_tc_n): Output indicating that the timer has reached its count compare value and has overflowed back to 0.  Gate mode (timer_gate_n): input indicating that the timer may count one tick on the next clock edge.  1st Alternate function: PIO[2].  2nd Alternate function: timer_gate_n[0].                                                                                                                                                                   |

| uart_rx[1:0]                          | I/O    | Z                        | Low                             | UART Receive Data Bus  UART mode: Each UART channel receives data on their respective input pin.  uart_rx[0] Alternate function: PIO[6].  uart_rx[1] Alternate function: PIO[4].                                                                                                                                                                                                                                                                                                                                               |

Table 1 Pin Description (Part 4 of 7)

| Name                                                             | Туре    | Reset<br>State<br>Status | Drive<br>Strength<br>Capability | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------|---------|--------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uart_tx[1:0]                                                     | I/O     | Z                        | Low                             | UART Transmit Data Bus  UART mode: Each UART channel sends data on their respective output pin. Note that these pins default to inputs at reset time and must be programmed via the PIO interface before being used as UART outputs.  uart_tx[0] Alternate function: PIO[5].  uart_tx[1] Alternate function: PIO[3].                                                                                                                                                                   |

| uart_cts_n[0]<br>uart_dsr_n[0]<br>uart_dtr_n[0]<br>uart_rts_n[0] | I/O     | Z                        | Low                             | UART Transmit Data Bus  UART mode: Data bus modem control signal pins for UART channel 0.  uart_cts_n[0] Alternate function: PIO[15].  uart_dsr_n[0] Alternate function: PIO[14].  uart_dtr_n[0] Alternate function: PIO[13].  uart_rts_n[0] Alternate function: PIO[12].                                                                                                                                                                                                              |

| spi_mosi                                                         | I/O     | L                        | Low                             | SPI Data Output Serial mode: Output pin from RC32334 as an Input to a Serial Chip for the Serial data input stream. In PCI satellite mode, acts as an Output pin from RC32334 that connects as an Input to a Serial Chip for the Serial data input stream for loading PCI Configuration Registers in the RC32334 Reset Initialization Vector PCI boot mode.  1st Alternate function: PIO[10]. Defaults to the output direction at reset time.  2nd Alternate function: pci_eeprom_mdo. |

| spi_miso                                                         | I/O     | Z                        | Low                             | SPI Data Input Serial mode: Input pin to RC32334 from the Output of a Serial Chip for the Serial data output stream. In PCI satellite mode, acts as an Input pin from RC32334 that connects as an output to a Serial Chip for the Serial data output stream for loading PCI Configuration Registers in the RC32334 Reset Initialization Vector PCI boot mode.  Defaults to input direction at reset time. 1st Alternate function: PIO[7]. 2nd Alternate function: pci_eeprom_mdi.      |

| spi_sck                                                          | I/O     | L                        | Low                             | SPI Clock Serial mode: Output pin for Serial Clock. In PCI satellite mode, acts as an Output pin for Serial Clock for loading PCI Configuration Registers in the RC323334 Reset Initialization Vector PCI boot mode.  1st Alternate function: PIO[9]. Defaults to the output direction at reset time.  2nd Alternate function: pci_eeprom_sk.                                                                                                                                          |

| spi_ss_n                                                         | I/O     | Н                        | Low                             | SPI Chip Select Output pin selecting the serial protocol device as opposed to the PCI satellite mode EEPROM device. Alternate function: PIO[8]. Defaults to the output direction at reset time.                                                                                                                                                                                                                                                                                        |

| CPU Core Specific                                                | Signals |                          |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| cpu_nmi_n                                                        | Input   |                          | _                               | CPU Non-Maskable Interrupt Requires external pull-up. This interrupt input is active low to the CPU.                                                                                                                                                                                                                                                                                                                                                                                   |

| cpu_masterclk                                                    | Input   |                          | _                               | CPU Master System Clock Provides the basic system clock.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| cpu_int_n[5:4], [2:0]                                            | Input   |                          | _                               | CPU Interrupt Requires external pull-up. These interrupt inputs are active low to the CPU.                                                                                                                                                                                                                                                                                                                                                                                             |

| cpu_coldreset_n                                                  | Input   | L                        | _                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 1 Pin Description (Part 5 of 7)

| Name                      | Туре   | Reset<br>State<br>Status | Drive<br>Strength<br>Capability       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------|--------|--------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cpu_dt_r_n                | Output | Z                        | _                                     | CPU Direction Transmit/Receive This active-low signal controls the DT/R pin of an optional FCT245 transceiver bank. It is asserted during read operations. 1st Alternate function: mem_245_dt_r_n. 2nd Alternate function: sdram_245_dt_r_n.                                                                                                                                                                                                                 |

| JTAG Interface Sig        | ınals  |                          |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

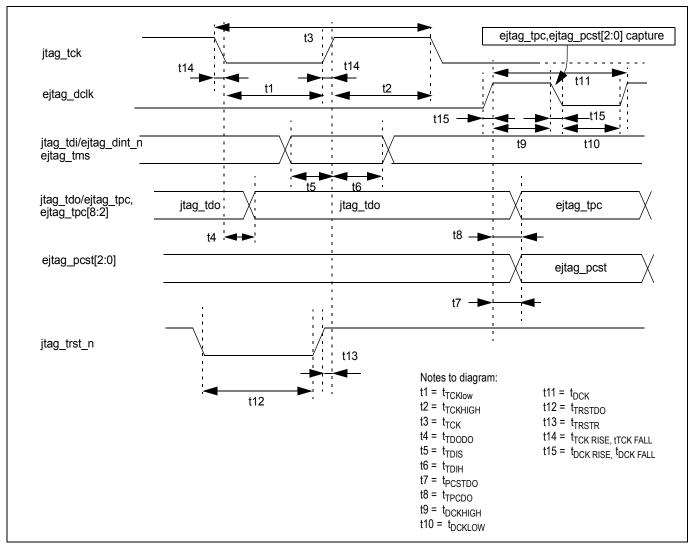

| jtag_tck                  | Input  |                          | _                                     | JTAG Test Clock Requires external pull-down. An input test clock used to shift into or out of the Boundary-Scan register cells. jtag_tck is independent of the system and the processor clock with nominal 50% duty cycle.                                                                                                                                                                                                                                   |

| jtag_tdi,<br>ejtag_dint_n | Input  |                          | _                                     | JTAG Test Data In  Requires an external pull-up on the board.  On the rising edge of jtag_tck, serial input data are shifted into either the Instruction or Data register, depending on the TAP controller state. During Real Mode, this input is used as an interrupt line to stop the debug unit from Real Time mode and return the debug unit back to Run Time Mode (standard JTAG).  This pin is also used as the ejtag_dint_n signal in the EJTAG mode. |

| jtag_tdo,<br>ejtag_tpc    | Output | Z                        | High                                  | JTAG Test Data Out The jtag_tdo is serial data shifted out from instruction or data register on the falling edge of jtag_tck. When no data is shifted out, the jtag_tdo is tri-stated. During Real Time Mode, this signal provides a non-sequential program counter at the processor clock or at a division of processor clock. This pin is also used as the ejtag_tpc signal in the EJTAG mode.                                                             |

| jtag_tms                  | Input  |                          | _                                     | JTAG Test Mode Select Requires external pull-up. The logic signal received at the jtag_tms input is decoded by the TAP controller to control test operation. jtag_tms is sampled on the rising edge of the jtag_tck.                                                                                                                                                                                                                                         |

| jtag_trst_n               | Input  | L                        | _                                     | JTAG Test Reset  When neither JTAG nor EJTAG are being used, jtag_trst_n must be driven low (pulled down) or the jtag_tms/ejtag_tms signals must be pulled up and jtag_clk actively clocked.                                                                                                                                                                                                                                                                 |

| ejtag_dclk                | Output | Z                        | _                                     | EJTAG Test Clock Processor Clock. During Real Time Mode, this signal is used to capture address and data from the ejtag_tpc signal at the processor clock speed or any division of the internal pipeline.                                                                                                                                                                                                                                                    |

| ejtag_pcst[2:0]           | I/O    | Z                        | Low                                   | EJTAG PC Trace Status Information  111 (STL) Pipe line Stall  110 (JMP) Branch/Jump forms with PC output  101 (BRT) Branch/Jump forms with no PC output  100 (EXP) Exception generated with an exception vector code output  011 (SEQ) Sequential performance  010 (TST) Trace is outputted at pipeline stall time  001 (TSQ) Trace trigger output at performance time  000 (DBM) Run Debug Mode  Alternate function: modebit[2:0].                          |

| ejtag_debugboot           | Input  |                          | Requires external pull- down          | EJTAG DebugBoot The ejtag_debugboot input is used during reset and forces the CPU core to take a debug exception at the end of the reset sequence instead of a reset exception. This enables the CPU to boot from the ICE probe without having the external memory working. This input signal is level sensitive and is not latched internally. This signal will also set the JtagBrk bit in the JTAG_Control_Register[12].                                  |

| ejtag_tms                 | Input  |                          | —<br>Requires<br>external pull-<br>up | EJTAG Test Mode Select An external pull-up on the board is required. The ejtag_tms is sampled on the rising edge of jtag_tck.                                                                                                                                                                                                                                                                                                                                |

Table 1 Pin Description (Part 6 of 7)

| Name            | Туре | Reset<br>State<br>Status | Drive<br>Strength<br>Capability | Description                                                                                                                                                                                                                                                                                                                                  |

|-----------------|------|--------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Debug Signals   | •    | <u> </u>                 | <u> </u>                        |                                                                                                                                                                                                                                                                                                                                              |

| debug_cpu_dma_n | I/O  | Z                        | Low                             | Debug CPU versus DMA Negated De-assertion high during debug_cpu_ads_n assertion or debug_cpu_ack_n assertion indicates transaction was generated from the CPU. Assertion low during debug_cpu_ads_n assertion or debug_cpu_ack_n assertion indicates transaction was generated from DMA. Alternate function: modebit[6].                     |

| debug_cpu_ack_n | I/O  | Z                        | Low                             | Debug CPU Acknowledge Negated Indicates either a data acknowledge to the CPU or DMA. Alternate function: modebit[4].                                                                                                                                                                                                                         |

| debug_cpu_ads_n | I/O  | Z                        | Low                             | Debug CPU Address/Data Strobe Negated Assertion indicates that either a CPU or a DMA transaction is beginning and that the mem_data[31:4] bus has the current block address. Alternate function: modebit[5].                                                                                                                                 |

| debug_cpu_i_d_n | I/O  | Z                        | Low                             | Debug CPU Instruction versus Data Negated Assertion during debug_cpu_ads_n assertion or debug_cpu_ack_n assertion indicates transaction is a CPU or DMA data transaction. De-assertion during debug_cpu_ads_n assertion or debug_cpu_ack_n assertion indicates transaction is a CPU instruction transaction. Alternate function: modebit[3]. |

Table 1 Pin Description (Part 7 of 7)

# **Mode Bit Settings to Configure Controller on Reset**

The following table lists the mode bit settings to configure the controller on cold reset.

| Pin             | Mode Bit    | Description                                             | Value | Mode Setting             |  |  |

|-----------------|-------------|---------------------------------------------------------|-------|--------------------------|--|--|

| ejtag_pcst[2:0] | 2:0 MSB (2) | Clock Multiplier                                        | 0     | Multiply by 2            |  |  |

|                 |             | MasterClock is multiplied internally to generate PClock | 1     | Multiply by 3            |  |  |

|                 |             | ate F Clock                                             | 2     | Multiply by 4            |  |  |

|                 |             |                                                         | 3     | Reserved                 |  |  |

|                 |             |                                                         | 4     | Reserved                 |  |  |

|                 |             |                                                         | 5     | Reserved                 |  |  |

|                 |             |                                                         | 6     | Reserved                 |  |  |

|                 |             |                                                         | 7     | Reserved                 |  |  |

| debug_cpu_i_d_n | 3           | EndBit                                                  | 0     | Little-endian ordering   |  |  |

|                 |             |                                                         | 1     | Big-endian ordering      |  |  |

| debug_cpu_ack_n | 4           | Reserved                                                | 0     |                          |  |  |

| debug_cpu_ads_n | 5           | Reserved                                                | 0     |                          |  |  |

| debug_cpu_dma_n | 6           | TmrIntEn                                                | 0     | Enables timer interrupt  |  |  |

|                 |             | Enables/Disables the timer interrupt on Int*[5]         | 1     | Disables timer interrupt |  |  |

| mem_addr[17]    | 7           | Reserved for future use                                 | 1     |                          |  |  |

Table 2 Boot-Mode Configuration Settings (Part 1 of 2)

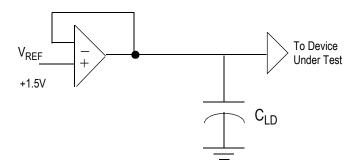

### **Clock Parameters — RC32334**

(Ta = 0°C to +70°C Commercial, Ta = -40°C to +85°C Industrial,  $V_{cc}$  I/O = +3.3V±5%,  $V_{cc}$  Core = +3.3V±5%)

| Parameter                                     | Symbol                                                                            | Test Conditions   |     | 2334<br>MHz  |      | 2334<br>MHz  | RC3:<br>150 | Units        |    |

|-----------------------------------------------|-----------------------------------------------------------------------------------|-------------------|-----|--------------|------|--------------|-------------|--------------|----|

|                                               |                                                                                   |                   | Min | Max          | Min  | Max          | Min         | Max          |    |

| cpu_masterclock HIGH                          | t <sub>MCHIGH</sub>                                                               | Transition ≤ 2ns  | 8   | _            | 6.75 | _            | 6           | _            | ns |

| cpu_masterclock LOW                           | t <sub>MCLOW</sub>                                                                | Transition ≤ 2ns  | 8   | _            | 6.75 | _            | 6           | _            | ns |

| cpu_masterclock period <sup>1</sup>           | tMCP                                                                              | _                 | 20  | 66.6         | 15   | 66.6         | 13.33       | 66.6         | ns |

| cpu_masterclock Rise & Fall Time <sup>2</sup> | t <sub>MCRise</sub> , t <sub>MCFall</sub>                                         | _                 |     | 3            | _    | 3            | _           | 3            | ns |

| cpu_masterclock Jitter                        | t <sub>JITTER</sub>                                                               | _                 |     | <u>+</u> 250 | _    | <u>+</u> 250 | _           | <u>+</u> 200 | ps |

| pci_clk Rise & Fall Time                      | t <sub>PCRise</sub> , t <sub>PCFall</sub>                                         | PCI 2.2           | _   | 1.6          | _    | 1.6          | _           | 1.6          | ns |

| pci_clk Period <sup>1</sup>                   | t <sub>PCP</sub>                                                                  |                   | 15  | _            | 15   | _            | 15          | _            | ns |

| jtag_tck Rise & Fall Time                     | t <sub>JCRise</sub> , t <sub>JCFall</sub>                                         | _                 | _   | 5            | _    | 5            | _           | 5            | ns |

| ejtag_dck period                              | t <sub>DCK</sub> , t <sub>11</sub>                                                |                   | 10  | _            | 10   | _            | 10          | _            | ns |

| jtag_tck clock period                         | t <sub>TCK,</sub> t <sub>3</sub>                                                  |                   | 100 | _            | 100  | _            | 100         | _            | ns |

| ejtag_dclk High, Low Time                     | t <sub>DCK High</sub> , t <sub>9</sub><br>t <sub>DCK Low</sub> , t <sub>10</sub>  |                   | 4   | _            | 4    | _            | 4           | _            | ns |

| ejtag_dclk Rise, Fall Time                    | t <sub>DCK Rise</sub> , t <sub>9</sub><br>t <sub>DCK Fall</sub> , t <sub>10</sub> |                   | _   | 1            | _    | 1            | _           | 1            | ns |

| output_clk <sup>3</sup>                       | Tdo21                                                                             |                   | N/A | N/A          | N/A  | N/A          | N/A         | N/A          | _  |

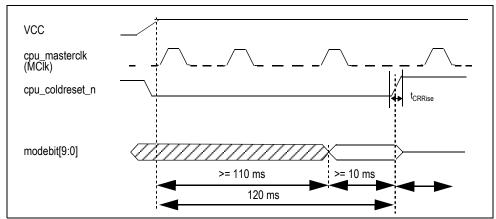

| cpu_coldreset_n<br>Asserted during power-up   |                                                                                   | power-on sequence | 120 | _            | 120  | _            | 120         | _            | ms |

| cpu_coldreset_n Rise Time                     | t <sub>CRRise</sub>                                                               |                   | _   | 5            | _    | 5            | _           | 5            | ns |

Table 5 Clock Parameters - RC32334

### **Reset Specification**

Figure 3 Mode Configuration Interface Cold Reset Sequence

<sup>&</sup>lt;sup>1.</sup> cpu\_masterclock frequency should never be below pci\_clk frequency if PCI interface is used.

<sup>&</sup>lt;sup>2.</sup> Rise and fall times are measured between 10% and 90%

<sup>&</sup>lt;sup>3.</sup> Output\_clk should not be used in a system. Only the cpu\_masterclock or its derivative must be used to drive all the subsystems with designs based on the RC32334 device. Refer to the RC3233x Device Errata for more information.

| Signal                                                                                                                                   | Symbol    | Reference                                |     | 2334 <sup>1</sup><br>MHz | RC32334 <sup>1</sup><br>133MHz |     |     | 2334 <sup>1</sup><br>MHz | Unit  | User<br>Manual<br>Timing    |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------|-----|--------------------------|--------------------------------|-----|-----|--------------------------|-------|-----------------------------|--|--|--|--|--|

| Signal                                                                                                                                   | - Cymison | Edge                                     | Min | Max                      | Min                            | Max | Min | Max                      | Oilit | Diagram<br>Reference        |  |  |  |  |  |

| pci_eeprom_mdi                                                                                                                           | Thld      | pci_clk rising,<br>pci_eeprom_sk falling | 15  | _                        | 12                             | _   | 10  | _                        | ns    |                             |  |  |  |  |  |

| pci_eeprom_mdo, pci_eeprom_cs                                                                                                            | Tdo       | pci_clk rising,<br>pci_eeprom_sk falling |     | 15                       | _                              | 12  | _   | 10                       | ns    |                             |  |  |  |  |  |

| pci_eeprom_sk                                                                                                                            | Tdo       | pci_clk rising                           |     | 15                       | _                              | 12  |     | 10                       | ns    |                             |  |  |  |  |  |

| pci_ad[31:0], pci_cbe_n[3:0], pci_par, pci_frame_n, pci_trdy_n, pci_irdy_n, pci_stop_n, pci_perr_n, pci_serr_n, pci_serr_n, pci_devsel_n | Tdo       | pci_clk rising                           | 2   | 6                        | 2                              | 6   | 2   | 6                        | ns    | Per PCI 2.2                 |  |  |  |  |  |

| pci_req_n[0], pci_gnt_[2], pci_gnt_n[1],<br>pci_gnt_n[0], pci_inta_n                                                                     | Tdo       | pci_clk rising                           | 2   | 6                        | 2                              | 6   | 2   | 6                        | ns    |                             |  |  |  |  |  |

| SDRAM Controller                                                                                                                         |           |                                          |     |                          |                                |     |     | •                        |       | •                           |  |  |  |  |  |

| sdram_245_dt_r_n                                                                                                                         | Tdo8      | cpu_masterclk rising                     | _   | 15                       | _                              | 12  | _   | 10                       | ns    |                             |  |  |  |  |  |

| sdram_ras_n, sdram_cas_n, sdram_we_n, sdram_cs_n[3:0], sdram_s_n[1:0], sdram_bemask_n[3:0], sdram_cke                                    | Tdo9      | cpu_masterclk rising                     |     | 12                       | _                              | 9   |     | 8                        | ns    |                             |  |  |  |  |  |

| sdram_addr_12                                                                                                                            | Tdo10     | cpu_masterclk rising                     | _   | 12                       | _                              | 9   | _   | 8                        | ns    |                             |  |  |  |  |  |

| sdram_245_oe_n                                                                                                                           | Tdo11     | cpu_masterclk rising                     | _   | 12                       | _                              | 9   | _   | 8                        | ns    | Chapter 11,<br>Figures 11.4 |  |  |  |  |  |

| sdram_245_dt_r_n                                                                                                                         | Tdoh4     | cpu_masterclk rising                     | 1   | _                        | 1                              | _   | 1   | _                        | ns    | and 11.5                    |  |  |  |  |  |

| sdram_ras_n, sdram_cas_n, sdram_we_n, sdram_cs_n[3:0], sdram_s_n[1:0], sdram_bemask_n[3:0] sdram_cke, sdram_addr_12, sdram_245_oe_n      | Tdoh4     | cpu_masterclk rising                     | 2.5 | _                        | 2.5                            | _   | 2.5 | _                        | ns    | -                           |  |  |  |  |  |

| DMA                                                                                                                                      |           |                                          |     | •                        |                                | •   |     | •                        |       |                             |  |  |  |  |  |

| dma_ready_n[1:0], dma_done_n[1:0]                                                                                                        | Tsu7      | cpu_masterclk rising                     | 9   | _                        | 7                              | _   | 6   | _                        | ns    | Chapter 13,                 |  |  |  |  |  |

| dma_ready_n[1:0], dma_done_n[1:0]                                                                                                        | Thld9     | cpu_masterclk rising                     | 1   | _                        | 1                              | _   | 1   | _                        | ns    | Figure 13.4                 |  |  |  |  |  |

| Interrupt Handling                                                                                                                       |           |                                          |     |                          |                                |     |     |                          |       |                             |  |  |  |  |  |