# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 1.6MHz                                                                  |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 6                                                                       |

| Program Memory Size        | 1KB (512 x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 64 x 8                                                                  |

| RAM Size                   | -                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 4x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny15l-1pu |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

A flexible interrupt module has its control registers in the I/O space with an additional Global Interrupt Enable bit in the Status Register. All the different interrupts have a separate Interrupt Vector in the Interrupt Vector table at the beginning of the program memory. The different interrupts have priority in accordance with their Interrupt Vector position. The lower the Interrupt Vector address, the higher the priority.

# The General Purpose Register File

Figure 3 shows the structure of the 32 general purpose registers in the CPU.

Figure 3. AVR CPU General Purpose Working Registers

General Purpose Working Registers

| 7               | 0             |

|-----------------|---------------|

| R               | )             |

| R               | I             |

| Rź              | 2             |

|                 |               |

|                 |               |

| R2              | 8             |

| R2              | 9             |

| R30 (Z-register | Low Byte)     |

| R31 (Z-registe  | er High Byte) |

All the register operating instructions in the instruction set have direct- and single-cycle access to all registers. The only exception is the five constant arithmetic and logic instructions SBCI, SUBI, CPI, ANDI, and ORI between a constant and a register and the LDI instruction for load-immediate constant data. These instructions apply to the second half of the registers in the Register File – R16..R31. The general SBC, SUB, CP, AND, OR, and all other operations between two registers or on a single-register apply to the entire Register File.

Registers 30 and 31 form a 16-bit pointer (the Z-pointer) which is used for indirect Flash memory and Register File access. When the Register File is accessed, the contents of R31 is discarded by the CPU.

| The ALU – Arithmetic<br>Logic Unit | The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, ALU operations between registers in the Register File are executed. The ALU operations are divided into three main categories – arithmetic, logic and bit-functions. Some microcontrollers in the AVR product family feature a hardware multiplier in the arithmetic part of the ALU. |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The Flash Program<br>Memory        | The ATtiny15L contains 1K byte On-chip, In-System Programmable Flash memory for program storage. Since all instructions are single 16-bit words, the Flash is organized as 512 x 16 words. The Flash memory has an endurance of at least 1,000 write/erase cycles.                                                                                                                                                               |

|                                    | The ATtiny15L Program Counter is nine bits wide, thus addressing the 512 words Flash Program memory.                                                                                                                                                                                                                                                                                                                             |

|                                    | See page 54 for a detailed description on Flash memory programming.                                                                                                                                                                                                                                                                                                                                                              |

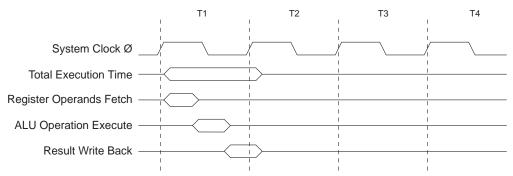

# Figure 11. Single Cycle ALU Operation

# I/O Memory

The I/O space definition of the ATtiny15L is shown in Table 2.

# Table 2. ATtiny15L I/O Space<sup>(1)</sup>

| Address Hex | Name   | Function                                      |

|-------------|--------|-----------------------------------------------|

| \$3F        | SREG   | Status Register                               |

| \$3B        | GIMSK  | General Interrupt Mask Register               |

| \$3A        | GIFR   | General Interrupt Flag Register               |

| \$39        | TIMSK  | Timer/Counter Interrupt Mask Register         |

| \$38        | TIFR   | Timer/Counter Interrupt Flag Register         |

| \$35        | MCUCR  | MCU Control Register                          |

| \$34        | MCUSR  | MCU Status Register                           |

| \$33        | TCCR0  | Timer/Counter0 Control Register               |

| \$32        | TCNT0  | Timer/Counter0 (8-bit)                        |

| \$31        | OSCCAL | Oscillator Calibration Register               |

| \$30        | TCCR1  | Timer/Counter1 Control Register               |

| \$2F        | TCNT1  | Timer/Counter1 (8-bit)                        |

| \$2E        | OCR1A  | Timer/Counter1 Output Compare Register A      |

| \$2D        | OCR1B  | Timer/Counter1 Output Compare Register B      |

| \$2C        | SFIOR  | Special Function I/O Register                 |

| \$21        | WDTCR  | Watchdog Timer Control Register               |

| \$1E        | EEAR   | EEPROM Address Register                       |

| \$1D        | EEDR   | EEPROM Data Register                          |

| \$1C        | EECR   | EEPROM Control Register                       |

| \$18        | PORTB  | Data Register, Port B                         |

| \$17        | DDRB   | Data Direction Register, Port B               |

| \$16        | PINB   | Input Pins, Port B                            |

| \$08        | ACSR   | Analog Comparator Control and Status Register |

| \$07        | ADMUX  | ADC Multiplexer Select Register               |

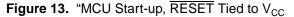

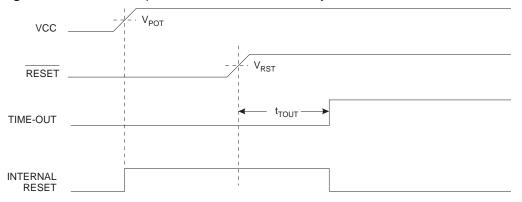

### Figure 14. MCU Start-up, RESET Extended Externally

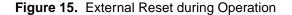

### **External Reset**

An External Reset is generated by a low-level on the RESET pin. Reset pulses longer than 500 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset Threshold Voltage ( $V_{RST}$ ) on its positive edge, the delay timer starts the MCU after the Time-out period  $t_{TOUT}$  has expired.

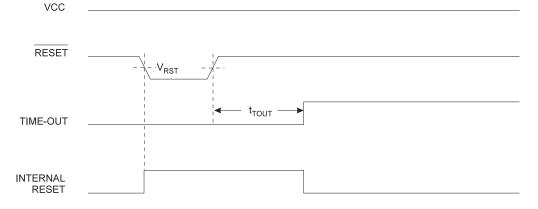

MCU Status Register – MCUSR The MCU Status Register provides information on which reset source caused an MCU Reset.

### • Bit 7..4 - Res: Reserved Bits

These bits are reserved bits in the ATtiny15L and always read as zero.

#### • Bit 3 – WDRF: Watchdog Reset Flag

This bit is set (one) if a Watchdog Reset occurs. The bit is reset (zero) by a Power-on Reset, or by writing a logical "0" to the flag.

#### Bit 2 – BORF: Brown-out Reset Flag

This bit is set (one) if a Brown-out Reset occurs. The bit is reset (zero) by a Power-on Reset, or by writing a logical "0" to the flag.

#### Bit 1 – EXTRF: External Reset Flag

This bit is set (one) if a External Reset occurs. The bit is reset (zero) by a Power-on Reset, or by writing a logical "0" to the flag.

#### Bit 0 – PORF: Power-on Reset Flag

This bit is set (one) if a Power-on Reset occurs. The bit is reset (zero) by writing a logical "0" to the flag.

To make use of the Reset Flags to identify a reset condition, the user should read and then reset the MCUSR as early as possible in the program. If the register is cleared before another reset occurs, the source of the reset can be found by examining the Reset Flags.

Internal VoltageATtiny15L features an internal bandgap reference with a nominal voltage of 1.22V. ThisReferencereference is used for Brown-out Detection, and it can be used as an input to the Analog<br/>Comparator. The 2.56V reference to the ADC is generated from the internal bandgap<br/>reference.

Voltage Reference Enable Signals and Start-up Time

The voltage reference has a start-up time that may influence the way it should be used. The maximum start-up time is 10  $\mu$ s. To save power, the reference is not always turned on. The reference is on during the following situations:

- 1. When the BOD is enabled (by programming the BODEN Fuse).

- 2. When the bandgap reference is connected to the Analog Comparator (by setting the AINBG bit in ACSR).

- 3. When the ADC is enabled.

Thus, when the BOD is not enabled, after setting the AINBG bit, the user must always allow the reference to start-up before the output from the Analog Comparator is used. The bandgap reference uses typically 10  $\mu$ A, and to reduce power consumption in Power-down mode, the user can avoid the three conditions above to ensure that the reference is turned off before entering Power-down mode.

# **Timer/Counters**

The ATtiny15L provides two general purpose 8-bit Timer/Counters. The Timer/Counters have separate prescaling selection from separate 10-bit prescalers. The Timer/Counter0 uses internal clock (CK) as the clock time base. The Timer/Counter1 may use either the internal clock (CK) or the fast peripheral clock (PCK) as the clock time base.

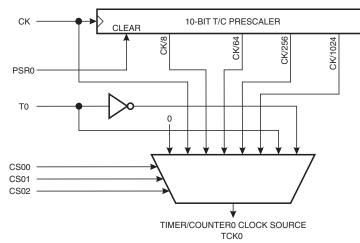

Figure 18 shows the Timer/Counter prescaler.

# The Timer/Counter0 Prescaler

Figure 18. Timer/Counter0 Prescaler

The four prescaled selections are: CK/8, CK/64, CK/256, and CK/1024, where CK is the Oscillator clock. CK, external source and stop, can also be selected as clock sources. Setting the PSR10 bit in SFIOR resets the prescaler. This allows the user to operate with a predictable prescaler.

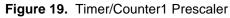

# The Timer/Counter1 Prescaler

Figure 19 shows the Timer/Counter1 prescaler. For Timer/Counter1 the clock selections are: PCK, PCK/2, PCK/4, PCK/8, CK (=PCK/16), CK/2, CK/4, CK/8,CK/16, CK/32, CK/64, CK/128, CK/256, CK/512, CK/1024, and stop. The clock options are described in Table 12 on page 31 and the Timer/Counter1 Control Register (TCCR1). Setting the PSR1 bit in the SFIOR Register resets the 10-bit prescaler. This allows the user to operate with a predictable prescaler.

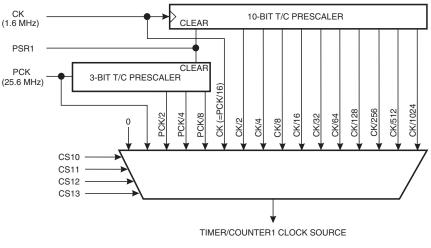

### The Timer Counter 0 – TCNT0

The Timer/Counter0 is implemented as an up-counter with read and write access. If the Timer/Counter0 is written and a clock source is present, the Timer/Counter0 continues counting in the timer clock cycle following the write operation.

### **The 8-bit Timer/Counter1** This module features a high-resolution and a high-accuracy usage with the lower prescaling opportunities. Timer/Counter1 can also be used as an accurate, high speed, 8-bit Pulse Width Modulator (PWM) using clock speeds up to 25.6 MHz. In this mode, Timer/Counter1 and the Output Compare Registers serve as a standalone PWM. Refer to page 34 for a detailed description of this function. Similarly, the high-prescaling opportunities make this unit useful for lower-speed functions or exact-timing functions with infrequent actions.

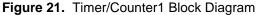

Figure 21 shows the block diagram for Timer/Counter1.

The two Status Flags (Overflow and Compare Match) are found in the Timer/Counter Interrupt Flag Register (TIFR). Control signals are found in the Timer/Counter Control Register (TCCR1). The interrupt enable/disable settings are found in the Timer/Counter Interrupt Mask Register (TIMSK).

The frequency of the PWM will be Timer Clock Frequency divided by OCR1B value + 1.

| Clock Selection | OCR1B | PWM Frequency |

|-----------------|-------|---------------|

| СК              | 159   | 10 kHz        |

| PCK/8           | 159   | 20 kHz        |

| PCK/4           | 213   | 30 kHz        |

| PCK/4           | 159   | 40 kHz        |

| PCK/2           | 255   | 50 kHz        |

| PCK/2           | 213   | 60 kHz        |

| PCK/2           | 181   | 70 kHz        |

| PCK/2           | 159   | 80 kHz        |

| PCK/2           | 141   | 90 kHz        |

| PCK             | 255   | 100 kHz       |

| PCK             | 231   | 110 kHz       |

| PCK             | 213   | 120 kHz       |

| PCK             | 195   | 130 kHz       |

| PCK             | 181   | 140 kHz       |

| PCK             | 169   | 150 kHz       |

Table 14.

Timer/Counter1

Clock

Prescale

Select

The exact duty-cycle of the non-inverted PWM output is:

$\frac{(\mathsf{OCR1A}\texttt{+}1) \times T_{T1} - T_{PCK}}{(\mathsf{OCR1B}\texttt{+}1) \times T_{T1}}$

Where:

$T_{T1}$  is the period of the selected Timer/Counter1 Clock Source.  $T_{PCK}$  is the period of the PCK Clock (39.1 ns).

- 1. In the same operation, write a logical "1" to WDTOE and WDE. A logical "1" must be written to WDE even though it is set to one before the disable operation starts.

- 2. Within the next four clock cycles, write a logical "0" to WDE. This disables the Watchdog.

- Bits 2..0 WDP2, WDP1, WDP0: Watchdog Timer Prescaler Bits 2, 1, and 0

The WDP2, WDP1 and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding time-out periods are shown in Table 15.

| WDP2 | WDP1 | WDP0 | Time-out Period |

|------|------|------|-----------------|

| 0    | 0    | 0    | 16K cycles      |

| 0    | 0    | 1    | 32K cycles      |

| 0    | 1    | 0    | 64K cycles      |

| 0    | 1    | 1    | 128K cycles     |

| 1    | 0    | 0    | 256K cycles     |

| 1    | 0    | 1    | 512K cycles     |

| 1    | 1    | 0    | 1,024K cycles   |

| 1    | 1    | 1    | 2,048K cycles   |

Table 15.

Watchdog Timer Prescale Select

The user should poll the EEWE bit before starting the read operation. If a write operation is in progress when new data or address is written to the EEPROM I/O Registers, the write operation will be interrupted and the result is undefined.

The calibrated oscillator is used to time EEPROM. In Table 16 the typical programming time is listed for EEPROM access from the CPU.

| Table 16. | Typical | EEPROM | Programming | Times |

|-----------|---------|--------|-------------|-------|

|-----------|---------|--------|-------------|-------|

| Parameter                  | Number of Calibrated RC | Min Programming | Max Programming |  |

|----------------------------|-------------------------|-----------------|-----------------|--|

|                            | Oscillator Cycles       | Time            | Time            |  |

| EEPROM write<br>(from CPU) | 8192                    | 4.6 ms          | 8.2 ms          |  |

# Preventing EEPROM Corruption

During periods of low  $V_{CC}$ , the EEPROM data can be corrupted because the supply voltage is too low for the CPU and the EEPROM to operate properly. These issues are the same as for board-level systems using the EEPROM and the same design solutions should be applied.

An EEPROM data corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the EEPROM requires a minimum voltage to operate correctly. Second, the CPU itself can execute instructions incorrectly if the supply voltage for executing instructions is too low.

EEPROM data corruption can easily be avoided by following these design recommendations (one is sufficient):

- Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal Brown-out Detector (BOD) if the operating voltage matches the detection level. If not, an external low V<sub>CC</sub> Reset Protection circuit can be applied.

- Keep the AVR core in Power-down sleep mode during periods of low V<sub>CC</sub>. This will prevent the CPU from attempting to decode and execute instructions, effectively protecting the EEPROM Registers from unintentional writes.

- 3. Store constants in Flash memory if the ability to change memory contents from software is not required. Flash memory cannot be updated by the CPU and will not be subject to corruption.

# The Analog Comparator

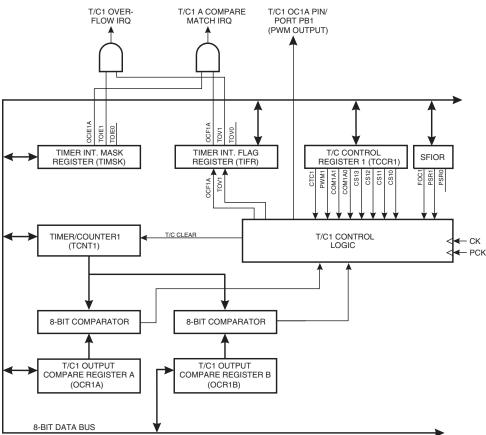

The Analog Comparator compares the input values on the positive pin PB0 (AIN0) and negative pin PB1 (AIN1). When the voltage on the positive pin PB0 (AIN0) is higher than the voltage on the negative pin PB1 (AIN1), the Analog Comparator Output (ACO) is set (one). The comparator's output can trigger a separate interrupt, exclusive to the Analog Comparator. The user can select interrupt triggering on comparator output rise, fall or toggle. A block diagram of the Comparator and its surrounding logic is shown in Figure 24.

### • Bit 7 – ACD: Analog Comparator Disable

When this bit is set (one), the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. This will reduce power consumption in Active and Idle mode. When changing the ACD-bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

# • Bit 6 – ACBG: Analog Comparator Bandgap Select

When this bit is set, a fixed bandgap voltage of  $1.22 \pm 0.05V$  replaces the normal input to the positive pin (AIN0) of the comparator. When this bit is cleared, the normal input pin PB0 is applied to the positive pin of the comparator.

# • Bit 5 – ACO: Analog Comparator Output

ACO is directly connected to the comparator output.

### • Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set (one) when a comparator output event triggers the interrupt mode defined by ACI1 and ACI0. The Analog Comparator Interrupt routine is executed if the ACIE bit is set (one) and the I-bit in SREG is set (one). ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logical "1" to the flag.

| I/O Port B                         | All AVR por<br>ports. This r<br>ally changin<br>applies for o<br>resistors (if                                        | means th<br>ig the dii<br>changing                                 | nat the di<br>rection of<br>g drive va                     | rection of<br>any oth<br>lue (if c                      | of one po<br>ner pin wi                                    | ort pin ca<br>ith the SI                             | n be cha<br>Bl and C                                | anged wi<br>BI instru                                         | thout uninctions. T                                           | ntention-<br>he same                                         |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------|

|                                    | Port B is a 6-bit bi-directional I/O port.                                                                            |                                                                    |                                                            |                                                         |                                                            |                                                      |                                                     |                                                               |                                                               |                                                              |

|                                    | Three data<br>Register –<br>Pins – PINE<br>and the Dat                                                                | PORTB,<br>3, \$16. T                                               | , \$18, Da<br>The Port                                     | ata Dire<br>B Input                                     | ction Reg<br>Pins add                                      | gister – I<br>Iress is r                             | DDRB, \$                                            | 617, and                                                      | the Port                                                      | t B Input                                                    |

|                                    | Ports PB5<br>page 4. If P<br>open-drain<br>ridden with                                                                | PB5 is no<br>output. A                                             | ot configu<br>All I/O pir                                  | ured as                                                 | External                                                   | Reset, i                                             | it is inpu                                          | t with no                                                     | pull-up                                                       | or as an                                                     |

|                                    | The Port B<br>directly. PB<br>nally pulled                                                                            | 5 can sir                                                          | nk 12 mA                                                   | . When                                                  | pins PB                                                    | 0 to PB4                                             | are use                                             | d as inpu                                                     | uts and a                                                     | re exter-                                                    |

| Unconnected Pins                   | If some pine<br>level. The s<br>internal pull<br>sumption du<br>down. Conr<br>may cause                               | implest<br>-up. In tl<br>uring res<br>necting u                    | method t<br>his case,<br>et is impo<br>unused p            | o ensur<br>the pull<br>ortant, it<br>ins diree          | e a defin<br>I-up will t<br>is recom<br>ctly to Vo         | ed level<br>be disabl<br>nmendec<br>c or GN          | of an un<br>ed durin<br>I to use a<br>D is not      | used pir<br>g reset.<br>an exterr<br>recomm                   | n, is to er<br>If low por<br>nal pull-up<br>ended, s          | nable the<br>wer con-<br>p or pull-<br>ince this             |

| Alternative Functions of<br>Port B | In ATtiny15<br>inputs for th<br>these do no<br>conversion.<br>triggers of th<br>voltage clos<br>power cons<br>page 4. | ne ADC.<br>t switch<br>During<br>he digita<br>se to V <sub>C</sub> | If some<br>when a c<br>Power-c<br>I inputs a<br>cc/2 to be | Port B<br>conversion<br>lown mo<br>are disco<br>e prese | pins are<br>on is in p<br>ode and<br>onnected<br>nt during | configur<br>rogress.<br>ADC No<br>on these<br>Power- | ed as o<br>This mig<br>ise Red<br>pins. T<br>down w | utputs, it<br>ht corrup<br>uction m<br>his allow<br>ithout ca | t is essen<br>of the res<br>ode, the<br>s an ana<br>ausing ex | ntial that<br>ult of the<br>Schmitt<br>log input<br>xcessive |

|                                    | When the p<br>ters have to<br>External Re                                                                             | be set a                                                           | according                                                  | to the a                                                | alternate                                                  | function                                             | descript                                            | ion. Whe                                                      | en PB5 is                                                     | used as                                                      |

| The Port B Data Register –         |                                                                                                                       |                                                                    |                                                            |                                                         |                                                            |                                                      |                                                     |                                                               |                                                               |                                                              |

| PORTB                              | Bit                                                                                                                   | 7                                                                  | 6                                                          | 5                                                       | 4                                                          | 3                                                    | 2                                                   | 1                                                             | 0                                                             |                                                              |

|                                    | \$18                                                                                                                  | -                                                                  | -                                                          | -                                                       | PORTB4                                                     | PORTB3                                               | PORTB2                                              | PORTB1                                                        | PORTB0                                                        | PORTB                                                        |

|                                    | Read/Write<br>Initial Value                                                                                           | R<br>0                                                             | R<br>0                                                     | R<br>0                                                  | R/W<br>0                                                   | R/WS<br>0                                            | R/W<br>0                                            | R/W<br>0                                                      | R/W<br>0                                                      |                                                              |

|                                    |                                                                                                                       |                                                                    |                                                            |                                                         |                                                            |                                                      |                                                     |                                                               |                                                               |                                                              |

| The Port B Data Direction          | Bit                                                                                                                   | 7                                                                  | 6                                                          | 5                                                       | Л                                                          | 3                                                    | 2                                                   | 1                                                             | 0                                                             |                                                              |

| Register – DDRB                    | ыл<br>\$17                                                                                                            | -                                                                  | 0<br>—                                                     | 5<br>DDB5                                               | 4<br>DDB4                                                  | 3<br>DDB3                                            | Z<br>DDB2                                           | DDB1                                                          | DDB0                                                          | DDRB                                                         |

|                                    | Read/Write                                                                                                            | =<br>R                                                             | R                                                          | R/W                                                     | R/W                                                        | R/W                                                  | R/W                                                 | R/W                                                           | R/W                                                           | 0010                                                         |

|                                    | Initial Value                                                                                                         | 0                                                                  | 0                                                          | 0                                                       | 0                                                          | 0                                                    | 0                                                   | 0                                                             | 0                                                             |                                                              |

# Memory Programming

# Program and Data Memory Lock Bits

The ATtiny15L MCU provides two Lock bits that can be left unprogrammed, "1", or can be programmed, "0", to obtain the additional features listed in Table 23. The Lock bits can only be erased with the Chip Erase command.

### Table 23. Lock Bit Protection Modes

| Memory Lock Bits |     | Bits |                                                          |  |  |

|------------------|-----|------|----------------------------------------------------------|--|--|

| Mode             | LB1 | LB2  | Protection Type                                          |  |  |

| 1                | 1   | 1    | No memory lock features enabled.                         |  |  |

| 2                | 0   | 1    | Further programming of the Flash and EEPROM is disabled. |  |  |

| 3                | 0   | 0    | Same as mode 2, but verify is also disabled.             |  |  |

### **Fuse Bits**

The ATtiny15L has six Fuse bits (BODLEVEL, BODEN, SPIEN, RSTDSBL, and CKSEL1..0). All the Fuse bits are programmable in both High-voltage and Low-voltage Serial Programming modes. Changing the Fuses does not have effect while in programming mode.

- The BODLEVEL Fuse selects the Brown-out Detection level and changes the startup times. See "Brown-out Detection" on page 17. See Table 5 on page 15. Default value is programmed "0".

- When the BODEN Fuse is programed "0", the Brown-out Detector is enabled. See "Brown-out Detection" on page 17. Default value is unprogrammed "1".

- When the SPIEN Fuse bit is programmed "0", Low-voltage Serial Program and Data Downloading is enabled. Default value is programmed "0". Unprogramming this fuse while in the Low-voltage Serial Programming mode will disable future In-System downloading attempts.

- When the RSTDISBL Fuse is programmed "0", the External Reset function of pin PB5 is disabled<sup>(1)</sup>. Default value is unprogrammed "1". Programming this fuse while in the Low-voltage Serial Programming mode will disable future In-System downloading attempts.

- CKSEL1..0 Fuses: See Table 5 on page 15 for which combination of CKSEL1..0 to use. Default value is "00", 64 ms + 18 CK.

The status of the Fuse bits is not affected by Chip Erase.

Note: 1. If the RSTDISBL Fuse is programmed, then the programming hardware should apply +12V to PB5 while the ATtiny15L is in Power-on Reset. If not, the part can fail to enter Programming mode caused by drive contention on PB0 and/or PB5.

# **Signature Bytes** All Atmel microcontrollers have a three-byte signature code that identifies the device.

The three bytes reside in a separate address space, and for the ATtiny15L they are:

- 1. \$000 : \$1E (indicates manufactured by Atmel).

- 2. \$001 : \$90 (indicates 1 Kb Flash memory).

- 3. \$002 : \$06 (indicates ATtiny15L device when \$001 is \$90).

# ATtiny15L

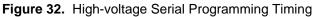

# High-voltage Serial Programming Characteristics

**Table 26.** High-voltage Serial Programming Characteristics,  $T_A = 25^{\circ}C \pm 10^{\circ}$ ,  $V_{CC} = 5.0V \pm 10^{\circ}$  (unless otherwise noted)

| Symbol            | Parameter                                                 | Min  | Тур  | Max  | Units |

|-------------------|-----------------------------------------------------------|------|------|------|-------|

| t <sub>SHSL</sub> | SCI (PB3) Pulse Width High                                | 25.0 |      |      | ns    |

| t <sub>SLSH</sub> | SCI (PB3) Pulse Width Low                                 | 25.0 |      |      | ns    |

| t <sub>IVSH</sub> | SDI (PB0), SII (PB1) Valid to SCI (PB3) High (8th edge)   | 50.0 |      |      | ns    |

| t <sub>SHIX</sub> | SDI (PB0), SII (PB1) Hold after SCI (PB3) High (8th edge) | 50.0 |      |      | ns    |

| t <sub>SHOV</sub> | SCI (PB3) High (9th edge) to SDO (PB2) Valid              | 10.0 | 16.0 | 32.0 | ns    |

# Low-voltage Serial Downloading

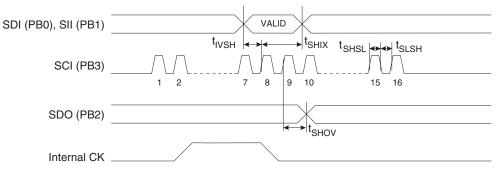

Both the program and data memory arrays can be programmed using the SPI bus while RESET is pulled to GND. The serial interface consists of pins SCK, MOSI (input) and MISO (output). See Figure 33. After RESET is set low, the Programming Enable instruction needs to be executed first before program/erase instructions can be executed.

### Figure 33. Serial Programming and Verify

For the EEPROM, an auto-erase cycle is provided within the self-timed write instruction and there is no need to first execute the Chip Erase instruction. The Chip Erase instruction turns the content of every memory location in both the program and EEPROM arrays into \$FF.

The program and EEPROM memory arrays have separate address spaces: \$0000 to \$01FF for Program memory and \$000 to \$03F for EEPROM memory.

The device is clocked from the internal clock at the uncalibrated minimum frequency (0.8 - 1.6 MHz). The minimum low and high periods for the serial clock (SCK) input are defined as follows:

Low: > 2 MCU clock cycles

High: > 2 MCU clock cycles

### Low-voltage Serial Programming Algorithm

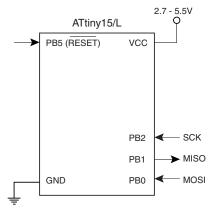

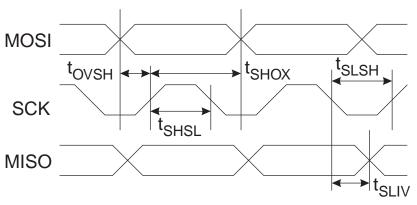

When writing serial data to the ATtiny15L, data is clocked on the rising edge of SCK. When reading data from the ATtiny15L, data is clocked on the falling edge of SCK. See Figure 34, Figure 35, and Table 28 for timing details. To program and verify the ATtiny15L in the Serial Programming mode, the following sequence is recommended (See 4-byte instruction formats in Table 27):

1. Power-up sequence:

Apply power between  $V_{CC}$  and GND while RESET and SCK are set to "0". If the programmer cannot guarantee that SCK is held low during Power-up, RESET must be given a positive pulse of at least two MCU cycles duration after SCK has been set to "0".

- 2. Wait for at least 20 ms and enable serial programming by sending the Programming Enable serial instruction to the MOSI (PB0) pin. Refer to the above section for minimum low and high periods for the serial clock input SCK.

- 3. The serial programming instructions will not work if the communication is out of synchronization. When in sync, the second byte (\$53) will echo back when issuing the third byte of the Programming Enable instruction. Whether the echo is correct or not, all four bytes of the instruction must be transmitted. If the \$53 did not echo back, give SCK a positive pulse and issue a new Programming Enable instruction. If the \$53 is not seen within 32 attempts, there is no functional device connected.

- If a Chip Erase is performed (must be done to erase the Flash), wait t<sub>WD\_ERASE</sub> after the instruction, give RESET a positive pulse, and start over from step 2. See Table 29 on page 63 for t<sub>WD\_ERASE</sub> value.

- 5. The Flash or EEPROM array is programmed one byte at a time by supplying the address and data together with the appropriate write instruction. An EEPROM memory location is first automatically erased before new data is written. Use data polling to detect when the next byte in the Flash or EEPROM can be written. If polling is not used, wait t<sub>WD\_PROG\_FL</sub> or t<sub>WD\_PROG\_EE</sub>, respectively, before transmitting the next instruction. See Table 30 on page 63 for the t<sub>WD\_PROG\_FL</sub> and t<sub>WD\_PROG\_EE</sub> values. In an erased device, no \$FFs in the data file(s) need to be programmed.

- 6. Any memory location can be verified by using the Read instruction, which returns the content at the selected address at the serial output MISO (PB1) pin.

- 7. At the end of the programming session, **RESET** can be set high to commence normal operation.

- 8. Power-off sequence (if needed):

Set RESET to "1".

Turn  $V_{CC}$  power off.

Low-voltage Serial Programming Characteristics

| Table 28.            | Low-voltage Serial Programming Characteristics, $T_A = -40^{\circ}C$ to $85^{\circ}C$ , |

|----------------------|-----------------------------------------------------------------------------------------|

| $V_{\rm CC} = 2.7$ - | 5.5V (Unless Otherwise Noted)                                                           |

| Symbol              | Parameter                                         | Min                   | Тур   | Max    | Units |

|---------------------|---------------------------------------------------|-----------------------|-------|--------|-------|

| 1/t <sub>CLCL</sub> | RC Oscillator Frequency ( $V_{CC} = 2.7 - 5.5V$ ) | 0.8                   | 1.6   |        | MHz   |

| t <sub>CLCL</sub>   | RC Oscillator Period ( $V_{CC} = 2.7 - 5.5V$ )    |                       | 625.0 | 1250.0 | ns    |

| t <sub>SHSL</sub>   | SCK Pulse Width High                              | 2.0 t <sub>CLCL</sub> |       |        | ns    |

| t <sub>SLSH</sub>   | SCK Pulse Width Low                               | 2.0 t <sub>CLCL</sub> |       |        | ns    |

| t <sub>OVSH</sub>   | MOSI Setup to SCK High                            | t <sub>CLCL</sub>     |       |        | ns    |

| t <sub>SHOX</sub>   | MOSI Hold after SCK High                          | 2.0 t <sub>CLCL</sub> |       |        | ns    |

| t <sub>SLIV</sub>   | SCK Low to MISO Valid                             | 10.0                  | 16.0  | 32.0   | ns    |

| Table 29. | Minimum Wait De | lay after the Chip Erase | Instruction |

|-----------|-----------------|--------------------------|-------------|

|-----------|-----------------|--------------------------|-------------|

| Symbol                | Minimum Wait Delay |

|-----------------------|--------------------|

| t <sub>WD_ERASE</sub> | 8.2 ms             |

Table 30. Minimum Wait Delay after Writing a Flash or EEPROM Location

| Symbol                 | Minimum Wait Delay |

|------------------------|--------------------|

| t <sub>WD_FLASH</sub>  | 4.1 ms             |

| t <sub>WD_EEPROM</sub> | 8.2 ms             |

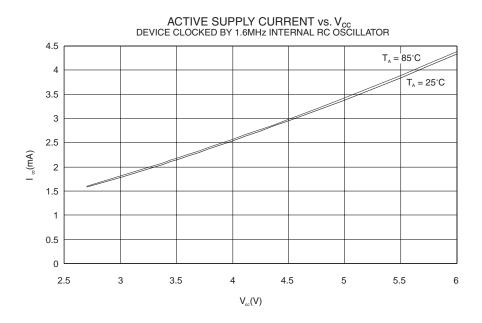

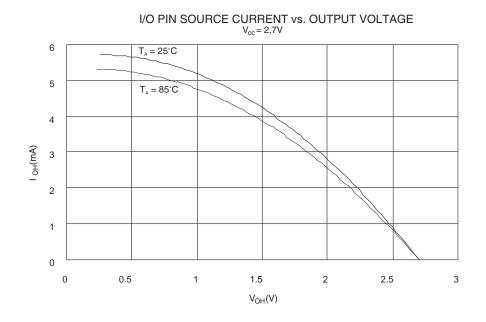

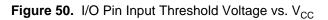

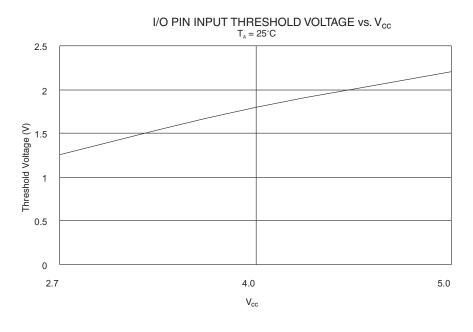

# Typical Characteristics

The following charts show typical behavior. These data are characterized but not tested. All current consumption measurements are performed with all I/O pins configured as inputs and with internal pull-ups enabled.

The current consumption is a function of several factors such as: Operating voltage, operating frequency, loading of I/O pins, switching rate of I/O pins, code executed and ambient temperature. The dominating factors are operating voltage and frequency.

The current drawn from capacitive loaded pins may be estimated (for one pin) as  $C_L \bullet V_{CC} \bullet f$  where  $C_L$  = load capacitance,  $V_{CC}$  = operating voltage and f = average switching frequency of I/O pin.

The difference between current consumption in Power-down mode with Watchdog Timer enabled and Power-down mode with Watchdog Timer disabled represents the differential current drawn by the Watchdog Timer.

Figure 36. Active Supply Current vs. V<sub>CC</sub>

Figure 49. I/O Pin Source Current vs. Output Voltage

# ATtiny15L Register Summary

| Address | Name     | Bit 7 | Bit 6  | Bit 5    | Bit 4            | Bit 3            | Bit 2       | Bit 1  | Bit 0  | Page    |

|---------|----------|-------|--------|----------|------------------|------------------|-------------|--------|--------|---------|

| \$3F    | SREG     | I     | т      | н        | S                | V                | N           | Z      | С      | page 11 |

| \$3E    | Reserved |       | •      | •        | •                |                  | •           | •      |        |         |

| \$3C    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$3B    | GIMSK    | -     | INT0   | PCIE     | -                | -                | -           | -      | -      | page 19 |

| \$3A    | GIFR     | -     | INTF0  | PCIF     | -                | -                | -           | -      | -      | page 20 |

| \$39    | TIMSK    | -     | OCIE1A | -        | -                | -                | TOIE1       | TOIE0  | -      | page 20 |

| \$38    | TIFR     | -     | OCF1A  | -        | -                | -                | TOV1        | TOV0   | -      | page 21 |

| \$37    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$36    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$35    | MCUCR    | -     | PUD    | SE       | SM1              | SM0              | -           | ISC01  | ISC00  | page 22 |

| \$34    | MCUSR    | -     | -      | -        | -                | WDRF             | BORF        | EXTRF  | PORF   | page 18 |

| \$33    | TCCR0    | -     | -      | -        | -                | -                | CS02        | CS01   | CS00   | page 27 |

| \$32    | TCNT0    |       |        |          | Timer/Cou        | nter0 (8-Bit)    |             |        |        | page 28 |

| \$31    | OSCCAL   |       |        |          | Oscillator Calil | oration Register |             |        |        | page 24 |

| \$30    | TCCR1    | CTC1  | PWM1   | COM1A1   | COM1A0           | CS13             | CS12        | CS11   | CS10   | page 29 |

| \$2F    | TCNT1    |       |        |          | Timer/Cou        | nter1 (8-Bit)    |             |        |        | page 30 |

| \$2E    | OCR1A    |       |        | Timer/Co | ounter1 Output C | compare Registe  | r A (8-Bit) |        |        | page 31 |

| \$2D    | OCR1B    |       |        | Timer/Co | ounter1 Output C | compare Registe  | r B (8-Bit) |        |        | page 32 |

| \$2C    | SFIOR    | -     | -      | -        | -                | -                | FOC1A       | PSR1   | PSR0   | page 26 |

| \$2B    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$2A    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$29    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$28    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$27    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$26    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$25    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$24    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$23    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$22    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$21    | WDTCR    | -     | -      | -        | WDTOE            | WDE              | WDP2        | WDP1   | WDP0   | page 34 |

| \$20    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$1F    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$1E    | EEAR     | -     | -      | EEAR5    | EEAR4            | EEAR3            | EEAR2       | EEAR1  | EEAR0  | page 36 |

| \$1D    | EEDR     |       |        |          | EEPROM Data      | Register (8-Bit) |             |        |        | page 36 |

| \$1C    | EECR     | -     | -      | -        | -                | EERIE            | EEMWE       | EEWE   | EERE   | page 37 |

| \$1B    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$1A    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$19    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$18    | PORTB    | -     | -      | -        | PORTB4           | PORTB3           | PORTB2      | PORTB1 | PORTB0 | page 51 |

| \$17    | DDRB     | -     | -      | DDB5     | DDB4             | DDB3             | DDB2        | DDB1   | DDB0   | page 51 |

| \$16    | PINB     | -     | -      | PINB5    | PINB4            | PINB3            | PINB2       | PINB1  | PINB0  | page 52 |

| \$15    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$14    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$13    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$12    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$11    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$10    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$0F    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$0E    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$0D    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$0C    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$0B    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$0A    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$09    | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$08    | ACSR     | ACD   | ACBG   | ACO      | ACI              | ACIE             | -           | ACIS1  | ACIS0  | page 39 |

| \$07    | ADMUX    | REFS1 | REFS0  | ADLAR    | -                | -                | MUX2        | MUX1   | MUX0   | page 46 |

| \$06    | ADCSR    | ADEN  | ADSC   | ADFR     | ADIF             | ADIE             | ADPS2       | ADPS1  | ADPS0  | page 47 |

| \$05    | ADCH     |       |        |          | ADC Data Reg     | gister High Byte |             |        |        | page 49 |

| \$04    | ADCL     |       |        |          | ADC Data Re      | gister Low Byte  |             |        |        | page 49 |

|         | Reserved |       |        |          |                  |                  |             |        |        |         |

| \$00    | Reserved |       |        |          |                  |                  |             |        |        |         |

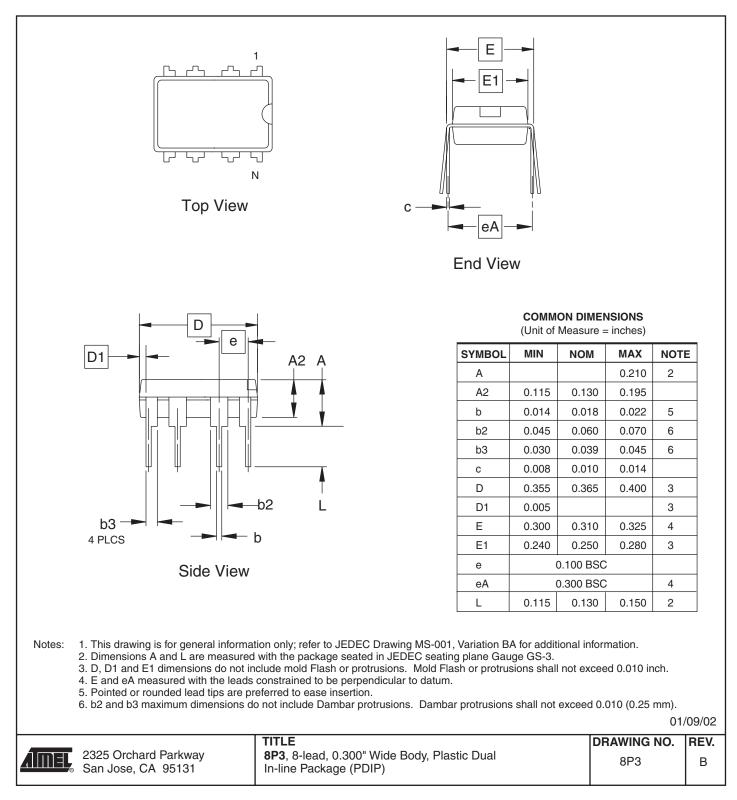

# **Packaging Information**

8P3

80

ATtiny15L

| I/O Port B                                      | 51   |

|-------------------------------------------------|------|

| Memory Programming                              | 54   |

| Program and Data Memory Lock Bits               | . 54 |

| Fuse Bits                                       | . 54 |

| Signature Bytes                                 | . 54 |

| Calibration Byte                                | . 55 |

| Programming the Flash                           | . 55 |

| High-voltage Serial Programming                 | . 55 |

| High-voltage Serial Programming Algorithm       | . 56 |

| High-voltage Serial Programming Characteristics | . 59 |

| Low-voltage Serial Downloading                  | . 59 |

| Low-voltage Serial Programming Characteristics  | . 63 |

| Electrical Characteristics                      | 64   |

| Absolute Maximum Ratings                        | . 64 |

| DC Characteristics                              |      |

| Typical Characteristics                         | 66   |

| ATtiny15L Register Summary                      | 75   |

| ATtiny15L Instruction Set Summary               | 76   |

| Ordering Information                            | 78   |

| Packaging Information                           | 79   |

| 8P3                                             |      |

| 8S2                                             | . 80 |

| Datasheet revision history                      | 81   |

| Rev H - 09/07                                   |      |

| Rev G - 06/07                                   |      |

| Rev F - 06/05                                   |      |

| Table of Contents                               | i    |

ii