Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                 |

|----------------------------|----------------------------------------------------------|

| Core Processor             | AVR                                                      |

| Core Size                  | 8-Bit                                                    |

| Speed                      | 1.6MHz                                                   |

| Connectivity               | -                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                    |

| Number of I/O              | 6                                                        |

| Program Memory Size        | 1KB (512 x 16)                                           |

| Program Memory Type        | FLASH                                                    |

| EEPROM Size                | 64 x 8                                                   |

| RAM Size                   | ·                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                              |

| Data Converters            | A/D 4x10b                                                |

| Oscillator Type            | Internal                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                        |

| Mounting Type              | Surface Mount                                            |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                            |

| Supplier Device Package    | 8-SOIC                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/attiny15l-1si |

|                            |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Description

The ATtiny15L is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the ATtiny15L achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATtiny15L provides 1K byte of Flash, 64 bytes EEPROM, six general purpose I/O lines, 32 general purpose working registers, two 8-bit Timer/Counters, one with high-speed PWM output, internal Oscillators, internal and external interrupts, programmable Watchdog Timer, 4-channel 10-bit Analog-to-Digital Converter with one differential voltage input with optional 20x gain, and three software-selectable Power-saving modes. The Idle mode stops the CPU while allowing the ADC, anAlog Comparator, Timer/Counters and interrupt system to continue functioning. The ADC Noise Reduction mode facilitates high-accuracy ADC measurements by stopping the CPU while allowing the ADC to continue functioning. The Power-down mode saves the register contents but freezes the Oscillators, disabling all other chip functions until the next interrupt or Hardware Reset. The wake-up or interrupt on pin change features enable the ATtiny15L to be highly responsive to external events, still featuring the lowest power consumption while in the Power-saving modes.

The device is manufactured using Atmel's high-density, Non-volatile memory technology. By combining a RISC 8-bit CPU with Flash on a monolithic chip, the ATtiny15L is a powerful microcontroller that provides a highly flexible and cost-efficient solution to many embedded control applications. The peripheral features make the ATtiny15L particularly suited for battery chargers, lighting ballasts and all kinds of intelligent sensor applications.

The ATtiny15L AVR is supported with a full suite of program and system development tools including macro assemblers, program debugger/simulators, In-circuit emulators and evaluation kits.

A flexible interrupt module has its control registers in the I/O space with an additional Global Interrupt Enable bit in the Status Register. All the different interrupts have a separate Interrupt Vector in the Interrupt Vector table at the beginning of the program memory. The different interrupts have priority in accordance with their Interrupt Vector position. The lower the Interrupt Vector address, the higher the priority.

### The General Purpose Register File

Figure 3 shows the structure of the 32 general purpose registers in the CPU.

Figure 3. AVR CPU General Purpose Working Registers

General Purpose Working Registers

| 7               | 0             |

|-----------------|---------------|

| R               | )             |

| R               | I             |

| Rź              | 2             |

|                 |               |

|                 |               |

| R2              | 8             |

| R2              | 9             |

| R30 (Z-register | Low Byte)     |

| R31 (Z-registe  | er High Byte) |

All the register operating instructions in the instruction set have direct- and single-cycle access to all registers. The only exception is the five constant arithmetic and logic instructions SBCI, SUBI, CPI, ANDI, and ORI between a constant and a register and the LDI instruction for load-immediate constant data. These instructions apply to the second half of the registers in the Register File – R16..R31. The general SBC, SUB, CP, AND, OR, and all other operations between two registers or on a single-register apply to the entire Register File.

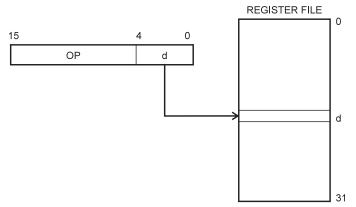

Registers 30 and 31 form a 16-bit pointer (the Z-pointer) which is used for indirect Flash memory and Register File access. When the Register File is accessed, the contents of R31 is discarded by the CPU.

| The ALU – Arithmetic<br>Logic Unit | The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, ALU operations between registers in the Register File are executed. The ALU operations are divided into three main categories – arithmetic, logic and bit-functions. Some microcontrollers in the AVR product family feature a hardware multiplier in the arithmetic part of the ALU. |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The Flash Program<br>Memory        | The ATtiny15L contains 1K byte On-chip, In-System Programmable Flash memory for program storage. Since all instructions are single 16-bit words, the Flash is organized as 512 x 16 words. The Flash memory has an endurance of at least 1,000 write/erase cycles.                                                                                                                                                               |

|                                    | The ATtiny15L Program Counter is nine bits wide, thus addressing the 512 words Flash Program memory.                                                                                                                                                                                                                                                                                                                             |

|                                    | See page 54 for a detailed description on Flash memory programming.                                                                                                                                                                                                                                                                                                                                                              |

# The Program and Data Addressing Modes

The ATtiny15L AVR RISC Microcontroller supports powerful and efficient addressing modes. This section describes the various addressing modes supported in the ATtiny15L. In the figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits.

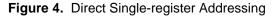

Register Direct, Singleregister Rd

The operand is contained in register d (Rd).

### **Register Indirect**

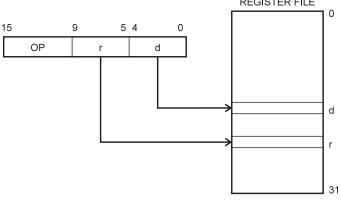

Figure 5. Indirect Register Addressing

The register accessed is the one pointed to by the Z-register low byte (R30).

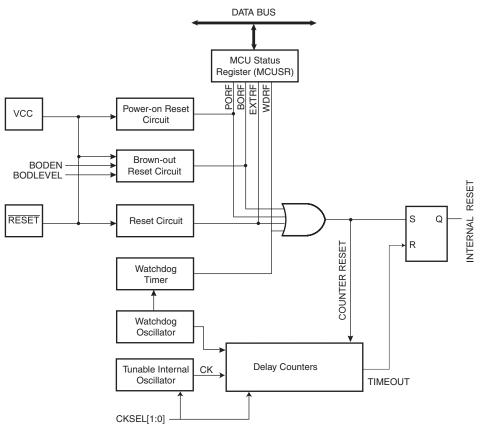

Figure 12. Reset Logic

**Table 4.** Reset Characteristics  $(V_{CC} = 5.0V)^{(1)}$

| Symbol           | Parameter                        | Condition      | Min | Тур | Max                  | Units |

|------------------|----------------------------------|----------------|-----|-----|----------------------|-------|

|                  | Power-on Reset Threshold         | BOD disabled   | 1.0 | 1.4 | 1.8                  | V     |

| V <sub>POT</sub> | Voltage (rising)                 | BOD enabled    | 1.7 | 2.2 | 2.7                  | V     |

|                  | Power-on Reset Threshold         | BOD disabled   | 0.4 | 0.6 | 0.8                  | V     |

|                  | Voltage (falling) <sup>(1)</sup> | BOD enabled    | 1.7 | 2.2 | 2.7                  | V     |

| V <sub>RST</sub> | RESET Pin Threshold<br>Voltage   |                | _   | _   | 0.85 V <sub>CC</sub> | V     |

|                  | Brown-out Reset Threshold        | (BODLEVEL = 1) | 2.3 | 2.7 | 2.9                  | V     |

| V <sub>BOT</sub> | Voltage                          | (BODLEVEL = 0) | 3.4 | 4.0 | 4.3                  | V     |

Note: 1. The Power-on Reset will not work unless the supply voltage has been below  $V_{\text{POT}}$  (falling).

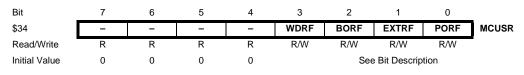

MCU Status Register – MCUSR The MCU Status Register provides information on which reset source caused an MCU Reset.

### • Bit 7..4 - Res: Reserved Bits

These bits are reserved bits in the ATtiny15L and always read as zero.

### • Bit 3 – WDRF: Watchdog Reset Flag

This bit is set (one) if a Watchdog Reset occurs. The bit is reset (zero) by a Power-on Reset, or by writing a logical "0" to the flag.

### Bit 2 – BORF: Brown-out Reset Flag

This bit is set (one) if a Brown-out Reset occurs. The bit is reset (zero) by a Power-on Reset, or by writing a logical "0" to the flag.

### Bit 1 – EXTRF: External Reset Flag

This bit is set (one) if a External Reset occurs. The bit is reset (zero) by a Power-on Reset, or by writing a logical "0" to the flag.

#### Bit 0 – PORF: Power-on Reset Flag

This bit is set (one) if a Power-on Reset occurs. The bit is reset (zero) by writing a logical "0" to the flag.

To make use of the Reset Flags to identify a reset condition, the user should read and then reset the MCUSR as early as possible in the program. If the register is cleared before another reset occurs, the source of the reset can be found by examining the Reset Flags.

Internal VoltageATtiny15L features an internal bandgap reference with a nominal voltage of 1.22V. ThisReferencereference is used for Brown-out Detection, and it can be used as an input to the Analog<br/>Comparator. The 2.56V reference to the ADC is generated from the internal bandgap<br/>reference.

Voltage Reference Enable Signals and Start-up Time

The voltage reference has a start-up time that may influence the way it should be used. The maximum start-up time is 10  $\mu$ s. To save power, the reference is not always turned on. The reference is on during the following situations:

- 1. When the BOD is enabled (by programming the BODEN Fuse).

- 2. When the bandgap reference is connected to the Analog Comparator (by setting the AINBG bit in ACSR).

- 3. When the ADC is enabled.

Thus, when the BOD is not enabled, after setting the AINBG bit, the user must always allow the reference to start-up before the output from the Analog Comparator is used. The bandgap reference uses typically 10  $\mu$ A, and to reduce power consumption in Power-down mode, the user can avoid the three conditions above to ensure that the reference is turned off before entering Power-down mode.

vector \$003) is executed if a compare match A in Timer/Counter1 occurs, i.e., when the OCF1A bit is set (one) in the Timer/Counter Interrupt Flag Register (TIFR).

### • Bit 5..3 - Res: Reserved Bits

These bits are reserved bits in the ATtiny15L and always read as zero.

### Bit 2 – TOIE1: Timer/Counter1 Overflow Interrupt Enable

When the TOIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 Overflow interrupt is enabled. The corresponding interrupt (at vector \$004) is executed if an overflow in Timer/Counter1 occurs, i.e., when the TOV1 bit is set (one) in the Timer/Counter Interrupt Flag Register (TIFR).

### • Bit 1 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt (at vector \$005) is executed if an overflow in Timer/Counter0 occurs, i.e., when the TOV0 bit is set (one) in the Timer/Counter Interrupt Flag Register (TIFR).

### • Bit 0 - Res: Reserved Bit

This bit is a reserved bit in the ATtiny15L and always reads as zero.

### The Timer/Counter Interrupt Flag Register – TIFR

| Bit           | 7 | 6     | 5 | 4 | 3 | 2    | 1    | 0 |      |

|---------------|---|-------|---|---|---|------|------|---|------|

| \$38          | - | OCF1A | - | - | - | TOV1 | TOV0 | - | TIFR |

| Read/Write    | R | R/W   | R | R | R | R/W  | R/W  | R | -    |

| Initial Value | 0 | 0     | 0 | 0 | 0 | 0    | 0    | 0 |      |

### • Bit 7 - Res: Reserved Bit

This bit is a reserved bit in the ATtiny15L and always reads as zero.

### Bit 6 – OCF1A: Output Compare Flag 1A

The OCF1A bit is set (one) when compare match occurs between Timer/Counter1 and the data value in OCR1A (Output Compare Register 1A). OCF1A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1A is cleared by writing a logical "1" to the flag. When the I-bit in SREG, OCIE1A, and OCF1A are set (one), the Timer/Counter1 compare match A interrupt is executed.

### • Bits 5..3 - Res: Reserved bits

These bits are reserved bits in the ATtiny15L and always read as zero.

### Bit 2 – TOV1: Timer/Counter1 Overflow Flag

The bit TOV1 is set (one) when an overflow occurs in Timer/Counter1. TOV1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV1 is cleared by writing a logical "1" to the flag. When the SREG I-bit, TOIE1 (Timer/Counter1 Overflow Interrupt Enable) and TOV1 are set (one), the Timer/Counter1 Overflow Interrupt is executed.

### • Bits 4, 3 – SM1, SM0: Sleep Mode Select Bits 1 and 0

These bits select between the three available sleep modes, as shown in Table 7.

Table 7. Sleep Modes

| SM1 | SM0 | Sleep Mode               |

|-----|-----|--------------------------|

| 0   | 0   | Idle mode                |

| 0   | 1   | ADC Noise Reduction mode |

| 1   | 0   | Power-down mode          |

| 1   | 1   | Reserved                 |

For details, refer to "Sleep Modes" below.

### • Bit 2 - Res: Reserved Bit

This bit is a reserved bit in the ATtiny15L and always reads as zero.

### • Bits 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask is set (one). The activity on the external INT0 pin that activates the interrupt is defined in Table 8:

| Table 8. Inte | rrupt 0 Sense | Control <sup>(1)</sup> |

|---------------|---------------|------------------------|

|---------------|---------------|------------------------|

| ISC01 | ISC00 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT0 generates an interrupt request.    |

| 0     | 1     | Any change on INT0 generates an interrupt request        |

| 1     | 0     | The falling edge of INT0 generates an interrupt request. |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.  |

Note: 1. When changing the ISC10/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK Register. Otherwise an interrupt can occur when the bits are changed.

**Sleep Modes**

**Idle Mode**

To enter any of the three sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruction must be executed. The SM1 and SM0 bits in the MCUCR Register select which sleep mode (Idle, ADC Noise Reduction or Power-down) will be activated by the SLEEP instruction (see Table 7). If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU wakes up. The MCU is then halted for four cycles, executes the interrupt routine and resumes execution from the instruction following SLEEP. On wake-up from Power-down mode on pin change, two instruction cycles are executed before the Pin Change Interrupt Flag is updated. The contents of the Register File, SRAM, and I/O memory are unaltered when the device wakes up from sleep. If a reset occurs during sleep mode, the MCU wakes up and executes from the Reset Vector.

When the SM1/SM0 bits are "00", the SLEEP instruction forces the MCU into the Idle mode, stopping the CPU but allowing the ADC, Analog Comparator, Timer/Counters, Watchdog and the Interrupt system to continue operating. This enables the MCU to wake-up from external triggered interrupts as well as internal ones like the Timer Overflow Interrupt and Watchdog Reset. If the ADC is enabled, a conversion starts automatically when this mode is entered. If wake-up from the Analog Comparator interrupt is not required, the Analog Comparator can be powered down by setting the ADCbit in the Analog Comparator Control and Status Register (ACSR). This will reduce power consumption in Idle mode.

## ATtiny15L

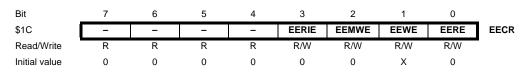

#### The EEPROM Control Register – EECR

### • Bit 7..4 – RES: Reserved Bits

These bits are reserved bits in the ATtiny15L and will always read as zero.

### • Bit 3 – EERIE: EEPROM Ready Interrupt Enable

When the I-bits in SREG and EERIE are set (one), the EEPROM Ready Interrupt is enabled. When cleared (zero), the interrupt is disabled. The EEPROM Ready Interrupt generates a constant interrupt when EEWE is cleared (zero).

## • Bit 2 – EEMWE: EEPROM Master Write Enable

The EEMWE bit determines whether setting EEWE to one causes the EEPROM to be written. When EEMWE is set (one), setting EEWE will write data to the EEPROM at the selected address. If EEMWE is zero, setting EEWE will have no effect. When EEMWE has been set (one) by software, hardware clears the bit to zero after four clock cycles. See the description of the EEWE bit for an EEPROM write procedure.

## • Bit 1 – EEWE: EEPROM Write Enable

The EEPROM Write Enable Signal – EEWE – is the write strobe to the EEPROM. When address and data are correctly set up, the EEWE bit must be set to write the value in to the EEPROM. The EEMWE bit must be set when the logical "1" is written to EEWE, otherwise no EEPROM write takes place. The following procedure should be followed when writing the EEPROM (the order of steps 2 and 3 is not essential):

- 1. Wait until EEWE becomes zero.

- 2. Write new EEPROM address to EEAR (optional).

- 3. Write new EEPROM data to EEDR (optional).

- 4. Write a logical "1" to the EEMWE bit in EECR.

- 5. Within four clock cycles after setting EEMWE, write a logical "1" to EEWE.

**Caution:** An interrupt between step 4 and step 5 will make the write cycle fail, since the EEPROM Master Write Enable will time-out. If an interrupt routine accessing the EEPROM is interrupting another EEPROM access, the EEAR or EEDR Register will be modified, causing the interrupted EEPROM access to fail. It is recommended to have the Global Interrupt Flag cleared during the four last steps to avoid these problems.

When the write access time (typically 5.1 ms if the internal RC Oscillator is calibrated to 1.6 MHz) has elapsed, the EEWE bit is cleared (zero) by hardware. The user software can poll this bit and wait for a zero before writing the next byte. When EEWE has been set, the CPU is halted for two cycles before the next instruction is executed.

## • Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable Signal EERE is the read strobe to the EEPROM. When the correct address is set up in the EEAR Register, the EERE bit must be set. When the EERE bit is cleared (zero) by hardware, requested data is found in the EEDR Register. The EEPROM read access takes one instruction and there is no need to poll the EERE bit. When EERE has been set, the CPU is halted for four cycles before the next instruction is executed.

The user should poll the EEWE bit before starting the read operation. If a write operation is in progress when new data or address is written to the EEPROM I/O Registers, the write operation will be interrupted and the result is undefined.

The calibrated oscillator is used to time EEPROM. In Table 16 the typical programming time is listed for EEPROM access from the CPU.

| Table 16. | Typical | EEPROM | Programming | Times |

|-----------|---------|--------|-------------|-------|

|-----------|---------|--------|-------------|-------|

| Parameter                  | Number of Calibrated RC | Min Programming | Max Programming |  |  |

|----------------------------|-------------------------|-----------------|-----------------|--|--|

|                            | Oscillator Cycles       | Time            | Time            |  |  |

| EEPROM write<br>(from CPU) | 8192                    | 4.6 ms          | 8.2 ms          |  |  |

### Preventing EEPROM Corruption

During periods of low  $V_{CC}$ , the EEPROM data can be corrupted because the supply voltage is too low for the CPU and the EEPROM to operate properly. These issues are the same as for board-level systems using the EEPROM and the same design solutions should be applied.

An EEPROM data corruption can be caused by two situations when the voltage is too low. First, a regular write sequence to the EEPROM requires a minimum voltage to operate correctly. Second, the CPU itself can execute instructions incorrectly if the supply voltage for executing instructions is too low.

EEPROM data corruption can easily be avoided by following these design recommendations (one is sufficient):

- Keep the AVR RESET active (low) during periods of insufficient power supply voltage. This can be done by enabling the internal Brown-out Detector (BOD) if the operating voltage matches the detection level. If not, an external low V<sub>CC</sub> Reset Protection circuit can be applied.

- Keep the AVR core in Power-down sleep mode during periods of low V<sub>CC</sub>. This will prevent the CPU from attempting to decode and execute instructions, effectively protecting the EEPROM Registers from unintentional writes.

- 3. Store constants in Flash memory if the ability to change memory contents from software is not required. Flash memory cannot be updated by the CPU and will not be subject to corruption.

### • Bits 4..3 - Res: Reserved Bits

These bits are reserved bits in the ATtiny15L and always read as zero.

### • Bits 2..0 – MUX2..MUX0: Analog Channel and Gain Selection Bits 2..0

The value of these bits selects which analog input is connected to the ADC. In case of differential input (PB3 - PB4), gain selection is also made with these bits. Selecting PB3 as both inputs to the differential gain stage enables offset measurements. Refer to Table 20 for details. If these bits are changed during a conversion, the change will not go into effect until this conversion is complete (ADIF in ADCSR is set).

| MUX20              | Single-ended<br>Input | Positive Negative<br>Differential Input Differential Input O |            |     |  |  |  |

|--------------------|-----------------------|--------------------------------------------------------------|------------|-----|--|--|--|

| 000                | ADC0 (PB5)            |                                                              |            |     |  |  |  |

| 001                | ADC1 (PB2)            |                                                              | N/A        |     |  |  |  |

| 010                | ADC2 (PB3)            | - N/A<br>-                                                   |            |     |  |  |  |

| 011                | ADC3 (PB4)            |                                                              |            |     |  |  |  |

| 100 <sup>(1)</sup> |                       | ADC2 (PB3)                                                   | ADC2 (PB3) | 1x  |  |  |  |

| 101 <sup>(1)</sup> | N1/A                  | ADC2 (PB3)                                                   | ADC2 (PB3) | 20x |  |  |  |

| 110                | N/A                   | ADC2 (PB3)                                                   | ADC3 (PB4) | 1x  |  |  |  |

| 111                |                       | ADC2 (PB3)                                                   | ADC3 (PB4) | 20x |  |  |  |

Table 20. Input Channel and Gain Selections

Note: 1. For offset calibration only. See "Operation" on page 42.

### The ADC Control and Status Register – ADCSR

| Bit           | 7    | 6    | 5    | 4    | 3    | 2     | 1     | 0     |       |

|---------------|------|------|------|------|------|-------|-------|-------|-------|

| \$06          | ADEN | ADSC | ADFR | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | ADCSR |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W   | R/W   | R/W   |       |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0     | 0     | 0     |       |

### • Bit 7 – ADEN: ADC Enable

Writing a logical "1" to this bit enables the ADC. By clearing this bit to zero, the ADC is turned off. Turning the ADC off while a conversion is in progress will terminate this conversion.

### • Bit 6 – ADSC: ADC Start Conversion

In Single Conversion mode, a logical "1" must be written to this bit to start each conversion. In Free Running mode, a logical "1" must be written to this bit to start the first conversion.

When the conversion completes, ADSC returns to zero in Single Conversion mode and stays high in Free Running mode.

Writing a "0" to this bit has no effect.

### Bit 5 – ADFR: ADC Free Running Select

When this bit is set (one), the ADC operates in Free Running mode. In this mode, the ADC samples and updates the Data Registers continuously. Clearing this bit (zero) will terminate Free Running mode. If active channels are used (MUX2 in ADMUX set), the

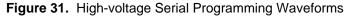

## High-voltage Serial Programming Algorithm

To program and verify the ATtiny15L in the High-voltage Serial Programming mode, the following sequence is recommended (See instruction formats in Table 25):

1. Power-up sequence:

Apply 4.5 - 5.5V between  $V_{CC}$  and GND. Set PB5 and PB0 to "0" and wait at least 30  $\mu s.$

Set PB3 to "0". Wait at least 100 ns.

Apply 12V to PB5 and wait at least 100 ns before changing PB0. Wait 8  $\mu s$  before giving any instructions.

- 2. The Flash array is programmed one byte at a time by supplying first the address, then the low and high data byte. The write instruction is self-timed; wait until the PB2 (RDY/BSY) pin goes high.

- 3. The EEPROM array is programmed one byte at a time by supplying first the address, then the data byte. The write instruction is self-timed; wait until the PB2 (RDY/BSY) pin goes high.

- 4. Any memory location can be verified by using the Read instruction, which returns the contents at the selected address at serial output PB2.

- 5. Power-off sequence: Set PB3 to "0". Set PB5 to "0". Turn V<sub>CC</sub> power off.

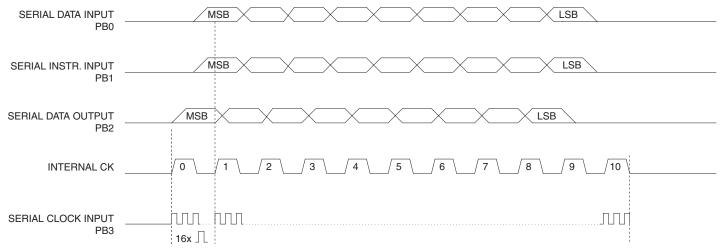

When writing or reading serial data to the ATtiny15L, data is clocked on the eight rising edge of the 16 external clock pulses needed to generate the internal clock. See Figure 31, Figure 32, and Table 26 for an explanation.

### **Data Polling**

When a byte is being programmed into the Flash or EEPROM, reading the address location being programmed will give the value \$FF. At the time the device is ready for a new byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the value \$FF so when programming this value, the user will have to wait for at least  $t_{WD_PROG_FL}$  before programming the next Flash byte, or  $t_{WD_PROG_EE}$  before the next EEPROM byte. As a chip-erased device contains \$FF in all locations, programming of addresses that are meant to contain \$FF can be skipped. This does not apply if the EEPROM is reprogrammed without chip-erasing the device. In that case, data polling cannot be used for the value \$FF and the user will have to wait at least  $t_{WD_PROG_EE}$  before programming the next byte. See Table 30 for  $t_{WD_PROG_FL}$  and  $t_{WD_PROG_EE}$  values.

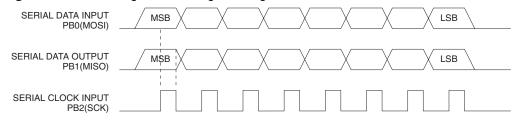

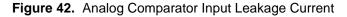

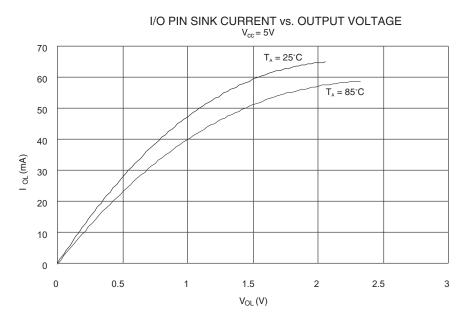

Figure 41. Analog Comparator Offset Voltage vs. Common Mode Voltage

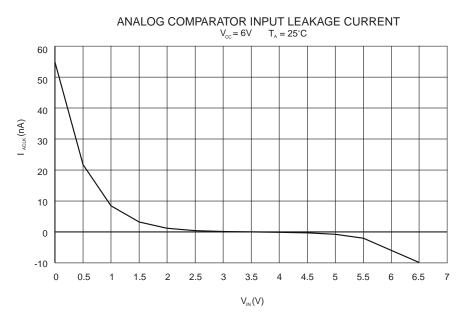

Figure 45. Pull-up Resistor Current vs. Input Voltage

## ATtiny15L Instruction Set Summary

| Mnemonic         | Operands      | Description                            | Operation                                                                | Flags                  | # Clocks |

|------------------|---------------|----------------------------------------|--------------------------------------------------------------------------|------------------------|----------|

| ARITHMETIC AND   | LOGIC INSTRUC | TIONS                                  |                                                                          | •                      |          |

| ADD              | Rd, Rr        | Add Two Registers                      | $Rd \leftarrow Rd + Rr$                                                  | Z,C,N,V,H              | 1        |

| ADC              | Rd, Rr        | Add with Carry Two Registers           | $Rd \leftarrow Rd + Rr + C$                                              | Z,C,N,V,H              | 1        |

| SUB              | Rd, Rr        | Subtract Two Registers                 | $Rd \leftarrow Rd - Rr$                                                  | Z,C,N,V,H              | 1        |

| SUBI             | Rd, K         | Subtract Constant from Register        | $Rd \leftarrow Rd - K$                                                   | Z,C,N,V,H              | 1        |

| SBC              | Rd, Rr        | Subtract with Carry Two Registers      | $Rd \leftarrow Rd - Rr - C$                                              | Z,C,N,V,H              | 1        |

| SBCI             | Rd, K         | Subtract with Carry Constant from Reg. | $Rd \leftarrow Rd - K - C$                                               | Z,C,N,V,H              | 1        |

| AND              | Rd, Rr        | Logical AND Registers                  | $Rd \leftarrow Rd \bullet Rr$                                            | Z,N,V                  | 1        |

| ANDI             | Rd, K         | Logical AND Register and Constant      | $Rd \leftarrow Rd \bullet K$                                             | Z,N,V                  | 1        |

| OR               | Rd, Rr        | Logical OR Registers                   | $Rd \leftarrow Rd \vee Rr$                                               | Z,N,V                  | 1        |

| ORI              | Rd, K         | Logical OR Register and Constant       | $Rd \leftarrow Rd \lor K$                                                | Z,N,V                  | 1        |

| EOR              | Rd, Rr        | Exclusive OR Registers                 | Rd ← Rd⊕Rr                                                               | Z,N,V                  | 1        |

| COM              | Rd            | One's Complement                       | $Rd \leftarrow FF - Rd$                                                  | Z,C,N,V                | 1        |

| NEG              | Rd            | Two's Complement                       | Rd ← \$00 - Rd                                                           | Z,C,N,V,H              | 1        |

| SBR              | Rd, K         | Set Bit(s) in Register                 | $Rd \leftarrow Rd \lor K$                                                | Z,N,V                  | 1        |

| CBR              | Rd, K         | Clear Bit(s) in Register               | $Rd \leftarrow Rd \bullet (FFh - K)$                                     | Z,N,V                  | 1        |

| INC              | Rd            | Increment                              | $Rd \leftarrow Rd + 1$                                                   | Z,N,V                  | 1        |

| DEC              | Rd            | Decrement                              | $Rd \leftarrow Rd - 1$                                                   | Z,N,V                  | 1        |

| TST              | Rd            | Test for Zero or Minus                 | $Rd \leftarrow Rd \bullet Rd$                                            | Z,N,V<br>Z,N,V         | 1        |

| CLR              | Rd            | Clear Register                         | $Rd \leftarrow Rd \oplus Rd$                                             | Z,N,V                  | 1        |

| SER              | Rd            | Set Register                           | Rd ← \$FF                                                                | None                   | 1        |

| BRANCH INSTRU    |               | Cor register                           | πα — φι τ                                                                | INOLIC                 | I I      |

| RJMP             | k             | Relative Jump                          | $PC \leftarrow PC + k + 1$                                               | None                   | 2        |

| RCALL            | k k           | Relative Subroutine Call               | $PC \leftarrow PC + k + 1$                                               | None                   | 3        |

| RET              | ĸ             | Subroutine Return                      | $PC \leftarrow STACK$                                                    | None                   | 4        |

| RETI             |               | Interrupt Return                       | PC ← STACK                                                               | INONE                  | 4        |

| CPSE             | Rd, Rr        | •                                      | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3                                 | None                   | 1/2      |

| CP3E             | Rd, Rr        | Compare, Skip if Equal                 | Rd - Rr                                                                  |                        | 1/2      |

| CPC              | Rd, Rr        | Compare                                | Rd - Rr - C                                                              | Z,N,V,C,H<br>Z,N,V,C,H | 1        |

| CPI              |               | Compare with Carry                     |                                                                          |                        | 1        |

|                  | Rd, K         | Compare Register with Immediate        | Rd - K                                                                   | Z,N,V,C,H              |          |

| SBRC             | Rr, b         | Skip if Bit in Register Cleared        | if $(Rr(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$                      | None                   | 1/2      |

| SBRS             | Rr, b         | Skip if Bit in Register is Set         | if $(\text{Rr}(b) = 1) \text{PC} \leftarrow \text{PC} + 2 \text{ or } 3$ | None                   | 1/2      |

| SBIC             | P, b          | Skip if Bit in I/O Register Cleared    | if $(P(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$                       | None                   | 1/2      |

| SBIS             | P, b          | Skip if Bit in I/O Register is Set     | if $(P(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$                       | None                   | 1/2      |

| BRBS             | s, k          | Branch if Status Flag Set              | if (SREG(s) = 1) then PC $\leftarrow$ PC + k + 1                         | None                   | 1/2      |

| BRBC             | s, k          | Branch if Status Flag Cleared          | if (SREG(s) = 0) then PC $\leftarrow$ PC + k + 1                         | None                   | 1/2      |

| BREQ             | k             | Branch if Equal                        | if (Z = 1) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRNE             | k             | Branch if Not Equal                    | if (Z = 0) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRCS             | k             | Branch if Carry Set                    | if (C = 1) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRCC             | k             | Branch if Carry Cleared                | if (C = 0) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRSH             | k             | Branch if Same or Higher               | if (C = 0) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRLO             | k             | Branch if Lower                        | if (C = 1) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRMI             | k             | Branch if Minus                        | if (N = 1) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRPL             | k             | Branch if Plus                         | if (N = 0) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRGE             | k             | Branch if Greater or Equal, Signed     | if (N $\oplus$ V= 0) then PC $\leftarrow$ PC + k + 1                     | None                   | 1/2      |

| BRLT             | k             | Branch if Less Than Zero, Signed       | if (N $\oplus$ V= 1) then PC $\leftarrow$ PC + k + 1                     | None                   | 1/2      |

| BRHS             | k             | Branch if Half-carry Flag Set          | if (H = 1) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRHC             | k             | Branch if Half-carry Flag Cleared      | if (H = 0) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRTS             | k             | Branch if T-flag Set                   | if (T = 1) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRTC             | k             | Branch if T-flag Cleared               | if (T = 0) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRVS             | k             | Branch if Overflow Flag is Set         | if (V = 1) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRVC             | k             | Branch if Overflow Flag is Cleared     | if (V = 0) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRIE             | k             | Branch if Interrupt Enabled            | if (I = 1) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| BRID             | k             | Branch if Interrupt Disabled           | if (I = 0) then PC $\leftarrow$ PC + k + 1                               | None                   | 1/2      |

| DATA TRANSFER    | INSTRUCTIONS  |                                        |                                                                          |                        |          |

| LD               | Rd, Z         | Load Register Indirect                 | $Rd \leftarrow (Z)$                                                      | None                   | 2        |

| ST               | Z, Rr         | Store Register Indirect                | $(Z) \leftarrow Rr$                                                      | None                   | 2        |

| MOV              | Rd, Rr        | Move between Registers                 | $Rd \leftarrow Rr$                                                       | None                   | 1        |

| LDI              | Rd, K         | Load Immediate                         | $Rd \leftarrow K$                                                        | None                   | 1        |

| IN               | Rd, P         | In Port                                | $Rd \leftarrow P$                                                        | None                   | 1        |

| OUT              | P, Rr         | Out Port                               | P ← Rr                                                                   | None                   | 1        |

| LPM              |               | Load Program Memory                    | R0 ← (Z)                                                                 | None                   | 3        |

|                  |               |                                        |                                                                          |                        | -        |

| BIT AND BIT-TEST | INSTRUCTIONS  |                                        |                                                                          |                        |          |

## ATtiny15L

## ATtiny15L Instruction Set Summary (Continued)

| Mnemonic | Operands | Description                     | Operation                                                          | Flags   | # Clocks |

|----------|----------|---------------------------------|--------------------------------------------------------------------|---------|----------|

| CBI      | P, b     | Clear Bit in I/O Register       | I/O(P,b) ← 0                                                       | None    | 2        |

| LSL      | Rd       | Logical Shift Left              | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                     | Z,C,N,V | 1        |

| LSR      | Rd       | Logical Shift Right             | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                     | Z,C,N,V | 1        |

| ROL      | Rd       | Rotate Left through Carry       | $Rd(0) \leftarrow C, Rd(n+1) \leftarrow Rd(n), C \leftarrow Rd(7)$ | Z,C,N,V | 1        |

| ROR      | Rd       | Rotate Right through Carry      | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0)$ | Z,C,N,V | 1        |

| ASR      | Rd       | Arithmetic Shift Right          | Rd(n) ← Rd(n+1), n = 06                                            | Z,C,N,V | 1        |

| SWAP     | Rd       | Swap Nibbles                    | $Rd(30) \leftarrow Rd(74), Rd(74) \leftarrow Rd(30)$               | None    | 1        |

| BSET     | s        | Flag Set                        | SREG(s) ← 1                                                        | SREG(s) | 1        |

| BCLR     | s        | Flag Clear                      | $SREG(s) \leftarrow 0$                                             | SREG(s) | 1        |

| BST      | Rr, b    | Bit Store from Register to T    | $T \leftarrow Rr(b)$                                               | Т       | 1        |

| BLD      | Rd, b    | Bit Load from T to Register     | $Rd(b) \leftarrow T$                                               | None    | 1        |

| SEC      |          | Set Carry                       | C ← 1                                                              | С       | 1        |

| CLC      |          | Clear Carry                     | C ← 0                                                              | С       | 1        |

| SEN      |          | Set Negative Flag               | N ← 1                                                              | N       | 1        |

| CLN      |          | Clear Negative Flag             | N ← 0                                                              | N       | 1        |

| SEZ      |          | Set Zero Flag                   | Z ← 1                                                              | Z       | 1        |

| CLZ      |          | Clear Zero Flag                 | Z ← 0                                                              | Z       | 1        |

| SEI      |          | Global Interrupt Enable         | l ← 1                                                              | 1       | 1        |

| CLI      |          | Global Interrupt Disable        | l ← 0                                                              | 1       | 1        |

| SES      |          | Set Signed Test Flag            | S ← 1                                                              | S       | 1        |

| CLS      |          | Clear Signed Test Flag          | S ← 0                                                              | S       | 1        |

| SEV      |          | Set Two's Complement Overflow   | V ← 1                                                              | V       | 1        |

| CLV      |          | Clear Two's Complement Overflow | $V \leftarrow 0$                                                   | V       | 1        |

| SET      |          | Set T in SREG                   | T ← 1                                                              | Т       | 1        |

| CLT      |          | Clear T in SREG                 | T ← 0                                                              | Т       | 1        |

| SEH      |          | Set Half-carry Flag in SREG     | H ← 1                                                              | Н       | 1        |

| CLH      |          | Clear Half-carry Flag in SREG   | H ← 0                                                              | Н       | 1        |

| NOP      |          | No Operation                    |                                                                    | None    | 1        |

| SLEEP    |          | Sleep                           | (see specific descr. for Sleep function)                           | None    | 1        |

| WDR      |          | Watchdog Reset                  | (see specific descr. for WDR/timer)                                | None    | 1        |

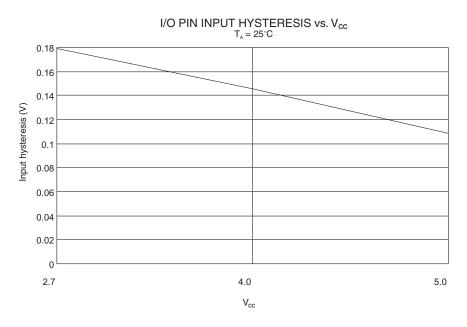

## **Packaging Information**

8P3

80

ATtiny15L

| I/O Port B                                      | 51   |

|-------------------------------------------------|------|

| Memory Programming                              | 54   |

| Program and Data Memory Lock Bits               | . 54 |

| Fuse Bits                                       | . 54 |

| Signature Bytes                                 | . 54 |

| Calibration Byte                                | . 55 |

| Programming the Flash                           | . 55 |

| High-voltage Serial Programming                 | . 55 |

| High-voltage Serial Programming Algorithm       | . 56 |

| High-voltage Serial Programming Characteristics | . 59 |

| Low-voltage Serial Downloading                  | . 59 |

| Low-voltage Serial Programming Characteristics  | . 63 |

| Electrical Characteristics                      | 64   |

| Absolute Maximum Ratings                        | . 64 |

| DC Characteristics                              |      |

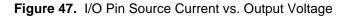

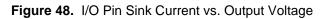

| Typical Characteristics                         | 66   |

| ATtiny15L Register Summary                      | 75   |

| ATtiny15L Instruction Set Summary               | 76   |

| Ordering Information                            | 78   |

| Packaging Information                           | 79   |

| 8P3                                             |      |

| 8S2                                             | . 80 |

| Datasheet revision history                      | 81   |

| Rev H - 09/07                                   |      |

| Rev G - 06/07                                   |      |

| Rev F - 06/05                                   |      |

| Table of Contents                               | i    |

ii