Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

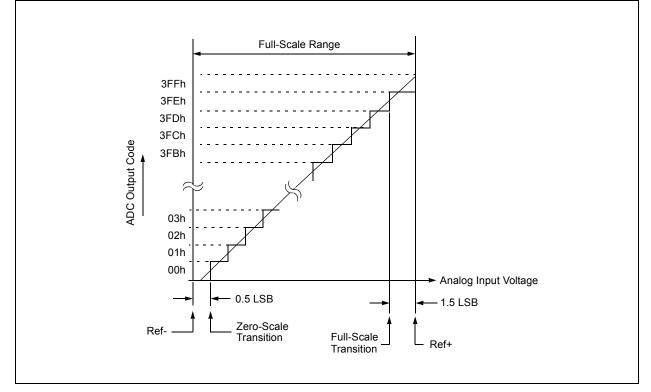

| Data Converters            | A/D 12x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1508-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

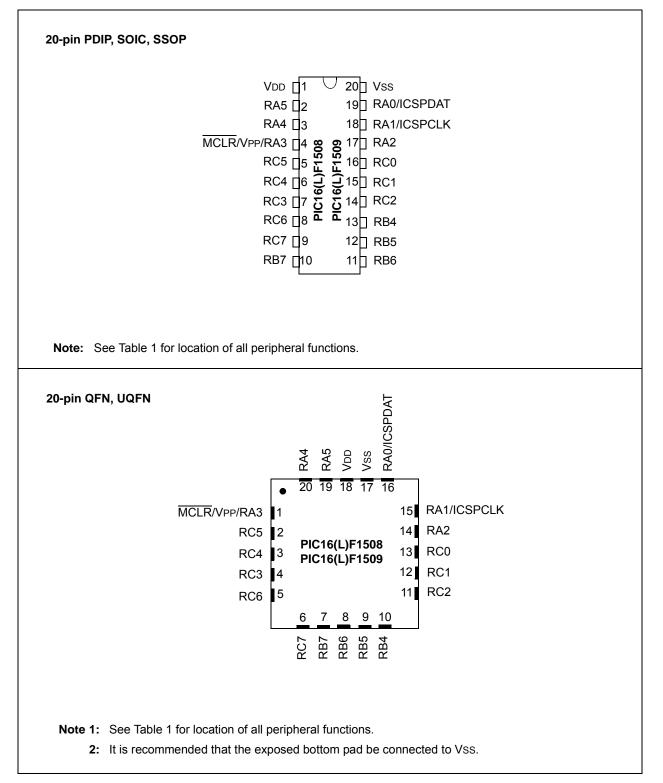

## **PIN DIAGRAMS**

#### **TABLE 3-9:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| INDEE     |                 |               |                                                    |                                 |               |            |        | 020/    |        |                      |                                 |

|-----------|-----------------|---------------|----------------------------------------------------|---------------------------------|---------------|------------|--------|---------|--------|----------------------|---------------------------------|

| Address   | Name            | Bit 7         | Bit 6                                              | Bit 5                           | Bit 4         | Bit 3      | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 3    | 1               |               |                                                    |                                 |               |            |        |         |        |                      |                                 |

| F8Ch      | —               | Unimplemen    | ted                                                |                                 |               |            |        |         |        | —                    | —                               |

| —<br>FE3h |                 |               |                                                    |                                 |               |            |        |         |        |                      |                                 |

| FE4h      | STATUS_<br>SHAD | —             | —                                                  | -                               | _             | —          | Z_SHAD | DC_SHAD | C_SHAD | xxx                  | uuu                             |

| FE5h      | WREG_<br>SHAD   | Working Reg   | jister Shadow                                      |                                 |               |            |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FE6h      | BSR_<br>SHAD    | —             | —                                                  | — — Bank Select Register Shadow |               |            |        |         |        | x xxxx               | u uuuu                          |

| FE7h      | PCLATH_<br>SHAD | _             | Program Counter Latch High Register Shadow         |                                 |               |            |        |         |        | -xxx xxxx            | uuuu uuuu                       |

| FE8h      | FSR0L_<br>SHAD  | Indirect Data | Memory Add                                         | Iress 0 Low F                   | Pointer Shado | W          |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FE9h      | FSR0H_<br>SHAD  | Indirect Data | Memory Add                                         | lress 0 High I                  | Pointer Shade | ow         |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FEAh      | FSR1L_<br>SHAD  | Indirect Data | Indirect Data Memory Address 1 Low Pointer Shadow  |                                 |               |            |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FEBh      | FSR1H_<br>SHAD  | Indirect Data | Indirect Data Memory Address 1 High Pointer Shadow |                                 |               |            |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FECh      | —               | Unimplemen    | ted                                                |                                 |               |            |        |         |        | _                    | —                               |

| FEDh      | STKPTR          | _             | —                                                  | _                               | Current Star  | ck Pointer |        |         |        | 1 1111               | 1 1111                          |

| FEEh      | TOSL            | Top-of-Stack  | Low byte                                           |                                 |               |            |        |         |        | XXXX XXXX            | uuuu uuuu                       |

| FEFh      | TOSH            | —             | Top-of-Stack                                       | High byte                       |               |            |        |         |        | -xxx xxxx            | -uuu uuuu                       |

Legend:

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16F1508/9 only.

2:

Unimplemented, read as '1'.

## 5.3.5 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PPLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

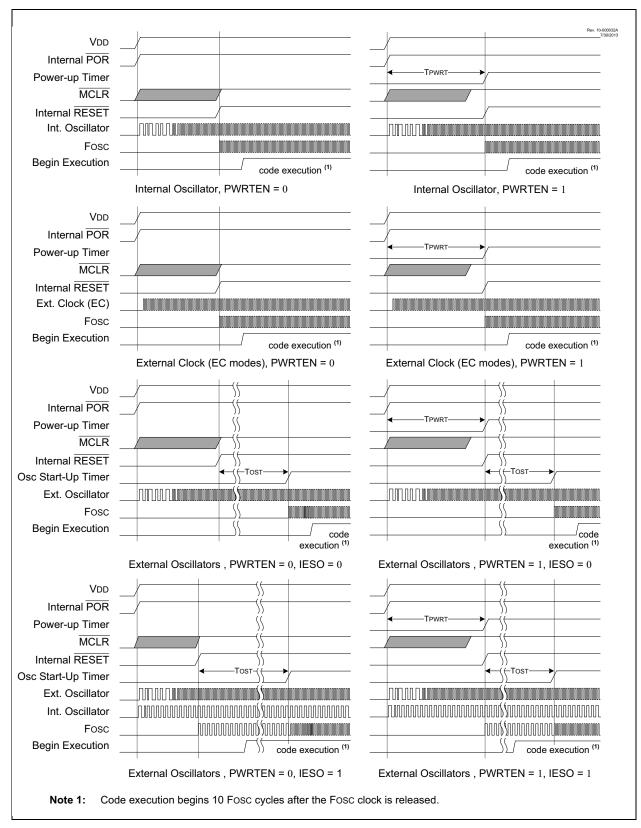

## 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT, or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

**Note:** Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCSTAT register to remain clear.

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1    | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|-------|------------|-------|----------|--------|---------------------|

| OSCCON | —      |        | IRCF  | <3:0> |            | _     | SCS<1:0> |        | 59                  |

| PCON   | STKOVF | STKUNF | —     | RWDT  | RMCLR      | RI    | POR      | BOR    | 68                  |

| STATUS | —      | —      | _     | TO    | PD         | Z     | DC       | С      | 19                  |

| WDTCON | —      | _      |       |       | WDTPS<4:0> | >     |          | SWDTEN | 88                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

### TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|-----------|---------|---------------------|

|         | 13:8 |         | —       | FCMEN    | IESO     | CLKOUTEN | BORE     | N<1:0>    | —       | 44                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | E<1:0>   |          | FOSC<2:0> |         | 41                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

## 17.8 Register Definitions: Comparator Control

| R/W-0/0         | R-0/0                  | R/W-0/0                                 | R/W-0/0          | U-0              | R/W-1/1          | R/W-0/0         | R/W-0/0         |

|-----------------|------------------------|-----------------------------------------|------------------|------------------|------------------|-----------------|-----------------|

| CxON            | CxOUT                  | CxOE                                    | CxPOL            | _                | CxSP             | CxHYS           | CxSYNC          |

| bit 7           | •                      |                                         | •                |                  |                  | •               | bit 0           |

|                 |                        |                                         |                  |                  |                  |                 |                 |

| Legend:         | . 1.11                 |                                         | 1.11             |                  |                  | 1               |                 |

| R = Readabl     |                        | W = Writable                            |                  | •                | mented bit, read |                 | othor Doooto    |

| u = Bit is unc  | 0                      | x = Bit is unki                         |                  | -n/n = value     | at POR and BC    | rk/value at all | other Resets    |

| '1' = Bit is se | t                      | '0' = Bit is cle                        | areo             |                  |                  |                 |                 |

| bit 7           | CxON: Com              | parator Enable                          | bit              |                  |                  |                 |                 |

|                 |                        | ator is enabled                         |                  |                  |                  |                 |                 |

|                 | 0 = Compara            | ator is disabled                        | and consumes     | s no active pow  | ver              |                 |                 |

| bit 6           | CxOUT: Con             | nparator Output                         | bit              |                  |                  |                 |                 |

|                 |                        | (inverted polar                         | <u>ity):</u>     |                  |                  |                 |                 |

|                 | 1 = CxVP <             |                                         |                  |                  |                  |                 |                 |

|                 | 0 = CxVP >             | (non-inverted)                          | oolarity):       |                  |                  |                 |                 |

|                 | 1 = CxVP >             |                                         | <u>Jolanty).</u> |                  |                  |                 |                 |

|                 | 0 = CxVP <             | CxVN                                    |                  |                  |                  |                 |                 |

| bit 5           | CxOE: Com              | parator Output                          | Enable bit       |                  |                  |                 |                 |

|                 |                        | is present on th                        |                  | Requires that th | he associated T  | RIS bit be clea | red to actually |

|                 |                        | pin. Not affect                         | ed by CxON.      |                  |                  |                 |                 |

|                 |                        | is internal only                        |                  |                  |                  |                 |                 |

| bit 4           |                        | nparator Outpu                          | -                | ct bit           |                  |                 |                 |

|                 |                        | ator output is inv<br>ator output is no |                  |                  |                  |                 |                 |

| bit 3           | •                      |                                         |                  |                  |                  |                 |                 |

|                 | •                      | nted: Read as '                         |                  | :4               |                  |                 |                 |

| bit 2           | -                      | parator Speed/F                         |                  |                  |                  |                 |                 |

|                 | •                      | ator mode in no<br>ator mode in lov     |                  | •                |                  |                 |                 |

| bit 1           | -                      | nparator Hyster                         | -                | -                |                  |                 |                 |

|                 |                        | ator hysteresis                         |                  |                  |                  |                 |                 |

|                 | 0 = Compar             | ator hysteresis                         | disabled         |                  |                  |                 |                 |

| bit 0           | CxSYNC: Co             | omparator Outp                          | ut Synchronou    | us Mode bit      |                  |                 |                 |

|                 |                        | ator output to 1                        |                  |                  |                  | ges on Timer1   | clock source    |

|                 | Output ι<br>0 = Compar | updated on the                          | •••              |                  |                  |                 |                 |

|                 |                        |                                         |                  |                  |                  |                 |                 |

### REGISTER 17-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0                                                                                           | R/W-0/0                                                                                                                                                                                                                                                                                                                                                    | R/W-0/0                                                            | U-0              | R/W-0/0          | R/W-0/0    | R/W-0/0      |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------|------------------|------------|--------------|--|--|--|

| CxINTP           | CxINTN                                                                                            | CxPC                                                                                                                                                                                                                                                                                                                                                       | H<1:0>                                                             |                  |                  | CxNCH<2:0> |              |  |  |  |

| bit 7            |                                                                                                   |                                                                                                                                                                                                                                                                                                                                                            |                                                                    |                  |                  |            | bit 0        |  |  |  |

| Legend:          |                                                                                                   |                                                                                                                                                                                                                                                                                                                                                            |                                                                    |                  |                  |            |              |  |  |  |

| R = Readable     | bit                                                                                               | W = Writable                                                                                                                                                                                                                                                                                                                                               | bit                                                                | U = Unimpler     | mented bit, read | d as '0'   |              |  |  |  |

| u = Bit is unch  | nanged                                                                                            | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                            | nown                                                               |                  | at POR and BC    |            | other Resets |  |  |  |

| '1' = Bit is set | •                                                                                                 | '0' = Bit is cle                                                                                                                                                                                                                                                                                                                                           |                                                                    |                  |                  |            |              |  |  |  |

|                  |                                                                                                   |                                                                                                                                                                                                                                                                                                                                                            |                                                                    |                  |                  |            |              |  |  |  |

| bit 7            | 1 = The CxIF                                                                                      | nparator Interru<br>- interrupt flag<br>upt flag will be                                                                                                                                                                                                                                                                                                   | will be set upo                                                    | n a positive goi | ing edge of the  |            |              |  |  |  |

| bit 6            | CxINTN: Cor<br>1 = The CxIF                                                                       | <ul> <li>0 = No interrupt flag will be set on a positive going edge of the CxOUT bit</li> <li>CxINTN: Comparator Interrupt on Negative Going Edge Enable bits</li> <li>1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit</li> <li>0 = No interrupt flag will be set on a negative going edge of the CxOUT bit</li> </ul> |                                                                    |                  |                  |            |              |  |  |  |

| bit 5-4          | CxPCH<1:0><br>11 = CxVP c<br>10 = CxVP c<br>01 = CxVP c                                           | Comparator I<br>connects to Vss<br>onnects to FVF<br>onnects to DAC<br>onnects to CXII                                                                                                                                                                                                                                                                     | Positive Input<br>R Voltage Refe<br>C Voltage Refe                 | Channel Select   |                  |            |              |  |  |  |

| bit 3            | Unimplemer                                                                                        | ted: Read as '                                                                                                                                                                                                                                                                                                                                             | 0'                                                                 |                  |                  |            |              |  |  |  |

| bit 2-0          | 111 = Reser<br>110 = Reser<br>101 = Reser<br>100 = CxVN<br>011 = CxVN<br>010 = CxVN<br>001 = CxVN | ved                                                                                                                                                                                                                                                                                                                                                        | /R Voltage ref<br>kIN3- pin<br>kIN2- pin<br>kIN2- pin<br>kIN1- pin |                  | ct bits          |            |              |  |  |  |

## REGISTER 17-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

## REGISTER 17-3: CMOUT: COMPARATOR OUTPUT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| _     | —   | _   | —   | _   | _   | MC2OUT | MC1OUT |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

- bit 7-2 Unimplemented: Read as '0'

- bit 1 MC2OUT: Mirror Copy of C2OUT bit

- bit 0 MC10UT: Mirror Copy of C10UT bit

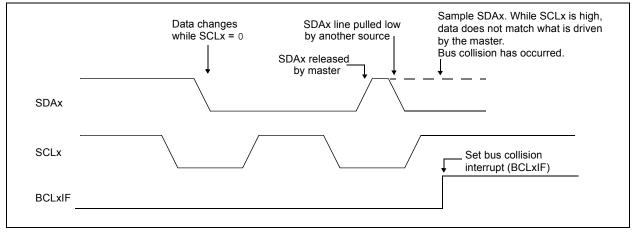

#### FIGURE 21-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

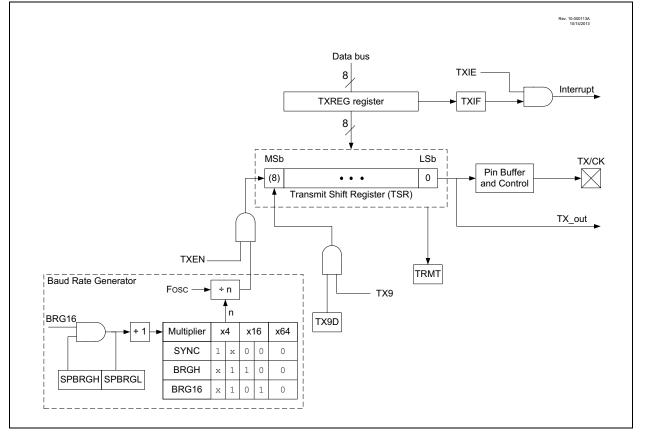

## 22.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous Full-Duplex is useful system. mode for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- · Two-character input buffer

- · One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- Input buffer overrun error detection

- · Received character framing error detection

- · Half-duplex synchronous master

- Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- · 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 22-1 and Figure 22-2.

The EUSART transmit output (TX\_out) is available to the TX/CK pin and internally to the following peripherals:

• Configurable Logic Cell (CLC)

#### FIGURE 22-1: EUSART TRANSMIT BLOCK DIAGRAM

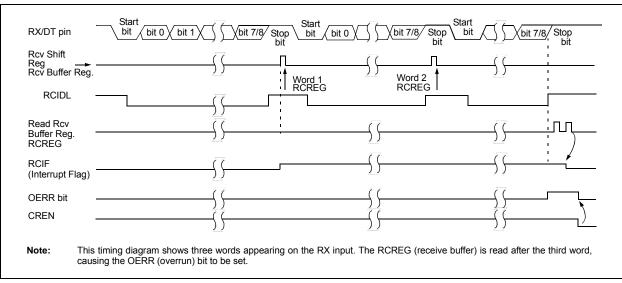

- 22.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section22.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

22.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section22.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

## FIGURE 22-5: ASYNCHRONOUS RECEPTION

### 22.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate.

The Auto-Baud Detect feature (see **Section22.4.1 "Auto-Baud Detect**") can be used to compensate for changes in the INTOSC frequency.

There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

#### 22.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 22-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 22-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 22-6. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte <u>following</u> the Break character (see <u>Section22.4.3 "Auto-Wake-up</u> on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

#### TABLE 22-6: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

### FIGURE 22-6: AUTOMATIC BAUD RATE CALIBRATION

| BRG Value<br>RX pin     |               | <u>0000h</u> | tart bit       | Edge #1 _ Edge #2 _ Edge #3 _ Edge #4 _ Edge # |            |

|-------------------------|---------------|--------------|----------------|------------------------------------------------|------------|

| BRG Clock               |               | mmm          | หนุ่มน         |                                                |            |

| ABDEN bit               | Set by User — |              | <br> <br> <br> | Aut                                            | to Cleared |

| RCIDL                   |               |              | i<br>I         |                                                |            |

| RCIF bit<br>(Interrupt) |               |              | 1<br>1<br>1    |                                                |            |

| Read<br>RCREG           |               | I<br>I       | -<br>          |                                                |            |

| SPBRGL                  |               |              | X              | xh                                             | 1Ch        |

| SPBRGH                  |               | ·            | X              | Xh /                                           | 00h        |

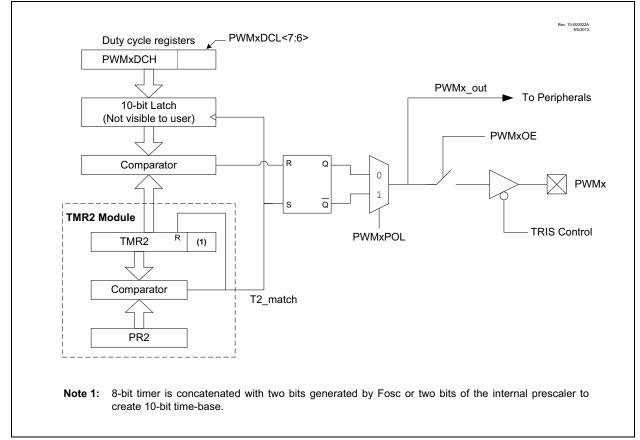

## 23.0 PULSE-WIDTH MODULATION (PWM) MODULE

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PR2

- T2CON

- PWMxDCH

- PWMxDCL

- PWMxCON

## FIGURE 23-1: SIMPLIFIED PWM BLOCK DIAGRAM

For a step-by-step procedure on how to set up this module for PWM operation, refer to Section 23.1.9 "Setup for PWM Operation using PWMx Pins".

| R/W-0/0          | R/W-0/0                                     | U-0                                | U-0             | R/W-0/0                      | R/W-0/0          | R/W-0/0   | R/W-0/0    |  |  |

|------------------|---------------------------------------------|------------------------------------|-----------------|------------------------------|------------------|-----------|------------|--|--|

| GxASE            | GxARSEN                                     | —                                  | —               | GxASDSC2                     | GxASDSC1         | GxASDSFLT | GxASDSCLC2 |  |  |

| bit 7            |                                             |                                    |                 |                              |                  |           | bit 0      |  |  |

| Legend:          |                                             |                                    |                 |                              |                  |           |            |  |  |

| R = Readable I   | hit                                         | W = Writable                       | hit             | II = I Inimplen              | nented bit, read | las '0'   |            |  |  |

| u = Bit is uncha |                                             | at POR and BO                      |                 | ther Resets                  |                  |           |            |  |  |

| '1' = Bit is set | angeu                                       | x = Bit is unk<br>'0' = Bit is cle |                 |                              | ends on condit   |           |            |  |  |

|                  |                                             |                                    |                 |                              |                  | · · · ·   |            |  |  |

| bit 7            | GxASE: Auto                                 | -Shutdown Ev                       | ent Status bit  |                              |                  |           |            |  |  |

|                  | 1 = An auto-s                               |                                    |                 |                              |                  |           |            |  |  |

|                  | 0 = No auto-shutdown event has occurred     |                                    |                 |                              |                  |           |            |  |  |

| bit 6            | GxARSEN: A                                  |                                    |                 |                              |                  |           |            |  |  |

|                  | 1 = Auto-rest<br>0 = Auto-rest              |                                    |                 |                              |                  |           |            |  |  |

| bit 5-4          | Unimplemen                                  | ted: Read as                       | <b>'</b> 0'     |                              |                  |           |            |  |  |

| bit 3            | GxASDSC2:                                   | CWG Auto-sh                        | utdown on Co    | omparator C2 E               | Enable bit       |           |            |  |  |

|                  |                                             |                                    |                 | out (C2OUT_a                 | sync) is high    |           |            |  |  |

|                  | 0 = Compara                                 | •                                  |                 |                              |                  |           |            |  |  |

| bit 2            |                                             |                                    |                 | omparator C1 E               |                  |           |            |  |  |

|                  | 1 = Snutdown0 = Compara                     | •                                  |                 | out (C1OUT_a:<br>on shutdown | sync) is nign    |           |            |  |  |

| bit 1            | GxASDSFLT:                                  | •                                  |                 |                              |                  |           |            |  |  |

|                  | 1 = Shutdow                                 | n when CWG                         | IFLT input is I | ow                           |                  |           |            |  |  |

|                  | 0 = CWG1FLT input has no effect on shutdown |                                    |                 |                              |                  |           |            |  |  |

|                  | 0 = CWG1FL                                  | .i input nas no                    | J enection sh   | luown                        |                  |           |            |  |  |

| bit 0            |                                             | 2: CWG Auto                        | -shutdown on    | CLC2 Enable                  | bit              |           |            |  |  |

### REGISTER 26-3: CWGxCON2: CWG CONTROL REGISTER 2

| PIC16LF1508/9 |                        | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode |       |               |                |       |            |                                                                                                         |

|---------------|------------------------|-------------------------------------------------------------------------|-------|---------------|----------------|-------|------------|---------------------------------------------------------------------------------------------------------|

| PIC16F15      | 08/9                   | Low-Power Sleep Mode, VREGPM = 1                                        |       |               |                |       |            |                                                                                                         |

| Param.<br>No. | Device Characteristics | Min.                                                                    | Тур†  | Max.<br>+85°C | Max.<br>+125°C | Units | Conditions |                                                                                                         |

|               |                        |                                                                         |       |               |                |       | Vdd        | Note                                                                                                    |

| D022          | Base IPD               | _                                                                       | 0.020 | 1.0           | 8.0            | μA    | 1.8        | WDT, BOR, FVR and SOSC disabled, all Peripherals inactive                                               |

|               |                        | —                                                                       | 0.025 | 2.0           | 9.0            | μA    | 3.0        |                                                                                                         |

| D022          | Base IPD               | —                                                                       | 0.25  | 3.0           | 10             | μA    | 2.3        | WDT, BOR, FVR and SOSC<br>disabled, all Peripherals inactive,<br>Low-Power Sleep mode                   |

|               |                        | —                                                                       | 0.30  | 4.0           | 12             | μA    | 3.0        |                                                                                                         |

|               |                        | —                                                                       | 0.40  | 6.0           | 15             | μA    | 5.0        |                                                                                                         |

| D022A         | Base IPD               | —                                                                       | 9.8   | 16            | 18             | μA    | 2.3        | WDT, BOR, FVR and SOSC<br>disabled, all Peripherals inactive,<br>Normal Power Sleep mode,<br>VREGPM = 0 |

|               |                        | —                                                                       | 10.3  | 18            | 20             | μA    | 3.0        |                                                                                                         |

|               |                        | _                                                                       | 11.5  | 21            | 26             | μA    | 5.0        |                                                                                                         |

| D023          |                        | _                                                                       | 0.26  | 2.0           | 9.0            | μA    | 1.8        | WDT Current                                                                                             |

|               |                        | —                                                                       | 0.44  | 3.0           | 10             | μA    | 3.0        |                                                                                                         |

| D023          |                        | _                                                                       | 0.43  | 6.0           | 15             | μA    | 2.3        | WDT Current                                                                                             |

|               |                        |                                                                         | 0.53  | 7.0           | 20             | μA    | 3.0        |                                                                                                         |

|               |                        | —                                                                       | 0.64  | 8.0           | 22             | μA    | 5.0        |                                                                                                         |

| D023A         |                        | _                                                                       | 15    | 28            | 30             | μA    | 1.8        | FVR Current                                                                                             |

|               |                        | —                                                                       | 18    | 30            | 33             | μA    | 3.0        |                                                                                                         |

| D023A         |                        | —                                                                       | 18    | 33            | 35             | μA    | 2.3        | FVR Current                                                                                             |

|               |                        |                                                                         | 19    | 35            | 37             | μA    | 3.0        |                                                                                                         |

|               |                        |                                                                         | 20    | 37            | 39             | μA    | 5.0        |                                                                                                         |

| D024          |                        | —                                                                       | 6.0   | 17            | 20             | μA    | 3.0        | BOR Current                                                                                             |

| D024          |                        |                                                                         | 7.0   | 17            | 30             | μA    | 3.0        | BOR Current                                                                                             |

|               |                        |                                                                         | 8.0   | 20            | 40             | μA    | 5.0        |                                                                                                         |

| D24A          |                        | _                                                                       | 0.1   | 4.0           | 10             | μA    | 3.0        | LPBOR Current                                                                                           |

| D24A          |                        |                                                                         | 0.35  | 5.0           | 14             | μA    | 3.0        | LPBOR Current                                                                                           |

|               |                        | —                                                                       | 0.45  | 8.0           | 17             | μA    | 5.0        |                                                                                                         |

TABLE 29-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2)</sup>

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral ∆ current can be determined by subtracting the base IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

**3:** ADC clock source is FRC.

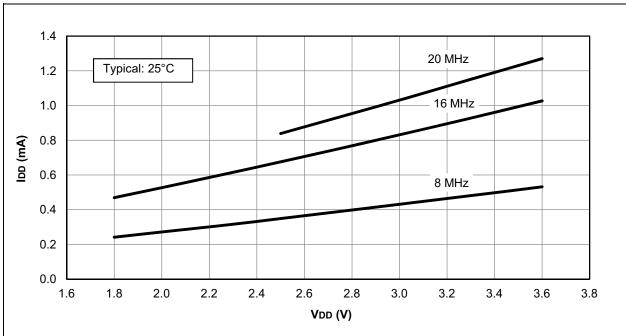

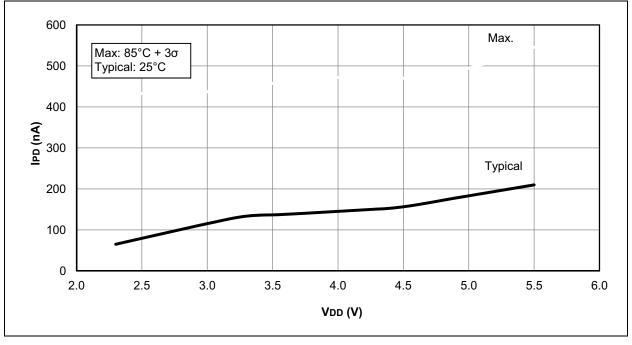

FIGURE 30-15: IDD TYPICAL, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16LF1508/9 ONLY

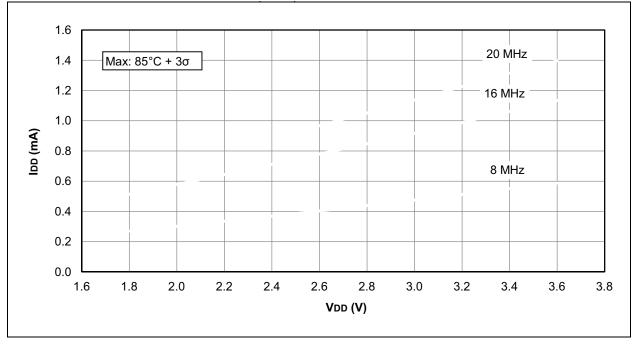

FIGURE 30-16: IDD MAXIMUM, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16LF1508/9 ONLY

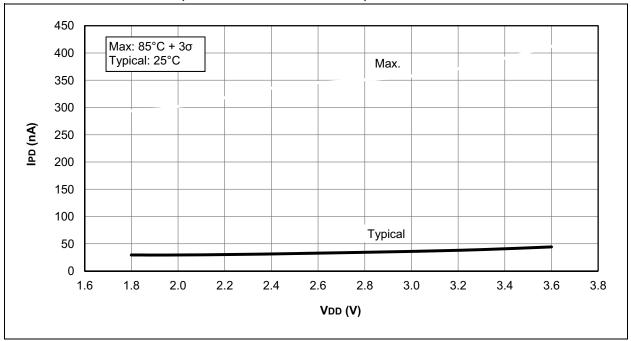

FIGURE 30-31: IPD BASE, LOW-POWER SLEEP MODE, PIC16LF1508/9 ONLY

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820