Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

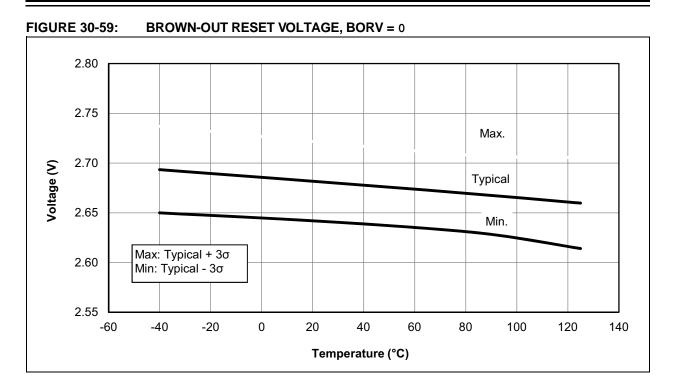

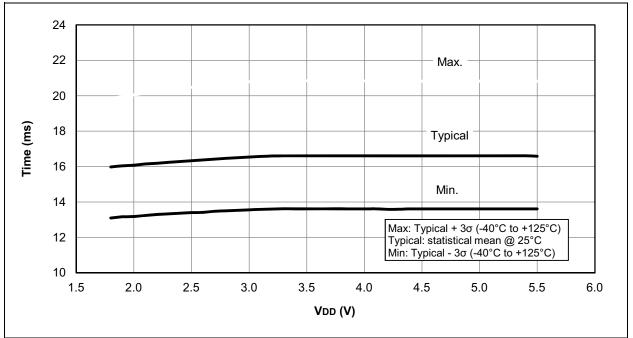

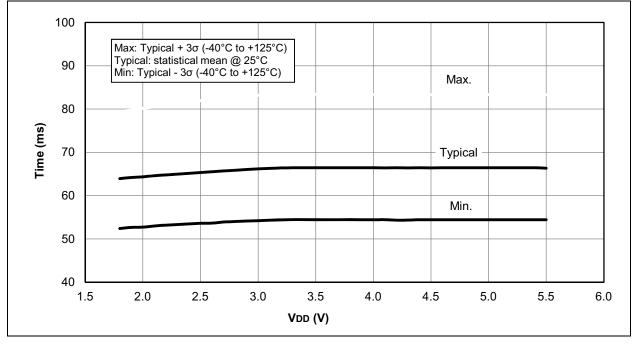

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1508-i-gz |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-2: PIC16(L)F1508/9 PINOUT DESCRIPTION

| Name                                                    | Function | Input<br>Type | Output<br>Type | Description                                           |  |  |

|---------------------------------------------------------|----------|---------------|----------------|-------------------------------------------------------|--|--|

| RA0/AN0/C1IN+/DAC1OUT1/                                 | RA0      | TTL           | CMOS           | General purpose I/O.                                  |  |  |

| CSPDAT/ICDDAT                                           | AN0      | AN            | _              | ADC Channel input.                                    |  |  |

|                                                         | C1IN+    | AN            | _              | Comparator positive input.                            |  |  |

|                                                         | DAC1OUT1 | _             | AN             | Digital-to-Analog Converter output.                   |  |  |

|                                                         | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                                       |  |  |

|                                                         | ICDDAT   | ST            | CMOS           | In-Circuit Debug data.                                |  |  |

| RA1/AN1/CLC4IN1/VREF+/                                  | RA1      | TTL           | CMOS           | General purpose I/O.                                  |  |  |

| C1IN0-/C2IN0-/ICSPCLK/                                  | AN1      | AN            |                | ADC Channel input.                                    |  |  |

| CDCLK                                                   | CLC4IN1  | ST            | _              | Configurable Logic Cell source input.                 |  |  |

|                                                         | VREF+    | AN            | _              | ADC Positive Voltage Reference input.                 |  |  |

|                                                         | C1IN0-   | AN            |                | Comparator negative input.                            |  |  |

|                                                         | C2IN0-   | AN            |                | Comparator negative input.                            |  |  |

|                                                         | ICSPCLK  | ST            | —              | ICSP Programming Clock.                               |  |  |

|                                                         | ICDCLK   | ST            | _              | In-Circuit Debug Clock.                               |  |  |

| RA2/AN2/C1OUT/DAC1OUT2/                                 | RA2      | ST            | CMOS           | General purpose I/O.                                  |  |  |

| TOCKI/INT/PWM3/CLC1/                                    | AN2      | AN            | _              | ADC Channel input.                                    |  |  |

| CWG1FLT                                                 | C1OUT    | _             | CMOS           | Comparator output.                                    |  |  |

|                                                         | DAC1OUT2 | _             | AN             | Digital-to-Analog Converter output.                   |  |  |

|                                                         | TOCKI    | ST            |                | Timer0 clock input.                                   |  |  |

|                                                         | INT      | ST            |                | External interrupt.                                   |  |  |

|                                                         | PWM3     | _             | CMOS           | PWM output.                                           |  |  |

|                                                         | CLC1     | _             | CMOS           | Configurable Logic Cell source output.                |  |  |

|                                                         | CWG1FLT  | ST            |                | Complementary Waveform Generator Fault input.         |  |  |

| RA3/CLC1IN0/VPP/T1G <sup>(1)</sup> /SS <sup>(1)</sup> / | RA3      | TTL           |                | General purpose input with IOC and WPU.               |  |  |

| MCLR                                                    | CLC1IN0  | ST            |                | Configurable Logic Cell source input.                 |  |  |

|                                                         | VPP      | HV            |                | Programming voltage.                                  |  |  |

|                                                         | T1G      | ST            |                | Timer1 Gate input.                                    |  |  |

|                                                         | SS       | ST            |                | Slave Select input.                                   |  |  |

|                                                         | MCLR     | ST            |                | Master Clear with internal pull-up.                   |  |  |

| RA4/AN3/SOSCO/                                          | RA4      | TTL           | CMOS           | General purpose I/O.                                  |  |  |

| CLKOUT/T1G                                              | AN3      | AN            |                | ADC Channel input.                                    |  |  |

|                                                         | SOSCO    | XTAL          | XTAL           | Secondary Oscillator Connection.                      |  |  |

|                                                         | CLKOUT   | _             | CMOS           | Fosc/4 output.                                        |  |  |

|                                                         | T1G      | ST            | _              | Timer1 Gate input.                                    |  |  |

| RA5/CLKIN/T1CKI/NCO1CLK/                                | RA5      | TTL           | CMOS           | General purpose I/O.                                  |  |  |

| SOSCI                                                   | CLKIN    | CMOS          | _              | External clock input (EC mode).                       |  |  |

|                                                         | T1CKI    | ST            | _              | Timer1 clock input.                                   |  |  |

|                                                         | NCO1CLK  | ST            |                | Numerically Controlled Oscillator Clock source input. |  |  |

|                                                         | SOSCI    | XTAL          | XTAL           | Secondary Oscillator Connection.                      |  |  |

HV = High Voltage XTAL = Crystal

Schmitt Trigger input with levels

**Note 1:** Alternate pin function selected with the APFCON (Register 11-1) register.

#### 5.2.2.4 Peripheral Clock Sources

The clock sources described in this chapter and the Timer's are available to different peripherals. Table 5-1 lists the clocks and timers available for each peripheral.

| TABLE 5- |      | PERIPHERAL CLOCK<br>SOURCES |          |          |      |      |      |      |  |

|----------|------|-----------------------------|----------|----------|------|------|------|------|--|

|          | FOSC | FRC                         | HFINTOSC | LFINTOSC | TMR0 | TMR1 | TMR2 | SOSC |  |

| ADC      | •    | •                           |          |          |      |      |      |      |  |

| CLC      | •    | •                           | •        | •        | •    | •    | •    | •    |  |

| COMP     |      |                             |          |          |      | ٠    |      | ٠    |  |

| CWG      | •    |                             | •        |          |      |      |      |      |  |

| EUSART   | •    |                             |          |          |      |      | •    |      |  |

| MSSP     | ٠    |                             |          |          |      |      | ٠    |      |  |

| NCO      | •    |                             | ٠        |          |      |      |      |      |  |

| PWM      | •    |                             |          |          |      |      | •    |      |  |

| PWRT     |      |                             |          | •        |      |      |      |      |  |

| TMR0     | •    |                             |          |          |      |      |      |      |  |

| TMR1     | ٠    |                             |          | ٠        |      |      |      | ٠    |  |

| TMR2     | •    |                             |          |          |      |      |      |      |  |

| WDT      |      |                             |          | ٠        |      |      |      |      |  |

#### 5.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The postscaled output of the 16 MHz HFINTOSC and 31 kHz LFINTOSC connect to a multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register (Register 5-1) select the frequency output of the internal oscillators.

| Note: | Following any Reset, the IRCF<3:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '0111' |

|       | and the frequency selection is set to    |

|       | 500 kHz. The user can modify the IRCF    |

|       | bits to select a different frequency.    |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

#### Internal Oscillator Clock Switch 5.2.2.6 Timina

When switching between the HFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- IRCF<3:0> bits of the OSCCON register are 1. modified.

- If the new clock is shut down, a clock start-up 2. delay is started.

- Clock switch circuitry waits for a falling edge of 3. the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- The OSCSTAT register is updated as required. 6.

- Clock switch is complete. 7.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-3.

Start-up delay specifications are located in Table 29-8, "Oscillator Parameters".

| R-1/q            | U-0                                                                | R-q/q                                                                                                                                         | R-0/q                                                              | U-0               | U-0                | R-0/q      | R-0/q         |  |  |  |  |

|------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------|--------------------|------------|---------------|--|--|--|--|

| SOSCR            |                                                                    | OSTS                                                                                                                                          | HFIOFR                                                             | _                 | —                  | LFIOFR     | HFIOFS        |  |  |  |  |

| bit 7            |                                                                    |                                                                                                                                               |                                                                    |                   |                    |            | bit C         |  |  |  |  |

|                  |                                                                    |                                                                                                                                               |                                                                    |                   |                    |            |               |  |  |  |  |

| Legend:          |                                                                    |                                                                                                                                               |                                                                    |                   |                    |            |               |  |  |  |  |

| R = Readable     | e bit                                                              | W = Writable                                                                                                                                  | bit                                                                | U = Unimplem      | ented bit, read    | as '0'     |               |  |  |  |  |

| u = Bit is unc   | hanged                                                             | x = Bit is unkn                                                                                                                               | -n/n = Value a                                                     | t POR and BOI     | R/Value at all oth | ner Resets |               |  |  |  |  |

| '1' = Bit is set | t                                                                  | '0' = Bit is clea                                                                                                                             | ared                                                               | q = Conditiona    | al                 |            |               |  |  |  |  |

| bit 7            | <u>If T1OSCEN</u><br>1 = Second<br>0 = Second<br><u>If T1OSCEN</u> | lary oscillator is r<br>lary oscillator is r                                                                                                  | eady<br>not ready                                                  |                   |                    |            |               |  |  |  |  |

| bit 6            | Unimplemer                                                         | nted: Read as '0                                                                                                                              | ,                                                                  |                   |                    |            |               |  |  |  |  |

| bit 5            | When the FC<br>1 = OST ha<br>0 = OST is<br>bits.<br>For all other  | lator Start-up Tim<br><u>SC&lt;2:0&gt; bits se</u><br>as counted 1024<br>counting, device<br><u>FOSC&lt;2:0&gt; bit s</u><br>2, "OSTS Bit Det | elect HS. XT or<br>clocks, device<br>is clocked from<br>elections: | is clocked by the |                    |            | the IRCF<3:0> |  |  |  |  |

| bit 4            | 1 = HFINTC                                                         | gh-Frequency Int<br>DSC is ready<br>DSC is not ready                                                                                          | ernal Oscillator                                                   | Ready bit         |                    |            |               |  |  |  |  |

| bit 3-2          | Unimplemer                                                         | nted: Read as '0                                                                                                                              | ,                                                                  |                   |                    |            |               |  |  |  |  |

| bit 1            | 1 = LFINTO                                                         | LFIOFR: Low-Frequency Internal Oscillator Ready bit<br>1 = LFINTOSC is ready<br>0 = LFINTOSC is not ready                                     |                                                                    |                   |                    |            |               |  |  |  |  |

| bit 0            | 1 = HFINTC                                                         | h-Frequency Inte<br>SC 16 MHz Osc<br>SC 16 MHz is ne                                                                                          | illator is stable                                                  | and is driving th |                    | DSC        |               |  |  |  |  |

# REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|------------|-------|-------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  |       | _          |       | _     | _     | BORRDY | 64                  |

| PCON   | STKOVF | STKUNF | _     | RWDT       | RMCLR | RI    | POR   | BOR    | 68                  |

| STATUS | —      | _      | _     | TO         | PD    | Z     | DC    | С      | 19                  |

| WDTCON | —      | —      |       | WDTPS<4:0> |       |       |       |        | 88                  |

TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

TABLE 6-6:

SUMMARY OF CONFIGURATION WORD WITH RESETS

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4   | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|----------|------------|----------|----------|-----------|----------|---------------------|

| CONFIG1 | 13:8 |         | —       | FCMEN    | IESO       | CLKOUTEN | BORE     | N<1:0>    | _        | 40                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WRTE WDTE< |          | [        | FOSC<2:0> | <b>`</b> | 43                  |

|         | 13:8 | _       | _       | LVP      | —          | LPBOR    | BORV     | STVREN    | _        | 40                  |

| CONFIG2 | 7:0  | _       | _       | _        | _          | _        | _        | WRT       | <1:0>    | 43                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

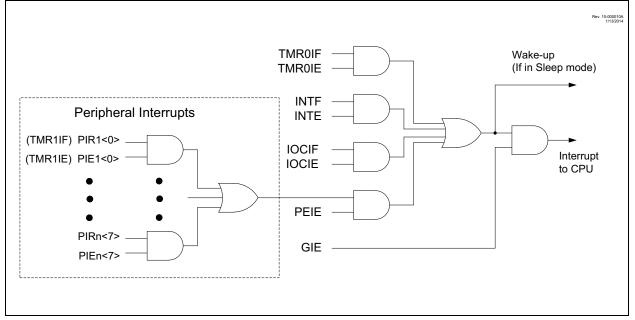

# 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|--------|---------|--------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF  | INTF   | IOCIF  | 75                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA    | PS<2:0> |        |        | 154                 |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | SSP1IE | —       | TMR2IE | TMR1IE | 76                  |

| PIE2       | OSFIE   | C2IE   | C1IE   | _      | BCL1IE | NCO1IE  | _      | —      | 77                  |

| PIE3       | _       | _      | _      | _      | CLC4IE | CLC3IE  | CLC2IE | CLC1IE | 78                  |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | SSP1IF | —       | TMR2IF | TMR1IF | 79                  |

| PIR2       | OSFIF   | C2IF   | C1IF   |        | BCL1IF | NCO1IF  |        | _      | 80                  |

| PIR3       | _       |        |        |        | CLC4IF | CLC3IF  | CLC2IF | CLC1IF | 81                  |

#### TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

PIC16(L)F1508/9

# 11.8 Register Definitions: PORTC

# REGISTER 11-12: PORTC: PORTC REGISTER

| R/W-x/u          | R/W-x/u                                 | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|------------------|-----------------------------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| RC7              | RC6                                     | RC5               | RC4     | RC3                                                   | RC2     | RC1     | RC0     |  |  |

| bit 7            |                                         |                   |         |                                                       |         |         | bit 0   |  |  |

|                  |                                         |                   |         |                                                       |         |         |         |  |  |

| Legend:          |                                         |                   |         |                                                       |         |         |         |  |  |

| R = Readable     | bit                                     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unch  | u = Bit is unchanged x = Bit is unknown |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set |                                         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |  |

bit 7-0 **RC<7:0>**: PORTC General Purpose I/O Pin bits 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

### REGISTER 11-13: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

# REGISTER 11-14: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

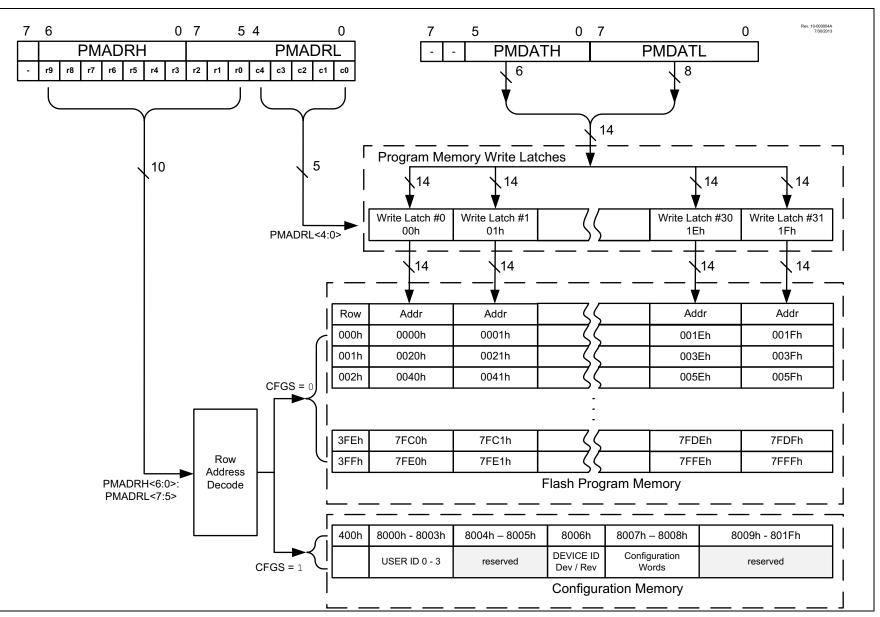

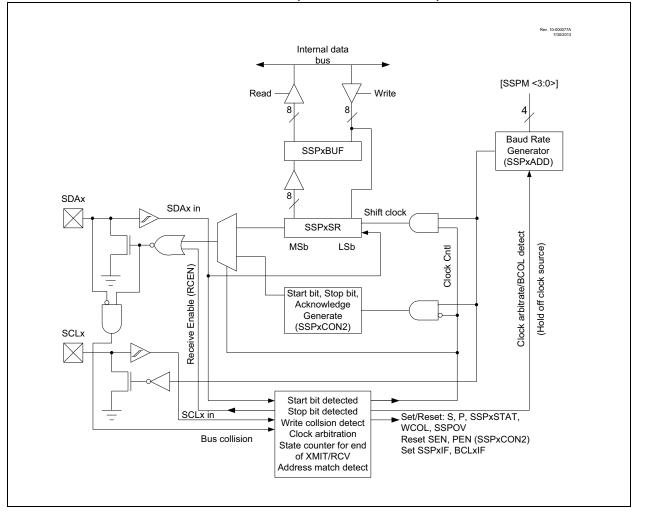

# 21.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

# 21.1 MSSP Module Overview

The Master Synchronous Serial Port (MSSPx) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSPx module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- · Clock Parity

- Slave Select Synchronization (Slave mode only)

- Daisy-chain connection of slave devices

Figure 21-1 is a block diagram of the SPI interface module.

## FIGURE 21-1: MSSP BLOCK DIAGRAM (SPI MODE)

The  $I^2C$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- Clock stretching

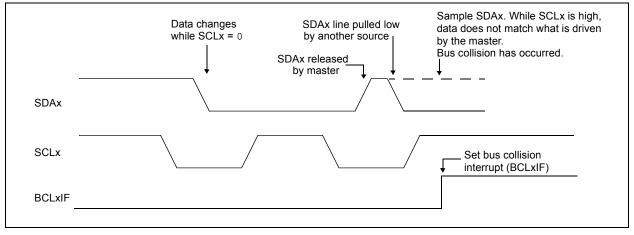

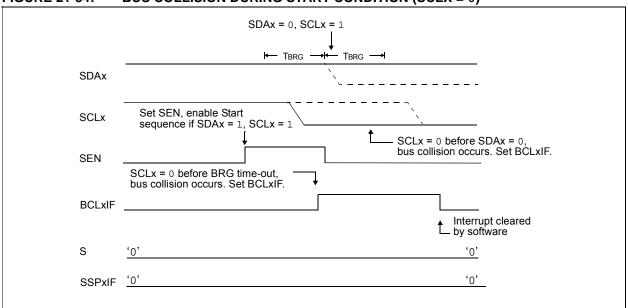

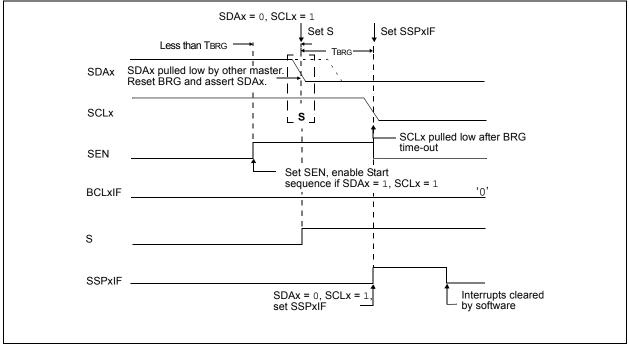

- Bus collision detection

- General call address matching

- Address masking

- · Address Hold and Data Hold modes

- · Selectable SDAx hold times

Figure 21-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 21-3 is a diagram of the  $I^2C$  interface module in Slave mode.

Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSPxCON1 and SSPxCON2 registers control different operational aspects of the same module, while SSPxCON1 and SSP2CON1 control the same features for two different modules.

2: Throughout this section, generic references to an MSSPx module in any of its operating modes may be interpreted as being equally applicable to MSSPx or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

# FIGURE 21-2: MSSPX BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

# 21.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCKx)

- Serial Data Out (SDOx)

- Serial Data In (SDIx)

- Slave Select (SSx)

Figure 21-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 21-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 21-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDOx output pin which is connected to, and received by, the slave's SDIx input pin. The slave device transmits information out on its SDOx output pin, which is connected to, and received by, the master's SDIx input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register. During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on its SDOx pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDOx pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

#### FIGURE 21-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz                                    |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 16.000 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0             | 0.00       | 13332                       | 300.0              | 0.00       | 9215                        |

| 1200   | 1200                                                 | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200.1            | 0.01       | 3332                        | 1200               | 0.00       | 2303                        |

| 2400   | 2400                                                 | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2399.5            | -0.02      | 1666                        | 2400               | 0.00       | 1151                        |

| 9600   | 9597                                                 | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9592              | -0.08      | 416                         | 9600               | 0.00       | 287                         |

| 10417  | 10417                                                | 0.00       | 479                         | 10425             | 0.08       | 441                         | 10417             | 0.00       | 383                         | 10433              | 0.16       | 264                         |

| 19.2k  | 19.23k                                               | 0.16       | 259                         | 19.20k            | 0.00       | 239                         | 19.23k            | 0.16       | 207                         | 19.20k             | 0.00       | 143                         |

| 57.6k  | 57.47k                                               | -0.22      | 86                          | 57.60k            | 0.00       | 79                          | 57.97k            | 0.64       | 68                          | 57.60k             | 0.00       | 47                          |

| 115.2k | 116.3k                                               | 0.94       | 42                          | 115.2k            | 0.00       | 39                          | 114.29k           | -0.79      | 34                          | 115.2k             | 0.00       | 23                          |

# TABLE 22-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|------------------------------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz                                     |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                                                | 0.00       | 6666                        | 300.0            | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200                                                 | -0.02      | 1666                        | 1200             | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1202             | 0.16       | 207                         |

| 2400   | 2401                                                 | 0.04       | 832                         | 2398             | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 103                         |

| 9600   | 9615                                                 | 0.16       | 207                         | 9615             | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 25                          |

| 10417  | 10417                                                | 0          | 191                         | 10417            | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k                                               | 0.16       | 103                         | 19.23k           | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 57.14k                                               | -0.79      | 34                          | 58.82k           | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | —                | _          | _                           |

| 115.2k | 117.6k                                               | 2.12       | 16                          | 111.1k           | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | _                | —          | —                           |

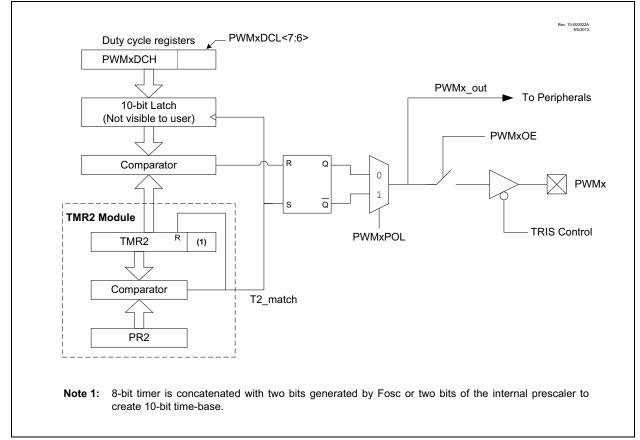

# 23.0 PULSE-WIDTH MODULATION (PWM) MODULE

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PR2

- T2CON

- PWMxDCH

- PWMxDCL

- PWMxCON

# FIGURE 23-1: SIMPLIFIED PWM BLOCK DIAGRAM

For a step-by-step procedure on how to set up this module for PWM operation, refer to Section 23.1.9 "Setup for PWM Operation using PWMx Pins".

# PIC16(L)F1508/9

# PIC16(L)F1508/9

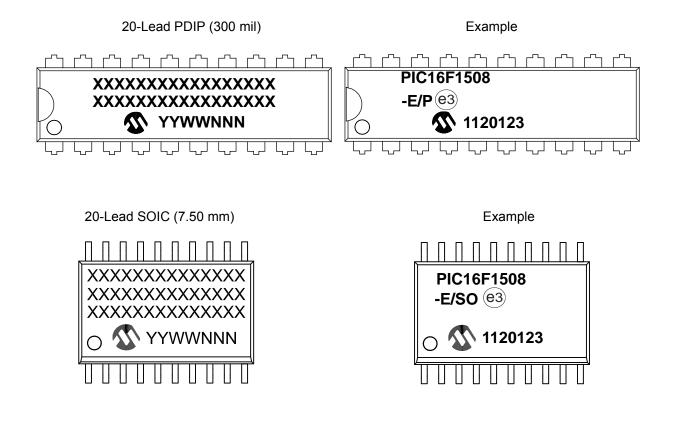

# 32.0 PACKAGING INFORMATION

# 32.1 Package Marking Information

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                                           |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

# 32.2 Package Details

The following sections give the technical details of the packages.

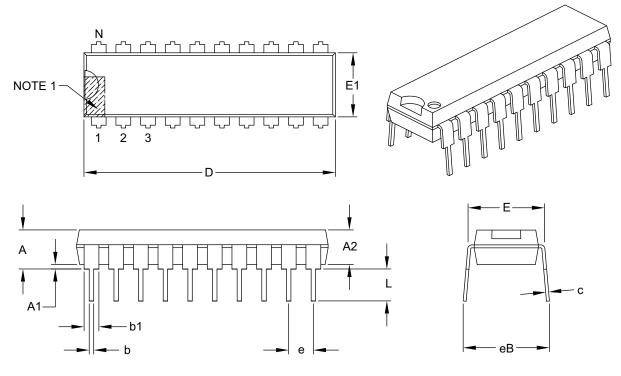

# 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES           |          |       |       |  |  |

|----------------------------|------------------|----------|-------|-------|--|--|

| Dimensio                   | Dimension Limits |          |       |       |  |  |

| Number of Pins             | N                | 20       |       |       |  |  |

| Pitch                      | е                | .100 BSC |       |       |  |  |

| Top to Seating Plane       | А                | -        | -     | .210  |  |  |

| Molded Package Thickness   | A2               | .115     | .130  | .195  |  |  |

| Base to Seating Plane      | A1               | .015     | -     | _     |  |  |

| Shoulder to Shoulder Width | E                | .300     | .310  | .325  |  |  |

| Molded Package Width       | E1               | .240     | .250  | .280  |  |  |

| Overall Length             | D                | .980     | 1.030 | 1.060 |  |  |

| Tip to Seating Plane       | L                | .115     | .130  | .150  |  |  |

| Lead Thickness             | с                | .008     | .010  | .015  |  |  |

| Upper Lead Width           | b1               | .045     | .060  | .070  |  |  |

| Lower Lead Width           | b                | .014     | .018  | .022  |  |  |

| Overall Row Spacing §      | eB               | -        | -     | .430  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B