Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1508-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

The block diagram of these devices are shown in Figure 1-1, the available peripherals are shown in Table 1-1, and the pinout descriptions are shown in Table 1-2.

| TABLE 1-1: | DEVICE PERIPHERAL SUMMARY |

|------------|---------------------------|

|------------|---------------------------|

| Peripheral                                                             |            | PIC12(L)F1501 | PIC16(L)F1503 | PIC16(L)F1507 | PIC16(L)F1508 | PIC16(L)F1509 |

|------------------------------------------------------------------------|------------|---------------|---------------|---------------|---------------|---------------|

| Analog-to-Digital Converter (A                                         | ADC)       | •             | •             | •             | •             | •             |

| Complementary Wave Generation                                          | ator (CWG) | •             | •             | •             | ٠             | •             |

| Digital-to-Analog Converter (I                                         | DAC)       | ٠             | •             |               | ٠             | •             |

| Enhanced Universal<br>Synchronous/Asynchronous<br>Transmitter (EUSART) | Receiver/  |               |               |               | ٠             | •             |

| Fixed Voltage Reference (FV                                            | R)         | ٠             | •             | •             | ٠             | •             |

| Numerically Controlled Oscilla                                         | ator (NCO) | ٠             | •             | •             | ٠             | •             |

| Temperature Indicator                                                  |            | ٠             | •             | •             | ٠             | •             |

| Comparators                                                            |            |               |               |               |               |               |

|                                                                        | C1         | ٠             | •             |               | ٠             | •             |

|                                                                        | C2         |               | •             |               | •             | •             |

| Configurable Logic Cell (CLC                                           | :)         |               |               |               |               |               |

|                                                                        | CLC1       | •             | •             | •             | •             | •             |

|                                                                        | CLC2       | •             | •             | •             | ٠             | •             |

|                                                                        | CLC3       |               |               |               | ٠             | •             |

|                                                                        | CLC4       |               |               |               | •             | •             |

| Master Synchronous Serial P                                            | orts       |               | 1             |               |               |               |

|                                                                        | MSSP1      |               | •             |               | •             | •             |

| PWM Modules                                                            |            |               |               |               |               |               |

|                                                                        | PWM1       | •             | •             | •             | •             | •             |

|                                                                        | PWM2       | •             | •             | •             | •             | •             |

|                                                                        | PWM3       | •             | •             | •             | •             | •             |

| PWM4                                                                   |            |               | •             | •             | ٠             | •             |

| Timers                                                                 | 1          |               |               |               |               |               |

|                                                                        | Timer0     | •             | •             | •             | ٠             | •             |

|                                                                        | Timer1     | •             | •             | •             | •             | •             |

|                                                                        | Timer2     | •             | •             | •             | •             | •             |

# 3.4 PCL and PCLATH

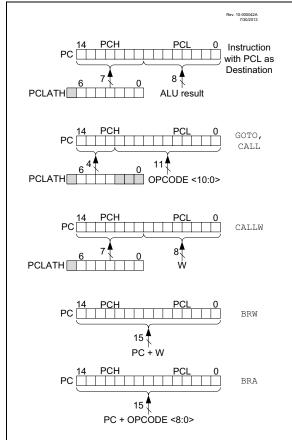

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-3 shows the five situations for the loading of the PC.

### 3.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

### 3.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

### 3.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

### 3.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

|                |                                                                                                                  | R/P-1                                                                                                                                                                                        | R/P-1                                                                                                                                         | R/P-1                                                                                  | R/P-1                                          | R/P-1                             | U-1           |

|----------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------|---------------|

|                |                                                                                                                  | LVP <sup>(1)</sup>                                                                                                                                                                           | DEBUG <sup>(3)</sup>                                                                                                                          | LPBOR                                                                                  | BORV <sup>(2)</sup>                            | STVREN                            | _             |

|                |                                                                                                                  | bit 13                                                                                                                                                                                       | ·                                                                                                                                             |                                                                                        |                                                |                                   | bita          |

| U-1            | U-1                                                                                                              | U-1                                                                                                                                                                                          | U-1                                                                                                                                           | U-1                                                                                    | U-1                                            | R/P-1                             | R/P-1         |

| _              | —                                                                                                                | _                                                                                                                                                                                            | _                                                                                                                                             | —                                                                                      | _                                              | WRT<                              | :1:0>         |

| bit 7          | ·                                                                                                                | ·                                                                                                                                                                                            | ·                                                                                                                                             |                                                                                        |                                                |                                   | bit           |

| Legend:        |                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                               |                                                                                        |                                                |                                   |               |

| R = Readal     | ole bit                                                                                                          | P = Programr                                                                                                                                                                                 | nable bit                                                                                                                                     | U = Unimplen                                                                           | nented bit, read                               | d as '1'                          |               |

| '0' = Bit is c | leared                                                                                                           | '1' = Bit is set                                                                                                                                                                             |                                                                                                                                               | -n = Value wh                                                                          | en blank or aft                                | er Bulk Erase                     |               |

|                |                                                                                                                  |                                                                                                                                                                                              |                                                                                                                                               |                                                                                        |                                                |                                   |               |

| bit 13         | 1 = Low-volta                                                                                                    | oltage Programr<br>age programmir<br>age on MCLR r                                                                                                                                           | ng enabled                                                                                                                                    |                                                                                        | 3                                              |                                   |               |

| bit 12         | 1 = In-Circuit                                                                                                   |                                                                                                                                                                                              | bled, ICSPCLK                                                                                                                                 |                                                                                        |                                                | urpose I/O pins<br>to the debugge | r             |

| bit 11         | 1 = Low-Pow                                                                                                      | /-Power BOR E<br>/er Brown-out R<br>/er Brown-out R                                                                                                                                          | eset is disable                                                                                                                               |                                                                                        |                                                |                                   |               |

| bit 10         | 1 = Brown-ou                                                                                                     | n-Out Reset Vo<br>ut Reset voltage<br>ut Reset voltage                                                                                                                                       | e (VBOR), low tr                                                                                                                              | ip point selecte                                                                       |                                                |                                   |               |

| bit 9          | STVREN: Sta<br>1 = Stack Ov                                                                                      | ack Overflow/U<br>erflow or Under<br>erflow or Under                                                                                                                                         | nderflow Reset                                                                                                                                | Enable bit<br>a Reset                                                                  |                                                |                                   |               |

| bit 8-2        |                                                                                                                  | nted: Read as '                                                                                                                                                                              |                                                                                                                                               |                                                                                        |                                                |                                   |               |

| bit 1-0        | <u>4 kW Flash n</u><br>11 = Wr<br>10 = 000<br>01 = 000<br><u>8 kW Flash n</u><br>11 = Wr<br>10 = 000<br>01 = 000 | Flash Memory S<br>nemory (PIC16)<br>ite protection of<br>0h to 1FFh write<br>0h to 7FFh write<br>0h to 7FFh write<br>nemory (PIC16)<br>ite protection of<br>00h to 01FFh w<br>00h to 0FFFh w | (L)F1508/9 only<br>ff<br>e protected, 20<br>e protected, 80<br>e protected, no<br>(L)F1509 only)<br>ff<br>rite protected,<br>vrite protected, | ()<br>0h to FFFh ma<br>0h to FFFh ma<br>addresses ma<br>0200h to 1FFF<br>1000h to 1FFF | y be modified<br>y be modified<br>h may be mod | ified                             |               |

| Note 1:        | The LVP bit canr                                                                                                 |                                                                                                                                                                                              |                                                                                                                                               |                                                                                        | -                                              |                                   |               |

|                | See VBOR param                                                                                                   |                                                                                                                                                                                              |                                                                                                                                               | • •                                                                                    |                                                |                                   |               |

|                |                                                                                                                  | -                                                                                                                                                                                            |                                                                                                                                               | -                                                                                      |                                                |                                   | -   - :     : |

### REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2

**3:** The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

# 5.3.5 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PPLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

# 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT, or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

**Note:** Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCSTAT register to remain clear.

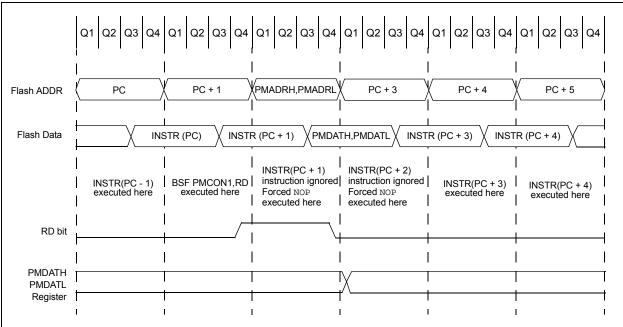

#### FIGURE 10-2: FLASH PROGRAM MEMORY READ CYCLE EXECUTION

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

\* This code block will read 1 word of program

- \* memory at the memory address:

- PROG\_ADDR\_HI : PROG\_ADDR\_LO

- \* data will be returned in the variables;

- \* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL                  | PMADRL                   | ; Select Bank for PMCON registers                                                                            |

|--------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------|

| MOVLW                    | PROG_ADDR_LO             | ;                                                                                                            |

| MOVWF                    | PMADRL                   | ; Store LSB of address                                                                                       |

| MOVLW                    | PROG_ADDR_HI             | ;                                                                                                            |

| MOVWF                    | PMADRH                   | ; Store MSB of address                                                                                       |

| BCF<br>BSF<br>NOP<br>NOP | PMCON1,CFGS<br>PMCON1,RD | ; Do not select Configuration Space<br>; Initiate read<br>; Ignored (Figure 10-2)<br>; Ignored (Figure 10-2) |

| MOVF                     | PMDATL,W                 | ; Get LSB of word                                                                                            |

| MOVWF                    | PROG_DATA_LO             | ; Store in user location                                                                                     |

| MOVF                     | PMDATH,W                 | ; Get MSB of word                                                                                            |

| MOVWF                    | PROG_DATA_HI             | ; Store in user location                                                                                     |

# 17.8 Register Definitions: Comparator Control

| R/W-0/0         | R-0/0                  | R/W-0/0                                 | R/W-0/0          | U-0              | R/W-1/1          | R/W-0/0         | R/W-0/0         |

|-----------------|------------------------|-----------------------------------------|------------------|------------------|------------------|-----------------|-----------------|

| CxON            | CxOUT                  | CxOE                                    | CxPOL            | _                | CxSP             | CxHYS           | CxSYNC          |

| bit 7           | •                      |                                         | •                |                  |                  | •               | bit 0           |

|                 |                        |                                         |                  |                  |                  |                 |                 |

| Legend:         | . 1.11                 |                                         | 1.11             |                  |                  | 1               |                 |

| R = Readabl     |                        | W = Writable                            |                  | •                | mented bit, read |                 | othor Doooto    |

| u = Bit is unc  | 0                      | x = Bit is unknown                      |                  | -n/n = value     | at POR and BC    | rk/value at all | other Resets    |

| '1' = Bit is se | t                      | '0' = Bit is cle                        | areo             |                  |                  |                 |                 |

| bit 7           | CxON: Com              | parator Enable                          | bit              |                  |                  |                 |                 |

|                 |                        | ator is enabled                         |                  |                  |                  |                 |                 |

|                 | 0 = Compara            | ator is disabled                        | and consumes     | s no active pow  | ver              |                 |                 |

| bit 6           | CxOUT: Con             | nparator Output                         | bit              |                  |                  |                 |                 |

|                 |                        | (inverted polar                         | <u>ity):</u>     |                  |                  |                 |                 |

|                 | 1 = CxVP <             |                                         |                  |                  |                  |                 |                 |

|                 | 0 = CxVP >             | (non-inverted)                          | oolarity):       |                  |                  |                 |                 |

|                 | 1 = CxVP >             |                                         | <u>Jolanty).</u> |                  |                  |                 |                 |

|                 | 0 = CxVP <             | CxVN                                    |                  |                  |                  |                 |                 |

| bit 5           | CxOE: Com              | parator Output                          | Enable bit       |                  |                  |                 |                 |

|                 |                        | is present on th                        |                  | Requires that th | he associated T  | RIS bit be clea | red to actually |

|                 |                        | pin. Not affect                         | ed by CxON.      |                  |                  |                 |                 |

|                 |                        | is internal only                        |                  |                  |                  |                 |                 |

| bit 4           |                        | nparator Outpu                          | -                | ct bit           |                  |                 |                 |

|                 |                        | ator output is inv<br>ator output is no |                  |                  |                  |                 |                 |

| bit 3           | •                      |                                         |                  |                  |                  |                 |                 |

|                 | •                      | nted: Read as '                         |                  | :4               |                  |                 |                 |

| bit 2           | -                      | parator Speed/F                         |                  |                  |                  |                 |                 |

|                 | •                      | ator mode in no<br>ator mode in lov     |                  | •                |                  |                 |                 |

| bit 1           | -                      | nparator Hyster                         | -                | -                |                  |                 |                 |

|                 |                        | ator hysteresis                         |                  |                  |                  |                 |                 |

|                 | 0 = Compar             | ator hysteresis                         | disabled         |                  |                  |                 |                 |

| bit 0           | CxSYNC: Co             | omparator Outp                          | ut Synchronou    | us Mode bit      |                  |                 |                 |

|                 |                        | ator output to 1                        |                  |                  |                  | ges on Timer1   | clock source    |

|                 | Output ι<br>0 = Compar | updated on the                          | •••              |                  |                  |                 |                 |

|                 |                        |                                         |                  |                  |                  |                 |                 |

#### REGISTER 17-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

### 19.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 19.4 Timer1 (Secondary) Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal. The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires some time to start-up and stabilize before use. The SOSCR bit in the OSCSTAT register monitors the oscillator and indicates when the oscillator is ready for use. When T1OSCEN is set, the SOSCR bit is cleared. After 1024 cycles of the oscillator are countered, the SOSCR bit is set, indicating that the oscillator should be stable and ready for use.

# 19.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 19.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 19.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads. For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 19.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 19.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 19-3 for timing details.

# TABLE 19-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 19.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 19-4. Source selection is controlled by the T1GSS<1:0> bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

| TABLE 19-4: | TIMER1 GATE SOURCES |

|-------------|---------------------|

|-------------|---------------------|

| T1GSS   | Timer1 Gate Source                                                    |

|---------|-----------------------------------------------------------------------|

| 00      | Timer1 Gate pin (T1G)                                                 |

| 01      | Overflow of Timer0 (T0_overflow)<br>(TMR0 increments from FFh to 00h) |

| 10      | Comparator 1 Output (C1OUT_sync) <sup>(1)</sup>                       |

| 11      | Comparator 2 Output (C2OUT_sync) <sup>(1)</sup>                       |

| Nata di |                                                                       |

Note 1: Optionally synchronized comparator output.

#### 21.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCKx pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCKx pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 21.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 21-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

#### 21.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 0100).

When the  $\overline{\text{SSx}}$  pin is low, transmission and reception are enabled and the SDOx pin is driven.

When the  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SSx}$ pin control enabled (SSPxCON1<3:0> = 0100), the SPI module will reset if the $\overline{SSx}$ pin is set to VDD. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable SSx pin control.                                                                               |

| 3:      | While operated in SPI Slave mode the SMP bit of the SSPxSTAT register must remain clear.                                                                             |

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPEN bit.

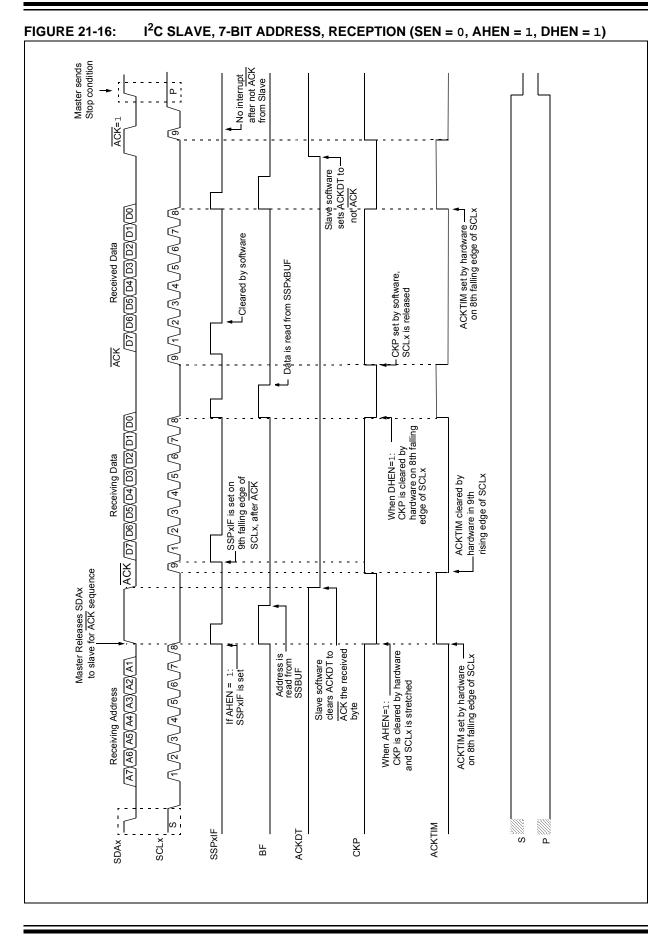

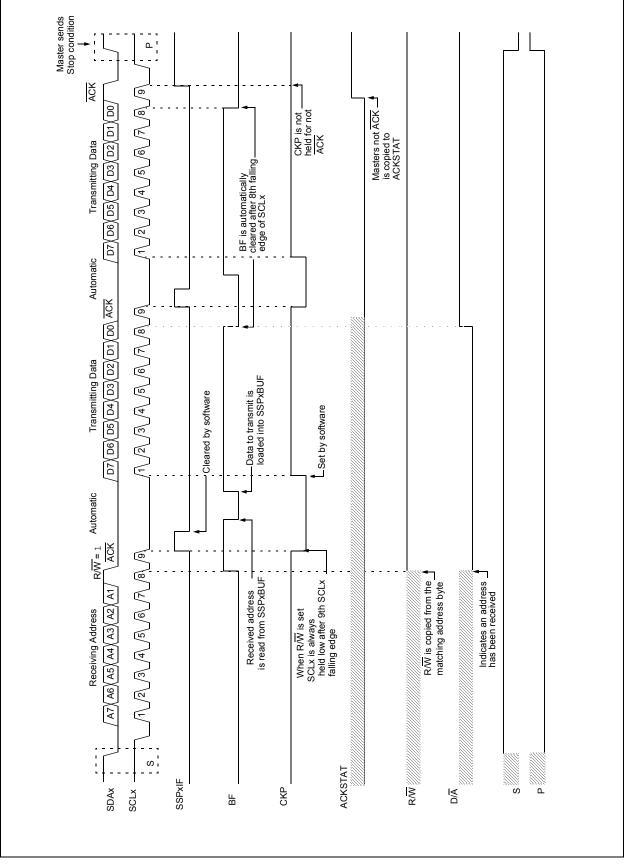

#### 21.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCLx pin is held low (see **Section21.5.6 "Clock Stretching"** for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCLx pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCLx input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 21.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDAx line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 21.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 21-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDAx and SCLx.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit set is received by the slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCLx, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

**Note 1:** If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCLx (ninth) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

#### 23.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 23-4.

# EQUATION 23-4: PWM RESOLUTION

Resolution =  $\frac{\log[4(PR2 + 1)]}{\log(2)}$  bits

**Note:** If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| PWM Frequency             | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

### TABLE 23-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

### 23.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 23.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

### 23.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

| R/W-0/0                            | R/W-0/0                                                                                                                                      | U-0             | U-0             | R/W-0/0         | R/W-0/0          | R/W-0/0   | R/W-0/0     |  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|------------------|-----------|-------------|--|

| GxASE                              | GxARSEN                                                                                                                                      | —               | —               | GxASDSC2        | GxASDSC1         | GxASDSFLT | GxASDSCLC2  |  |

| bit 7                              |                                                                                                                                              |                 |                 |                 |                  |           | bit 0       |  |

| Legend:                            |                                                                                                                                              |                 |                 |                 |                  |           |             |  |

| R = Readable I                     | hit                                                                                                                                          | W = Writable    | hit             | II = I Inimplen | nented bit, read | las '0'   |             |  |

| u = Bit is uncha                   |                                                                                                                                              | x = Bit is unk  |                 |                 | at POR and BO    |           | ther Resets |  |

| '1' = Bit is set                   | angeu                                                                                                                                        | 0' = Bit is cle |                 |                 | ends on condit   |           |             |  |

|                                    |                                                                                                                                              |                 |                 |                 |                  | · · · ·   |             |  |

| bit 7                              | GxASE: Auto                                                                                                                                  | -Shutdown Ev    | ent Status bit  |                 |                  |           |             |  |

|                                    | 1 = An auto-s                                                                                                                                |                 |                 |                 |                  |           |             |  |

|                                    | 0 = No auto-s                                                                                                                                |                 |                 | ed              |                  |           |             |  |

| bit 6                              | GxARSEN: A                                                                                                                                   |                 | nable bit       |                 |                  |           |             |  |

|                                    | 1 = Auto-restart is enabled<br>0 = Auto-restart is disabled                                                                                  |                 |                 |                 |                  |           |             |  |

| bit 5-4 Unimplemented: Read as '0' |                                                                                                                                              |                 |                 |                 |                  |           |             |  |

| bit 3                              |                                                                                                                                              |                 |                 |                 |                  |           |             |  |

|                                    | $1 =$ Shutdown when Comparator C2 output (C2OUT_async) is high                                                                               |                 |                 |                 |                  |           |             |  |

|                                    | 0 = Compara                                                                                                                                  | •               |                 |                 |                  |           |             |  |

| bit 2                              |                                                                                                                                              |                 |                 | omparator C1 E  |                  |           |             |  |

|                                    | <ul> <li>1 = Shutdown when Comparator C1 output (C1OUT_async) is high</li> <li>0 = Comparator C1 output has no effect on shutdown</li> </ul> |                 |                 |                 |                  |           |             |  |

| bit 1                              |                                                                                                                                              |                 |                 |                 |                  |           |             |  |

|                                    | 1 = Shutdown when CWG1FLT input is low                                                                                                       |                 |                 |                 |                  |           |             |  |

|                                    | 0 = CWG1FLT input has no effect on shutdown                                                                                                  |                 |                 |                 |                  |           |             |  |

|                                    | 0 = CWG1FL                                                                                                                                   | I input has no  | b effect on shi | utdown          |                  |           |             |  |

| bit 0                              |                                                                                                                                              | 2: CWG Auto     | -shutdown on    | CLC2 Enable     | bit              |           |             |  |

### REGISTER 26-3: CWGxCON2: CWG CONTROL REGISTER 2

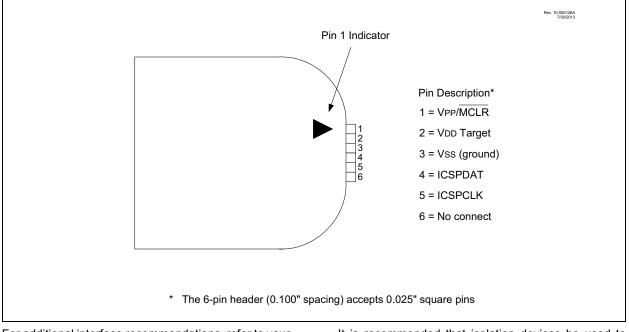

#### FIGURE 27-2: PICkit<sup>™</sup> PROGRAMMER STYLE CONNECTOR INTERFACE

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

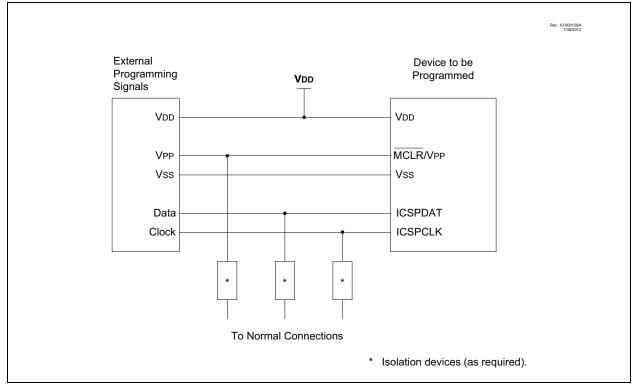

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 27-3 for more information.

#### FIGURE 27-3: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

# 29.2 Standard Operating Conditions

The standard operating conditions for any device are defined as:

|                                              | ······                                                                                                                                                                          |        |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Operating Voltage:<br>Operating Temperature: | $\label{eq:VDDMIN} \begin{array}{l} \forall V \text{DDMIN} \leq V \text{DD} \leq V \text{DDMAX} \\ \text{TA}\_\text{MIN} \leq \text{TA} \leq \text{TA}\_\text{MAX} \end{array}$ |        |

| VDD — Operating Supply                       | Voltage <sup>(1)</sup>                                                                                                                                                          |        |

| PIC16LF1508/9                                |                                                                                                                                                                                 |        |

| VDDMIN (Fo                                   | $sc \leq 16 \text{ MHz}$ )                                                                                                                                                      |        |

|                                              |                                                                                                                                                                                 |        |

| VDDMAX                                       |                                                                                                                                                                                 |        |

| PIC16F1508/9                                 |                                                                                                                                                                                 |        |

| VDDMIN (Fo                                   | osc ≤ 16 MHz)                                                                                                                                                                   |        |

| VDDMIN (16                                   | 6 MHz < Fosc ≤ 20 MHz)                                                                                                                                                          | +2.5V  |

| VDDMAX                                       |                                                                                                                                                                                 |        |

| TA — Operating Ambient                       | Temperature Range                                                                                                                                                               |        |

| Industrial Temperatu                         | ire                                                                                                                                                                             |        |

| TA_MIN                                       |                                                                                                                                                                                 | -40°C  |

| Та_мах                                       |                                                                                                                                                                                 | +85°C  |

| Extended Temperatu                           | ure                                                                                                                                                                             |        |

| TA_MIN                                       |                                                                                                                                                                                 | -40°C  |

| Та_мах                                       |                                                                                                                                                                                 | +125°C |

|                                              |                                                                                                                                                                                 |        |

Note 1: See Parameter D001, DC Characteristics: Supply Voltage.

| PIC16LF | 1508/9          | Standard Operating Conditions (unless otherwise stated) |      |       |       |     |                                         |  |

|---------|-----------------|---------------------------------------------------------|------|-------|-------|-----|-----------------------------------------|--|

| PIC16F1 | 508/9           |                                                         |      |       |       |     |                                         |  |

| Param.  | Device          | Min.                                                    | Typ† | Max.  | Units |     | Conditions                              |  |

| No.     | Characteristics | 141111.                                                 | וקעי | WIAX. | Units | Vdd | Note                                    |  |

| D019B   |                 | —                                                       | 6    | 16    | μA    | 1.8 | Fosc = 32 kHz,                          |  |

|         |                 | —                                                       | 8    | 22    | μA    | 3.0 | External Clock (ECL),<br>Low-Power mode |  |

| D019B   |                 | -                                                       | 13   | 28    | μA    | 2.3 | Fosc = 32 kHz,                          |  |

|         |                 |                                                         | 15   | 31    | μA    | 3.0 | External Clock (ECL),                   |  |

|         |                 | —                                                       | 16   | 36    | μA    | 5.0 | Low-Power mode                          |  |

| D019C   |                 |                                                         | 19   | 35    | μA    | 1.8 | Fosc = 500 kHz,                         |  |

|         |                 | —                                                       | 32   | 55    | μA    | 3.0 | External Clock (ECL),<br>Low-Power mode |  |

| D019C   |                 | _                                                       | 31   | 52    | μA    | 2.3 | Fosc = 500 kHz,                         |  |

|         |                 | _                                                       | 38   | 65    | μA    | 3.0 | External Clock (ECL),                   |  |

|         |                 | —                                                       | 44   | 74    | μA    | 5.0 | Low-Power mode                          |  |

| D020    |                 | _                                                       | 140  | 210   | μA    | 1.8 | Fosc = 4 MHz,                           |  |

|         |                 | —                                                       | 250  | 330   | μA    | 3.0 | EXTRC (Note 3)                          |  |

| D020    |                 | _                                                       | 210  | 290   | μA    | 2.3 | Fosc = 4 MHz,                           |  |

|         |                 | _                                                       | 280  | 380   | μA    | 3.0 | EXTRC (Note 3)                          |  |

|         |                 | —                                                       | 350  | 470   | μA    | 5.0 |                                         |  |

| D021    |                 | -                                                       | 1135 | 1700  | μΑ    | 3.0 | Fosc = 20 MHz,<br>HS Oscillator         |  |

| D021    |                 | —                                                       | 1170 | 1800  | μA    | 3.0 | Fosc = 20 MHz,                          |  |

|         |                 | —                                                       | 1555 | 2300  | μA    | 5.0 | HS Oscillator                           |  |

#### SUPPLY CURRENT (Ind)<sup>(1,2)</sup> (CONTINUED) TABLE 29-2

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

For RC oscillator configurations, current through REXT is not included. The current through the resistor can 3: be extended by the formula IR = VDD/2REXT (mA) with REXT in  $k\Omega$ .

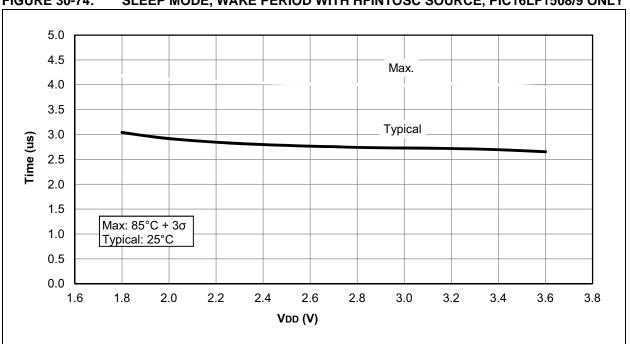

FIGURE 30-74: SLEEP MODE, WAKE PERIOD WITH HFINTOSC SOURCE, PIC16LF1508/9 ONLY

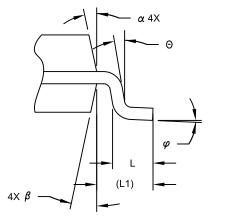

# 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| VIEW C |  |

|--------|--|

|--------|--|

|                           | Units            |           | MILLIMETERS |      |  |  |

|---------------------------|------------------|-----------|-------------|------|--|--|

| Dimension Lim             | Dimension Limits |           | NOM         | MAX  |  |  |

| Number of Pins            | N                |           | 20          |      |  |  |

| Pitch                     | е                |           | 1.27 BSC    |      |  |  |

| Overall Height            | Α                | -         | -           | 2.65 |  |  |

| Molded Package Thickness  | A2               | 2.05      | -           | -    |  |  |

| Standoff §                | A1               | 0.10      | -           | 0.30 |  |  |

| Overall Width E 10.30 BSC |                  |           |             |      |  |  |

| Molded Package Width      | E1               | 7.50 BSC  |             |      |  |  |

| Overall Length            | D                | 12.80 BSC |             |      |  |  |

| Chamfer (Optional)        | h                | 0.25      | -           | 0.75 |  |  |

| Foot Length               | L                | 0.40      | -           | 1.27 |  |  |

| Footprint                 | L1               |           | 1.40 REF    |      |  |  |

| Lead Angle                | Θ                | 0°        | -           | -    |  |  |

| Foot Angle                | φ                | 0°        | -           | 8°   |  |  |

| Lead Thickness            | С                | 0.20      | -           | 0.33 |  |  |

| Lead Width                | b                | 0.31      | -           | 0.51 |  |  |

| Mold Draft Angle Top      | α                | 5°        | -           | 15°  |  |  |

| Mold Draft Angle Bottom   | β                | 5°        | -           | 15°  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2

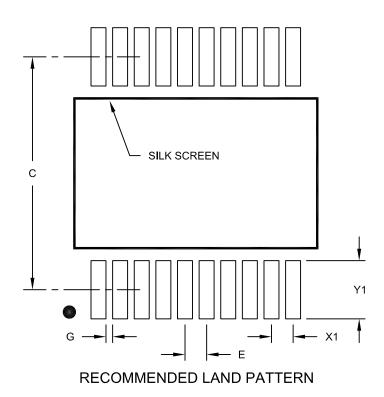

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |      |          |      |

|--------------------------|------------------|------|----------|------|

| Dimension                | Dimension Limits |      |          | MAX  |

| Contact Pitch            | E                |      | 0.65 BSC |      |

| Contact Pad Spacing      | С                |      | 7.20     |      |

| Contact Pad Width (X20)  | X1               |      |          | 0.45 |

| Contact Pad Length (X20) | Y1               |      |          | 1.75 |

| Distance Between Pads    | G                | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A

# APPENDIX A: DATA SHEET REVISION HISTORY

# Revision A (10/2011)

Original release.

### Revision B (6/2013)

Updated Electrical Specifications and added Characterization Data.

### Revision C (7/2013)

Corrected upper and lower bit definitions of address, Section 3.2. Added clarification of Buffer Gain Selection bits, Section 13.2. Removed "Preliminary" status from Section 30. Updated Figures 15-1, 29-9. Clarified information in Registers 7-1,13-1, 15-2. Clarified information in Tables 29-5, 29-10, 29-13. Removed Index.

### **Revision D (10/2014)**

Document re-release.

### **Revision E (10/2015)**

Added Section 3.2 High-Endurance Flash. Updated Figure 26-1; Registers 4-2, 7-5, and 26-3; Sections 22.4.2, 24.1.5, 26.9.1.2, 26.11.1, and 29.1; and Table 26-2.