Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1509-e-gz |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

#### 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 3.5 "Stack"** for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

# 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 28.0 "Instruction Set Summary**" for more details.

# 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

# 4.2 Register Definitions: Configuration Words

|                                       |                                                                                                       | R/P-1                       | R/P-1               | R/P-1                           | R/P-1          | R/P-1             | U-1          |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------|---------------------|---------------------------------|----------------|-------------------|--------------|--|--|

|                                       |                                                                                                       | FCMEN <sup>(1)</sup>        | IESO <sup>(1)</sup> | CLKOUTEN                        | BORE           | N<1:0> <b>(2)</b> | _            |  |  |

|                                       |                                                                                                       | bit 13                      |                     |                                 |                |                   | bit          |  |  |

| R/P-1                                 | R/P-1                                                                                                 | R/P-1                       | R/P-1               | R/P-1                           | R/P-1          | R/P-1             | R/P-1        |  |  |

| CP(3)                                 | MCLRE                                                                                                 | PWRTE                       | WDT                 | E<1:0>                          |                | FOSC<2:0>         |              |  |  |

| bit 7                                 |                                                                                                       | 11                          |                     |                                 |                |                   | bit          |  |  |

|                                       |                                                                                                       |                             |                     |                                 |                |                   |              |  |  |

| Legend:                               |                                                                                                       |                             |                     |                                 |                |                   |              |  |  |

| R = Readab                            | le bit                                                                                                | P = Programm                | able bit            | U = Unimpleme                   | ented bit, rea | d as '1'          |              |  |  |

| 0' = Bit is cl                        | eared                                                                                                 | '1' = Bit is set            |                     | -n = Value wher                 | n blank or af  | ter Bulk Erase    |              |  |  |

|                                       |                                                                                                       |                             |                     |                                 |                |                   |              |  |  |

| bit 13                                |                                                                                                       | -Safe Clock Mor             |                     | bit                             |                |                   |              |  |  |

|                                       |                                                                                                       | Clock Monitor is            |                     |                                 |                |                   |              |  |  |

|                                       |                                                                                                       | Clock Monitor is            |                     |                                 |                |                   |              |  |  |

| bit 12                                |                                                                                                       | al External Switch          |                     | ed Start-up) mod                | o is onablad   |                   |              |  |  |

|                                       |                                                                                                       | External Switcho            | • •                 | • •                             |                |                   |              |  |  |

| bit 11 CLKOUTEN: Clock Out Enable bit |                                                                                                       |                             |                     |                                 |                |                   |              |  |  |

|                                       | 1 = CLKOUT function is disabled. I/O function on the CLKOUT pin                                       |                             |                     |                                 |                |                   |              |  |  |

|                                       |                                                                                                       | function is ena             |                     | •                               |                |                   |              |  |  |

| oit 10-9                              |                                                                                                       | >: Brown-Out Re             | eset Enable b       | oits <sup>(2)</sup>             |                |                   |              |  |  |

|                                       | <ul> <li>11 = BOR enabled</li> <li>10 = BOR enabled during operation and disabled in Sleep</li> </ul> |                             |                     |                                 |                |                   |              |  |  |

|                                       |                                                                                                       |                             |                     | e BORCON regis                  | ter            |                   |              |  |  |

|                                       | 00 = BOR dis                                                                                          | •                           |                     |                                 |                |                   |              |  |  |

| bit 8                                 | Unimplemen                                                                                            | ted: Read as '1             | ,                   |                                 |                |                   |              |  |  |

| bit 7                                 | CP: Code Pro                                                                                          | otection bit <sup>(3)</sup> |                     |                                 |                |                   |              |  |  |

|                                       |                                                                                                       | memory code p               |                     |                                 |                |                   |              |  |  |

|                                       | -                                                                                                     | memory code p               |                     |                                 |                |                   |              |  |  |

| bit 6                                 |                                                                                                       | LR/VPP Pin Fun              | ction Select b      | bit                             |                |                   |              |  |  |

|                                       | <u>If LVP bit = 1</u><br>This bit is                                                                  |                             |                     |                                 |                |                   |              |  |  |

|                                       | $\frac{\text{If LVP bit} = 0}{2}$                                                                     |                             |                     |                                 |                |                   |              |  |  |

|                                       | 1 = MCLF                                                                                              | R/VPP pin function          |                     | ea <u>k pull-</u> up enable     |                |                   |              |  |  |

|                                       |                                                                                                       | •                           | n is digital inpu   | ut; MCLR internally             | / disabled; W  | eak pull-up unde  | r control of |  |  |

|                                       | WPU/                                                                                                  |                             |                     |                                 |                |                   |              |  |  |

| bit 5                                 | 1 = PWRT di                                                                                           | ver-Up Timer Er             | able bit            |                                 |                |                   |              |  |  |

|                                       | 0 = PWRT e                                                                                            |                             |                     |                                 |                |                   |              |  |  |

| oit 4-3                               |                                                                                                       | Watchdog Time               | er Enable bits      |                                 |                |                   |              |  |  |

|                                       | 11 = WDT en                                                                                           | -                           |                     |                                 |                |                   |              |  |  |

|                                       |                                                                                                       |                             |                     |                                 |                |                   |              |  |  |

|                                       |                                                                                                       | abled while run             |                     | bled in Sleep<br>n the WDTCON r |                |                   |              |  |  |

# REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1

# 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

Note: When FSCM is enabled, Two-Speed Start-up will automatically be enabled.

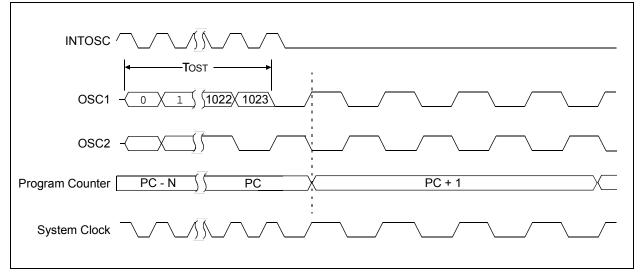

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

#### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the CPU is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or the internal oscillator. See Table 5-2.

#### TABLE 5-3: OSCILLATOR SWITCHING DELAYS

| Switch From      | Switch To            | Oscillator Delay                 |  |  |

|------------------|----------------------|----------------------------------|--|--|

|                  | LFINTOSC             | 1 cycle of each clock source     |  |  |

|                  | HFINTOSC             | 2 μs (approx.)                   |  |  |

| Any clock source | ECH, ECM, ECL, EXTRC | 2 cycles                         |  |  |

|                  | LP, XT, HS           | 1024 Clock Cycles (OST)          |  |  |

|                  | Secondary Oscillator | 1024 Secondary Oscillator Cycles |  |  |

#### FIGURE 5-8: TWO-SPEED START-UP

#### 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | ТО | PD | Condition                                                         |

|--------|--------|------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |

| 0      | 0      | 1    | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |

| 0      | 0      | u    | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |

| u      | u      | 0    | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |

| u      | u      | u    | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |

| u      | u      | u    | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |

| u      | u      | u    | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |

| u      | u      | u    | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |

| u      | u      | u    | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |

| 1      | u      | u    | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |

| u      | 1      | u    | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |

#### TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

#### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u muumuu           | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 muumuu           | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

### 11.1 Alternate Pin Function

The Alternate Pin Function Control (APFCON) register is used to steer specific peripheral input and output functions between different pins. The APFCON register is shown in Register 11-1. For this device family, the following functions can be moved between different pins.

- <u>ss</u>

- T1G

- CLC1

- NCO1

bit 0

# These bits have no effect on the values of any TRIS register. PORT and TRIS overrides will be routed to the correct pin. The unselected pin will be unaffected.

# 11.2 Register Definitions: Alternate Pin Function Control

#### **REGISTER 11-1:** APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER

| U-0            | U-0              | U-0                        | R/W-0/0 | R/W-0/0        | U-0              | R/W-0/0          | R/W-0/0     |

|----------------|------------------|----------------------------|---------|----------------|------------------|------------------|-------------|

|                | _                | _                          | SSSEL   | T1GSEL         | _                | CLC1SEL          | NCO1SEL     |

| bit 7          | ·                |                            |         |                |                  |                  | bit 0       |

|                |                  |                            |         |                |                  |                  |             |

| Legend:        |                  |                            |         |                |                  |                  |             |

| R = Readab     | ole bit          | W = Writable               | bit     | U = Unimplem   | nented bit, read | as '0'           |             |

| u = Bit is ur  | nchanged         | x = Bit is unk             | nown    | -n/n = Value a | t POR and BO     | R/Value at all o | ther Resets |

| '1' = Bit is s | et               | '0' = Bit is cle           | ared    |                |                  |                  |             |

|                |                  |                            |         |                |                  |                  |             |

| bit 7-5        | Unimplemer       | nted: Read as              | ʻ0'     |                |                  |                  |             |

| bit 4          | SSSEL: Pin       | Selection bit              |         |                |                  |                  |             |

|                |                  | tion is on RA3             |         |                |                  |                  |             |

|                | 0 = SS functions | tion is on RC6             |         |                |                  |                  |             |

| bit 3          |                  | Selection bit              |         |                |                  |                  |             |

|                | 1 = T1G fur      | -                          |         |                |                  |                  |             |

|                |                  | nction is on RA            |         |                |                  |                  |             |

| bit 2          | Unimplemer       | Unimplemented: Read as '0' |         |                |                  |                  |             |

| bit 1          | CLC1SEL: P       | in Selection bi            | t       |                |                  |                  |             |

|                | 1 = CLC1 fu      | unction is on R            | C5      |                |                  |                  |             |

- 0 = CLC1 function is on RA2

- **NCO1SEL:** Pin Selection bit 1 = NCO1 function is on RC6

- 0 = NCO1 function is on RC1

### 11.3 PORTA Registers

#### 11.3.1 DATA REGISTER

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 11-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input-only and its TRIS bit will always read as '1'. Example 11-1 shows how to initialize an I/O port.

Reading the PORTA register (Register 11-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

#### 11.3.2 DIRECTION CONTROL

The TRISA register (Register 11-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.3.3 ANALOG CONTROL

The ANSELA register (Register 11-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### EXAMPLE 11-1: INITIALIZING PORTA

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

# 11.3.4 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-2.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC and comparator inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below in Table 11-2.

| Pin Name | Function Priority <sup>(1)</sup>                        |

|----------|---------------------------------------------------------|

| RA0      | ICSPDAT<br>DAC1OUT1<br>RA0                              |

| RA1      | RA1                                                     |

| RA2      | DAC1OUT2<br>CLC1 <sup>(2)</sup><br>C1OUT<br>PWM3<br>RA2 |

| RA3      | None                                                    |

| RA4      | CLKOUT<br>SOSCO<br>RA4                                  |

| RA5      | SOSCI<br>RA5                                            |

#### TABLE 11-2: PORTA OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

2: Default pin (see APFCON register).

**3:** Alternate pin (see APFCON register).

#### 17.2.5 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 17-2 shows the output state versus input conditions, including polarity control.

TABLE 17-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### 17.2.6 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the Normal-Speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

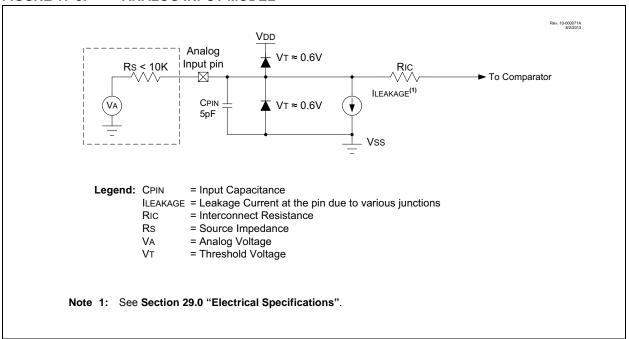

#### 17.3 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 17-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

# 19.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- · 2-bit prescaler

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- ADC Auto-Conversion Trigger(s)

- Selectable Gate Source Polarity

- · Gate Toggle mode

- · Gate Single-Pulse mode

- · Gate Value Status

- · Gate Event Interrupt

Figure 19-1 is a block diagram of the Timer1 module.

T1GSS<1:0> Rev. 10-000018A 8/5/2013 T1GSPM T1G 🔀 00 T0 overflow 01 1 C1OUT\_sync T1GVAL 10 0 D Q Single Pulse 0 Acq. Control C2OUT\_sync 11 1 Q1-D ō T1GGO/DONE \_\_\_́ >СК T1GPOL O Interrupt TMR10N set bit R TMR1GIF T1GTM det TMR1GE set flag bit TMR1IF TMR10N EN TMR1<sup>(2)</sup> T1\_overflow Synchronized Clock Input TMR1H TMR1L D 0 1 T1CLK **T1SYNC** TMR1CS<1:0> OUT SOSCI/T1CKI LFINTOSC Secondary 11 Oscillator 1 SOSCO 10 Prescaler Synchronize<sup>(3)</sup> 0 Fosc 1,2,4,8 01 Internal Clock det ΕN 00 2 Fosc/4 Fosc/2 Internal Clock T1CKPS<1:0> T1OSCEN Internal Sleep Clock Input (1) Secondary Clock To Clock Switching Module Note 1: ST Buffer is high speed type when using T1CKI. Timer1 register increments on rising edge. 2: 3: Synchronize does not operate while in Sleep.

# PIC16(L)F1508/9

© 2011-2015 Microchip Technology Inc.

#### 21.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCKx pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCKx pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

#### 21.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisy-chain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisy-chain feature only requires a single Slave Select line from the master device.

Figure 21-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

#### 21.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 0100).

When the  $\overline{\text{SSx}}$  pin is low, transmission and reception are enabled and the SDOx pin is driven.

When the  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SSx}$ pin control enabled (SSPxCON1<3:0> = 0100), the SPI module will reset if the $\overline{SSx}$ pin is set to VDD. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | When the SPI is used in Slave mode with CKE set; the user must enable SSx pin control.                                                                               |

| 3:      | While operated in SPI Slave mode the SMP bit of the SSPxSTAT register must remain clear.                                                                             |

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPEN bit.

#### 22.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDxCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPxBRGL register pair. The overflow condition will set the RCIF flag. The counter continues to count until the fifth rising edge is detected on the RX pin. The RCIDL bit will remain false ('0') until the fifth rising edge, at which time, the RCIDL bit will be set. If the RCREG is read after the overflow occurs, but before the fifth rising edge, then the fifth rising edge will set the RCIF again.

Terminating the auto-baud process early to clear an overflow condition will prevent proper detection of the sync character fifth rising edge. If any falling edges of the sync character have not yet occurred when the ABDEN bit is cleared, then those will be falsely detected as start bits. The following steps are recommended to clear the overflow condition:

- 1. Read RCREG to clear RCIF.

- 2. If RCIDL is zero, then wait for RCIF and repeat step 1.

- 3. Clear the ABDOVF bit.

#### 22.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 22-7), and asynchronously if the device is in Sleep mode (Figure 22-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 22.4.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

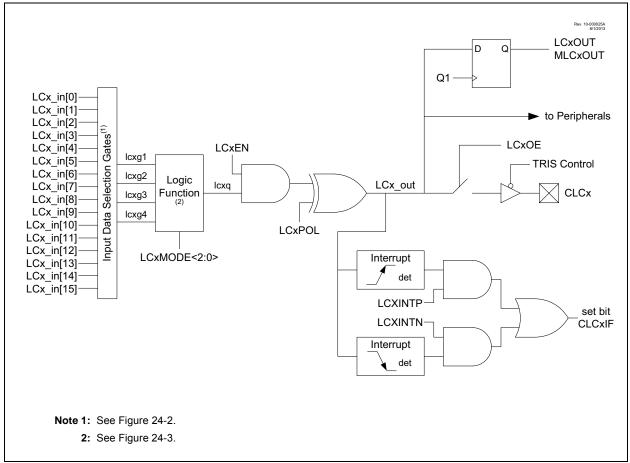

# 24.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 16 input signals, and through the use of configurable gates, reduces the 16 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- · Register bits

The output can be directed internally to peripherals and to an output pin.

Refer to Figure 24-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

#### FIGURE 24-1: CONFIGURABLE LOGIC CELL BLOCK DIAGRAM

| U-0              | R/W-x/u                                | R/W-x/u                               | R/W-x/u      | U-0                       | R/W-x/u          | R/W-x/u                    | R/W-x/u     |  |  |

|------------------|----------------------------------------|---------------------------------------|--------------|---------------------------|------------------|----------------------------|-------------|--|--|

| _                |                                        | LCxD2S<2:0>(1)                        |              | —                         | L                | .CxD1S<2:0> <sup>(1)</sup> |             |  |  |

| bit 7            |                                        |                                       |              | ·                         |                  |                            | bit 0       |  |  |

|                  |                                        |                                       |              |                           |                  |                            |             |  |  |

| Legend:          |                                        |                                       |              |                           |                  |                            |             |  |  |

| R = Readable     | bit                                    | W = Writable b                        | oit          | U = Unimplei              | mented bit, read | 1 as '0'                   |             |  |  |

| u = Bit is unch  | nanged                                 | x = Bit is unkn                       | own          | -n/n = Value              | at POR and BO    | R/Value at all o           | ther Resets |  |  |

| '1' = Bit is set |                                        | '0' = Bit is clea                     | ared         |                           |                  |                            |             |  |  |

|                  |                                        |                                       |              |                           |                  |                            |             |  |  |

| bit 7            | Unimpleme                              | nted: Read as 'o                      | )'           |                           |                  |                            |             |  |  |

| bit 6-4          | LCxD2S<2:                              | 0>: Input Data 2                      | Selection Co | ntrol bits <sup>(1)</sup> |                  |                            |             |  |  |

|                  | 111 = LCx_                             | in[11] is selected                    | l for lcxd2  |                           |                  |                            |             |  |  |

|                  | 110 = LCx_in[10] is selected for lcxd2 |                                       |              |                           |                  |                            |             |  |  |

|                  |                                        | 101 = LCx_in[9] is selected for lcxd2 |              |                           |                  |                            |             |  |  |

|                  |                                        | in[8] is selected                     |              |                           |                  |                            |             |  |  |

|                  |                                        | in[7] is selected                     |              |                           |                  |                            |             |  |  |

|                  |                                        | in[6] is selected                     |              |                           |                  |                            |             |  |  |

|                  |                                        | in[5] is selected                     |              |                           |                  |                            |             |  |  |

|                  | 000 = LCx                              | in[4] is selected                     | for lcxd2    |                           |                  |                            |             |  |  |

| bit 3            | Unimpleme                              | nted: Read as '0                      | )'           |                           |                  |                            |             |  |  |

| bit 2-0          | LCxD1S<2:                              | 0>: Input Data 1                      | Selection Co | ntrol bits <sup>(1)</sup> |                  |                            |             |  |  |

|                  | 111 = LCx_                             | in[7] is selected                     | for lcxd1    |                           |                  |                            |             |  |  |

|                  | 110 = LCx                              | in[6] is selected                     | for lcxd1    |                           |                  |                            |             |  |  |

|                  | 101 = LCx_                             | in[5] is selected                     | for lcxd1    |                           |                  |                            |             |  |  |

|                  |                                        | in[4] is selected                     |              |                           |                  |                            |             |  |  |

|                  | 011 = LCx_                             | in[3] is selected                     | for lcxd1    |                           |                  |                            |             |  |  |

|                  | 010 = LCx_                             | in[2] is selected                     | for lcxd1    |                           |                  |                            |             |  |  |

|                  | 001 = LCx_                             | in[1] is selected                     | for lcxd1    |                           |                  |                            |             |  |  |

|                  | 000 = LCx_                             | in[0] is selected                     | for lcxd1    |                           |                  |                            |             |  |  |

### REGISTER 24-3: CLCxSEL0: MULTIPLEXER DATA 1 AND 2 SELECT REGISTER

**Note 1:** See Table 24-1 for signal names associated with inputs.

# 28.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 28-3 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 28.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

#### TABLE 28-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |

| n     | FSR or INDF number. (0-1)                                                                                                                                                         |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                       |

#### TABLE 28-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-Out bit    |

| С     | Carry bit       |

| DC    | Digit Carry bit |

| Z     | Zero bit        |

| PD    | Power-Down bit  |

# PIC16(L)F1508/9

| CALL             | Call Subroutine                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                   |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                      |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<6:3>) → PC<14:11>                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                      |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle instruc-<br>tion. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                              |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] CLRWDT                                                                                                                    |

| Operands:                      | None                                                                                                                              |

| Operation:<br>Status Affected: | $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow PD$ $\overline{TO, PD}$ |

| Description:                   | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT.<br>Status bits TO and PD are set.  |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                  |

| Operation:       | $\begin{array}{l} (\text{PC}) +1 \rightarrow \text{TOS}, \\ (\text{W}) \rightarrow \text{PC} < 7:0 >, \\ (\text{PCLATH} < 6:0 >) \rightarrow \text{PC} < 14:8 > \end{array}$                                          |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |

| COMF             | Complement f                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                             |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                    |

| Status Affected: | Z                                                                                                                                                             |

| Description:     | The contents of register 'f' are com-<br>plemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                 |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                           |

| Status Affected: | None                                                                                                                                                                              |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is '0', the<br>result is placed in the W register. If 'd'<br>is '1', the result is placed in register 'f'. |

| XORLW            | Exclusive OR literal with W                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of the W register are<br>XOR'ed with the 8-bit<br>literal 'k'. The result is placed in the<br>W register. |

| TRIS             | Load TRIS Register with W                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] TRIS f                                                                                                                                       |

| Operands:        | $5 \le f \le 7$                                                                                                                                      |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |

| Status Affected: | None                                                                                                                                                 |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                              |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

### 31.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 31.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 31.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 31.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

# APPENDIX A: DATA SHEET REVISION HISTORY

# Revision A (10/2011)

Original release.

### Revision B (6/2013)

Updated Electrical Specifications and added Characterization Data.

### Revision C (7/2013)

Corrected upper and lower bit definitions of address, Section 3.2. Added clarification of Buffer Gain Selection bits, Section 13.2. Removed "Preliminary" status from Section 30. Updated Figures 15-1, 29-9. Clarified information in Registers 7-1,13-1, 15-2. Clarified information in Tables 29-5, 29-10, 29-13. Removed Index.

#### **Revision D (10/2014)**

Document re-release.

#### **Revision E (10/2015)**

Added Section 3.2 High-Endurance Flash. Updated Figure 26-1; Registers 4-2, 7-5, and 26-3; Sections 22.4.2, 24.1.5, 26.9.1.2, 26.11.1, and 29.1; and Table 26-2.

# THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support