# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 17                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1509-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R-1/q            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R-q/q                                                | R-0/q             | U-0            | U-0             | R-0/q              | R-0/q      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------|----------------|-----------------|--------------------|------------|

| SOSCR            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OSTS                                                 | HFIOFR            | _              | —               | LFIOFR             | HFIOFS     |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      |                   |                |                 |                    | bit C      |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      |                   |                |                 |                    |            |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      |                   |                |                 |                    |            |

| R = Readable     | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | W = Writable                                         | bit               | U = Unimplem   | ented bit, read | as '0'             |            |

| u = Bit is unc   | hanged                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | x = Bit is unkn                                      | own               | -n/n = Value a | t POR and BOI   | R/Value at all oth | ner Resets |

| '1' = Bit is set | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | '0' = Bit is clea                                    | ared              | q = Conditiona | al              |                    |            |

| bit 7            | <u>If T1OSCEN</u><br>1 = Second<br>0 = Second<br><u>If T1OSCEN</u>                                                                                                                                                                                                                                                                                                                                                                                                       | lary oscillator is r<br>lary oscillator is r         | eady<br>not ready |                |                 |                    |            |

| bit 6            | Unimplemer                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nted: Read as '0                                     | ,                 |                |                 |                    |            |

| bit 5            | <ul> <li>OSTS: Oscillator Start-up Timer Status bit</li> <li>When the FOSC&lt;2:0&gt; bits select HS. XT or LP oscillator:</li> <li>1 = OST has counted 1024 clocks, device is clocked by the FOSC&lt;2:0&gt; bit selection</li> <li>0 = OST is counting, device is clocked from the internal oscillator (INTOSC) selected by the IRCF&lt;3:0&gt; bits.</li> <li>For all other FOSC&lt;2:0&gt; bit selections:</li> <li>See Table 5-2, "OSTS Bit Definition".</li> </ul> |                                                      |                   |                |                 |                    |            |

| bit 4            | 1 = HFINTC                                                                                                                                                                                                                                                                                                                                                                                                                                                               | gh-Frequency Int<br>DSC is ready<br>DSC is not ready | ernal Oscillator  | Ready bit      |                 |                    |            |

| bit 3-2          | Unimplemer                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Unimplemented: Read as '0'                           |                   |                |                 |                    |            |

| bit 1            | LFIOFR: Low-Frequency Internal Oscillator Ready bit<br>1 = LFINTOSC is ready<br>0 = LFINTOSC is not ready                                                                                                                                                                                                                                                                                                                                                                |                                                      |                   |                |                 |                    |            |

| bit 0            | <ul> <li>HFIOFS: High-Frequency Internal Oscillator Stable bit</li> <li>1 = HFINTOSC 16 MHz Oscillator is stable and is driving the INTOSC</li> <li>0 = HFINTOSC 16 MHz is not stable, the Start-up Oscillator is driving INTOSC</li> </ul>                                                                                                                                                                                                                              |                                                      |                   |                |                 |                    |            |

#### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

## PIC16(L)F1508/9

### 6.3 Register Definitions: BOR Control

#### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | R/W-0/u | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|---------|-----|-----|-----|-----|-----|--------|

| SBOREN  | BORFS   | —   | —   | —   | —   | —   | BORRDY |

| bit 7   |         |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <pre>SBOREN: Software Brown-Out Reset Enable bit If BOREN &lt;1:0&gt; in Configuration Words = 01: 1 = BOR Enabled 0 = BOR Disabled If BOREN &lt;1:0&gt; in Configuration Words ≠ 01: SBOREN is read/write, but has no effect on the BOR</pre>                                                                                                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | BORFS: Brown-Out Reset Fast Start bit <sup>(1)</sup><br><u>If BOREN &lt;1:0&gt; = 10 (Disabled in Sleep) or BOREN&lt;1:0&gt; = 01 (Under software control):</u><br>1 = Band gap is forced on always (covers sleep/wake-up/operating cases)<br>0 = Band gap operates normally, and may turn off<br><u>If BOREN&lt;1:0&gt; = 11 (Always on) or BOREN&lt;1:0&gt; = 00 (Always off)</u><br>BORFS is Read/Write, but has no effect. |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 0   | <b>BORRDY:</b> Brown-Out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                                                                                                                                                                                            |

| Note 1: | BOREN<1:0> bits are located in Configuration Words.                                                                                                                                                                                                                                                                                                                                                                            |

#### 6.4 Low-Power Brown-Out Reset (LPBOR)

The Low-Power Brown-out Reset (LPBOR) operates like the BOR to detect low voltage conditions on the VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit (BOR) is changed to indicate that a BOR Reset has occurred. The BOR bit in PCON is used for both BOR and the LPBOR. Refer to Register 6-2.

The LPBOR voltage threshold (Lapboard) has a wider tolerance than the BOR (Vpor), but requires much less current (LPBOR current) to operate. The LPBOR is intended for use when the BOR is configured as disabled (BOREN = 00) or disabled in Sleep mode (BOREN = 10).

Refer to Figure 6-1 to see how the LPBOR interacts with other modules.

#### 6.4.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

#### 6.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2).

#### TABLE 6-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

#### 6.5.1 MCLR ENABLED

When  $\overline{\text{MCLR}}$  is enabled and the pin is held low, the device is held in Reset. The  $\overline{\text{MCLR}}$  pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

#### **Note:** A Reset does not drive the MCLR pin low.

#### 6.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 11.3 "PORTA Registers"** for more information.

#### 6.6 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The TO and PD bits in the STATUS register are changed to indicate the WDT Reset. See **Section 9.0 "Watchdog Timer (WDT)"** for more information.

#### 6.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

#### 6.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 3.5.2 "Overflow/Underflow Reset"** for more information.

#### 6.9 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

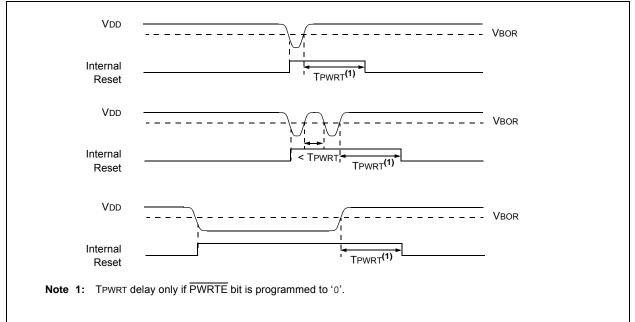

#### 6.10 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\mathsf{PWRTE}}$  bit of Configuration Words.

#### 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)"** for more information.

The Power-up Timer runs independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 Foss cycles (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

| R/W-0/0          | R/W-0/0                                       | R/W-0/0                   | U-0            | R/W-0/0        | R/W-0/0          | U-0              | U-0         |

|------------------|-----------------------------------------------|---------------------------|----------------|----------------|------------------|------------------|-------------|

| OSFIF            | C2IF                                          | C1IF                      | _              | BCL1IF         | NCO1IF           |                  | —           |

| bit 7            |                                               |                           |                |                |                  |                  | bit         |

|                  |                                               |                           |                |                |                  |                  |             |

| Legend:          |                                               |                           |                |                |                  |                  |             |

| R = Readable     | e bit                                         | W = Writable I            | bit            | U = Unimplen   | nented bit, read | as '0'           |             |

| u = Bit is uncl  | hanged                                        | x = Bit is unkn           | iown           | -n/n = Value a | at POR and BOF   | R/Value at all o | ther Resets |

| '1' = Bit is set |                                               | '0' = Bit is clea         | ared           |                |                  |                  |             |

|                  |                                               |                           |                |                |                  |                  |             |

| bit 7            |                                               | illator Fail Interru      | ipt Flag bit   |                |                  |                  |             |

|                  | 1 = Interrupt                                 | is pending is not pending |                |                |                  |                  |             |

| bit 6            | •                                             | arator C2 Interru         | unt Elog hit   |                |                  |                  |             |

|                  | 1 = Interrupt                                 |                           | ipt Flag bit   |                |                  |                  |             |

|                  |                                               | is not pending            |                |                |                  |                  |             |

| bit 5            | •                                             | arator C1 Interru         | pt Flag bit    |                |                  |                  |             |

|                  | 1 = Interrupt                                 |                           |                |                |                  |                  |             |

|                  | 0 = Interrupt                                 | is not pending            |                |                |                  |                  |             |

| bit 4            | Unimplemented: Read as '0'                    |                           |                |                |                  |                  |             |

| bit 3            | BCL1IF: MSSP Bus Collision Interrupt Flag bit |                           |                |                |                  |                  |             |

|                  | 1 = Interrupt                                 |                           |                |                |                  |                  |             |

| <b>h</b> :+ 0    | •                                             | is not pending            |                | n Elea bit     |                  |                  |             |

| bit 2            | 1 = Interrupt                                 | merically Contro          | lied Oscillato | or Flag bit    |                  |                  |             |

|                  |                                               | is not pending            |                |                |                  |                  |             |

| bit 1-0          | -                                             | nted: Read as '           | )'             |                |                  |                  |             |

|                  | -                                             |                           |                |                |                  |                  |             |

| Note: Int        | errupt flag bits                              | are set when an           | interrupt      |                |                  |                  |             |

|                  |                                               | regardless of the         |                |                |                  |                  |             |

|                  |                                               | enable bit or the         |                |                |                  |                  |             |

| Int              | errupt Enable                                 | bit, GIE of the           | INTCON         |                |                  |                  |             |

#### REGISTER 7-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

register. User software should ensure the appropriate interrupt flag bits are clear prior

to enabling an interrupt.

### 9.6 Register Definitions: Watchdog Timer Control

| U-0              | U-0                                                  | R/W-0/0                                                                                      | R/W-1/1                                                                                           | R/W-0/0                   | R/W-1/1          | R/W-1/1          | R/W-0/0      |  |  |

|------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------|------------------|------------------|--------------|--|--|

| _                |                                                      |                                                                                              |                                                                                                   | WDTPS<4:0                 | >                |                  | SWDTEN       |  |  |

| bit 7            |                                                      |                                                                                              |                                                                                                   |                           |                  |                  | bit          |  |  |

|                  |                                                      |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

| Legend:          |                                                      |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

| R = Readable     | e bit                                                | W = Writable                                                                                 | bit                                                                                               | U = Unimpler              | nented bit, read | d as '0'         |              |  |  |

| u = Bit is unc   | hanged                                               | x = Bit is unkr                                                                              | iown                                                                                              | -n/n = Value a            | at POR and BO    | R/Value at all o | other Resets |  |  |

| '1' = Bit is set | t                                                    | '0' = Bit is clea                                                                            | ared                                                                                              |                           |                  |                  |              |  |  |

|                  |                                                      |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

| bit 7-6          | Unimpleme                                            | ented: Read as '                                                                             | o'                                                                                                |                           |                  |                  |              |  |  |

| bit 5-1          | WDTPS<4:                                             | 0>: Watchdog Ti                                                                              | mer Period So                                                                                     | elect bits <sup>(1)</sup> |                  |                  |              |  |  |

|                  |                                                      | Prescale Rate                                                                                |                                                                                                   |                           |                  |                  |              |  |  |

|                  |                                                      | Reserved. Results                                                                            | s in minimum                                                                                      | interval (1:32)           |                  |                  |              |  |  |

|                  | •                                                    |                                                                                              |                                                                                                   | ( )                       |                  |                  |              |  |  |

|                  | •                                                    |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

|                  | •                                                    |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

|                  | 10011 = Reserved. Results in minimum interval (1:32) |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

|                  | 10010 <b>= 1</b>                                     | :8388608 (2 <sup>23</sup> ) (1                                                               | nterval 256s                                                                                      | nominal)                  |                  |                  |              |  |  |

|                  | 10001 = 1                                            | $10001 = 1:4194304 (2^{22}) (Interval 128s nominal)$                                         |                                                                                                   |                           |                  |                  |              |  |  |

|                  | 10000 <b>= 1</b>                                     | 10000 = 1:2097152 (2 <sup>21</sup> ) (Interval 64s nominal)                                  |                                                                                                   |                           |                  |                  |              |  |  |

|                  | 01111 <b>= 1</b>                                     | 01111 = 1:1048576 (2 <sup>20</sup> ) (Interval 32s nominal)                                  |                                                                                                   |                           |                  |                  |              |  |  |

|                  | 01110 = 1                                            | :524288 (2 <sup>19</sup> ) (In                                                               | 524288 (2 <sup>19</sup> ) (Interval 16s nominal)                                                  |                           |                  |                  |              |  |  |

|                  | 01101 = 1                                            | :262144 (2 <sup>10</sup> ) (In<br>:131072 (2 <sup>17</sup> ) (In                             | 262144 (2 <sup>18</sup> ) (Interval 8s nominal)<br>31072 (2 <sup>17</sup> ) (Interval 4s nominal) |                           |                  |                  |              |  |  |

|                  |                                                      |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

|                  |                                                      | 01011 = 1:65536 (Interval 2s nominal) (Reset value)<br>01010 = 1:32768 (Interval 1s nominal) |                                                                                                   |                           |                  |                  |              |  |  |

|                  |                                                      | 01001 = 1.16384 (Interval 512 ms nominal)                                                    |                                                                                                   |                           |                  |                  |              |  |  |

|                  | 01000 = 1                                            | :8192 (Interval 2                                                                            | 56 ms nomina                                                                                      | al)                       |                  |                  |              |  |  |

|                  |                                                      | :4096 (Interval 1                                                                            |                                                                                                   |                           |                  |                  |              |  |  |

|                  |                                                      | :2048 (Interval 6                                                                            |                                                                                                   |                           |                  |                  |              |  |  |

|                  |                                                      | :1024 (Interval 3)                                                                           |                                                                                                   | )                         |                  |                  |              |  |  |

|                  |                                                      | :512 (Interval 16<br>:256 (Interval 8 r                                                      | ,                                                                                                 |                           |                  |                  |              |  |  |

|                  |                                                      | :128 (Interval 4 r                                                                           |                                                                                                   |                           |                  |                  |              |  |  |

|                  |                                                      | :64 (Interval 2 m                                                                            |                                                                                                   |                           |                  |                  |              |  |  |

|                  | 00000 = 1                                            | :32 (Interval 1 m                                                                            | s nominal)                                                                                        |                           |                  |                  |              |  |  |

| bit 0            | SWDTEN:                                              | Software Enable/                                                                             | Disable for W                                                                                     | atchdog Timer             | bit              |                  |              |  |  |

|                  | <u>If WDTE&lt;1:0&gt; = 1x</u> :                     |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

|                  | This bit is ig                                       |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

|                  |                                                      | $\frac{\text{If WDTE}<1:0> = 01}{1 = \text{WDT is turned on}}$                               |                                                                                                   |                           |                  |                  |              |  |  |

|                  | 1 = WDT is<br>0 = WDT is                             |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

|                  | <u>If WDTE&lt;1</u> :                                |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

|                  | This bit is ig                                       |                                                                                              |                                                                                                   |                           |                  |                  |              |  |  |

#### **REGISTER 9-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER**

Note 1: Times are approximate. WDT time is based on 31 kHz LFINTOSC.

#### 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection ( $\overline{CP} = 0$ )<sup>(1)</sup>, disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory, as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

#### 10.1 PMADRL and PMADRH Registers

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

#### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

#### **10.2** Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

| Note: If the user wants to modify only a portion<br>of a previously programmed row, then the<br>contents of the entire row must be read<br>and saved in RAM prior to the erase.<br>Then, new data and retained data can be<br>written into the write latches to reprogram<br>the row of Flash program memory. How-<br>ever, any unprogrammed locations can be<br>written without first erasing the row. In this<br>case, it is not necessary to save and<br>rewrite the other previously programmed<br>locations |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

| TABLE 10-1: | FLASH MEMORY           |

|-------------|------------------------|

|             | ORGANIZATION BY DEVICE |

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |

|---------------|----------------------|-----------------------------|

| PIC16(L)F1508 | 32                   | 32                          |

| PIC16(L)F1509 | 32                   | 52                          |

## PIC16(L)F1508/9

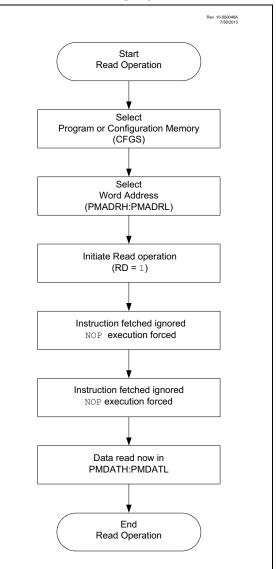

### 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program    |

|-------|---------------------------------------------|

|       | memory read are required to be NOPS.        |

|       | This prevents the user from executing a     |

|       | 2-cycle instruction on the next instruction |

|       | after the RD bit is set.                    |

#### FLASH PROGRAM MEMORY READ FLOWCHART

#### 11.4 Register Definitions: PORTA

| U-0                                   | U-0                                     | R/W-x/x      | R/W-x/x                                               | R-x/x       | R/W-x/x          | R/W-x/x  | R/W-x/x |

|---------------------------------------|-----------------------------------------|--------------|-------------------------------------------------------|-------------|------------------|----------|---------|

| —                                     | —                                       | RA5          | RA4                                                   | RA3         | RA2              | RA1      | RA0     |

| bit 7                                 |                                         |              |                                                       |             |                  |          | bit 0   |

|                                       |                                         |              |                                                       |             |                  |          |         |

| Legend:                               |                                         |              |                                                       |             |                  |          |         |

| R = Readable b                        | bit                                     | W = Writable | bit                                                   | U = Unimple | mented bit, read | l as '0' |         |

| u = Bit is uncha                      | u = Bit is unchanged x = Bit is unknown |              | -n/n = Value at POR and BOR/Value at all other Resets |             |                  |          |         |

| '1' = Bit is set '0' = Bit is cleared |                                         |              |                                                       |             |                  |          |         |

#### REGISTER 11-2: PORTA: PORTA REGISTER

| bit 7-6 | Unimplemented: Read as '0'                   |

|---------|----------------------------------------------|

| bit 5-0 | RA<5:0>: PORTA I/O Value bits <sup>(1)</sup> |

|         | 1 = Port pin is <u>&gt;</u> Vін              |

|         | 0 <b>= Port pin is <u>&lt;</u> Vı∟</b>       |

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 11-3: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     | —   | TRISA5  | TRISA4  | (1) | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>TRISA&lt;5:4&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

| bit 3   | Unimplemented: Read as '1'                                                                                                                         |

|         | •                                                                                                                                                  |

Note 1: Unimplemented, read as '1'.

#### REGISTER 15-4: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | ADRE    | S<9:2>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | mented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 ADRES<9:2>: ADC Result Register bits Upper eight bits of 10-bit conversion result

#### REGISTER 15-5: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | <1:0>   | —       | —       | —       | —       | —       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRES<1:0>: ADC Result Register bits Lower two bits of 10-bit conversion result Reserved: Do not use. bit 5-0

### 17.8 Register Definitions: Comparator Control

| R/W-0/0         | R-0/0                  | R/W-0/0                                 | R/W-0/0          | U-0              | R/W-1/1          | R/W-0/0         | R/W-0/0         |

|-----------------|------------------------|-----------------------------------------|------------------|------------------|------------------|-----------------|-----------------|

| CxON            | CxOUT                  | CxOE                                    | CxPOL            | _                | CxSP             | CxHYS           | CxSYNC          |

| bit 7           | •                      |                                         | 1                |                  |                  | •               | bit 0           |

|                 |                        |                                         |                  |                  |                  |                 |                 |

| Legend:         | . 1.11                 |                                         | 1.11             |                  |                  | 1               |                 |

| R = Readabl     |                        | W = Writable                            |                  | •                | mented bit, read |                 | othor Doooto    |

| u = Bit is unc  | 0                      | x = Bit is unki                         |                  | -n/n = value     | at POR and BC    | rk/value at all | other Resets    |

| '1' = Bit is se | t                      | '0' = Bit is cle                        | areo             |                  |                  |                 |                 |

| bit 7           | CxON: Com              | parator Enable                          | bit              |                  |                  |                 |                 |

|                 |                        | ator is enabled                         |                  |                  |                  |                 |                 |

|                 | 0 = Compara            | ator is disabled                        | and consumes     | s no active pow  | ver              |                 |                 |

| bit 6           | CxOUT: Con             | nparator Output                         | bit              |                  |                  |                 |                 |

|                 |                        | (inverted polar                         | <u>ity):</u>     |                  |                  |                 |                 |

|                 | 1 = CxVP <             |                                         |                  |                  |                  |                 |                 |

|                 | 0 = CxVP >             | (non-inverted)                          | oolarity):       |                  |                  |                 |                 |

|                 | 1 = CxVP >             |                                         | <u>Jolanty).</u> |                  |                  |                 |                 |

|                 | 0 = CxVP <             | CxVN                                    |                  |                  |                  |                 |                 |

| bit 5           | CxOE: Com              | parator Output                          | Enable bit       |                  |                  |                 |                 |

|                 |                        | is present on th                        |                  | Requires that th | he associated T  | RIS bit be clea | red to actually |

|                 |                        | pin. Not affect                         | ed by CxON.      |                  |                  |                 |                 |

|                 |                        | is internal only                        |                  |                  |                  |                 |                 |

| bit 4           |                        | nparator Outpu                          | -                | ct bit           |                  |                 |                 |

|                 |                        | ator output is inv<br>ator output is no |                  |                  |                  |                 |                 |

| bit 3           | •                      |                                         |                  |                  |                  |                 |                 |

|                 | •                      | nted: Read as '                         |                  | :4               |                  |                 |                 |

| bit 2           | -                      | parator Speed/F                         |                  |                  |                  |                 |                 |

|                 | •                      | ator mode in no<br>ator mode in lov     |                  | •                |                  |                 |                 |

| bit 1           | -                      | nparator Hyster                         | -                | -                |                  |                 |                 |

|                 |                        | ator hysteresis                         |                  |                  |                  |                 |                 |

|                 | 0 = Compar             | ator hysteresis                         | disabled         |                  |                  |                 |                 |

| bit 0           | CxSYNC: Co             | omparator Outp                          | ut Synchronou    | us Mode bit      |                  |                 |                 |

|                 |                        | ator output to 1                        |                  |                  |                  | ges on Timer1   | clock source    |

|                 | Output ι<br>0 = Compar | updated on the                          | •••              |                  |                  |                 |                 |

|                 |                        |                                         |                  |                  |                  |                 |                 |

#### REGISTER 17-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

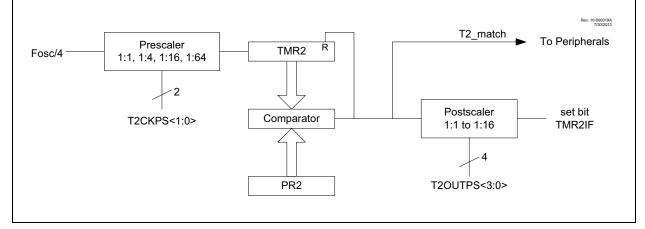

### 20.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match with PR2

See Figure 20-1 for a block diagram of Timer2.

#### FIGURE 20-1: TIMER2 BLOCK DIAGRAM

#### FIGURE 20-2: TIMER2 TIMING DIAGRAM

|                                                        | L                          | Rev. 10.0000304<br>7/30/2013 |

|--------------------------------------------------------|----------------------------|------------------------------|

| Fosc/4                                                 |                            |                              |

| Prescale                                               | 1:4                        |                              |

| PR2                                                    | 0x03                       |                              |

| TMR2 0x00 0x01 0x02                                    | 0x03                       | 0x00 0x01 0x02 X             |

| T2_match                                               | Pulse Width <sup>(1)</sup> |                              |

| <b>Note 1:</b> The Pulse Width of T2_match is equal to | the scaled inpu            | it of TMR2.                  |

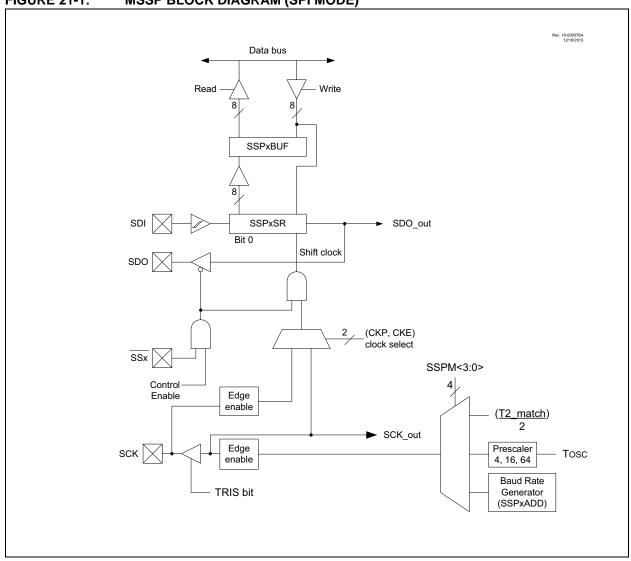

#### 21.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 21.1 MSSP Module Overview

The Master Synchronous Serial Port (MSSPx) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSPx module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- · Clock Parity

- Slave Select Synchronization (Slave mode only)

- Daisy-chain connection of slave devices

Figure 21-1 is a block diagram of the SPI interface module.

#### FIGURE 21-1: MSSP BLOCK DIAGRAM (SPI MODE)

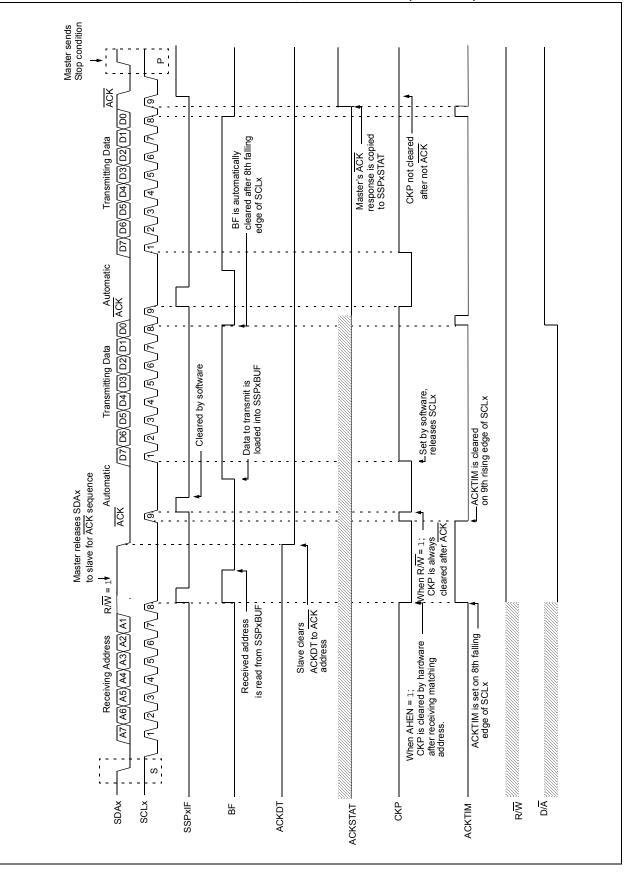

#### 21.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDAx and SCLx, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 21.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCLx line, the device outputting data on the SDAx changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCLx, is provided by the master. Data is valid to change while the SCLx signal is low, and sampled on the rising edge of the clock. Changes on the SDAx line while the SCLx line is high define special conditions on the bus, explained below.

#### 21.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of I<sup>2</sup>C communication that have definitions specific to I<sup>2</sup>C. That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips I<sup>2</sup>C<sup>TM</sup> specification.

#### 21.4.3 SDAX AND SCLX PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCLx and SDAx pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

Note: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

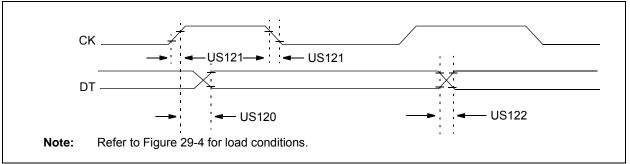

#### 21.4.4 SDAX HOLD TIME

The hold time of the SDAx pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDAx is held valid after the falling edge of SCLx. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

#### TABLE 21-2: I<sup>2</sup>C BUS TERMS

| TABLE 21-2:         | I <sup>2</sup> C BUS TERMS                                                                                                                                                            |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                           |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                        |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                         |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                              |

| Slave               | The device addressed by the master.                                                                                                                                                   |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                     |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                   |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                |

| Idle                | No master is controlling the bus,<br>and both SDAx and SCLx lines are<br>high.                                                                                                        |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                          |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                          |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                   |

| Write Request       | Slave receives a matching address with $R/\overline{W}$ bit clear, and is ready to clock in data.                                                                                     |

| Read Request        | Master sends an address byte with the $R/W$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCLx low to stall communication.                                                                                                                        |

| Bus Collision       | Any time the SDAx line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                           |

## PIC16(L)F1508/9

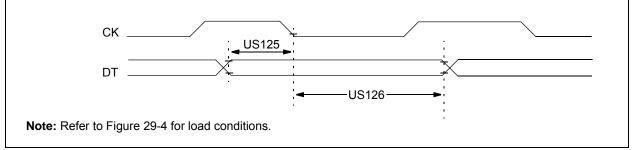

#### 22.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |

|-------|--------------------------------------------|

|       | the corresponding ANSEL bit must be        |

|       | cleared for the receiver to function.      |

#### 22.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

| Note: | If the device is configured as a slave and the TX/CK function is on an analog pin, the |  |  |    |  |  |

|-------|----------------------------------------------------------------------------------------|--|--|----|--|--|

|       | corresponding cleared.                                                                 |  |  | 0. |  |  |

#### 22.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters

will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 22.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

### 22.5.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 26.10 Operation During Sleep

The CWG module operates independently from the system clock and will continue to run during Sleep, provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep, provided that the CWG module is enabled, the input source is active, and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, the CPU will go idle during Sleep, but the CWG will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

#### 26.11 Configuring the CWG

The following steps illustrate how to properly configure the CWG to ensure a synchronous start:

- 1. Ensure that the TRIS control bits corresponding to CWGxA and CWGxB are set so that both are configured as inputs.

- 2. Clear the GxEN bit, if not already cleared.

- 3. Set desired dead-band times with the CWGxDBR and CWGxDBF registers.

- 4. Setup the following controls in CWGxCON2 auto-shutdown register:

- · Select desired shutdown source.

- Select both output overrides to the desired levels (this is necessary even if not using auto-shutdown because start-up will be from a shutdown state).

- Set the GxASE bit and clear the GxARSEN bit.

- 5. Select the desired input source using the CWGxCON1 register.

- 6. Configure the following controls in CWGxCON0 register:

- · Select desired clock source.

- Select the desired output polarities.

- Set the output enables for the outputs to be used.

- 7. Set the GxEN bit.

- Clear TRIS control bits corresponding to CWGxA and CWGxB to be used to configure those pins as outputs.

- If auto-restart is to be used, set the GxARSEN bit and the GxASE bit will be cleared automatically. Otherwise, clear the GxASE bit to start the CWG.

#### 26.11.1 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the GxASDLA and GxASDLB bits of the CWGxCON1 register (Register 26-3). GxASDLA controls the CWG1A override level and GxASDLB controls the CWG1B override level. The control bit logic level corresponds to the output logic drive level while in the shutdown state. The polarity control does not apply to the override level.

#### 26.11.2 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to have resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the GxARSEN bit of the CWGxCON2 register. Waveforms of software controlled and automatic restarts are shown in Figure 26-5 and Figure 26-6.

#### 26.11.2.1 Software Controlled Restart

When the GxARSEN bit of the CWGxCON2 register is cleared, the CWG must be restarted after an auto-shut-down event by software.

Clearing the shutdown state requires all selected shutdown inputs to be low, otherwise the GxASE bit will remain set. The overrides will remain in effect until the first rising edge event after the GxASE bit is cleared. The CWG will then resume operation.

#### 26.11.2.2 Auto-Restart

When the GxARSEN bit of the CWGxCON2 register is set, the CWG will restart from the auto-shutdown state automatically.

The GxASE bit will clear automatically when all shutdown sources go low. The overrides will remain in effect until the first rising edge event after the GxASE bit is cleared. The CWG will then resume operation.

#### TABLE 29-16: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS<sup>(1)</sup>

#### **Operating Conditions (unless otherwise stated)**

| Vdd = 3.0V, T | а = 25°С |