Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

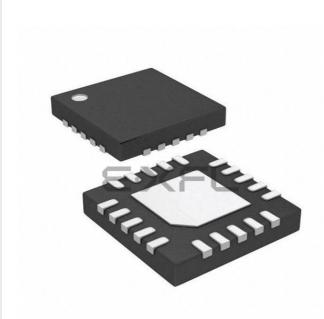

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

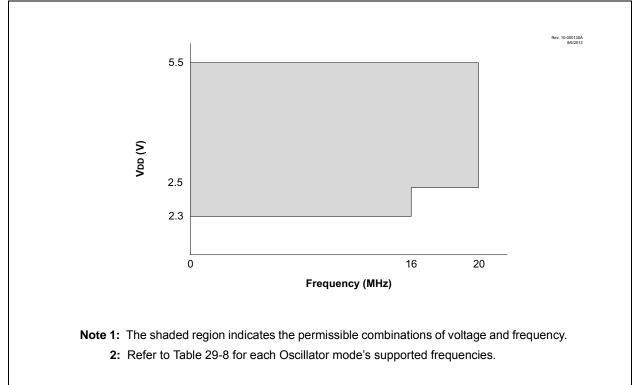

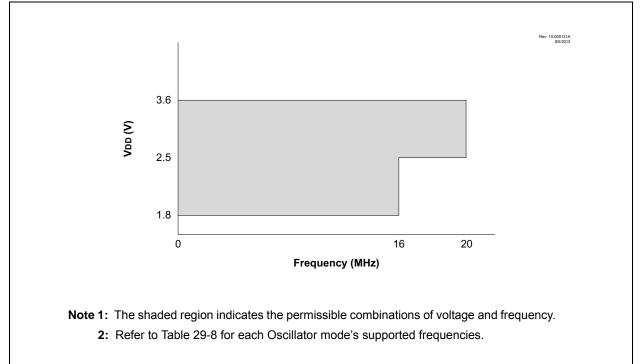

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

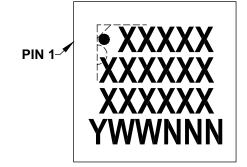

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1509t-i-gz |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

# 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 3.5 "Stack"** for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

# 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 28.0 "Instruction Set Summary**" for more details.

# TABLE 3-6: PIC16(L)F1508/9 MEMORY MAP, BANK 24-31

|      | BANK 24                       |      | BANK 25                       |      | BANK 26                       |      | BANK 27                       |      | BANK 28                       |      | BANK 29                       |      | BANK 30                       |      | BANK 31                       |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| C00h | Core Registers<br>(Table 3-2) | C80h | Core Registers<br>(Table 3-2) | D00h | Core Registers<br>(Table 3-2) | D80h | Core Registers<br>(Table 3-2) | E00h | Core Registers<br>(Table 3-2) | E80h | Core Registers<br>(Table 3-2) | F00h | Core Registers<br>(Table 3-2) | F80h | Core Registers<br>(Table 3-2) |

| C0Bh |                               | C8Bh |                               | D0Bh |                               | D8Bh |                               | E0Bh |                               | E8Bh |                               | F0Bh |                               | F8Bh |                               |

| C0Ch | —                             | C8Ch | _                             | D0Ch | —                             | D8Ch | —                             | E0Ch | _                             | E8Ch | _                             | F0Ch |                               | F8Ch |                               |

| C0Dh | —                             | C8Dh | -                             | D0Dh | —                             | D8Dh | —                             | E0Dh | -                             | E8Dh | _                             | F0Dh |                               | F8Dh |                               |

| C0Eh | —                             | C8Eh | -                             | D0Eh | —                             | D8Eh | —                             | E0Eh | —                             | E8Eh | —                             | F0Eh |                               | F8Eh |                               |

| C0Fh | —                             | C8Fh | _                             | D0Fh | —                             | D8Fh | —                             | E0Fh | —                             | E8Fh | _                             | F0Fh |                               | F8Fh |                               |

| C10h | —                             | C90h | _                             | D10h | —                             | D90h | —                             | E10h | —                             | E90h | _                             | F10h |                               | F90h |                               |

| C11h | —                             | C91h | _                             | D11h | —                             | D91h | —                             | E11h | —                             | E91h | _                             | F11h |                               | F91h |                               |

| C12h | —                             | C92h | _                             | D12h | —                             | D92h | —                             | E12h | _                             | E92h | _                             | F12h |                               | F92h |                               |

| C13h | —                             | C93h | _                             | D13h | —                             | D93h | —                             | E13h | _                             | E93h | _                             | F13h |                               | F93h |                               |

| C14h | _                             | C94h | -                             | D14h | —                             | D94h | —                             | E14h | —                             | E94h | _                             | F14h |                               | F94h |                               |

| C15h | _                             | C95h | -                             | D15h | —                             | D95h | —                             | E15h | —                             | E95h | —                             | F15h |                               | F95h |                               |

| C16h | _                             | C96h | -                             | D16h | —                             | D96h | —                             | E16h | —                             | E96h | —                             | F16h |                               | F96h |                               |

| C17h | _                             | C97h | -                             | D17h | —                             | D97h | —                             | E17h | —                             | E97h | —                             | F17h | See Table 3-7 for             | F97h | See Table 3-7 for             |

| C18h | _                             | C98h | -                             | D18h | —                             | D98h | —                             | E18h | —                             | E98h | —                             | F18h | register mapping              | F98h | register mapping              |

| C19h | _                             | C99h | _                             | D19h | _                             | D99h | _                             | E19h | _                             | E99h | _                             | F19h | details                       | F99h | details                       |

| C1Ah | —                             | C9Ah | _                             | D1Ah | —                             | D9Ah | —                             | E1Ah | _                             | E9Ah | _                             | F1Ah |                               | F9Ah |                               |

| C1Bh | —                             | C9Bh |                               | D1Bh | —                             | D9Bh | —                             | E1Bh | -                             | E9Bh | _                             | F1Bh |                               | F9Bh |                               |

| C1Ch | _                             | C9Ch | -                             | D1Ch | —                             | D9Ch | —                             | E1Ch | —                             | E9Ch | —                             | F1Ch |                               | F9Ch |                               |

| C1Dh | _                             | C9Dh | -                             | D1Dh | —                             | D9Dh | —                             | E1Dh | —                             | E9Dh | —                             | F1Dh |                               | F9Dh |                               |

| C1Eh | —                             | C9Eh | _                             | D1Eh | —                             | D9Eh | —                             | E1Eh | —                             | E9Eh | _                             | F1Eh |                               | F9Eh |                               |

| C1Fh | —                             | C9Fh | _                             | D1Fh | —                             | D9Fh | —                             | E1Fh | _                             | E9Fh | _                             | F1Fh |                               | F9Fh |                               |

| C20h |                               | CA0h |                               | D20h |                               | DA0h |                               | E20h |                               | EA0h |                               | F20h |                               | FA0h |                               |

|      | Unimplemented<br>Read as '0'  |      |                               |      |                               |

| C6Fh |                               | CEFh |                               | D6Fh |                               | DEFh |                               | E6Fh |                               | EEFh |                               | F6Fh |                               | FEFh |                               |

| C70h |                               | CF0h |                               | D70h |                               | DF0h |                               | E70h |                               | EF0h |                               | F70h |                               | FF0h |                               |

| 2.50 | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |

| CFFh |                               | CFFh |                               | D7Fh |                               | DFFh |                               | E7Fh |                               | EFFh |                               | F7Fh |                               | FFFh |                               |

Legend: = Unimplemented data memory locations, read as '0'.

### 6.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

### 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below Vpor for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |  |  |  |  |  |

|------------|--------|-------------|----------|---------------------------------------------------------------------|--|--|--|--|--|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |  |  |  |  |

| 10         | 37     | Awake       | Active   | Waits for BOR ready                                                 |  |  |  |  |  |

| 10         | Х      | Sleep       | Disabled | (BORRDY = 1)                                                        |  |  |  |  |  |

| 01         | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |  |  |  |  |

|            | 0      | Х           | Disabled | Begins immediately                                                  |  |  |  |  |  |

| 00         | Х      | х           | Disabled | (BORRDY = x)                                                        |  |  |  |  |  |

TABLE 6-1:BOR OPERATING MODES

Note 1: In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

## 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold. BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

| R/W-0/0          | R/W-0/0         | R/W-0/0                              | U-0           | R/W-0/0          | R/W-0/0          | U-0              | U-0          |

|------------------|-----------------|--------------------------------------|---------------|------------------|------------------|------------------|--------------|

| OSFIE            | C2IE            | C1IE                                 | —             | BCL1IE           | NCO1IE           | _                | _            |

| bit 7            |                 |                                      |               |                  | 1 1              |                  | bit 0        |

|                  |                 |                                      |               |                  |                  |                  |              |

| Legend:          |                 |                                      |               |                  |                  |                  |              |

| R = Readable     | e bit           | W = Writable                         | bit           | U = Unimpler     | mented bit, read | as '0'           |              |

| u = Bit is unch  | nanged          | x = Bit is unkr                      | nown          | -n/n = Value a   | at POR and BOF   | R/Value at all c | other Resets |

| '1' = Bit is set |                 | '0' = Bit is clea                    | ared          |                  |                  |                  |              |

|                  |                 |                                      |               |                  |                  |                  |              |

| bit 7            |                 | lator Fail Interru                   | •             | t                |                  |                  |              |

|                  |                 | the Oscillator F<br>the Oscillator F |               |                  |                  |                  |              |

| bit 6            |                 | arator C2 Interru                    |               | t                |                  |                  |              |

| bit o            | •               | the Comparato                        | •             |                  |                  |                  |              |

|                  |                 | the Comparate                        | •             |                  |                  |                  |              |

| bit 5            | C1IE: Compa     | arator C1 Interru                    | upt Enable bi | t                |                  |                  |              |

|                  |                 | the Comparato                        |               |                  |                  |                  |              |

|                  |                 | the Comparato                        | •             | ot               |                  |                  |              |

| bit 4            | Unimplemen      | ted: Read as '                       | 0'            |                  |                  |                  |              |

| bit 3            |                 | SP Bus Collisio                      |               |                  |                  |                  |              |

|                  |                 | the MSSP Bus                         |               |                  |                  |                  |              |

| bit 2            |                 | the MSSP Bus                         |               | •                | bla bit          |                  |              |

| DIL 2            |                 | the NCO interr                       |               | or Interrupt Ena |                  |                  |              |

|                  |                 | the NCO interr                       |               |                  |                  |                  |              |

| bit 1-0          |                 | ted: Read as '                       | •             |                  |                  |                  |              |

|                  | -               |                                      |               |                  |                  |                  |              |

| Note: Bit        | PEIE of the IN  | TCON register                        | must he       |                  |                  |                  |              |

|                  | t to enable any | •                                    |               |                  |                  |                  |              |

set to enable any peripheral interrupt.

# 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection ( $\overline{CP} = 0$ )<sup>(1)</sup>, disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory, as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

## 10.1 PMADRL and PMADRH Registers

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

# **10.2** Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

| Note: If the user wants to modify only a portion<br>of a previously programmed row, then the<br>contents of the entire row must be read<br>and saved in RAM prior to the erase.<br>Then, new data and retained data can be<br>written into the write latches to reprogram<br>the row of Flash program memory. How-<br>ever, any unprogrammed locations can be<br>written without first erasing the row. In this<br>case, it is not necessary to save and<br>rewrite the other previously programmed<br>locations |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

| TABLE 10-1: | FLASH MEMORY           |

|-------------|------------------------|

|             | ORGANIZATION BY DEVICE |

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |  |

|---------------|----------------------|-----------------------------|--|

| PIC16(L)F1508 | 32                   | 32                          |  |

| PIC16(L)F1509 | 32                   | 52                          |  |

# 16.6 Register Definitions: DAC Control

### REGISTER 16-1: DACxCON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0          | U-0                                                  | R/W-0/0            | R/W-0/0         | U-0             | R/W-0/0              | U-0                 | U-0   |  |  |  |

|------------------|------------------------------------------------------|--------------------|-----------------|-----------------|----------------------|---------------------|-------|--|--|--|

| DACEN            |                                                      | DACOE1             | DACOE2          | —               | DACPSS               | —                   | _     |  |  |  |

| bit 7            |                                                      |                    |                 |                 |                      |                     | bit C |  |  |  |

|                  |                                                      |                    |                 |                 |                      |                     |       |  |  |  |

| Legend:          |                                                      |                    |                 |                 |                      |                     |       |  |  |  |

| R = Readable b   | pit                                                  | W = Writable b     | it              | U = Unimplem    | ented bit, read as ' | 0'                  |       |  |  |  |

| u = Bit is uncha | inged                                                | x = Bit is unkno   | wn              | -n/n = Value at | POR and BOR/Va       | alue at all other R | esets |  |  |  |

| '1' = Bit is set |                                                      | '0' = Bit is clear | ed              |                 |                      |                     |       |  |  |  |

|                  |                                                      |                    |                 |                 |                      |                     |       |  |  |  |

| bit 7            | DACEN: DAC E                                         | Enable bit         |                 |                 |                      |                     |       |  |  |  |

|                  | 1 = DACx is e                                        |                    |                 |                 |                      |                     |       |  |  |  |

|                  | 0 = DACx is di                                       | isabled            |                 |                 |                      |                     |       |  |  |  |

| bit 6            | Unimplemente                                         | ed: Read as '0'    |                 |                 |                      |                     |       |  |  |  |

| bit 5            | DACOE1: DAC                                          | Voltage Output     | Enable bit      |                 |                      |                     |       |  |  |  |

|                  | 1 = DACx voltage level is output on the DACxOUT1 pin |                    |                 |                 |                      |                     |       |  |  |  |

|                  | 0 = DACx volta                                       | age level is disco | onnected from t | he DACxOUT1 p   | pin                  |                     |       |  |  |  |

| bit 4            |                                                      | Voltage Output     |                 |                 |                      |                     |       |  |  |  |

|                  |                                                      | age level is outp  |                 |                 | - *                  |                     |       |  |  |  |

|                  |                                                      | 0                  | onnected from t | he DACxOUT2 p   | nin                  |                     |       |  |  |  |

| bit 3            | Unimplemente                                         | ed: Read as '0'    |                 |                 |                      |                     |       |  |  |  |

| bit 2            |                                                      | Positive Source    | e Select bit    |                 |                      |                     |       |  |  |  |

|                  | 1 = VREF+ pi                                         | in                 |                 |                 |                      |                     |       |  |  |  |

|                  | 0 = VDD                                              |                    |                 |                 |                      |                     |       |  |  |  |

| bit 1-0          | Unimplemente                                         | ed: Read as '0'    |                 |                 |                      |                     |       |  |  |  |

### REGISTER 16-2: DACxCON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

| _     | _   | _   |         |         | DACR<4:0> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits

### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name     | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Register<br>on page |

|----------|-------|-------|--------|--------|-------|--------|-------|-------|---------------------|

| DAC1CON0 | DACEN | _     | DACOE1 | DACOE2 | _     | DACPSS | _     | —     | 144                 |

| DAC1CON1 | _     | _     | _      |        | 144   |        |       |       |                     |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

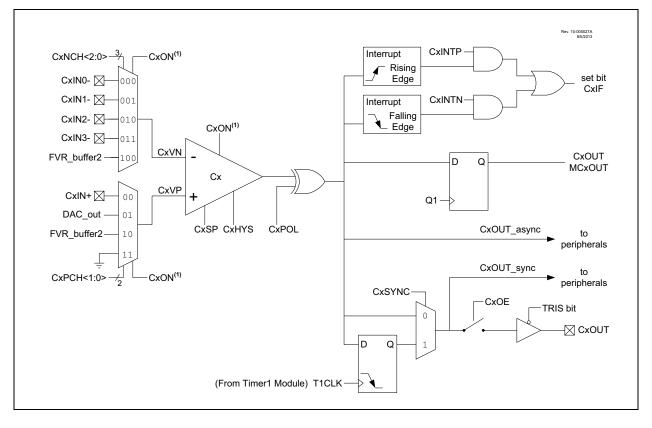

# 17.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- · Programmable input selection

- · Comparator output is available internally/externally

- · Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- Programmable Speed/Power optimization

- PWM shutdown

- Programmable and fixed voltage reference

# 17.1 Comparator Overview

A single comparator is shown in Figure 17-2 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are listed in Table 17-1.

### TABLE 17-1: AVAILABLE COMPARATORS

| Device        | C1 | C2 |

|---------------|----|----|

| PIC16(L)F1508 | •  | •  |

| PIC16(L)F1509 | •  | •  |

## FIGURE 17-1: COMPARATOR MODULE SIMPLIFIED BLOCK DIAGRAM

#### 21.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 21-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts idle.

- Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with  $R/\overline{W}$  bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. Slave loads low address into SSPxADD, releasing SCLx.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSPxIF is set.

**Note:** If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- 13. Master clocks a data byte to the slave and clocks out the slaves ACK on the ninth SCLx pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- 16. Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCLx.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

# 21.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCLx line is held low are the same. Figure 21-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 21-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

### 21.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCLx line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCLx.

The CKP bit of the SSPxCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCLx line to go low and then hold it. Setting CKP will release SCLx and allow more communication.

#### 21.5.6.1 Normal Clock Stretching

Following an  $\overline{ACK}$  if the R/W bit of SSPxSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPxBUF with data to transfer to the master. If the SEN bit of SSPxCON2 is set, the slave hardware will always stretch the clock after the  $\overline{ACK}$  sequence. Once the slave is ready, CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on if the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPxBUF was read before the ninth falling edge of SCLx.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPxBUF was loaded before the ninth falling edge of SCLx. It is now always cleared for read requests.

#### 21.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCLx is stretched without CKP being cleared. SCLx is released immediately after a write to SSPxADD.

| Note: | Previous versions of the module did not      |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|

|       | stretch the clock if the second address byte |  |  |  |  |

|       | did not match.                               |  |  |  |  |

#### 21.5.6.3 Byte NACKing

When the AHEN bit of SSPxCON3 is set; CKP is cleared by hardware after the eighth falling edge of SCLx for a received matching address byte. When the DHEN bit of SSPxCON3 is set, CKP is cleared after the eighth falling edge of SCLx for received data.

Stretching after the eighth falling edge of SCLx allows the slave to look at the received address or data and decide if it wants to ACK the received data.

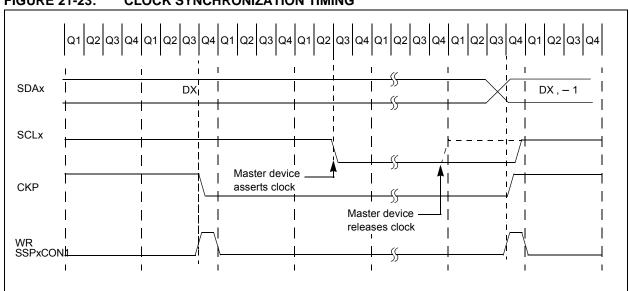

#### 21.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCLx line to go low and then hold it. However, clearing the CKP bit will not assert the SCLx output low until the SCLx output is already sampled low. Therefore, the CKP bit will not assert the SCLx line until an external  $I^2C$  master device has already asserted the SCLx line. The SCLx output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCLx. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCLx (see Figure 21-23).

#### FIGURE 21-23: CLOCK SYNCHRONIZATION TIMING

# 21.8 Register Definitions: MSSP Control

# REGISTER 21-1: SSPxSTAT: SSP STATUS REGISTER

| R/W-0/0                   | R/W-0/0                                                                                                                                                                                   | R-0/0                                                                                                | R-0/0             | R-0/0               | R-0/0                | R-0/0             | R-0/0  |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------|---------------------|----------------------|-------------------|--------|--|--|

| SMP                       | CKE                                                                                                                                                                                       | D/A                                                                                                  | Р                 | S                   | R/W                  | UA                | BF     |  |  |

| bit 7                     |                                                                                                                                                                                           |                                                                                                      |                   |                     |                      |                   | bit 0  |  |  |

|                           |                                                                                                                                                                                           |                                                                                                      |                   |                     |                      |                   |        |  |  |

| Legend:<br>R = Readable b | nit                                                                                                                                                                                       | W = Writable b                                                                                       | it                | II = I Inimplem     | nented bit, read as  | · <b>∩</b> '      |        |  |  |

| u = Bit is uncha          |                                                                                                                                                                                           | x = Bit is unkno                                                                                     |                   | •                   | t POR and BOR/       |                   | Pesets |  |  |

| '1' = Bit is set          | inged                                                                                                                                                                                     | '0' = Bit is clear                                                                                   |                   |                     |                      |                   |        |  |  |

|                           |                                                                                                                                                                                           |                                                                                                      | 00                |                     |                      |                   |        |  |  |

| bit 7                     | SMP: SPI Da                                                                                                                                                                               | ta Input Sample bi                                                                                   | t                 |                     |                      |                   |        |  |  |

|                           | <u>SPI Master m</u>                                                                                                                                                                       |                                                                                                      |                   |                     |                      |                   |        |  |  |

|                           | 0 = Input data                                                                                                                                                                            | a sampled at end o<br>a sampled at midd                                                              |                   |                     |                      |                   |        |  |  |

|                           | _                                                                                                                                                                                         | cleared when SP                                                                                      | l is used in Slav | e mode              |                      |                   |        |  |  |

|                           | 1 = Slew rate                                                                                                                                                                             | or Slave mode:<br>e control disabled<br>e control enabled                                            |                   |                     |                      |                   |        |  |  |

| bit 6                     |                                                                                                                                                                                           | ock Edge Select bi                                                                                   | t (SDI mada an    | <b>V</b> )          |                      |                   |        |  |  |

| bit o                     | In SPI Master                                                                                                                                                                             | or Slave mode:<br>occurs on transitio                                                                |                   | -                   |                      |                   |        |  |  |

|                           |                                                                                                                                                                                           |                                                                                                      |                   |                     |                      |                   |        |  |  |

|                           |                                                                                                                                                                                           | = Transmit occurs on transition from Idle to active clock state<br><u>1<sup>2</sup>C™ mode only:</u> |                   |                     |                      |                   |        |  |  |

|                           | 0 = Disable S                                                                                                                                                                             | put logic so that th<br>MBus specific inp                                                            | uts               | mpliant with SN     | 1Bus specification   |                   |        |  |  |

| bit 5                     |                                                                                                                                                                                           | dress bit (I <sup>2</sup> C mod                                                                      |                   |                     | _                    |                   |        |  |  |

|                           |                                                                                                                                                                                           | that the last byte r<br>that the last byte r                                                         |                   |                     |                      |                   |        |  |  |

| bit 4                     | P: Stop bit                                                                                                                                                                               | -                                                                                                    |                   |                     |                      |                   |        |  |  |

|                           |                                                                                                                                                                                           | ly. This bit is clear                                                                                |                   |                     |                      | s cleared.)       |        |  |  |

|                           |                                                                                                                                                                                           | that a Stop bit has<br>as not detected la                                                            |                   | last (this bit is ' | 0' on Reset)         |                   |        |  |  |

| bit 3                     | S: Start bit                                                                                                                                                                              |                                                                                                      |                   |                     |                      |                   |        |  |  |

|                           | (I <sup>2</sup> C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)<br>1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset) |                                                                                                      |                   |                     |                      |                   |        |  |  |

|                           |                                                                                                                                                                                           | as not detected la                                                                                   |                   |                     | o on Resety          |                   |        |  |  |

| bit 2                     |                                                                                                                                                                                           | rite bit information                                                                                 | •                 |                     |                      |                   |        |  |  |

|                           | This bit holds the $R/W$ bit information following the last address match. This bit is only valid from the address match to the next Start bit, Stop bit, or not ACK bit.                 |                                                                                                      |                   |                     |                      |                   |        |  |  |

|                           | <u>In I<sup>2</sup>C Slave r</u><br>1 = Read                                                                                                                                              | node:                                                                                                |                   |                     |                      |                   |        |  |  |

|                           | 0 = Write                                                                                                                                                                                 |                                                                                                      |                   |                     |                      |                   |        |  |  |

|                           | In I <sup>2</sup> C Master                                                                                                                                                                | <u>mode:</u><br>t is in progress                                                                     |                   |                     |                      |                   |        |  |  |

|                           |                                                                                                                                                                                           | t is not in progress                                                                                 | i                 |                     |                      |                   |        |  |  |

|                           | OR-ing                                                                                                                                                                                    | this bit with SEN, I                                                                                 | RSEN, PEN, RO     | CEN or ACKEN        | will indicate if the | MSSP is in Idle m | node.  |  |  |

| bit 1                     |                                                                                                                                                                                           | ddress bit (10-bit                                                                                   |                   |                     |                      | _                 |        |  |  |

|                           |                                                                                                                                                                                           | that the user need<br>does not need to b                                                             |                   | address in the      | SSPXADD registe      | r                 |        |  |  |

| bit 0                     | BF: Buffer Fu                                                                                                                                                                             |                                                                                                      |                   |                     |                      |                   |        |  |  |

|                           | Receive (SPI                                                                                                                                                                              | and I <sup>2</sup> C modes):                                                                         |                   |                     |                      |                   |        |  |  |

|                           |                                                                                                                                                                                           | complete, SSPxBL                                                                                     |                   |                     |                      |                   |        |  |  |

|                           | 0 = Receive r<br>Transmit (I <sup>2</sup> C                                                                                                                                               | not complete, SSP<br>mode only) <sup>,</sup>                                                         | ABOF IS empty     |                     |                      |                   |        |  |  |

|                           | 1 = Data trans                                                                                                                                                                            | smit in progress (d                                                                                  |                   |                     |                      |                   |        |  |  |

|                           | 0 = Data trans                                                                                                                                                                            | smit complete (doe                                                                                   | es not include th | ne ACK and Sto      | p bits), SSPxBUF     | is empty          |        |  |  |

### 22.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

### 22.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

## 22.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

### 22.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

# 22.3 Register Definitions: EUSART Control

# REGISTER 22-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-/0          | R/W-0/0                    | R/W-0/0                            | R/W-0/0        | R/W-0/0         | R/W-0/0          | R-1/1            | R/W-0/0      |

|-----------------|----------------------------|------------------------------------|----------------|-----------------|------------------|------------------|--------------|

| CSRC            | TX9                        | TXEN <sup>(1)</sup>                | SYNC           | SENDB           | BRGH             | TRMT             | TX9D         |

| oit 7           |                            |                                    |                |                 |                  |                  | bit          |

|                 |                            |                                    |                |                 |                  |                  |              |

| _egend:         |                            |                                    |                |                 |                  |                  |              |

| R = Readable    |                            | W = Writable                       |                | -               | nented bit, read |                  |              |

| u = Bit is uncl | •                          | x = Bit is unki                    |                | -n/n = Value a  | at POR and BOI   | R/Value at all c | other Resets |

| 1' = Bit is set |                            | '0' = Bit is cle                   | ared           |                 |                  |                  |              |

| oit 7           | CSRC: Cloc                 | k Source Select                    | t bit          |                 |                  |                  |              |

|                 | <u>Asynchrono</u>          | <u>us mode</u> :                   |                |                 |                  |                  |              |

|                 | Don't care                 |                                    |                |                 |                  |                  |              |

|                 | Synchronou                 |                                    | norotod inter- |                 | N N              |                  |              |

|                 |                            | mode (clock ge<br>node (clock fron |                |                 | )                |                  |              |

| oit 6           |                            | ransmit Enable I                   |                | ,               |                  |                  |              |

|                 |                            | 9-bit transmiss                    |                |                 |                  |                  |              |

|                 |                            | 8-bit transmiss                    |                |                 |                  |                  |              |

| oit 5           |                            | smit Enable bit <sup>(1</sup>      | 1)             |                 |                  |                  |              |

|                 | 1 = Transmi<br>0 = Transmi |                                    |                |                 |                  |                  |              |

| oit 4           |                            | ART Mode Sele                      | ect bit        |                 |                  |                  |              |

|                 | 1 = Synchro                |                                    |                |                 |                  |                  |              |

|                 | 0 = Asynchi                | ronous mode                        |                |                 |                  |                  |              |

| oit 3           |                            | nd Break Chara                     | cter bit       |                 |                  |                  |              |

|                 | Asynchrono                 |                                    |                |                 |                  |                  |              |

|                 |                            | ync Break on ne<br>eak transmissio |                | n (cleared by I | nardware upon o  | completion)      |              |

|                 | Synchronou                 |                                    | in completed   |                 |                  |                  |              |

|                 | Don't care                 |                                    |                |                 |                  |                  |              |

| oit 2           | BRGH: High                 | n Baud Rate Sel                    | ect bit        |                 |                  |                  |              |

|                 | Asynchrono                 |                                    |                |                 |                  |                  |              |

|                 | 1 = High sp<br>0 = Low spe |                                    |                |                 |                  |                  |              |

|                 | Synchronou                 |                                    |                |                 |                  |                  |              |

|                 | Unused in th               |                                    |                |                 |                  |                  |              |

| oit 1           | TRMT: Trans                | smit Shift Regist                  | ter Status bit |                 |                  |                  |              |

|                 | 1 = TSR em                 |                                    |                |                 |                  |                  |              |

|                 | 0 = TSR full               |                                    | <b>D</b> /     |                 |                  |                  |              |

| oit 0           | TX9D: Ninth<br>Can be addr | bit of Transmit                    |                |                 |                  |                  |              |

|                 |                            | ooo/data hit ar a                  | nority hit     |                 |                  |                  |              |

# 22.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section22.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- · SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 22.5.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

# TABLE 22-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION RECEPTION

| Name    | Bit 7                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                       | RCIDL  |        | SCKP   | BRG16  | —      | WUE    | ABDEN  | 235                 |

| INTCON  | GIE                          | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 75                  |

| PIE1    | TMR1GIE                      | ADIE   | RCIE   | TXIE   | SSP1IE | —      | TMR2IE | TMR1IE | 76                  |

| PIR1    | TMR1GIF                      | ADIF   | RCIF   | TXIF   | SSP1IF | —      | TMR2IF | TMR1IF | 79                  |

| RCREG   | EUSART Receive Data Register |        |        |        |        |        |        | 228*   |                     |

| RCSTA   | SPEN                         | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 234                 |

| TRISB   | TRISB7                       | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 113                 |

| TXSTA   | CSRC                         | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 233                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave reception.

\* Page provides register information.

### REGISTER 25-3: NCOxACCL: NCOx ACCUMULATOR REGISTER – LOW BYTE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | NCOxA   | CC<7:0> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

|         | 1.11    |         |         |         |         |         |         |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| Accumulator, Low Byte |

|-----------------------|

| ŀ                     |

### **REGISTER 25-4:** NCOxACCH: NCOx ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0      | R/W-0/0 | R/W-0/0          | R/W-0/0 | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|--------------|---------|------------------|---------|------------------------------------|---------|---------|---------|

|              |         |                  | NCOxAC  | C<15:8>                            |         |         |         |

| bit 7        |         |                  |         |                                    |         |         | bit 0   |

|              |         |                  |         |                                    |         |         |         |

| Legend:      |         |                  |         |                                    |         |         |         |

| R = Readable | bit     | W = Writable bit |         | U = Unimplemented bit, read as '0' |         |         |         |

|              |         |                  |         |                                    |         |         |         |

### bit 7-0 NCOxACC<15:8>: NCOx Accumulator, High Byte

'0' = Bit is cleared

### REGISTER 25-5: NCOxACCU: NCOx ACCUMULATOR REGISTER – UPPER BYTE

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|----------|---------|

| —     | —   | —   | —   |         | NCOXAC  | C<19:16> |         |

| bit 7 |     |     |     |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCOxACC<19:16>: NCOx Accumulator, Upper Byte

'1' = Bit is set

# 26.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces a complementary waveform with dead-band delay from a selection of input sources.

The CWG module has the following features:

- · Selectable dead-band clock source control

- Selectable input sources

- · Output enable control

- · Output polarity control

- Dead-band control with independent 6-bit rising and falling edge dead-band counters

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control

# 26.1 Fundamental Operation

The CWG generates two output waveforms from the selected input source.

The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time delay immediately where neither output is driven. This is referred to as dead time and is covered in **Section 26.5 "Dead-Band Control"**. A typical operating waveform, with dead band, generated from a single input signal is shown in Figure 26-2.

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in **Section 26.9 "Auto-Shutdown Control"**.

## 26.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the G1CS0 bit of the CWGxCON0 register (Register 26-1).

# 26.3 Selectable Input Sources

The CWG generates the output waveforms from the input sources in Table 26-1.

| TABLE 26-1: | SELECTABLE INPUT |

|-------------|------------------|

|             | SOURCES          |

| Source Peripheral | Signal Name |

|-------------------|-------------|

| Comparator C1     | C1OUT_sync  |

| Comparator C2     | C2OUT_sync  |

| PWM1              | PWM1_out    |

| PWM2              | PWM2_out    |

| PWM3              | PWM3_out    |

| PWM4              | PWM4_out    |

| NCO1              | NCO1_out    |