Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1509t-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| FIGURE 3-7: | ACCESSING THE STA |                | 4                                                                                     |

|-------------|-------------------|----------------|---------------------------------------------------------------------------------------|

|             |                   |                | Rev. 10-00043D<br>7/30/2013                                                           |

|             |                   |                |                                                                                       |

|             |                   |                |                                                                                       |

|             |                   |                | 1                                                                                     |

|             | 0x0F              | Return Address |                                                                                       |

|             | 0x0E              | Return Address |                                                                                       |

|             | 0x0D              | Return Address |                                                                                       |

|             | 0x0C              | Return Address |                                                                                       |

|             | 0x0B              | Return Address |                                                                                       |

|             | 0x0A              | Return Address | When the stack is full, the next CALL or                                              |

|             | 0x09              | Return Address | an interrupt will set the Stack Pointer to 0x10. This is identical to address 0x00 so |

|             | 0x08              | Return Address | the stack will wrap and overwrite the                                                 |

|             | 0x07              | Return Address | return address at 0x00. If the Stack                                                  |

|             | 0x06              | Return Address | Overflow/Underflow Reset is enabled, a<br>Reset will occur and location 0x00 will     |

|             | 0x05              | Return Address | not be overwritten.                                                                   |

|             | 0x04              | Return Address |                                                                                       |

|             | 0x03              | Return Address |                                                                                       |

|             | 0x02              | Return Address | _                                                                                     |

|             | 0x01              | Return Address |                                                                                       |

| TOSH        | H:TOSL 0x00       | Return Address | STKPTR = 0x10                                                                         |

| 103         |                   |                |                                                                                       |

|             |                   |                |                                                                                       |

|             |                   |                |                                                                                       |

### 3.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

### 3.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

## 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Internal access to the program memory is unaffected by any code protection setting.

### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4 "Write Protection"** for more information.

## 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

## 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC12(L)F1501/PIC16(L)F150X Memory Programming Specification*" (DS41573).

## 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

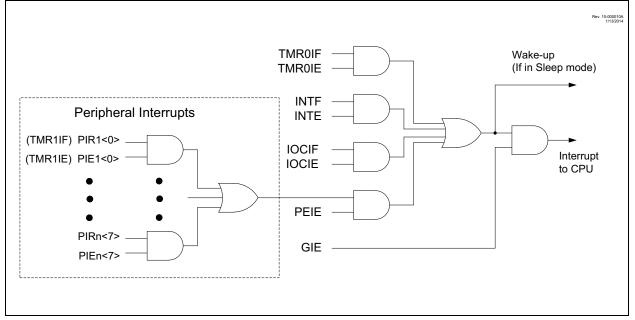

A block diagram of the interrupt logic is shown in Figure 7-1.

| R/W-0/0          | R/W-0/0         | R/W-0/0                              | U-0           | R/W-0/0          | R/W-0/0          | U-0              | U-0          |

|------------------|-----------------|--------------------------------------|---------------|------------------|------------------|------------------|--------------|

| OSFIE            | C2IE            | C1IE                                 | —             | BCL1IE           | NCO1IE           | _                | _            |

| bit 7            |                 |                                      |               |                  | 1 1              |                  | bit 0        |

|                  |                 |                                      |               |                  |                  |                  |              |

| Legend:          |                 |                                      |               |                  |                  |                  |              |

| R = Readable     | e bit           | W = Writable                         | bit           | U = Unimpler     | mented bit, read | as '0'           |              |

| u = Bit is unch  | nanged          | x = Bit is unkr                      | nown          | -n/n = Value a   | at POR and BOF   | R/Value at all c | other Resets |

| '1' = Bit is set |                 | '0' = Bit is clea                    | ared          |                  |                  |                  |              |

|                  |                 |                                      |               |                  |                  |                  |              |

| bit 7            |                 | lator Fail Interru                   | •             | t                |                  |                  |              |

|                  |                 | the Oscillator F<br>the Oscillator F |               |                  |                  |                  |              |

| bit 6            |                 | arator C2 Interru                    |               | t                |                  |                  |              |

| bit o            | •               | the Comparato                        | •             |                  |                  |                  |              |

|                  |                 | the Comparate                        | •             |                  |                  |                  |              |

| bit 5            | C1IE: Compa     | arator C1 Interru                    | upt Enable bi | t                |                  |                  |              |

|                  |                 | the Comparato                        |               |                  |                  |                  |              |

|                  |                 | the Comparato                        | •             | ot               |                  |                  |              |

| bit 4            | Unimplemen      | ted: Read as '                       | 0'            |                  |                  |                  |              |

| bit 3            |                 | SP Bus Collisio                      |               |                  |                  |                  |              |

|                  |                 | the MSSP Bus                         |               |                  |                  |                  |              |

| bit 2            |                 | the MSSP Bus                         |               | •                | bla bit          |                  |              |

| DIL 2            |                 | the NCO interr                       |               | or Interrupt Ena |                  |                  |              |

|                  |                 | the NCO interr                       |               |                  |                  |                  |              |

| bit 1-0          |                 | ted: Read as '                       | •             |                  |                  |                  |              |

|                  | -               |                                      |               |                  |                  |                  |              |

| Note: Bit        | PEIE of the IN  | TCON register                        | must he       |                  |                  |                  |              |

|                  | t to enable any | •                                    |               |                  |                  |                  |              |

set to enable any peripheral interrupt.

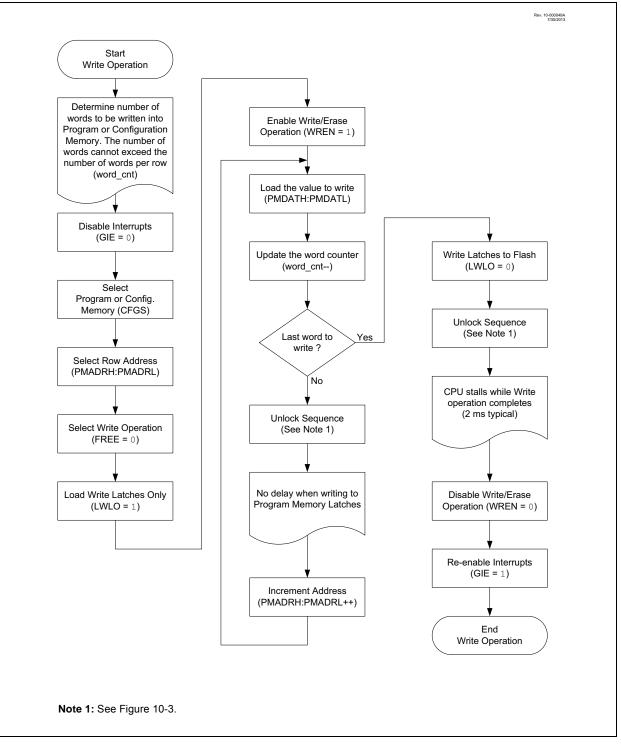

#### FIGURE 10-6: FLASH MEMORY WRITE FLOWCHART

-n/n = Value at POR and BOR/Value at all other Resets

| U-0            | U-0 | R/W-1/1      | R/W-1/1 | R/W-1/1      | R/W-1/1          | R/W-1/1 | R/W-1/1 |

|----------------|-----|--------------|---------|--------------|------------------|---------|---------|

| _              |     | WPUA5        | WPUA4   | WPUA3        | WPUA2            | WPUA1   | WPUA0   |

| bit 7          |     |              |         |              |                  |         | bit 0   |

|                |     |              |         |              |                  |         |         |

| Legend:        |     |              |         |              |                  |         |         |

| R = Readable b | it  | W = Writable | bit     | U = Unimpler | mented bit, read | as '0'  |         |

| REGISTER 11-6: | WPUA: WEAK PULL-UP PORTA REGISTER |

|----------------|-----------------------------------|

|                |                                   |

x = Bit is unknown

'0' = Bit is cleared

| bit 7-6 | Unimplemented: Read as '0'                           |

|---------|------------------------------------------------------|

| bit 5-0 | WPUA<5:0>: Weak Pull-up Register bits <sup>(3)</sup> |

|         | 1 = Pull-up enabled                                  |

|         | 0 = Pull-up disabled                                 |

u = Bit is unchanged

'1' = Bit is set

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is configured as an output.

- **3:** For the WPUA3 bit, when MCLRE = 1, weak pull-up is internally enabled, but not reported here.

| Name       | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|------------|-------|--------|--------|--------|--------|--------|---------|---------|---------------------|

| ANSELA     | _     | _      | _      | ANSA4  | _      | ANSA2  | ANSA1   | ANSA0   | 110                 |

| APFCON     | _     | -      | -      | SSSEL  | T1GSEL | _      | CLC1SEL | NCO1SEL | 107                 |

| LATA       | _     | _      | LATA5  | LATA4  | _      | LATA2  | LATA1   | LATA0   | 110                 |

| OPTION_REG | WPUEN | INTEDG | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |         | 154                 |

| PORTA      | _     | _      | RA5    | RA4    | RA3    | RA2    | RA1     | RA0     | 109                 |

| TRISA      | _     | _      | TRISA5 | TRISA4 | _(1)   | TRISA2 | TRISA1  | TRISA0  | 109                 |

| WPUA       | _     | _      | WPUA5  | WPUA4  | WPUA3  | WPUA2  | WPUA1   | WPUA0   | 111                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA. **Note 1:** Unimplemented, read as '1'.

TABLE 11-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|----------|-----------|---------|---------------------|

| 0015104 | 13:8 |         | 1       | FCMEN    | IESO      | CLKOUTEN | BOREI    | N<1:0>    | —       | 44                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          |          | FOSC<2:0> |         | 41                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

| IGURE 19-5:            | TIMERT GATE SINGLE-PULSE MC              |                                                               |

|------------------------|------------------------------------------|---------------------------------------------------------------|

| TMR1GE                 |                                          |                                                               |

| T1GPOL                 |                                          |                                                               |

| T1GSPM                 |                                          |                                                               |

| T1GG <u>O/</u><br>DONE | ← Set by software<br>Counting enabled on | Cleared by hardware on falling edge of T1GVAL                 |

| t1g_in                 | rising edge of T1G                       |                                                               |

| T1CKI                  |                                          |                                                               |

| T1GVAL                 |                                          |                                                               |

| Timer1                 | N N + 1                                  | N + 2                                                         |

| TMR1GIF                | Cleared by software                      | <ul> <li>Set by hardware on falling edge of T1GVAL</li> </ul> |

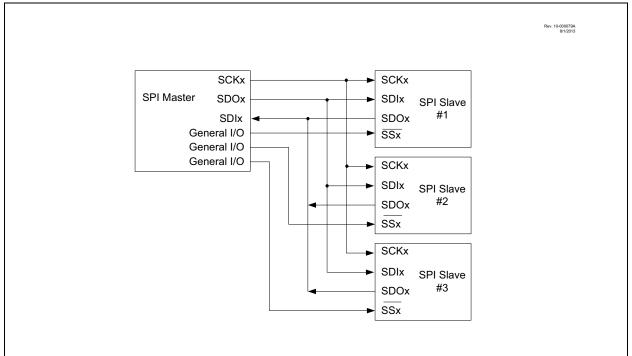

FIGURE 21-4: SPI MASTER AND MULTIPLE SLAVE CONNECTION

#### 21.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPxSTAT)

- MSSP Control Register 1 (SSPxCON1)

- MSSP Control Register 3 (SSPxCON3)

- MSSP Data Buffer register (SSPxBUF)

- MSSP Address register (SSPxADD)

- MSSP Shift register (SSPxSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and STATUS registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section21.7 "Baud Rate Generator**".

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

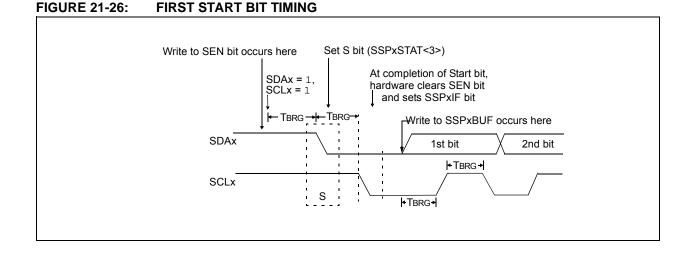

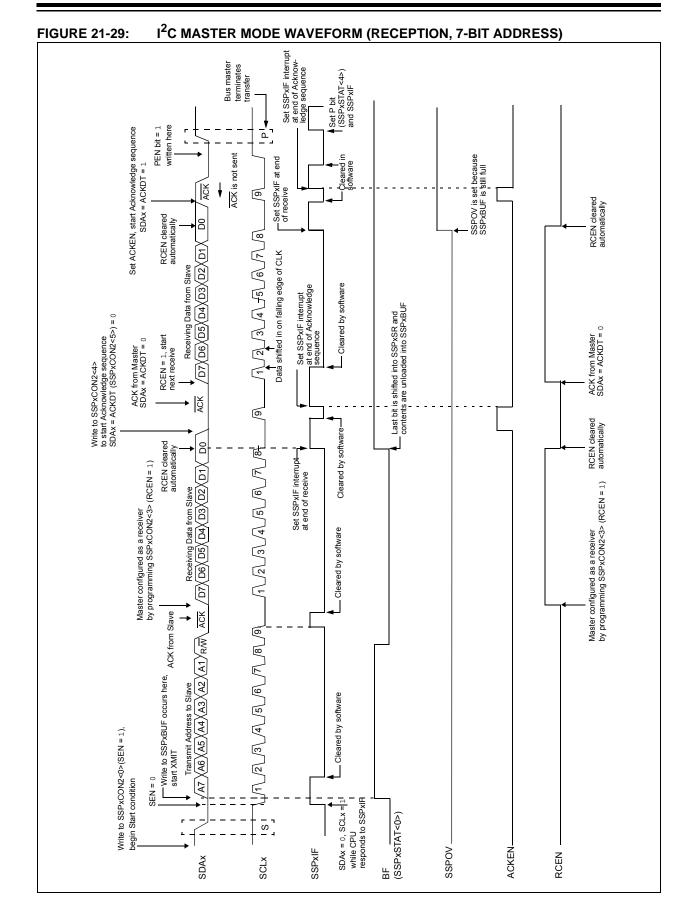

#### 21.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 21-26), the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit of the SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SDAx bit of the SSPxSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared

by hardware; the Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- 2: The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

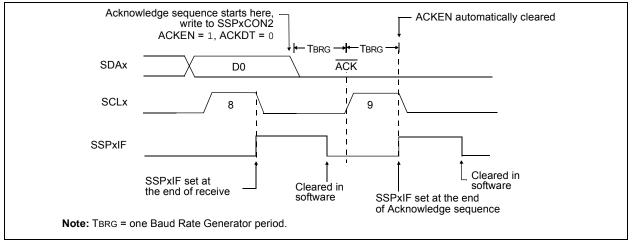

#### 21.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 21-30).

#### 21.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

## 21.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 21-31).

## 21.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### FIGURE 21-30: ACKNOWLEDGE SEQUENCE WAVEFORM

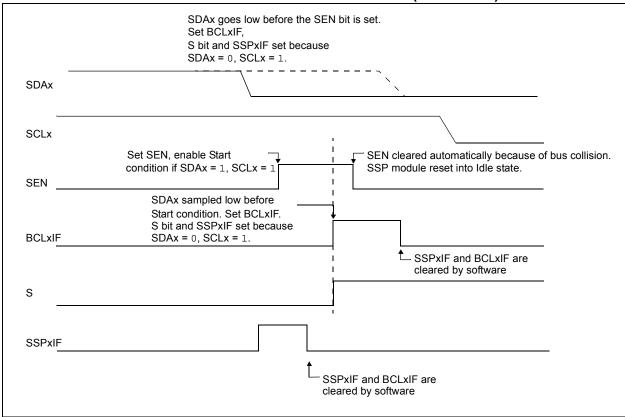

#### 21.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 21-33).

- b) SCL is sampled low before SDAx is asserted low (Figure 21-34).

During a Start condition, both the SDAx and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- · the BCL1IF flag is set and

- the MSSP module is reset to its Idle state (Figure 21-33).

The Start condition begins with the SDAx and SCLx pins deasserted. When the SDAx pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCLx pin is sampled low while SDAx is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDAx pin is sampled low during this count, the BRG is reset and the SDAx line is asserted early (Figure 21-35). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDAx before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

### FIGURE 21-33: BUS COLLISION DURING START CONDITION (SDAX ONLY)

#### 22.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 22-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 22.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

Note: If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

### 22.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section22.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional<br>characters will be received until the overrun |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | condition is cleared. See                                                                      |  |  |  |  |  |  |

|       | Section22.1.2.5 "Receive Overrun                                                               |  |  |  |  |  |  |

|       | Error" for more information on overrun                                                         |  |  |  |  |  |  |

|       | errors.                                                                                        |  |  |  |  |  |  |

#### 22.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- · RCIE, Interrupt Enable bit of the PIE1 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 24.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 24-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

TABLE 24-2: DATA GATING LOGIC

| CLCxGLS0 | LCxG1POL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 24-5)

- Gate 2: CLCxGLS1 (Register 24-6)

- Gate 3: CLCxGLS2 (Register 24-7)

- Gate 4: CLCxGLS3 (Register 24-8)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 24-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

### 24.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 24-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

### 24.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

| BCF              | Bit Clear f                                                         |  |

|------------------|---------------------------------------------------------------------|--|

| Syntax:          | [label]BCF f,b                                                      |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |  |

| Status Affected: | None                                                                |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                         |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                               |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                               |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                           |  |

| Status Affected: | None                                                                                                                                                                                                              |  |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |  |

| BRA              | Relative Branch                                                                                                                                                                                                               |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ]BRA label<br>[ <i>label</i> ]BRA \$+k                                                                                                                                                                         |  |  |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255 -256 $\leq$ k $\leq$ 255                                                                                                                                                                |  |  |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 |  |  |

| Status Affected: | None                                                                                                                                                                                                                          |  |  |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |  |  |

| BRW              | Relative Branch with W                                                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BRW                                                                                                                                                                                                     |

| Operands:        | None                                                                                                                                                                                                              |

| Operation:       | $(PC) + (W) \rightarrow PC$                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have incre-<br>mented to fetch the next instruction,<br>the new address will be PC + 1 + (W).<br>This instruction is a 2-cycle instruc-<br>tion. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BSF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

## DS40001609E-page 340

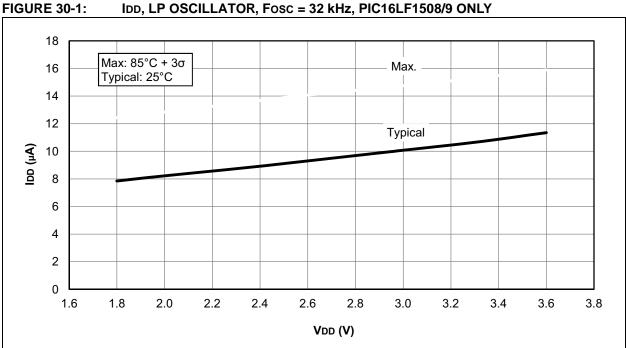

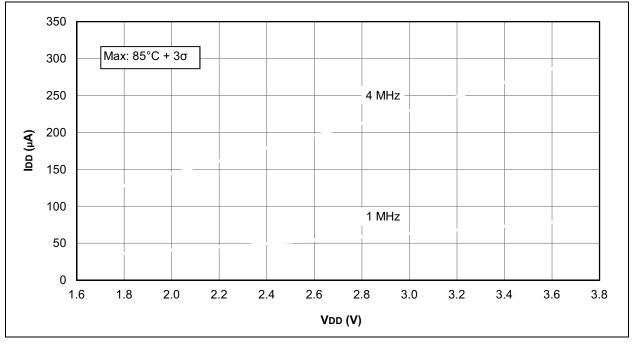

FIGURE 30-11: IDD TYPICAL, EXTERNAL CLOCK (ECM), MEDIUM POWER MODE, PIC16LF1508/9 ONLY

FIGURE 30-12: IDD MAXIMUM, EXTERNAL CLOCK (ECM), MEDIUM POWER MODE, PIC16LF1508/9 ONLY

### 31.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 31.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 31.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 31.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

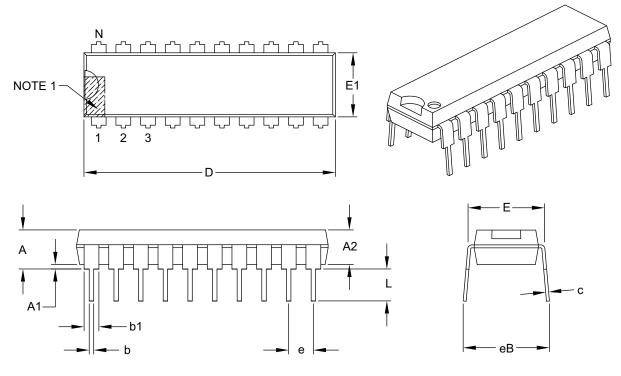

### 32.2 Package Details

The following sections give the technical details of the packages.

## 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |          | INCHES   |       |       |

|----------------------------|----------|----------|-------|-------|

| Dimensio                   | n Limits | MIN      | NOM   | MAX   |

| Number of Pins             | N        | 20       |       |       |

| Pitch                      | е        | .100 BSC |       |       |

| Top to Seating Plane       | А        | -        | -     | .210  |

| Molded Package Thickness   | A2       | .115     | .130  | .195  |

| Base to Seating Plane      | A1       | .015     | -     | _     |

| Shoulder to Shoulder Width | E        | .300     | .310  | .325  |

| Molded Package Width       | E1       | .240     | .250  | .280  |

| Overall Length             | D        | .980     | 1.030 | 1.060 |

| Tip to Seating Plane       | L        | .115     | .130  | .150  |

| Lead Thickness             | с        | .008     | .010  | .015  |

| Upper Lead Width           | b1       | .045     | .060  | .070  |

| Lower Lead Width           | b        | .014     | .018  | .022  |

| Overall Row Spacing §      | eB       | -        | -     | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B