Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1508-e-gz |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.2 Clock Source Types

Clock sources can be classified as external, internal or peripheral.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL modes), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (EXTRC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate the internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The peripheral clock source is a nominal 600 kHz internal RC oscillator, FRC. The FRC is traditionally used with the ADC module, but is sometimes available to other peripherals. See **Section 5.2.2.4** "**Peripheral Clock Sources**".

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching**" for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 5.3 "Clock Switching**" for more information.

#### 5.2.1.1 EC Mode

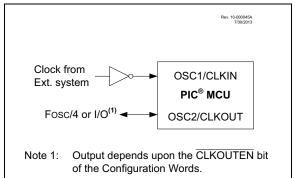

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through the Fosc bits in the Configuration Words:

- ECH High-power, 4-20 MHz

- ECM Medium-power, 0.5-4 MHz

- ECL Low-power, 0-0.5 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

### 5.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 5-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 5-3 and Figure 5-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

# 5.3.5 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PPLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

# 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT, or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

**Note:** Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCSTAT register to remain clear.

### 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator or external clock fail. If an oscillator mode is selected, the FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. When an external clock mode is selected, the FSCM can detect failure as soon as the device is released from Reset.

FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to external oscillator modes (LP, XT, HS) and external clock modes (ECH, ECM, ECL, EXTRC) and the Secondary Oscillator (SOSC).

#### 5.5.1 FAIL-SAFE DETECTION

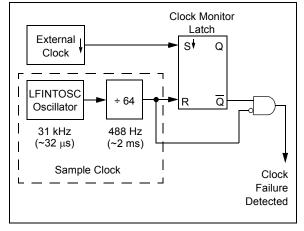

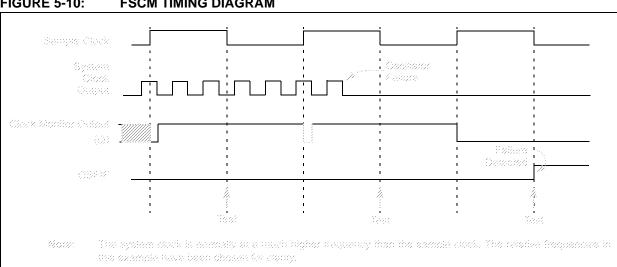

The FSCM module detects a failed oscillator by monitoring falling clock edges and using LFINTOSC as a time base. See Figure 5-9. Detection of a failed oscillator will take 32 to 96 cycles of the LFINTOSC. Figure 5-10 shows a timing diagram of the FSCM module.

#### 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the CPU clock to an internal clock source and sets the OSFIF bit of the PIR2 register. The internal clock source is determined by the IRCF<3:0> bits in the OSCCON register.

When the OSFIF bit is set, an interrupt will be generated, if the OSFIE bit in the PIE2 register is enabled. The user's firmware in the Interrupt Service Routine (ISR) can then take steps to mitigate the problems that may arise from the failed clock.

The system clock will continue to be sourced from the internal clock source until the fail-safe condition has been cleared, see Section 5.5.3 "Fail-Safe Condition Clearing".

#### 5.5.3 FAIL-SAFE CONDITION CLEARING

When a Fail-Safe condition exists, the user must take the following actions to clear the condition before returning to normal operation with the external source.

The next sections describe how to clear the Fail-Safe condition for specific clock selections (FOSC bits) and clock switching modes (SCS bit settings).

When a Fail-Safe condition occurs with the FOSC bits selecting external oscillator (FOSC<2:0> = HS, XT, LP) and the clock switch has been selected to run from the FOSC selection (SCS<1:0> = 00), the condition is cleared by performing the following procedure.

#### When SCS<1:0> = 00 (Running from FOSC selection)

#### SCS<1:0> = 1x:

Change the SCS bits in the OSCCON register to select the internal oscillator block. This resets the OST timer and allows it to operate again.

OSFIF = 0:

Clear the OSFIF bit in the PIR2 register.

SCS<1:0> = 00:

Change the SCS bits in the OSCCON register to select the FOSC Configuration Word clock selection. This will start the OST. The CPU will continue to operate from the internal oscillator until the OST count is reached. When OST expires, the clock module will switch to the external oscillator and the Fail-Safe condition will be cleared.

If the Fail-Safe condition still exists, the OSFIF bit will again be set by hardware.

#### 5.5.3.2 External Clock with SCS<1:0> = 00

When a Fail-Safe condition occurs with the FOSC bits selecting external clock (FOSC<2:0> = ECH, ECM, ECL, EXTRC) and the clock switch has selected to run from the FOSC selection (SCS<1:0> = 00), the condition is cleared by performing the following procedure.

When SCS<1:0> = 00 (Running from FOSC selection)

#### SCS<1:0> = 1x:

Change the SCS bits in the OSCCON register to select the internal oscillator block. This resets the OST timer and allows it to operate again.

OSFIF = 0:

Clear the OSFIF bit in the PIR2 register.

#### SCS<1:0> = 00:

Change the SCS bits in the OSCCON register to select the FOSC Configuration Word clock selection. Since the OST is not applicable with external clocks, the clock module will immediately switch to the external clock, and the fail-safe condition will be cleared.

If the Fail-Safe condition still exists, the OSFIF bit will again be set by hardware.

#### 5.5.3.3 Secondary Oscillator with SCS<1:0> = 01

When a Fail-Safe condition occurs with the clock switch selected to run from the Secondary Oscillator selection (SCS < 1:0 > = 01), regardless of the FOSC selection, the condition is cleared by performing the following procedure.

#### SCS<1:0> = 01 (Secondary Oscillator)

SCS<1:0> = 1x:

Change the SCS bits in the OSCCON register to select the internal oscillator block.

OSFIF = 0:

Clear the OSFIF bit in the PIR2 register.

Read SOSCR:

The OST is not used with the secondary oscillator, therefore, the user must determine if the secondary oscillator is ready by monitoring the SOSCR bit in the OSCSTAT register. When the SOSCR bit is set, the secondary oscillator is ready.

#### **FIGURE 5-10:** FSCM TIMING DIAGRAM

SCS<1:0> = 01:

Change the SCS bits in the OSCCON register to select the secondary oscillator. The clock module will immediately switch to the secondary oscillator and the fail-safe condition will be cleared.

If the Fail-Safe condition still exists, the OSFIF bit will again be set by hardware.

#### RESET OR WAKE-UP FROM SLEEP 5.5.4

The FSCM is designed to detect external oscillator or external clock failures.

When FSCM is used with an external oscillator, the Oscillator Start-up Timer (OST) count must expire before the FSCM becomes active. The OST is used after waking up from Sleep and after any type of Reset.

When the FSCM is used with external clocks, the OST is not used and the FSCM will be active as soon as the Reset or wake-up has completed.

When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Due to the wide range of oscillator start-up Note: times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep).

#### 15.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| The ADIF bit is set at the completion of |

|------------------------------------------|

| every conversion, regardless of whether  |

| or not the ADC interrupt is enabled.     |

|                                          |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

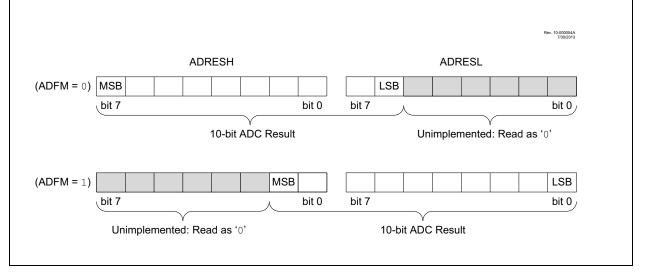

#### 15.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 15-3 shows the two output formats.

# FIGURE 15-3: 10-BIT ADC CONVERSION RESULT FORMAT

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u       | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------------|---------|-------------------|---------------|-------------------------------------------------------|---------|---------|---------|--|

| —                | —       | —                 | — — — ADRES<9 |                                                       | S<9:8>  |         |         |  |

| bit 7            |         |                   |               |                                                       |         |         | bit 0   |  |

|                  |         |                   |               |                                                       |         |         |         |  |

| Legend:          |         |                   |               |                                                       |         |         |         |  |

| R = Readable     | bit     | W = Writable      | bit           | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is uncha | anged   | x = Bit is unkr   | iown          | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set |         | '0' = Bit is clea | ared          |                                                       |         |         |         |  |

|                  |         |                   |               |                                                       |         |         |         |  |

#### REGISTER 15-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

bit 7-2 **Reserved**: Do not use.

| bit 1-0 | ADRES<9:8>: ADC Result Register bits       |

|---------|--------------------------------------------|

|         | Upper two bits of 10-bit conversion result |

# REGISTER 15-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |  |

|---------|------------|---------|---------|---------|---------|---------|---------|--|--|--|--|

|         | ADRES<7:0> |         |         |         |         |         |         |  |  |  |  |

| bit 7   | bit 7      |         |         |         |         |         |         |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

# PIC16(L)F1508/9

# TIMER1 GATE SINGLE-PULSE AND TOGGLE COMBINED MODE **FIGURE 19-6:** TMR1GE T1GPOL T1GSPM T1GTM Cleared by hardware on T1GGO/ Set by software falling edge of T1GVAL DONE Counting enabled on rising edge of T1G t1g\_in T1CKI T1GVAL Timer1 N + 1 N + 2) N + 3 N + 4 Ν Cleared by software Set by hardware on Cleared by software falling edge of T1GVAL TMR1GIF

The  $I^2C$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- Clock stretching

- Bus collision detection

- General call address matching

- Address masking

- · Address Hold and Data Hold modes

- · Selectable SDAx hold times

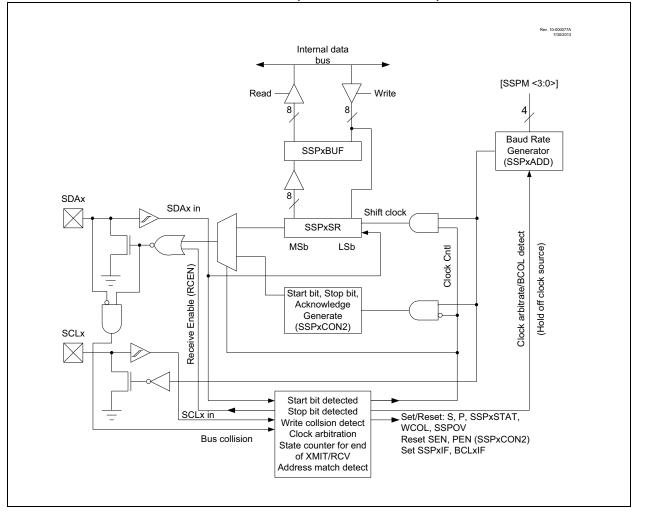

Figure 21-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 21-3 is a diagram of the  $I^2C$  interface module in Slave mode.

Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSPxCON1 and SSPxCON2 registers control different operational aspects of the same module, while SSPxCON1 and SSP2CON1 control the same features for two different modules.

2: Throughout this section, generic references to an MSSPx module in any of its operating modes may be interpreted as being equally applicable to MSSPx or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

### FIGURE 21-2: MSSPX BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

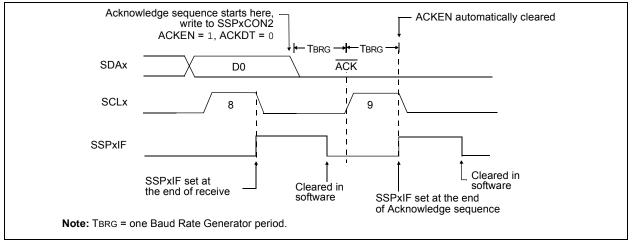

#### 21.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 21-30).

#### 21.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

## 21.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 21-31).

# 21.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### FIGURE 21-30: ACKNOWLEDGE SEQUENCE WAVEFORM

# 22.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section22.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- · SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 22.5.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

# TABLE 22-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION RECEPTION

| Name    | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|---------|--------|--------|------------|------------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF  | RCIDL  | _      | SCKP       | BRG16      | _      | WUE    | ABDEN  | 235                 |

| INTCON  | GIE     | PEIE   | TMR0IE | INTE       | IOCIE      | TMR0IF | INTF   | IOCIF  | 75                  |

| PIE1    | TMR1GIE | ADIE   | RCIE   | TXIE       | SSP1IE     | _      | TMR2IE | TMR1IE | 76                  |

| PIR1    | TMR1GIF | ADIF   | RCIF   | TXIF       | SSP1IF     | _      | TMR2IF | TMR1IF | 79                  |

| RCREG   |         |        | EUS    | ART Receiv | e Data Reg | jister |        |        | 228*                |

| RCSTA   | SPEN    | RX9    | SREN   | CREN       | ADDEN      | FERR   | OERR   | RX9D   | 234                 |

| TRISB   | TRISB7  | TRISB6 | TRISB5 | TRISB4     | TRISB3     | TRISB2 | TRISB1 | TRISB0 | 113                 |

| TXSTA   | CSRC    | TX9    | TXEN   | SYNC       | SENDB      | BRGH   | TRMT   | TX9D   | 233                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave reception.

\* Page provides register information.

#### REGISTER 23-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u           | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u         | R/W-x/u            | R/W-x/u              | R/W-x/u |

|-------------------|---------|----------------------|---------|-----------------|--------------------|----------------------|---------|

|                   |         |                      | PWMxI   | DCH<7:0>        |                    |                      |         |

| bit 7             |         |                      |         |                 |                    |                      | bit 0   |

|                   |         |                      |         |                 |                    |                      |         |

| Legend:           |         |                      |         |                 |                    |                      |         |

| R = Readable bit  | t       | W = Writable bit     |         | U = Unimpleme   | ented bit, read as | ʻ0'                  |         |

| u = Bit is unchan | iged    | x = Bit is unknown   | ı       | -n/n = Value at | POR and BOR/V      | alue at all other Re | esets   |

| '1' = Bit is set  |         | '0' = Bit is cleared |         |                 |                    |                      |         |

bit 7-0

**PWMxDCH<7:0>:** PWM Duty Cycle Most Significant bits These bits are the MSbs of the PWM duty cycle. The two LSbs are found in the PWMxDCL register.

#### REGISTER 23-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u                                                              | R/W-x/u                                                                       | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|-----|-----|-----|-----|--------|

| PWMxD                                                                | CL<7:6>                                                                       | _   | —   | —   | _   | —   | —      |

| bit 7                                                                |                                                                               | -   |     |     |     |     | bit 0  |

|                                                                      |                                                                               |     |     |     |     |     |        |

| Legend:                                                              |                                                                               |     |     |     |     |     |        |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                               |     |     |     |     |     |        |

| u = Bit is unchar                                                    | nged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |     |     |     |     |     | Resets |

| a Dicio anonai   |                                                |          |                                          |

|------------------|------------------------------------------------|----------|------------------------------------------|

| '1' = Bit is set | '0' = Bit is cleared                           |          |                                          |

| <b>1</b> 1 7 0   |                                                | · C      |                                          |

| bit 7-6          | PWMxDCL<7:6>: PWM Duty Cycle Least Sign        | nificant | DITS                                     |

|                  | These bits are the I Che of the DW/M duty such | The      | 1Cha are found in the DM/MyDCII register |

These bits are the LSbs of the PWM duty cycle. The MSbs are found in the PWMxDCH register. bit 5-0 **Unimplemented:** Read as '0'

#### TABLE 23-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

| Name    | Bit 7                         | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|------------------------|---------|---------|---------|--------|--------|--------|---------------------|

| PR2     | Timer2 module Period Register |                        |         |         |         |        |        |        |                     |

| PWM1CON | PWM1EN                        | PWM10E                 | PWM10UT | PWM1POL | _       | —      | —      | —      | 255                 |

| PWM1DCH |                               |                        |         | PWM1D0  | CH<7:0> |        |        |        | 256                 |

| PWM1DCL | PWM1D                         | CL<7:6>                | _       | _       | _       | —      | —      | —      | 256                 |

| PWM2CON | PWM2EN                        | PWM2OE                 | PWM2OUT | PWM2POL | _       | —      | _      | —      | 255                 |

| PWM2DCH |                               |                        |         | PWM2D0  | CH<7:0> |        |        |        | 256                 |

| PWM2DCL | PWM2D                         | CL<7:6>                | _       | _       | —       | —      | —      | —      | 256                 |

| PWM3CON | PWM3EN                        | PWM3OE                 | PWM3OUT | PWM3POL | _       | _      | _      | _      | 255                 |

| PWM3DCH |                               |                        | •       | PWM3D0  | CH<7:0> | •      |        | •      | 256                 |

| PWM3DCL | PWM3D                         | CL<7:6>                | —       | _       | —       | _      | _      | _      | 256                 |

| PWM4CON | PWM4EN                        | PWM4OE                 | PWM4OUT | PWM4POL | _       | _      | -      | _      | 255                 |

| PWM4DCH |                               |                        | •       | PWM4D0  | CH<7:0> | •      |        | •      | 256                 |

| PWM4DCL | PWM4D                         | CL<7:6>                | —       | _       | —       | _      | _      | _      | 256                 |

| T2CON   | _                             |                        | T2OUT   | PS<3:0> |         | TMR2ON | T2CKP  | S<1:0> | 168                 |

| TMR2    |                               | Timer2 module Register |         |         |         |        |        | 166*   |                     |

| TRISA   | —                             | —                      | TRISA5  | TRISA4  | —(1)    | TRISA2 | TRISA1 | TRISA0 | 109                 |

| TRISC   | TRISC7                        | TRISC6                 | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1 | TRISC0 | 117                 |

$\label{eq:legend: Legend: Legend: Legend: Legend: Legend: u = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM.$

\* Page provides register information.

Note 1: Unimplemented, read as '1'.

# 25.9 Register Definitions: NCOx Control Registers

#### REGISTER 25-1: NCOxCON: NCOx CONTROL REGISTER

| R/W-0/0          | R/W-0/0                                                           | R-0/0                                                                       | R/W-0/0       | U-0             | U-0                | U-0               | R/W-0/0    |  |  |  |  |  |

|------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------|-----------------|--------------------|-------------------|------------|--|--|--|--|--|

| NxEN             | NxOE                                                              | NxOUT                                                                       | NxPOL         | —               | —                  | —                 | NxPFM      |  |  |  |  |  |

| bit 7            |                                                                   | •                                                                           |               |                 |                    |                   | bit 0      |  |  |  |  |  |

| Legend:          |                                                                   |                                                                             |               |                 |                    |                   |            |  |  |  |  |  |

| R = Readable b   | <b>.</b> it                                                       | W = Writable bi                                                             | •             |                 | ented bit, read as | · 'O'             |            |  |  |  |  |  |

|                  |                                                                   |                                                                             |               | •               |                    |                   | <b>D</b> ( |  |  |  |  |  |

| u = Bit is uncha | inged                                                             | x = Bit is unkno                                                            |               | -n/n = Value at | POR and BOR/       | alue at all other | Resets     |  |  |  |  |  |

| '1' = Bit is set |                                                                   | '0' = Bit is clear                                                          | ed            |                 |                    |                   |            |  |  |  |  |  |

|                  |                                                                   |                                                                             |               |                 |                    |                   |            |  |  |  |  |  |

| bit 7            | NxEN: NCOx E                                                      | Enable bit                                                                  |               |                 |                    |                   |            |  |  |  |  |  |

|                  | 1 = NCOx module is enabled                                        |                                                                             |               |                 |                    |                   |            |  |  |  |  |  |

|                  | 0 = NCOx mod                                                      |                                                                             |               |                 |                    |                   |            |  |  |  |  |  |

| bit 6            |                                                                   | NxOE: NCOx Output Enable bit                                                |               |                 |                    |                   |            |  |  |  |  |  |

|                  | 1 = NCOx output pin is enabled<br>0 = NCOx output pin is disabled |                                                                             |               |                 |                    |                   |            |  |  |  |  |  |

| 5 H F            |                                                                   |                                                                             | I             |                 |                    |                   |            |  |  |  |  |  |

| bit 5            |                                                                   | xOUT: NCOx Output bit                                                       |               |                 |                    |                   |            |  |  |  |  |  |

|                  | 1 = NCOx output is high<br>0 = NCOx output is low                 |                                                                             |               |                 |                    |                   |            |  |  |  |  |  |

| bit 4            |                                                                   |                                                                             |               |                 |                    |                   |            |  |  |  |  |  |

| bit 4            |                                                                   | NxPOL: NCOx Polarity bit<br>1 = NCOx output signal is active low (inverted) |               |                 |                    |                   |            |  |  |  |  |  |

|                  |                                                                   | out signal is active                                                        | ( )           | rted)           |                    |                   |            |  |  |  |  |  |

| bit 3-1          | Unimplemente                                                      | ed: Read as '0'                                                             |               |                 |                    |                   |            |  |  |  |  |  |

| bit 0            | NxPFM: NCOx                                                       | Pulse Frequenc                                                              | v Mode bit    |                 |                    |                   |            |  |  |  |  |  |

| -                |                                                                   | rates in Pulse Fre                                                          |               |                 |                    |                   |            |  |  |  |  |  |

|                  | 0 = NCOx oper                                                     | rates in Fixed Du                                                           | ty Cycle mode |                 |                    |                   |            |  |  |  |  |  |

|                  |                                                                   |                                                                             |               |                 |                    |                   |            |  |  |  |  |  |

#### REGISTER 25-2: NCOxCLK: NCOx INPUT CLOCK CONTROL REGISTER

| NxPWS<2:0>(1, 2)         —         —         —         NxCKS<1:0>           bit 7           bit            bit </th <th>R/W-0/0</th> <th colspan="2">R/W-0/0 R/W-0/0 R/W-0/0</th> <th>U-0</th> <th>U-0</th> <th>U-0</th> <th colspan="2">R/W-0/0 R/W-0/</th> | R/W-0/0                      | R/W-0/0 R/W-0/0 R/W-0/0 |  | U-0 | U-0 | U-0 | R/W-0/0 R/W-0/ |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------|--|-----|-----|-----|----------------|--------|

| bit 7 bit                                                                                                                                                                                                                                                    | NxPWS<2:0> <sup>(1, 2)</sup> |                         |  | —   | —   | —   | NxCKS          | S<1:0> |

|                                                                                                                                                                                                                                                              | bit 7                        |                         |  |     |     |     |                | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 NxPWS<2:0>: NCOx Output Pulse Width Select bits<sup>(1, 2)</sup>

- 111 = 128 NCOx clock periods

- 110 = 64 NCOx clock periods

- 101 = 32 NCOx clock periods

- 100 = 16 NCOx clock periods

- 011 = 8 NCOx clock periods 010 = 4 NCOx clock periods

- 010 = 4 NCOx clock periods 001 = 2 NCOx clock periods

- 001 2 NCOX clock periods

- 000 = 1 NCOx clock periods

- bit 4-2 Unimplemented: Read as '0'

- bit 1-0 NxCKS<1:0>: NCOx Clock Source Select bits

- 11 = NCO1CLK pin

- 10 = LC1\_out

- 01 = Fosc

- 00 = HFINTOSC (16 MHz)

Note 1: NxPWS applies only when operating in Pulse Frequency mode.

2: If NCOx pulse width is greater than NCO\_overflow period, operation is indeterminate.

| PIC16LF |                 | Standard Operating Conditions (unless otherwise stated) |      |      |             |            |                                         |  |  |

|---------|-----------------|---------------------------------------------------------|------|------|-------------|------------|-----------------------------------------|--|--|

| PIC16F1 | 508/9           |                                                         |      |      |             |            |                                         |  |  |

| Param.  | Device          | Min.                                                    | Тур† | Max. | Units<br>μA | Conditions |                                         |  |  |

| No.     | Characteristics |                                                         |      |      |             | Vdd        | Note                                    |  |  |

| D016    |                 | _                                                       | 215  | 360  |             | 1.8        | Fosc = 500 kHz,                         |  |  |

|         |                 | —                                                       | 275  | 480  | μA          | 3.0        | HFINTOSC                                |  |  |

| D016    |                 | _                                                       | 270  | 450  | μA          | 2.3        | Fosc = 500 kHz,                         |  |  |

|         |                 | —                                                       | 300  | 500  | μA          | 3.0        | HFINTOSC                                |  |  |

|         |                 | —                                                       | 350  | 620  | μA          | 5.0        |                                         |  |  |

| D017*   |                 | _                                                       | 410  | 660  | μA          | 1.8        | Fosc = 8 MHz,                           |  |  |

|         |                 | —                                                       | 630  | 970  | μA          | 3.0        | HFINTOSC                                |  |  |

| D017*   |                 | _                                                       | 530  | 750  | μA          | 2.3        | Fosc = 8 MHz,                           |  |  |

|         |                 | —                                                       | 660  | 1100 | μA          | 3.0        | HFINTOSC                                |  |  |

|         |                 | —                                                       | 730  | 1200 | μA          | 5.0        |                                         |  |  |

| D018    |                 | _                                                       | 600  | 940  | μA          | 1.8        | Fosc = 16 MHz,                          |  |  |

|         |                 | —                                                       | 970  | 1400 | μA          | 3.0        | HFINTOSC                                |  |  |

| D018    |                 | —                                                       | 780  | 1200 | μA          | 2.3        | Fosc = 16 MHz,                          |  |  |

|         |                 | _                                                       | 1000 | 1550 | μA          | 3.0        | HFINTOSC                                |  |  |

|         |                 | _                                                       | 1090 | 1700 | μA          | 5.0        |                                         |  |  |

| D019A   |                 | _                                                       | 1030 | 1500 | μA          | 3.0        | Fosc = 20 MHz,                          |  |  |

|         |                 |                                                         |      |      |             |            | External Clock (ECH),                   |  |  |

| DOLOA   |                 |                                                         | 1000 | 1000 | •           | 0.0        | High-Power mode                         |  |  |

| D019A   |                 |                                                         | 1060 | 1600 | μA          | 3.0        | Fosc = 20 MHz,<br>External Clock (ECH), |  |  |

|         |                 | —                                                       | 1220 | 1800 | μA          | 5.0        | High-Power mode                         |  |  |

| TABLE 29-2: | SUPPLY CURRENT | (IDD) <sup>(1,2)</sup> ( | (CONTINUED) |

|-------------|----------------|--------------------------|-------------|

|-------------|----------------|--------------------------|-------------|

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in  $k\Omega$ .

#### TABLE 29-5: MEMORY PROGRAMMING SPECIFICATIONS

| Param.<br>No. | Sym.   | Characteristic                               | Min.   | Тур† | Max.   | Units | Conditions                                                           |

|---------------|--------|----------------------------------------------|--------|------|--------|-------|----------------------------------------------------------------------|

|               |        | Program Memory<br>Programming Specifications |        |      |        |       |                                                                      |

| D110          | VIHH   | Voltage on MCLR/VPP pin                      | 8.0    | _    | 9.0    | V     | (Note 2)                                                             |

| D112          | VPBE   | VDD for Bulk Erase                           | 2.7    | _    | VDDMAX | V     |                                                                      |

| D113          | VPEW   | VDD for Write or Row Erase                   | VDDMIN | —    | VDDMAX | V     |                                                                      |

| D114          | IPPPGM | Current on MCLR/VPP during<br>Erase/Write    | —      | 1.0  | —      | mA    |                                                                      |

| D115          | IDDPGM | Current on VDD during<br>Erase/Write         | —      | 5.0  | —      | mA    |                                                                      |

| D121          | Ep     | Program Flash Memory<br>Cell Endurance       | 10K    | _    |        | E/W   | -40°C ≤ TA ≤ +85°C<br>(Note 1)                                       |

| D122          | VPRW   | VDD for Read/Write                           | VDDMIN | _    | VDDMAX | V     |                                                                      |

| D123          | Tiw    | Self-timed Write Cycle Time                  | —      | 2    | 2.5    | ms    |                                                                      |

| D124          | TRETD  | Characteristic Retention                     | —      | 40   | —      | Year  | Provided no other specifications are violated                        |

| D125          | EHEFC  | High-Endurance Flash Cell                    | 100K   |      | _      | E/W   | $0^{\circ}C \le TA \le +60^{\circ}C$ , lower byte last 128 addresses |

#### Standard Operating Conditions (unless otherwise stated)

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Self-write and Block Erase.

2: Required only if single-supply programming is disabled.

#### TABLE 29-6: THERMAL CHARACTERISTICS

| Standar       | d Operating | Conditions (unless otherwise stated)   |      | I     | 1                                                        |

|---------------|-------------|----------------------------------------|------|-------|----------------------------------------------------------|

| Param.<br>No. | Sym.        | Characteristic                         | Тур. | Units | Conditions                                               |

| TH01          | θJA         | Thermal Resistance Junction to Ambient | 62.2 | °C/W  | 20-pin DIP package                                       |

|               |             |                                        | 77.7 | °C/W  | 20-pin SOIC package                                      |

|               |             |                                        | 87.3 | °C/W  | 20-pin SSOP package                                      |

|               |             |                                        | 46.2 | °C/W  | 20-pin QFN 4X4mm package                                 |

|               |             |                                        | 32.8 | °C/W  | 20-pin UQFN 4X4mm package                                |

| TH02          | θJC         | Thermal Resistance Junction to Case    | 27.5 | °C/W  | 20-pin DIP package                                       |

|               |             |                                        | 23.1 | °C/W  | 20-pin SOIC package                                      |

|               |             |                                        | 31.1 | °C/W  | 20-pin SSOP package                                      |

|               |             |                                        | 13.2 | °C/W  | 20-pin QFN 4X4mm package                                 |

|               |             |                                        | 27.4 | °C/W  | 20-pin UQFN 4X4mm package                                |

| TH03          | TJMAX       | Maximum Junction Temperature           | 150  | °C    |                                                          |

| TH04          | PD          | Power Dissipation                      |      | W     | PD = PINTERNAL + PI/O                                    |

| TH05          | PINTERNAL   | Internal Power Dissipation             |      | W     | $PINTERNAL = IDD \times VDD^{(1)}$                       |

| TH06          | Pi/o        | I/O Power Dissipation                  |      | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07          | Pder        | Derated Power                          |      | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |

#### Standard Operating Conditions (unless otherwise stated)

**Note 1:** IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature; TJ = Junction Temperature

# PIC16(L)F1508/9

### 31.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 31.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 31.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 31.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

# 31.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 31.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 31.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 31.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 31.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

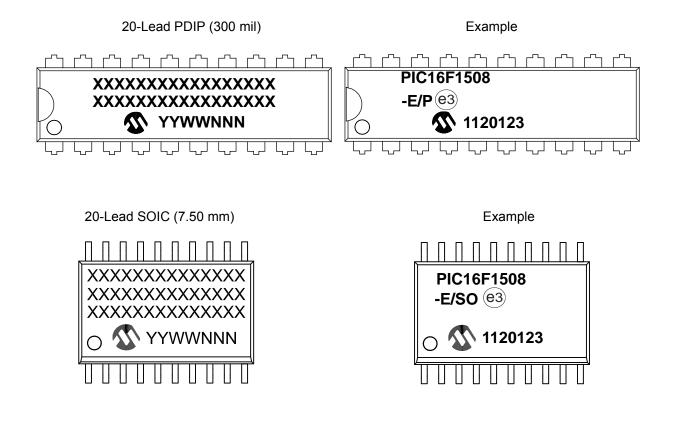

# 32.0 PACKAGING INFORMATION

# 32.1 Package Marking Information

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                                           |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

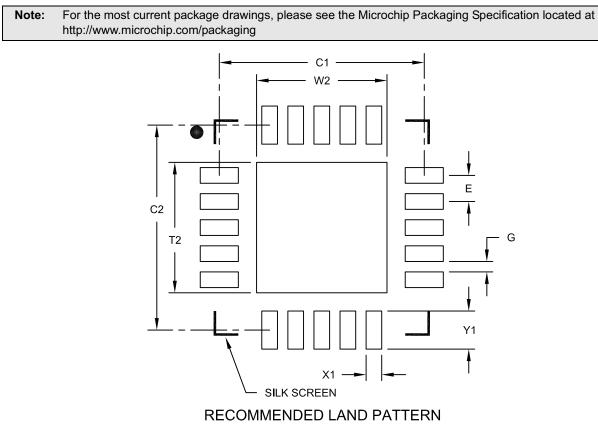

20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

|                            | MILLIMETERS     |      |      |      |

|----------------------------|-----------------|------|------|------|

| Dimensio                   | MIN             | NOM  | MAX  |      |

| Contact Pitch              | Contact Pitch E |      |      |      |

| Optional Center Pad Width  | W2              |      |      | 2.50 |

| Optional Center Pad Length | T2              |      |      | 2.50 |

| Contact Pad Spacing        | C1              |      | 3.93 |      |

| Contact Pad Spacing        | C2              |      | 3.93 |      |

| Contact Pad Width          | X1              |      |      | 0.30 |

| Contact Pad Length Y1      |                 |      |      | 0.73 |

| Distance Between Pads      | G               | 0.20 |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A