Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 20-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1508-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

The block diagram of these devices are shown in Figure 1-1, the available peripherals are shown in Table 1-1, and the pinout descriptions are shown in Table 1-2.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| TABLE 1-1. DEVICE P                                                    |               | <u></u>       | ,,,,,,,,,,    |               |               |   |

|------------------------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|---|

| Peripheral                                                             | PIC12(L)F1501 | PIC16(L)F1503 | PIC16(L)F1507 | PIC16(L)F1508 | PIC16(L)F1509 |   |

| Analog-to-Digital Converter (A                                         | ADC)          | •             | •             | •             | •             | • |

| Complementary Wave General                                             | ator (CWG)    | •             | •             | •             | •             | • |

| Digital-to-Analog Converter (I                                         | DAC)          | •             | •             |               | •             | • |

| Enhanced Universal<br>Synchronous/Asynchronous<br>Transmitter (EUSART) |               |               |               | •             | •             |   |

| Fixed Voltage Reference (FV                                            | R)            | •             | •             | •             | •             | • |

| Numerically Controlled Oscill                                          | •             | •             | •             | •             | •             |   |

| Temperature Indicator                                                  |               | •             | •             | •             | •             | • |

| Comparators                                                            |               |               |               |               |               |   |

|                                                                        | C1            | •             | •             |               | •             | • |

|                                                                        | C2            |               | •             |               | •             | • |

| Configurable Logic Cell (CLC                                           | ;)            |               |               |               |               |   |

|                                                                        | CLC1          | •             | •             | •             | •             | • |

|                                                                        | CLC2          | •             | •             | •             | •             | • |

|                                                                        | CLC3          |               |               |               | •             | • |

|                                                                        | CLC4          |               |               |               | •             | • |

| Master Synchronous Serial P                                            | orts          |               |               |               |               |   |

|                                                                        | MSSP1         |               | •             |               | •             | • |

| PWM Modules                                                            |               |               |               |               |               |   |

|                                                                        | PWM1          | •             | •             | •             | •             | • |

|                                                                        | PWM2          | •             | •             | •             | •             | • |

|                                                                        | PWM3          | •             | •             | •             | •             | • |

|                                                                        | •             | •             | •             | •             | •             |   |

| Timers                                                                 | ,             |               |               |               |               |   |

|                                                                        | Timer0        | •             | •             | •             | •             | • |

|                                                                        | Timer1        | •             | •             | •             | •             | • |

|                                                                        | Timer2        | •             | •             | •             | •             | • |

### 5.3.5 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely. when PPLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

### 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT, or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCSTAT register to remain clear.

### 9.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- · Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- · Multiple Reset conditions

- · Operation during Sleep

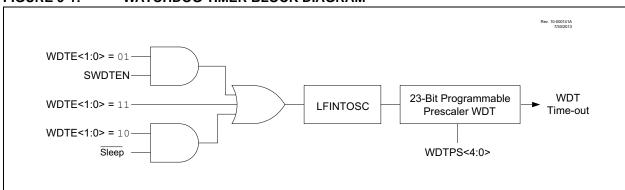

### FIGURE 9-1: WATCHDOG TIMER BLOCK DIAGRAM

### 11.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- · TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- · LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

TABLE 11-1: PORT AVAILABILITY PER DEVICE

| Device          | PORTA | PORTB | PORTC |

|-----------------|-------|-------|-------|

| PIC16(L)F1508/9 | •     | •     | •     |

| PIC16(L)F1508/9 | •     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

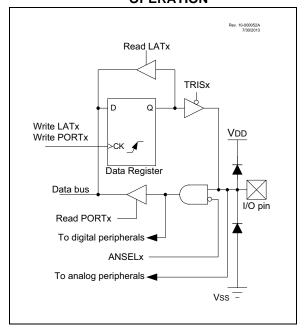

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

FIGURE 11-1: GENERIC I/O PORT OPERATION

### 16.6 Register Definitions: DAC Control

#### REGISTER 16-1: DACxCON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | U-0 | U-0   |

|---------|-----|---------|---------|-----|---------|-----|-------|

| DACEN   | _   | DACOE1  | DACOE2  | _   | DACPSS  | _   | _     |

| bit 7   |     |         |         |     |         |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 DACEN: DAC Enable bit

1 = DACx is enabled0 = DACx is disabled

bit 6 **Unimplemented:** Read as '0'

bit 5 DACOE1: DAC Voltage Output Enable bit

1 = DACx voltage level is output on the DACxOUT1 pin

0 = DACx voltage level is disconnected from the DACxOUT1 pin

bit 4 DACOE2: DAC Voltage Output Enable bit

1 = DACx voltage level is output on the DACxOUT2 pin

0 = DACx voltage level is disconnected from the DACxOUT2 pin

bit 3 Unimplemented: Read as '0'

bit 2 DACPSS: DAC Positive Source Select bit

1 = VREF+ pin0 = VDD

bit 1-0 **Unimplemented:** Read as '0'

#### REGISTER 16-2: DACxCON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

| _     | _   | _   |         |         | DACR<4:0> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits

### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name     | Bit 7 | Bit 6 | Bit 5  | Bit 4     | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Register on page |

|----------|-------|-------|--------|-----------|-------|--------|-------|-------|------------------|

| DAC1CON0 | DACEN | _     | DACOE1 | DACOE2    | _     | DACPSS | _     | _     | 144              |

| DAC1CON1 | _     | _     | _      | DACR<4:0> |       |        |       |       | 144              |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

### 19.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 19-1 displays the Timer1 enable selections.

TABLE 19-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

### 19.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 19-2 displays the clock source selections.

#### 19.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- · C1 or C2 comparator input to Timer1 gate

### 19.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI. The external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

Note:

In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · Timer1 enabled after POR

- · Write to TMR1H or TMR1L

- · Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

TABLE 19-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | T10SCEN | Clock Source                                     |

|-------------|---------|--------------------------------------------------|

| 11          | х       | LFINTOSC                                         |

| 1.0         | 1       | Secondary Oscillator Circuit on SOSCI/SOSCO Pins |

| 10          | 0       | External Clocking on T1CKI Pin                   |

| 01          | x       | System Clock (Fosc)                              |

| 00          | х       | Instruction Clock (Fosc/4)                       |

### 19.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

### 19.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

### 19.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 19-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | as changing the gate polarity may result in |  |  |  |  |  |  |

|       | indeterminate operation.                    |  |  |  |  |  |  |

### 19.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 19-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 19-6 for timing details.

#### 19.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 19.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

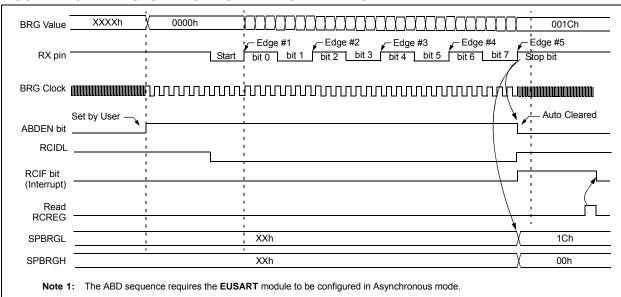

#### 22.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 22-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 22-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 22-6. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH

and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section22.4.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

TABLE 22-6: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

Note: During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

FIGURE 22-6: AUTOMATIC BAUD RATE CALIBRATION

### REGISTER 24-9: CLCDATA: CLC DATA OUTPUT

| U-0   | U-0 | U-0 | U-0 | R-0     | R-0     | R-0     | R-0     |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | _   | _   | MLC4OUT | MLC3OUT | MLC2OUT | MLC1OUT |

| bit 7 |     |     |     |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 Unimplemented: Read as '0'

bit 3 MLC4OUT: Mirror copy of LC4OUT bit

bit 2 MLC3OUT: Mirror copy of LC3OUT bit

bit 1 MLC2OUT: Mirror copy of LC2OUT bit

bit 0 MLC1OUT: Mirror copy of LC1OUT bit

DS40001609E-page 281

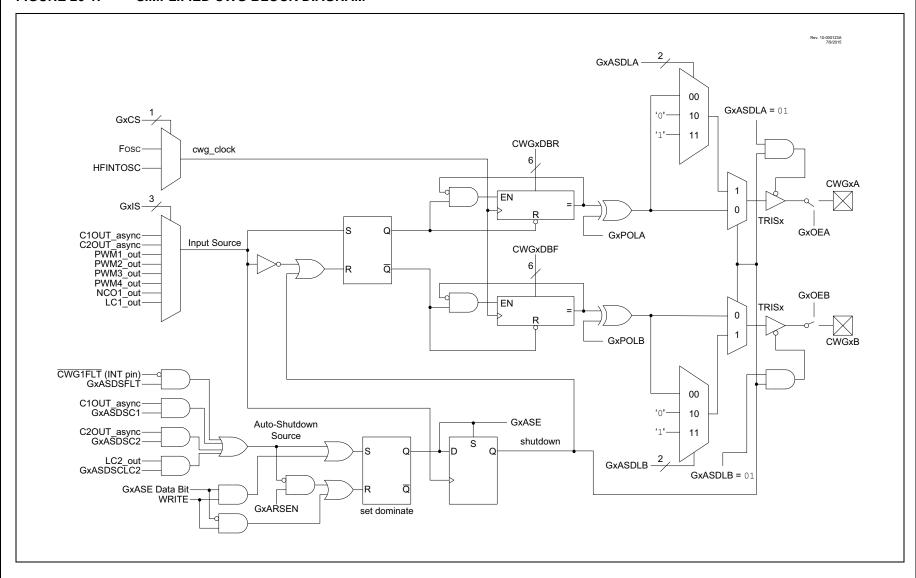

FIGURE 26-1: SIMPLIFIED CWG BLOCK DIAGRAM

### REGISTER 26-2: CWGxCON1: CWG CONTROL REGISTER 1

| R/W-x/u          | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|------------------|---------|---------|---------|-----|---------|-----------|---------|

| GxASDLB<1:0> GxA |         | GxASDI  | _A<1:0> | _   |         | GxIS<2:0> |         |

| bit 7            |         | •       |         |     |         |           | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 GxASDLB<1:0>: CWGx Shutdown State for CWGxB

When an auto shutdown event is present (GxASE = 1):

11 = CWGxB pin is driven to '1', regardless of the setting of the GxPOLB bit.

10 = CWGxB pin is driven to '0', regardless of the setting of the GxPOLB bit.

01 = CWGxB pin is tri-stated

00 = CWGxB pin is driven to its inactive state after the selected dead-band interval. GxPOLB still will control the polarity of the output.

bit 5-4 **GxASDLA<1:0>:** CWGx Shutdown State for CWGxA

When an auto shutdown event is present (GxASE = 1):

11 = CWGxA pin is driven to '1', regardless of the setting of the GxPOLA bit.

10 = CWGxA pin is driven to '0', regardless of the setting of the GxPOLA bit.

01 = CWGxA pin is tri-stated

00 = CWGxA pin is driven to its inactive state after the selected dead-band interval. GxPOLA still will control the polarity of the output.

bit 3 **Unimplemented:** Read as '0'

bit 2-0 GxIS<2:0>: CWGx Input Source Select bits

111 = CLC1 - LC1 out

110 = NCO1 - NCO1 out

101 = PWM4 - PWM4 out

$100 = PWM3 - PWM3_out$

011 = PWM2 - PWM2 out

010 = PWM1 - PWM1 out

001 = Comparator C2- C2OUT async

000 = Comparator C1 - C1OUT async

### 29.3 DC Characteristics

TABLE 29-1: SUPPLY VOLTAGE

| PIC16LF1508/9 PIC16F1508/9                                |      |                                                                                  | Standard Operating Conditions (unless otherwise stated) |      |                      |        |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|-----------------------------------------------------------|------|----------------------------------------------------------------------------------|---------------------------------------------------------|------|----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                           |      |                                                                                  |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Param.<br>No.                                             | Sym. | Characteristic                                                                   | Min.                                                    | Тур† | Max.                 | Units  | Conditions                                                                                                                                                                                                                                                                                                                      |  |  |  |

| D001                                                      | VDD  | Supply Voltage                                                                   |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                           |      |                                                                                  | VDDMIN<br>1.8<br>2.5                                    | _    | VDDMAX<br>3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz<br>Fosc ≤ 20 MHz                                                                                                                                                                                                                                                                                                  |  |  |  |

| D001                                                      |      |                                                                                  | 2.3<br>2.5                                              | _    | 5.5<br>5.5           | V<br>V | Fosc ≤ 16 MHz<br>Fosc ≤ 20 MHz                                                                                                                                                                                                                                                                                                  |  |  |  |

| D002*                                                     | VDR  | RAM Data Retention Voltage <sup>(1)</sup>                                        |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                           |      |                                                                                  | 1.5                                                     | _    | _                    | V      | Device in Sleep mode                                                                                                                                                                                                                                                                                                            |  |  |  |

| D002*                                                     |      |                                                                                  | 1.7                                                     | _    | _                    | V      | Device in Sleep mode                                                                                                                                                                                                                                                                                                            |  |  |  |

| D002A*                                                    | VPOR | VPOR Power-on Reset Release Voltage <sup>(2)</sup>                               |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                           |      |                                                                                  | _                                                       | 1.6  | _                    | V      |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| D002A*                                                    |      |                                                                                  | _                                                       | 1.6  | _                    | V      |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| D002B* VPORR* Power-on Reset Rearm Voltage <sup>(2)</sup> |      |                                                                                  |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                           |      |                                                                                  | _                                                       | 8.0  | _                    | V      |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| D002B*                                                    |      |                                                                                  | _                                                       | 1.5  | _                    | V      |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| D003                                                      | VFVR | Fixed Voltage Reference Voltage                                                  |                                                         |      |                      |        |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                                           |      | 1x gain (1.024V nominal)<br>2x gain (2.048V nominal)<br>4x gain (4.096V nominal) | -4                                                      | _    | +4<br>+7             | %<br>% | $\begin{split} &V \text{DD} \geq 2.5 \text{V},  -40^{\circ} \text{C} \leq \text{Ta} \leq +85^{\circ} \text{C} \\ &V \text{DD} \geq 2.5 \text{V},  -40^{\circ} \text{C} \leq \text{Ta} \leq +85^{\circ} \text{C} \\ &V \text{DD} \geq 4.75 \text{V},  -40^{\circ} \text{C} \leq \text{Ta} \leq +85^{\circ} \text{C} \end{split}$ |  |  |  |

| D004*                                                     | SVDD | VDD Rise Rate <sup>(2)</sup>                                                     | 0.05                                                    | _    | _                    | V/ms   | Ensures that the Power-on Reset signal is released properly.                                                                                                                                                                                                                                                                    |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> See Figure 29-3, POR and POR REARM with Slow Rising VDD.

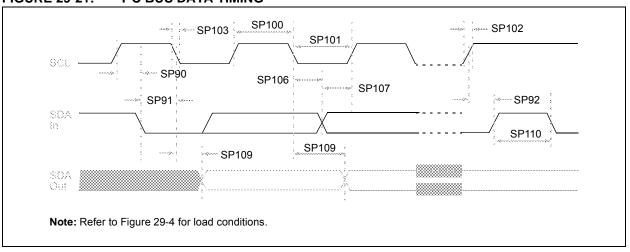

FIGURE 29-20: I<sup>2</sup>C BUS START/STOP BITS TIMING

TABLE 29-20: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Param.<br>No. | Symbol  | Charac          | Characteristic |      | Тур | Max. | Units | Conditions                   |  |

|---------------|---------|-----------------|----------------|------|-----|------|-------|------------------------------|--|

| SP90*         | Tsu:sta | Start condition | 100 kHz mode   | 4700 | _   | _    | ns    | Only relevant for Repeated   |  |

|               |         | Setup time      | 400 kHz mode   | 600  | _   | _    |       | Start condition              |  |

| SP91*         | THD:STA | Start condition | 100 kHz mode   | 4000 | _   | _    | ns    | After this period, the first |  |

|               |         | Hold time       | 400 kHz mode   | 600  | _   | _    |       | clock pulse is generated     |  |

| SP92*         | Tsu:sto | Stop condition  | 100 kHz mode   | 4700 | _   |      | ns    |                              |  |

|               |         | Setup time      | 400 kHz mode   | 600  | _   | _    |       |                              |  |

| SP93          | THD:STO | Stop condition  | 100 kHz mode   | 4000 | _   | _    | ns    |                              |  |

|               |         | Hold time       | 400 kHz mode   | 600  | _   | _    |       |                              |  |

<sup>\*</sup> These parameters are characterized but not tested.

### FIGURE 29-21: I<sup>2</sup>C BUS DATA TIMING

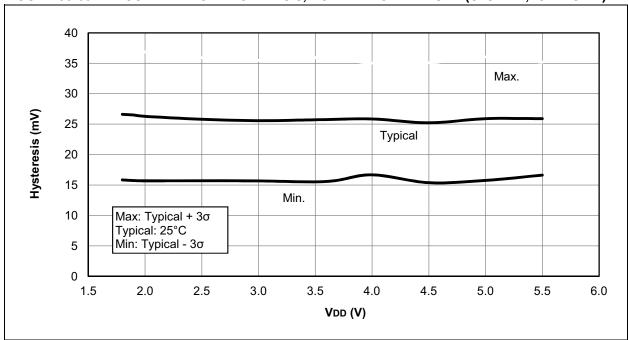

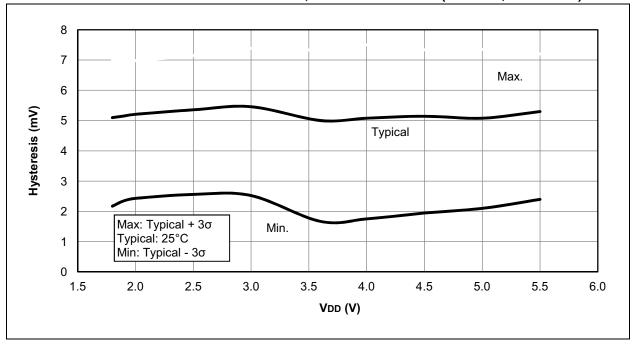

### 30.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

Note:

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

<sup>&</sup>quot;Typical" represents the mean of the distribution at 25°C. "MAXIMUM", "Max.", "MINIMUM" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

FIGURE 30-65: COMPARATOR HYSTERESIS, NORMAL POWER MODE (CxSP = 1, CxHYS = 1)

FIGURE 30-66: COMPARATOR HYSTERESIS, LOW-POWER MODE (CxSP = 0, CxHYS = 1)

### 31.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

### 31.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 31.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 31.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

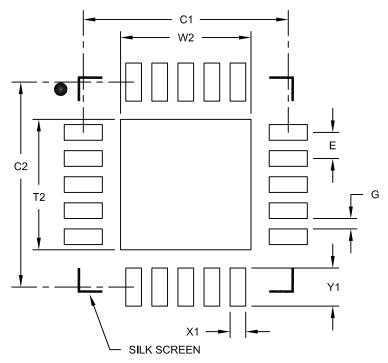

20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

|                            | Units |          |      | MILLIMETERS |  |  |  |

|----------------------------|-------|----------|------|-------------|--|--|--|

| Dimension Limits           |       | MIN      | NOM  | MAX         |  |  |  |

| Contact Pitch              | Ш     | 0.50 BSC |      |             |  |  |  |

| Optional Center Pad Width  | W2    |          |      | 2.50        |  |  |  |

| Optional Center Pad Length | T2    |          |      | 2.50        |  |  |  |

| Contact Pad Spacing        | C1    |          | 3.93 |             |  |  |  |

| Contact Pad Spacing        | C2    |          | 3.93 |             |  |  |  |

| Contact Pad Width          | X1    |          |      | 0.30        |  |  |  |

| Contact Pad Length         | Y1    |          |      | 0.73        |  |  |  |

| Distance Between Pads      | G     | 0.20     |      |             |  |  |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- · Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELoQ, KEELoQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-63277-918-2

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.