Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1508-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|------------|-------|-------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  | _     | _          |       | _     | _     | BORRDY | 64                  |

| PCON   | STKOVF | STKUNF | _     | RWDT       | RMCLR | RI    | POR   | BOR    | 68                  |

| STATUS | —      | _      | _     | TO         | PD    | Z     | DC    | С      | 19                  |

| WDTCON | —      | —      |       | WDTPS<4:0> |       |       |       |        | 88                  |

TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

Legend: — = unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

TABLE 6-6:

SUMMARY OF CONFIGURATION WORD WITH RESETS

| Name    | Bits   | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2   | Bit 9/1   | Bit 8/0  | Register<br>on Page |

|---------|--------|---------|---------|----------|----------|----------|------------|-----------|----------|---------------------|

| CONFIG1 | 13:8 — |         | —       | FCMEN    | IESO     | CLKOUTEN | BOREN<1:0> |           | _        | 40                  |

| CONFIGT | 7:0    | CP      | MCLRE   | PWRTE    | WD       | TE<1:0>  | [          | FOSC<2:0> | <b>`</b> | 43                  |

| CONFIG2 | 13:8   | _       | _       | LVP      | —        | LPBOR    | BORV       | STVREN    | _        | 40                  |

|         | 7:0    | _       | _       | _        | _        | _        | _          | WRT       | <1:0>    | 43                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

## 9.1 Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 29.0 "Electrical Specifications"** for the LFINTOSC tolerances.

## 9.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 9-1.

#### 9.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 9.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

### 9.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 9-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | х      | Х              | Active      |

| 10        |        | Awake          | Active      |

| 10        | х      | Sleep          | Disabled    |

| 0.1       | 1      | Х              | Active      |

| 01        | 0      | Х              | Disabled    |

| 00        | х      | Х              | Disabled    |

## TABLE 9-1: WDT OPERATING MODES

#### 9.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

## 9.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- · Any Reset

- CLRWDT instruction is executed

- Device enters Sleep

- · Device wakes up from Sleep

- Oscillator fail

- WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 9-2 for more information.

## 9.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting. When the device exits Sleep, the WDT is cleared again.

The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See Section 3.0 "Memory Organization" for more information.

| <b>TABLE 9-2:</b> | WDT CLEARING CONDITIONS |

|-------------------|-------------------------|

|-------------------|-------------------------|

| Conditions                                               | WDT                          |  |  |  |  |

|----------------------------------------------------------|------------------------------|--|--|--|--|

| WDTE<1:0> = 00                                           |                              |  |  |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |  |  |  |  |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |  |  |  |  |

| CLRWDT Command                                           | Cleared                      |  |  |  |  |

| Oscillator Fail Detected                                 |                              |  |  |  |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |  |  |  |  |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |  |  |  |  |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |  |  |  |  |

| U-1            | R/W-0/0              | R/W-0/0                                 | R/W/HC-0/0         | R/W/HC-x/q <sup>(2)</sup> | R/W-0/0            | R/S/HC-0/0           | R/S/HC-0/0        |

|----------------|----------------------|-----------------------------------------|--------------------|---------------------------|--------------------|----------------------|-------------------|

| (1)            | CFGS                 | LWLO                                    | FREE               | WRERR                     | WREN               | WR                   | RD                |

| oit 7          | ·                    |                                         | •                  |                           |                    |                      | bit               |

| Legend:        |                      |                                         |                    |                           |                    |                      |                   |

| R = Readal     | ble bit              | W = Writable b                          | it                 | U = Unimpleme             | ented bit, read as | s 'O'                |                   |

| S = Bit can    | only be set          | x = Bit is unkno                        | own                | -n/n = Value at           | POR and BOR/       | Value at all other I | Resets            |

| '1' = Bit is s | et                   | '0' = Bit is clea                       | red                | HC = Bit is clea          | ared by hardware   | 9                    |                   |

|                |                      |                                         |                    |                           |                    |                      |                   |

| bit 7          | Unimplement          | ed: Read as '1'                         |                    |                           |                    |                      |                   |

| bit 6          | CFGS: Config         | uration Select bit                      |                    |                           |                    |                      |                   |

|                |                      | configuration, Use                      |                    | ID Registers              |                    |                      |                   |

|                |                      | lash program me                         |                    |                           |                    |                      |                   |

| bit 5          |                      | Vrite Latches On                        |                    |                           |                    |                      |                   |

|                |                      |                                         |                    |                           |                    | next WR comman       |                   |

|                |                      | tiated on the nex                       |                    |                           |                    | an programment       | ory write laterie |

| bit 4          |                      | m Flash Erase E                         |                    |                           |                    |                      |                   |

|                | •                    |                                         |                    | VR command (ha            | ardware cleared    | upon completion)     | )                 |

|                | 0 = Performs         | a write operation                       | n on the next WF   | R command                 |                    |                      |                   |

| bit 3          | WRERR: Prog          | ram/Erase Error                         | Flag bit           |                           |                    |                      |                   |

|                |                      |                                         |                    | •                         | ce attempt or te   | rmination (bit is s  | et automatical    |

|                | •                    | et attempt (write '<br>ram or erase ope | ,                  |                           |                    |                      |                   |

| bit 2          |                      | •                                       | •                  | u normany.                |                    |                      |                   |

| DILZ           | •                    | am/Erase Enable<br>ogram/erase cyc      |                    |                           |                    |                      |                   |

|                | •                    | rogramming/eras                         |                    | Flash                     |                    |                      |                   |

| bit 1          | WR: Write Cor        | <b>o o</b>                              | 0 1 0              |                           |                    |                      |                   |

|                |                      | program Flash                           | orogram/erase o    | peration.                 |                    |                      |                   |

|                |                      | ation is self-timed                     |                    |                           | are once operation | on is complete.      |                   |

|                |                      | bit can only be se                      |                    |                           | 4                  |                      |                   |

|                | 0                    | erase operation                         | to the Flash is co | omplete and inac          | tive.              |                      |                   |

| bit 0          | RD: Read Cor         |                                         | and Dood toko      |                           | a algored in here  | ware The DD hit      | ann anly ha a     |

|                |                      | ed) in software.                        |                    | s one cycle. RD I         | s cleared in hard  | lware. The RD bit    | . Carl Only De S  |

|                | ``                   | initiate a program                      | n Flash read.      |                           |                    |                      |                   |

| Note 1:        | Unimplemented bit,   |                                         |                    |                           |                    |                      |                   |

| 2:             | The WRERR bit is a   |                                         | by hardware whe    | en a program me           | mory write or era  | ase operation is s   | tarted (WR = 1    |

| 2.             | The LWL O bit is ign | ored during a pro                       | aram memory e      | rase operation (          | PRFF = 1           |                      |                   |

# REGISTER 10-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

3: The LWLO bit is ignored during a program memory erase operation (FREE = 1).

## TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|---------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | ′R>1:0> | ADFVF | २<1:0> | 125                 |

**Legend:** Shaded cells are unused by the temperature indicator module.

## 15.2.6 ADC CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- Disable weak pull-ups either globally (Refer to the OPTION\_REG register) or individually (Refer to the appropriate WPUx register).

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- · Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

**Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 15.4 "ADC Acquisition Requirements".

#### EXAMPLE 15-1: ADC CONVERSION

```

;This code block configures the ADC

; for polling, Vdd and Vss references, FRC

;oscillator and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL

ADCON1

;

B'11110000' ;Right justify, FRC

MOVLW

;oscillator

MOVWF

ADCON1

;Vdd and Vss Vref+

BANKSEL

TRISA

TRISA,0

;Set RA0 to input

BSF

BANKSEL

ANSEL

;

BSF

ANSEL,0

;Set RA0 to analog

BANKSEL

WPUA

BCF

WPUA,0

;Disable weak

pull-up on RAO

BANKSEL

ADCON0

;

B'00000001' ;Select channel AN0

MOVLW

MOVWF

ADCON0

;Turn ADC On

SampleTime ;Acquisiton delay

CALL

ADCON0, ADGO ; Start conversion

BSF

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

;No, test again

$-1

BANKSEL

ADRESH

;

MOVE

ADRESH,W ;Read upper 2 bits

MOVWF

RESULTHI ;store in GPR space

BANKSEL

ADRESL

;

ADRESL,W

;Read lower 8 bits

MOVF

MOVWF

RESULTLO

;Store in GPR space

```

# REGISTER 15-4: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | ADRE    | S<9:2>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | mented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 ADRES<9:2>: ADC Result Register bits Upper eight bits of 10-bit conversion result

### REGISTER 15-5: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADRES<1:0> |         | —       | —       | —       | —       | —       | —       |

| bit 7      |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 ADRES<1:0>: ADC Result Register bits Lower two bits of 10-bit conversion result Reserved: Do not use. bit 5-0

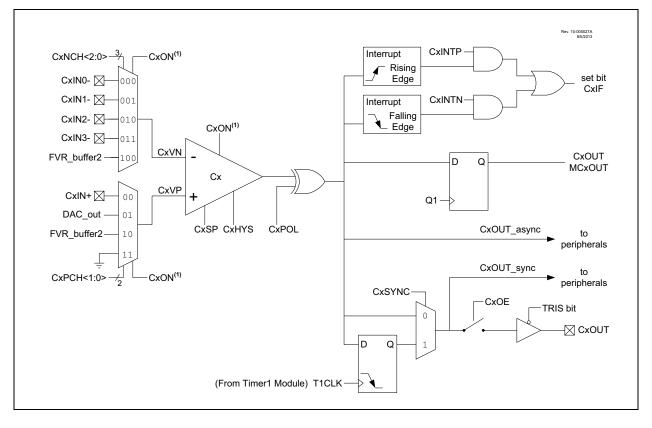

# 17.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- · Programmable input selection

- · Comparator output is available internally/externally

- · Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- Programmable Speed/Power optimization

- PWM shutdown

- Programmable and fixed voltage reference

# 17.1 Comparator Overview

A single comparator is shown in Figure 17-2 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are listed in Table 17-1.

## TABLE 17-1: AVAILABLE COMPARATORS

| Device        | C1 | C2 |

|---------------|----|----|

| PIC16(L)F1508 | •  | •  |

| PIC16(L)F1509 | •  | •  |

## FIGURE 17-1: COMPARATOR MODULE SIMPLIFIED BLOCK DIAGRAM

## 19.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 19.4 Timer1 (Secondary) Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal. The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires some time to start-up and stabilize before use. The SOSCR bit in the OSCSTAT register monitors the oscillator and indicates when the oscillator is ready for use. When T1OSCEN is set, the SOSCR bit is cleared. After 1024 cycles of the oscillator are countered, the SOSCR bit is set, indicating that the oscillator should be stable and ready for use.

# 19.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 19.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

## 19.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads. For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 19.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

## 19.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 19-3 for timing details.

# TABLE 19-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G Timer1 Operation |             |  |  |

|------------|--------|----------------------|-------------|--|--|

| $\uparrow$ | 0      | 0                    | Counts      |  |  |

| $\uparrow$ | 0      | 1                    | Holds Count |  |  |

| $\uparrow$ | 1      | 0                    | Holds Count |  |  |

| $\uparrow$ | 1      | 1                    | Counts      |  |  |

## 19.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 19-4. Source selection is controlled by the T1GSS<1:0> bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

| TABLE 19-4: | TIMER1 GATE SOURCES |

|-------------|---------------------|

|-------------|---------------------|

| T1GSS   | Timer1 Gate Source                                                    |

|---------|-----------------------------------------------------------------------|

| 00      | Timer1 Gate pin (T1G)                                                 |

| 01      | Overflow of Timer0 (T0_overflow)<br>(TMR0 increments from FFh to 00h) |

| 10      | Comparator 1 Output (C1OUT_sync) <sup>(1)</sup>                       |

| 11      | Comparator 2 Output (C2OUT_sync) <sup>(1)</sup>                       |

| Nata di |                                                                       |

Note 1: Optionally synchronized comparator output.

| Name    | Bit 7        | Bit 6           | Bit 5          | Bit 4          | Bit 3                   | Bit 2  | Bit 1   | Bit 0      | Register<br>on Page |  |

|---------|--------------|-----------------|----------------|----------------|-------------------------|--------|---------|------------|---------------------|--|

| ANSELA  | —            | _               | —              | ANSA4          | —                       | ANSA2  | ANSA1   | ANSA0      | 110                 |  |

| APFCON  | —            | _               | —              | SSSEL          | T1GSEL                  | —      | CLC1SEL | NCO1SEL    | 107                 |  |

| INTCON  | GIE          | PEIE            | TMR0IE         | INTE           | IOCIE                   | TMR0IF | INTF    | IOCIF      | 75                  |  |

| OSCSTAT | SOSCR        | _               | OSTS           | HFIOFR         | —                       | _      | LFIOFR  | HFIOFS     | 60                  |  |

| PIE1    | TMR1GIE      | ADIE            | RCIE           | TXIE           | SSP1IE                  | —      | TMR2IE  | TMR1IE     | 76                  |  |

| PIR1    | TMR1GIF      | ADIF            | RCIF           | TXIF           | SSP1IF                  | _      | TMR2IF  | TMR1IF     | 79                  |  |

| TMR1H   | Holding Regi | ster for the M  | ost Significan | t Byte of the  | 16-bit TMR1 (           | Count  |         |            | 159*                |  |

| TMR1L   | Holding Regi | ster for the Le | east Significa | nt Byte of the | 16-bit TMR1             | Count  |         |            | 159*                |  |

| TRISA   | —            | _               | TRISA5         | TRISA4         | _(1)                    | TRISA2 | TRISA1  | TRISA0     | 109                 |  |

| T1CON   | TMR1C        | S<1:0>          | T1CKP          | S<1:0>         | T10SCEN                 | T1SYNC | -       | TMR10N     | 163                 |  |

| T1GCON  | TMR1GE       | T1GPOL          | T1GTM          | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL | T1GS    | T1GSS<1:0> |                     |  |

## TABLE 19-5: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

Note 1: Unimplemented, read as '1'.

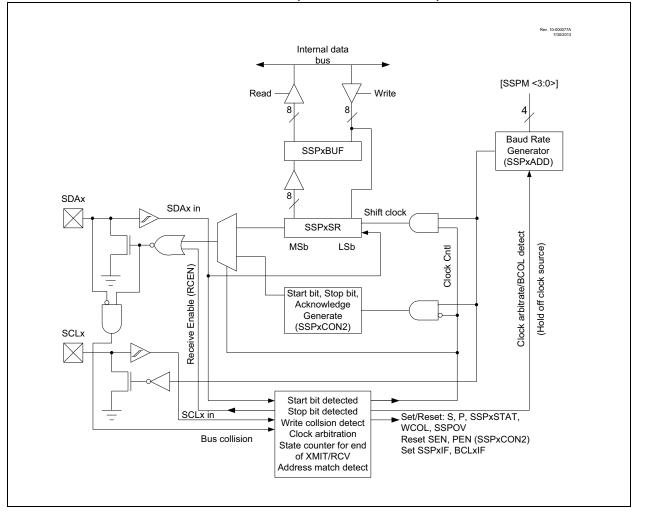

The  $I^2C$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- Clock stretching

- Bus collision detection

- General call address matching

- Address masking

- · Address Hold and Data Hold modes

- · Selectable SDAx hold times

Figure 21-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 21-3 is a diagram of the  $I^2C$  interface module in Slave mode.

Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSPxCON1 and SSPxCON2 registers control different operational aspects of the same module, while SSPxCON1 and SSP2CON1 control the same features for two different modules.

2: Throughout this section, generic references to an MSSPx module in any of its operating modes may be interpreted as being equally applicable to MSSPx or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

## FIGURE 21-2: MSSPX BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

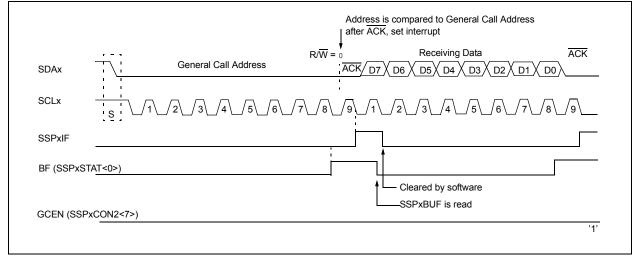

#### 21.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the I<sup>2</sup>C protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically  $\overline{ACK}$  the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 21-24 shows a General Call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCLx. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

## FIGURE 21-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

## 21.5.9 SSPx MASK REGISTER

An SSPx Mask (SSPxMSK) register (Register 21-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSPx operation until written with a mask value.

The SSPx Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSPx mask has no effect during the reception of the first (high) byte of the address.

# REGISTER 21-5: SSPxMSK: SSP MASK REGISTER

| R/W-1/1                                 | R/W-1/1                                                                                                                                                                                                                                | R/W-1/1                                                                                  | R/W-1/1                       | R/W-1/1                                               | R/W-1/1          | R/W-1/1  | R/W-1/1 |  |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------|------------------|----------|---------|--|--|--|

|                                         |                                                                                                                                                                                                                                        |                                                                                          | MSK                           | <7:0>                                                 |                  |          |         |  |  |  |

| bit 7                                   |                                                                                                                                                                                                                                        |                                                                                          |                               |                                                       |                  |          |         |  |  |  |

| r                                       |                                                                                                                                                                                                                                        |                                                                                          |                               |                                                       |                  |          |         |  |  |  |

| Legend:                                 |                                                                                                                                                                                                                                        |                                                                                          |                               |                                                       |                  |          |         |  |  |  |

| R = Readable                            | e bit                                                                                                                                                                                                                                  | W = Writable                                                                             | bit                           | U = Unimpler                                          | nented bit, read | l as '0' |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown |                                                                                                                                                                                                                                        |                                                                                          | nown                          | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |  |  |

| '1' = Bit is set                        |                                                                                                                                                                                                                                        | '0' = Bit is cle                                                                         | ared                          |                                                       |                  |          |         |  |  |  |

| bit 7-1                                 | MEK 27.1                                                                                                                                                                                                                               | Mook bito                                                                                |                               |                                                       |                  |          |         |  |  |  |

| DIL 7-1                                 | bit 7-1 <b>MSK&lt;7:1&gt;:</b> Mask bits<br>1 = The received address bit n is compared to SSPxADD <n> to detect I<sup>2</sup>C address match<br/>0 = The received address bit n is not used to detect I<sup>2</sup>C address match</n> |                                                                                          |                               |                                                       |                  |          |         |  |  |  |

| bit 0                                   | I <sup>2</sup> C Slave me<br>1 = The rec                                                                                                                                                                                               | ask bit for I <sup>2</sup> C S<br>ode, 10-bit addr<br>eived address b<br>eived address b | ess (SSPM<3<br>it 0 is compar | 3:0> = 0111 or<br>red to SSPxADI                      | D<0> to detect   |          | atch    |  |  |  |

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

# REGISTER 21-6: SSPxADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | ADD     | <7:0>          |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is uncha | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

#### Master mode:

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits SCLx pin clock period = ((ADD<7:0> + 1) \*4)/Fosc

#### <u>10-Bit Slave mode – Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## 10-Bit Slave mode – Least Significant Address Byte:

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

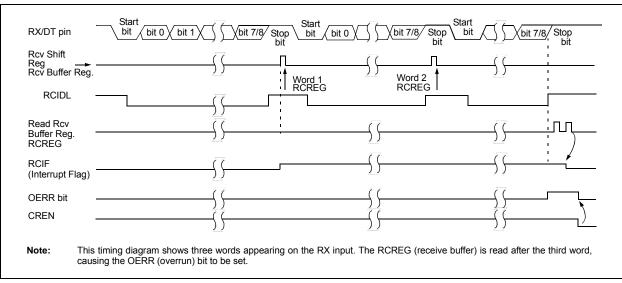

- 22.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section22.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

22.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section22.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

# FIGURE 22-5: ASYNCHRONOUS RECEPTION

| R-0/0            | R-1/1                           | U-0                                   | R/W-0/0         | R/W-0/0          | U-0             | R/W-0/0            | R/W-0/0      |

|------------------|---------------------------------|---------------------------------------|-----------------|------------------|-----------------|--------------------|--------------|

| ABDOVF           | RCIDL                           |                                       | SCKP            | BRG16            | _               | WUE                | ABDEN        |

| bit 7            |                                 |                                       |                 |                  |                 | ·                  | bit 0        |

|                  |                                 |                                       |                 |                  |                 |                    |              |

| Legend:          |                                 |                                       |                 |                  |                 |                    |              |

| R = Readable     |                                 | W = Writable                          | e bit           | •                | mented bit, rea |                    |              |

| u = Bit is uncl  | 0                               | x = Bit is unk                        | nown            | -n/n = Value a   | at POR and B    | OR/Value at all c  | other Resets |

| '1' = Bit is set |                                 | '0' = Bit is cle                      | eared           |                  |                 |                    |              |

| bit 7            | ABDOVF: A                       | uto-Baud Dete                         | ct Overflow bit |                  |                 |                    |              |

|                  | Asynchrono                      |                                       |                 |                  |                 |                    |              |

|                  | 1 = Auto-ba                     | ud timer overflo                      |                 |                  |                 |                    |              |

|                  |                                 | ud timer did not                      | overflow        |                  |                 |                    |              |

|                  | <u>Synchronou</u><br>Don't care | <u>s mode</u> :                       |                 |                  |                 |                    |              |

| bit 6            | RCIDL: Rec                      | eive Idle Flag b                      | bit             |                  |                 |                    |              |

|                  | Asynchrono                      | -                                     |                 |                  |                 |                    |              |

|                  | 1 = Receive                     |                                       |                 |                  |                 |                    |              |

|                  | 0 = Start bit<br>Synchronou     | has been recei<br>s mode:             | ved and the re  | ceiver is receiv | ing             |                    |              |

|                  | Don't care                      | <u>s mode</u> .                       |                 |                  |                 |                    |              |

| bit 5            | Unimpleme                       | nted: Read as                         | <b>'</b> 0'     |                  |                 |                    |              |

| bit 4            | SCKP: Sync                      | hronous Clock                         | Polarity Select | t bit            |                 |                    |              |

|                  | Asynchrono                      | <u>us mode</u> :                      |                 |                  |                 |                    |              |

|                  |                                 | t inverted data<br>t non-inverted o   |                 |                  |                 |                    |              |

|                  | Synchronou                      |                                       |                 |                  |                 |                    |              |

|                  |                                 | clocked on risin<br>clocked on fallir |                 |                  |                 |                    |              |

| bit 3            | BRG16: 16-                      | bit Baud Rate                         | Generator bit   |                  |                 |                    |              |

|                  |                                 | aud Rate Gene<br>ud Rate Gener        |                 |                  |                 |                    |              |

| bit 2            | Unimpleme                       | nted: Read as                         | '0'             |                  |                 |                    |              |

| bit 1            | WUE: Wake                       | -up Enable bit                        |                 |                  |                 |                    |              |

|                  | Asynchrono                      | <u>us mode</u> :                      |                 |                  |                 |                    |              |

|                  | automati                        | cally clear after                     | RCIF is set.    | No character w   | ill be received | , RCIF bit will be | set. WUE wil |

|                  |                                 | r is operating n                      | ormally         |                  |                 |                    |              |

|                  | <u>Synchronou</u><br>Don't care | s mode:                               |                 |                  |                 |                    |              |

| bit 0            |                                 | to-Baud Detect                        | Enable hit      |                  |                 |                    |              |

|                  | ASynchrono                      |                                       |                 |                  |                 |                    |              |

|                  | -                               | aud Detect mod                        | e is enabled (c | lears when au    | to-baud is corr | nplete)            |              |

|                  |                                 | aud Detect moc                        | -               |                  |                 | . ,                |              |

|                  | Synchronou                      | <u>s mode</u> :                       |                 |                  |                 |                    |              |

|                  | Don't care                      |                                       |                 |                  |                 |                    |              |

## REGISTER 22-3: BAUDCON: BAUD RATE CONTROL REGISTER

#### 22.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

#### 22.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave<br/>modesareidentical(seeSection22.5.1.3 "SynchronousMasterTransmission"), except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 22.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

# TABLE 22-9:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 235                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 75                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSP1IE | —      | TMR2IE | TMR1IE | 76                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSP1IF | —      | TMR2IF | TMR1IF | 79                  |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 234                 |

| TRISB   | TRISB7                        | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 113                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        |        |        |                     |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 233                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave transmission.

Page provides register information.

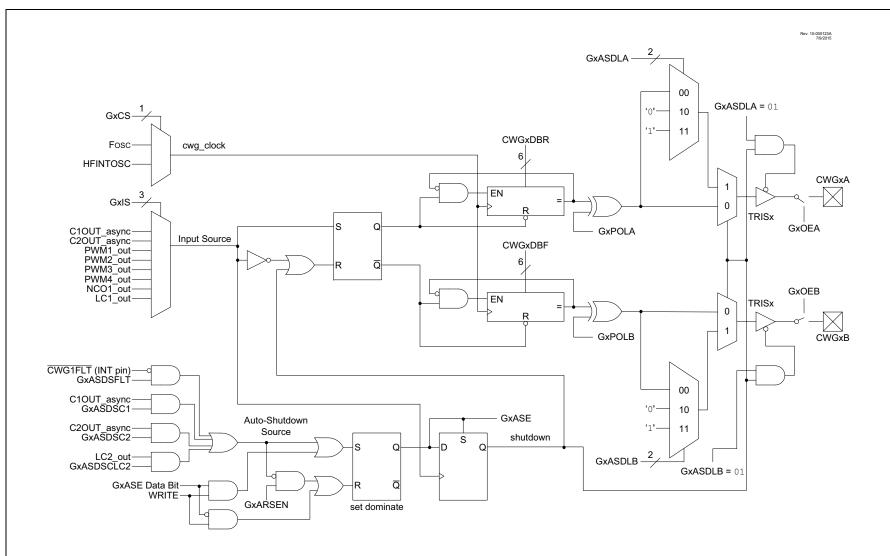

## FIGURE 26-1: SIMPLIFIED CWG BLOCK DIAGRAM

PIC16(L)F1508/9

DS40001609E-page 281

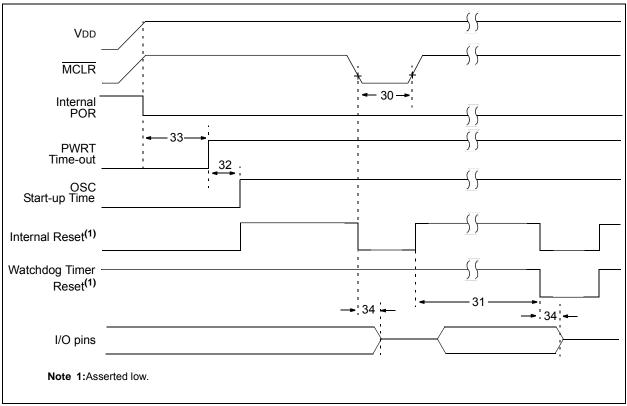

# FIGURE 29-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

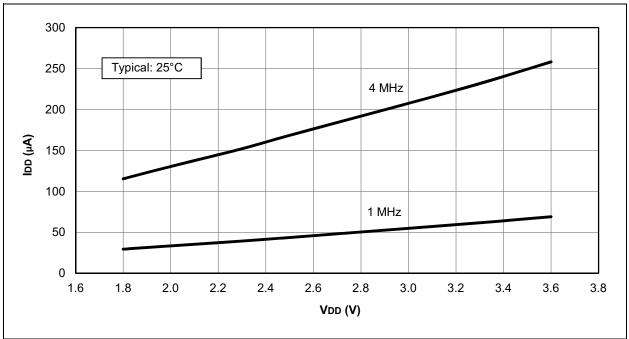

FIGURE 30-11: IDD TYPICAL, EXTERNAL CLOCK (ECM), MEDIUM POWER MODE, PIC16LF1508/9 ONLY

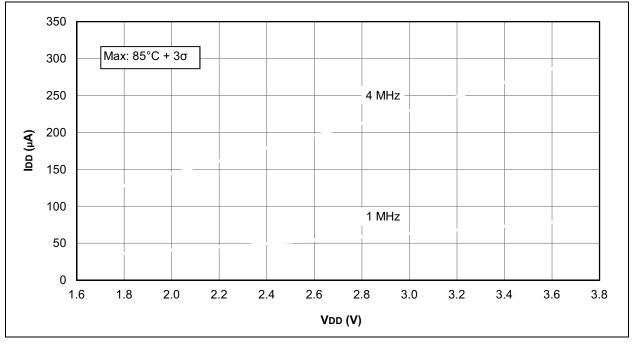

FIGURE 30-12: IDD MAXIMUM, EXTERNAL CLOCK (ECM), MEDIUM POWER MODE, PIC16LF1508/9 ONLY

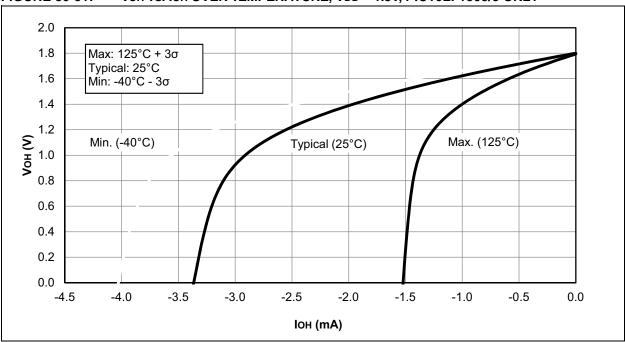

FIGURE 30-51: VOH vs. IOH OVER TEMPERATURE, VDD = 1.8V, PIC16LF1508/9 ONLY

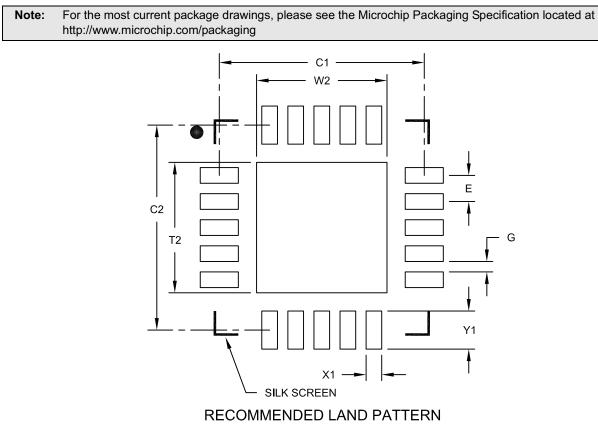

20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

|                            | Units     |      |          |      |  |

|----------------------------|-----------|------|----------|------|--|

| Dimensio                   | on Limits | MIN  | NOM      | MAX  |  |

| Contact Pitch              | E         |      | 0.50 BSC |      |  |

| Optional Center Pad Width  | W2        |      |          | 2.50 |  |

| Optional Center Pad Length | T2        |      |          | 2.50 |  |

| Contact Pad Spacing        | C1        |      | 3.93     |      |  |

| Contact Pad Spacing        | C2        |      | 3.93     |      |  |

| Contact Pad Width          | X1        |      |          | 0.30 |  |

| Contact Pad Length         |           |      |          | 0.73 |  |

| Distance Between Pads      | G         | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A