Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1508-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE OF CONTENTS

| 1.0   | Device Overview                                                           |     |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Enhanced Mid-Range CPU                                                    |     |

| 3.0   | Memory Organization                                                       |     |

| 4.0   | Device Configuration                                                      |     |

| 5.0   | Oscillator Module (With Fail-Safe Clock Monitor)                          |     |

| 6.0   | Resets                                                                    |     |

| 7.0   | Interrupts                                                                |     |

| 8.0   | Power-Down Mode (Sleep)                                                   |     |

| 9.0   | Watchdog Timer (WDT)                                                      |     |

| 10.0  | Flash Program Memory Control                                              |     |

| 11.0  | I/O Ports                                                                 | 106 |

| 12.0  | Interrupt-On-Change                                                       | 119 |

| 13.0  | Fixed Voltage Reference (FVR)                                             |     |

| 14.0  | Temperature Indicator Module                                              |     |

| 15.0  | Analog-to-Digital Converter (ADC) Module                                  |     |

| 16.0  | 5-Bit Digital-to-Analog Converter (DAC) Module                            |     |

| 17.0  | Comparator Module                                                         |     |

| 18.0  | Timer0 Module                                                             |     |

| 19.0  | Timer1 Module with Gate Control                                           |     |

|       | Timer2 Module                                                             |     |

|       | Master Synchronous Serial Port (MSSP) Module                              |     |

| 22.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |     |

| 23.0  | Pulse-Width Modulation (PWM) Module                                       |     |

| 24.0  | Configurable Logic Cell (CLC)                                             |     |

| 25.0  | Numerically Controlled Oscillator (NCO) Module                            |     |

| 26.0  | Complementary Waveform Generator (CWG) Module                             |     |

| 27.0  | In-Circuit Serial Programming™ (ICSP™)                                    |     |

| 28.0  | Instruction Set Summary                                                   |     |

| 29.0  |                                                                           |     |

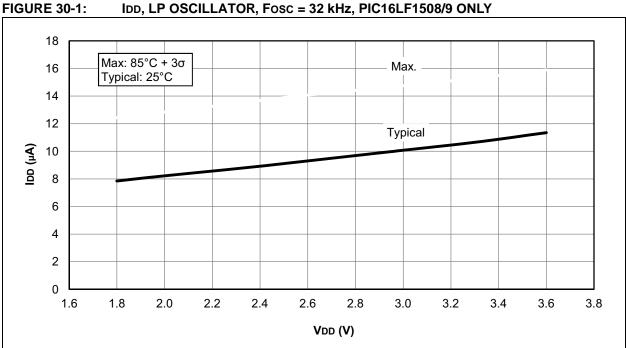

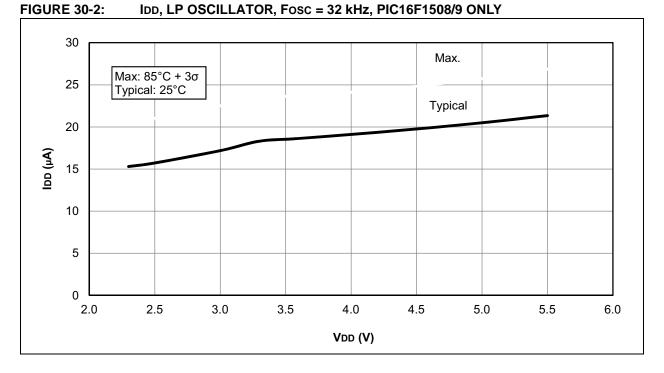

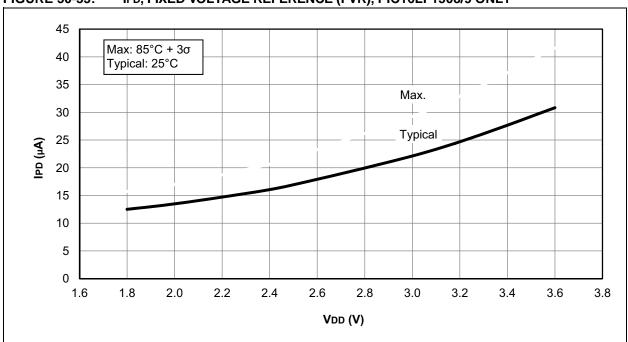

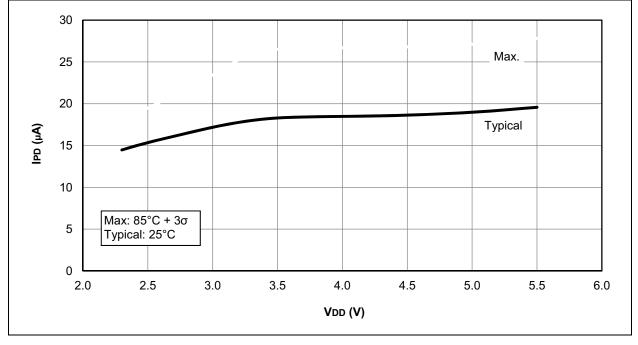

| 30.0  | DC and AC Characteristics Graphs and Charts                               |     |

| 31.0  | Development Support                                                       |     |

|       | Packaging Information                                                     |     |

| Appe  | ndix A: Data Sheet Revision History                                       |     |

| The N | Microchip Website                                                         |     |

|       | omer Change Notification Service                                          |     |

|       | omer Support                                                              |     |

| Produ | uct Identification System                                                 |     |

### TABLE 1-2: PIC16(L)F1508/9 PINOUT DESCRIPTION

| Name                                                    | Function | Input<br>Type | Output<br>Type | Description                                           |  |  |  |  |

|---------------------------------------------------------|----------|---------------|----------------|-------------------------------------------------------|--|--|--|--|

| RA0/AN0/C1IN+/DAC1OUT1/                                 | RA0      | TTL           | CMOS           | General purpose I/O.                                  |  |  |  |  |

| CSPDAT/ICDDAT                                           | AN0      | AN            | _              | ADC Channel input.                                    |  |  |  |  |

|                                                         | C1IN+    | AN            | _              | Comparator positive input.                            |  |  |  |  |

|                                                         | DAC1OUT1 | _             | AN             | Digital-to-Analog Converter output.                   |  |  |  |  |

|                                                         | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                                       |  |  |  |  |

|                                                         | ICDDAT   | ST            | CMOS           | In-Circuit Debug data.                                |  |  |  |  |

| RA1/AN1/CLC4IN1/VREF+/                                  | RA1      | TTL           | CMOS           | General purpose I/O.                                  |  |  |  |  |

| C1IN0-/C2IN0-/ICSPCLK/                                  | AN1      | AN            |                | ADC Channel input.                                    |  |  |  |  |

| CDCLK                                                   | CLC4IN1  | ST            |                | Configurable Logic Cell source input.                 |  |  |  |  |

|                                                         | VREF+    | AN            | _              | ADC Positive Voltage Reference input.                 |  |  |  |  |

|                                                         | C1IN0-   | AN            |                | Comparator negative input.                            |  |  |  |  |

|                                                         | C2IN0-   | AN            |                | Comparator negative input.                            |  |  |  |  |

|                                                         | ICSPCLK  | ST            | —              | ICSP Programming Clock.                               |  |  |  |  |

|                                                         | ICDCLK   | ST            | _              | In-Circuit Debug Clock.                               |  |  |  |  |

| RA2/AN2/C1OUT/DAC1OUT2/                                 | RA2      | ST            | CMOS           | General purpose I/O.                                  |  |  |  |  |

| TOCKI/INT/PWM3/CLC1/                                    | AN2      | AN            | _              | ADC Channel input.                                    |  |  |  |  |

| CWG1FLT                                                 | C1OUT    | _             | CMOS           | Comparator output.                                    |  |  |  |  |

|                                                         | DAC1OUT2 | _             | AN             | Digital-to-Analog Converter output.                   |  |  |  |  |

|                                                         | TOCKI    | ST            |                | Timer0 clock input.                                   |  |  |  |  |

|                                                         | INT      | ST            |                | External interrupt.                                   |  |  |  |  |

|                                                         | PWM3     | _             | CMOS           |                                                       |  |  |  |  |

|                                                         | CLC1     | _             | CMOS           | Configurable Logic Cell source output.                |  |  |  |  |

|                                                         | CWG1FLT  | ST            |                | Complementary Waveform Generator Fault input.         |  |  |  |  |

| RA3/CLC1IN0/VPP/T1G <sup>(1)</sup> /SS <sup>(1)</sup> / | RA3      | TTL           |                | General purpose input with IOC and WPU.               |  |  |  |  |

| MCLR                                                    | CLC1IN0  | ST            |                | Configurable Logic Cell source input.                 |  |  |  |  |

|                                                         | VPP      | HV            |                | Programming voltage.                                  |  |  |  |  |

|                                                         | T1G      | ST            |                | Timer1 Gate input.                                    |  |  |  |  |

|                                                         | SS       | ST            |                | Slave Select input.                                   |  |  |  |  |

|                                                         | MCLR     | ST            |                | Master Clear with internal pull-up.                   |  |  |  |  |

| RA4/AN3/SOSCO/                                          | RA4      | TTL           | CMOS           | General purpose I/O.                                  |  |  |  |  |

| CLKOUT/T1G                                              | AN3      | AN            |                | ADC Channel input.                                    |  |  |  |  |

|                                                         | SOSCO    | XTAL          | XTAL           | Secondary Oscillator Connection.                      |  |  |  |  |

|                                                         | CLKOUT   | _             | CMOS           | Fosc/4 output.                                        |  |  |  |  |

|                                                         | T1G      | ST            | _              | Timer1 Gate input.                                    |  |  |  |  |

| RA5/CLKIN/T1CKI/NCO1CLK/                                | RA5      | TTL           | CMOS           | General purpose I/O.                                  |  |  |  |  |

| SOSCI                                                   | CLKIN    | CMOS          | _              | External clock input (EC mode).                       |  |  |  |  |

|                                                         | T1CKI    | ST            | _              | Timer1 clock input.                                   |  |  |  |  |

|                                                         | NCO1CLK  | ST            |                | Numerically Controlled Oscillator Clock source input. |  |  |  |  |

|                                                         | SOSCI    | XTAL          | XTAL           |                                                       |  |  |  |  |

HV = High Voltage XTAL = Crystal

Schmitt Trigger input with levels

**Note 1:** Alternate pin function selected with the APFCON (Register 11-1) register.

## TABLE 3-6: PIC16(L)F1508/9 MEMORY MAP, BANK 24-31

|      | BANK 24                       |      | BANK 25                       |      | BANK 26                       |      | BANK 27                       |      | BANK 28                       |      | BANK 29                       |      | BANK 30                       |      | BANK 31                       |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------|

| C00h | Core Registers<br>(Table 3-2) | C80h | Core Registers<br>(Table 3-2) | D00h | Core Registers<br>(Table 3-2) | D80h | Core Registers<br>(Table 3-2) | E00h | Core Registers<br>(Table 3-2) | E80h | Core Registers<br>(Table 3-2) | F00h | Core Registers<br>(Table 3-2) | F80h | Core Registers<br>(Table 3-2) |

| C0Bh |                               | C8Bh |                               | D0Bh |                               | D8Bh |                               | E0Bh |                               | E8Bh |                               | F0Bh |                               | F8Bh |                               |

| C0Ch | —                             | C8Ch | _                             | D0Ch | —                             | D8Ch | —                             | E0Ch | _                             | E8Ch | _                             | F0Ch |                               | F8Ch |                               |

| C0Dh | —                             | C8Dh |                               | D0Dh | —                             | D8Dh | —                             | E0Dh | -                             | E8Dh | _                             | F0Dh |                               | F8Dh |                               |

| C0Eh | —                             | C8Eh | -                             | D0Eh | —                             | D8Eh | —                             | E0Eh | —                             | E8Eh | —                             | F0Eh |                               | F8Eh |                               |

| C0Fh | —                             | C8Fh | _                             | D0Fh | —                             | D8Fh | —                             | E0Fh | —                             | E8Fh | _                             | F0Fh |                               | F8Fh |                               |

| C10h | —                             | C90h | _                             | D10h | —                             | D90h | —                             | E10h | —                             | E90h | _                             | F10h |                               | F90h |                               |

| C11h | —                             | C91h | _                             | D11h | —                             | D91h | —                             | E11h | —                             | E91h | _                             | F11h |                               | F91h |                               |

| C12h | —                             | C92h | _                             | D12h | —                             | D92h | —                             | E12h | _                             | E92h | _                             | F12h |                               | F92h |                               |

| C13h | —                             | C93h | _                             | D13h | —                             | D93h | —                             | E13h | _                             | E93h | _                             | F13h |                               | F93h |                               |

| C14h | _                             | C94h | -                             | D14h | —                             | D94h | —                             | E14h | —                             | E94h | _                             | F14h |                               | F94h |                               |

| C15h | —                             | C95h | -                             | D15h | —                             | D95h | —                             | E15h | —                             | E95h | —                             | F15h |                               | F95h |                               |

| C16h | —                             | C96h | -                             | D16h | —                             | D96h | —                             | E16h | —                             | E96h | —                             | F16h |                               | F96h |                               |

| C17h | —                             | C97h | -                             | D17h | —                             | D97h | —                             | E17h | —                             | E97h | —                             | F17h | See Table 3-7 for             | F97h | See Table 3-7 for             |

| C18h | —                             | C98h | -                             | D18h | —                             | D98h | —                             | E18h | —                             | E98h | —                             | F18h | register mapping              | F98h | register mapping              |

| C19h | _                             | C99h | _                             | D19h | _                             | D99h | _                             | E19h | _                             | E99h | _                             | F19h | details                       | F99h | details                       |

| C1Ah | —                             | C9Ah | _                             | D1Ah | —                             | D9Ah | —                             | E1Ah | _                             | E9Ah | _                             | F1Ah |                               | F9Ah |                               |

| C1Bh | —                             | C9Bh |                               | D1Bh | —                             | D9Bh | —                             | E1Bh | -                             | E9Bh | _                             | F1Bh |                               | F9Bh |                               |

| C1Ch | —                             | C9Ch | -                             | D1Ch | —                             | D9Ch | —                             | E1Ch | —                             | E9Ch | —                             | F1Ch |                               | F9Ch |                               |

| C1Dh | —                             | C9Dh | -                             | D1Dh | —                             | D9Dh | —                             | E1Dh | —                             | E9Dh | —                             | F1Dh |                               | F9Dh |                               |

| C1Eh | —                             | C9Eh | _                             | D1Eh | —                             | D9Eh | —                             | E1Eh | —                             | E9Eh | _                             | F1Eh |                               | F9Eh |                               |

| C1Fh | —                             | C9Fh | _                             | D1Fh | —                             | D9Fh | —                             | E1Fh | _                             | E9Fh | _                             | F1Fh |                               | F9Fh |                               |

| C20h |                               | CA0h |                               | D20h |                               | DA0h |                               | E20h |                               | EA0h |                               | F20h |                               | FA0h |                               |

|      | Unimplemented<br>Read as '0'  |      |                               |      |                               |

| C6Fh |                               | CEFh |                               | D6Fh |                               | DEFh |                               | E6Fh |                               | EEFh |                               | F6Fh |                               | FEFh |                               |

| C70h |                               | CF0h |                               | D70h |                               | DF0h |                               | E70h |                               | EF0h |                               | F70h |                               | FF0h |                               |

| 2.50 | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |

| CFFh |                               | CFFh |                               | D7Fh |                               | DFFh |                               | E7Fh |                               | EFFh |                               | F7Fh |                               | FFFh |                               |

Legend: = Unimplemented data memory locations, read as '0'.

#### **TABLE 3-9:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| INDEE     |                 |               |                             |                |               |             |        | 020/    |        |                      |                                 |  |  |  |

|-----------|-----------------|---------------|-----------------------------|----------------|---------------|-------------|--------|---------|--------|----------------------|---------------------------------|--|--|--|

| Address   | Name            | Bit 7         | Bit 6                       | Bit 5          | Bit 4         | Bit 3       | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |  |  |  |

| Bank 3    | Bank 31         |               |                             |                |               |             |        |         |        |                      |                                 |  |  |  |

| F8Ch      | —               | Unimplemen    | ted                         |                |               |             |        |         |        | —                    | —                               |  |  |  |

| —<br>FE3h |                 |               |                             |                |               |             |        |         |        |                      |                                 |  |  |  |

| FE4h      | STATUS_<br>SHAD | _             | —                           | -              | _             | —           | Z_SHAD | DC_SHAD | C_SHAD | xxx                  | uuu                             |  |  |  |

| FE5h      | WREG_<br>SHAD   | Working Reg   | jister Shadow               |                |               |             |        |         |        | XXXX XXXX            | uuuu uuuu                       |  |  |  |

| FE6h      | BSR_<br>SHAD    | —             | —                           | _              | Bank Select   | Register Sh | adow   |         |        | x xxxx               | u uuuu                          |  |  |  |

| FE7h      | PCLATH_<br>SHAD | _             | Program Co                  | unter Latch H  | ligh Register | Shadow      |        |         |        | -xxx xxxx            | uuuu uuuu                       |  |  |  |

| FE8h      | FSR0L_<br>SHAD  | Indirect Data | Memory Add                  | lress 0 Low F  | Pointer Shado | W           |        |         |        | XXXX XXXX            | uuuu uuuu                       |  |  |  |

| FE9h      | FSR0H_<br>SHAD  | Indirect Data | Memory Add                  | lress 0 High I | Pointer Shade | ow          |        |         |        | XXXX XXXX            | uuuu uuuu                       |  |  |  |

| FEAh      | FSR1L_<br>SHAD  | Indirect Data | Memory Add                  | lress 1 Low F  | Pointer Shado | W           |        |         |        | XXXX XXXX            | uuuu uuuu                       |  |  |  |

| FEBh      | FSR1H_<br>SHAD  | Indirect Data | Memory Add                  | lress 1 High I | Pointer Shade | W           |        |         |        | XXXX XXXX            | uuuu uuuu                       |  |  |  |

| FECh      | —               | Unimplemen    | Inimplemented               |                |               |             |        |         |        |                      | —                               |  |  |  |

| FEDh      | STKPTR          | _             | — — — Current Stack Pointer |                |               |             |        |         |        |                      | 1 1111                          |  |  |  |

| FEEh      | TOSL            | Top-of-Stack  | Low byte                    |                |               |             |        |         |        | XXXX XXXX            | uuuu uuuu                       |  |  |  |

| FEFh      | TOSH            | —             | Top-of-Stack                | High byte      |               |             |        |         |        | -xxx xxxx            | -uuu uuuu                       |  |  |  |

Legend:

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16F1508/9 only.

2:

Unimplemented, read as '1'.

## REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH:External clock, High-Power mode: on CLKIN pin

- 110 = ECM: External clock, Medium Power mode: on CLKIN pin

- 101 = ECL: External clock, Low-Power mode: on CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

#### Note 1: When FSCM is enabled, Two-Speed Start-up will be automatically enabled, regardless of the IESO bit value.

- 2: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 3: Once enabled, code-protect can only be disabled by bulk erasing the device.

| Fosc      | VVVV<br>Q1 Q2 Q3 Q4 | \\\\\<br> a1 a2 a3 a4 | /////<br> a1 a2 a3 a4 | \_\_\_<br> 01 02 03 04 |                                       | /////<br>  Q1   Q2   Q3   Q4 | \<br> 01 02 03 04 | MMM<br> Q1 Q2 Q3 Q4 |

|-----------|---------------------|-----------------------|-----------------------|------------------------|---------------------------------------|------------------------------|-------------------|---------------------|

|           |                     |                       | Interru<br>during     | pt Sampled<br>Q1       |                                       |                              |                   |                     |

| Interrupt |                     |                       |                       |                        |                                       |                              |                   |                     |

| GIE       |                     |                       |                       |                        |                                       |                              |                   |                     |

| PC        | PC-1                | РС                    | PC                    | +1                     | 0004h                                 | 0005h                        |                   |                     |

| Execute   | 1-Cycle Insti       | ruction at PC         | Inst(PC)              | NOP                    | NOP                                   | Inst(0004h)                  |                   |                     |

|           |                     |                       |                       |                        |                                       |                              |                   |                     |

| Interrupt |                     |                       |                       |                        |                                       |                              |                   |                     |

| GIE       |                     |                       |                       |                        |                                       |                              |                   |                     |

|           | (                   |                       | PC+1/FSR              | \<br>/ New PC/         | · · · · · · · · · · · · · · · · · · · |                              |                   | ,                   |

| PC        | PC-1                | PC                    | ADDR                  | PC+1                   | 0004h                                 | 0005h                        |                   | ·                   |

| Execute   | 2-Cycle Inst        | ruction at PC         | Inst(PC)              | NOP                    | NOP                                   | Inst(0004h)                  |                   |                     |

|           |                     |                       |                       |                        |                                       |                              |                   |                     |

| Interrupt |                     |                       |                       |                        |                                       |                              |                   |                     |

| GIE       |                     |                       |                       |                        |                                       |                              |                   |                     |

| 50        |                     |                       |                       |                        |                                       | 000.45                       | 00055             | ,                   |

| PC        | PC-1                | PC                    | FSR ADDR              | PC+1                   | PC+2                                  | 0004h                        | 0005h             | ۱ <u> </u>          |

| Execute   | 3-Cycle Inst        | ruction at PC         | INST(PC)              | NOP                    | NOP                                   | NOP                          | Inst(0004h)       | Inst(0005h)         |

| Interrupt |                     |                       |                       |                        | /                                     |                              |                   |                     |

| GIE       |                     |                       |                       |                        |                                       | +                            |                   |                     |

|           | PC-1                |                       |                       |                        |                                       | 0+2                          | 0004h             | 0005h               |

| PC        |                     | PC                    | FSR ADDR              | PC+1                   | M                                     | Y' <sup>2</sup>              | 000411            | 000511              |

| Execute   | 3-Cycle Inst        | ruction at PC         | INST(PC)              | NOP                    | NOP                                   | NOP                          | NOP               | Inst(0004h)         |

|           |                     |                       |                       |                        |                                       |                              |                   |                     |

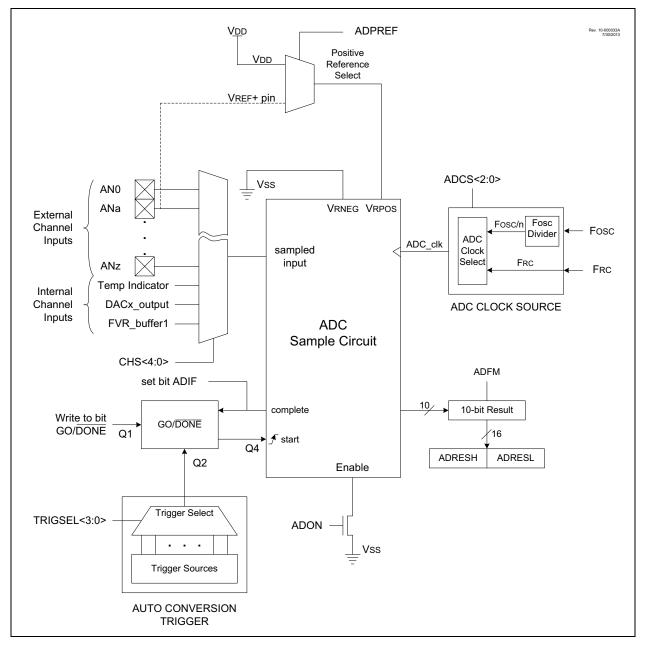

## 15.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive

FIGURE 15-1: ADC BLOCK DIAGRAM

approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 15-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

## 19.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 19.4 Timer1 (Secondary) Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal. The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires some time to start-up and stabilize before use. The SOSCR bit in the OSCSTAT register monitors the oscillator and indicates when the oscillator is ready for use. When T1OSCEN is set, the SOSCR bit is cleared. After 1024 cycles of the oscillator are countered, the SOSCR bit is set, indicating that the oscillator should be stable and ready for use.

## 19.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 19.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 19.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads. For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 19.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 19.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 19-3 for timing details.

## TABLE 19-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 19.6.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 19-4. Source selection is controlled by the T1GSS<1:0> bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

| TABLE 19-4: | TIMER1 GATE SOURCES |

|-------------|---------------------|

|-------------|---------------------|

| T1GSS   | Timer1 Gate Source                                                    |

|---------|-----------------------------------------------------------------------|

| 00      | Timer1 Gate pin (T1G)                                                 |

| 01      | Overflow of Timer0 (T0_overflow)<br>(TMR0 increments from FFh to 00h) |

| 10      | Comparator 1 Output (C1OUT_sync) <sup>(1)</sup>                       |

| 11      | Comparator 2 Output (C2OUT_sync) <sup>(1)</sup>                       |

| Nata di |                                                                       |

Note 1: Optionally synchronized comparator output.

#### 21.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 21-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCLx line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- Slave software reads ACKTIM bit of SSPxCON3 register, and R/W and D/A of the SSPxSTAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCLx.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

Note: SSPxBUF cannot be loaded until after the ACK.

- 13. Slave sets the CKP bit, releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the ninth SCLx pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not ACK the slave releases the bus allowing the master to send a Stop and end the communication.

**Note:** Master must send a not ACK on the last byte to ensure that the slave releases the SCLx line to receive a Stop.

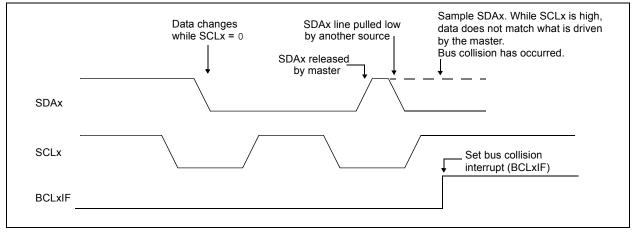

#### FIGURE 21-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

### REGISTER 21-2: SSPxCON1: SSP CONTROL REGISTER 1

| R/C/HS-0/        | 0 R/C/HS-0/0                                                                                                                                                                                                                                                                                              | R/W-0/0                                                                                                                    | R/W-0/0                                                                                                                                                                                                             | R/W-0/0                                                                                                                   | R/W-0/0                                                               | R/W-0/0                                                                                              | R/W-0/0                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------|

| WCOL             | SSPOV <sup>(1)</sup>                                                                                                                                                                                                                                                                                      | SSPEN                                                                                                                      | CKP                                                                                                                                                                                                                 |                                                                                                                           | SSPI                                                                  | M<3:0>                                                                                               |                                             |

| bit 7            |                                                                                                                                                                                                                                                                                                           |                                                                                                                            |                                                                                                                                                                                                                     |                                                                                                                           |                                                                       |                                                                                                      | bit (                                       |

|                  |                                                                                                                                                                                                                                                                                                           |                                                                                                                            |                                                                                                                                                                                                                     |                                                                                                                           |                                                                       |                                                                                                      |                                             |

| Legend:          |                                                                                                                                                                                                                                                                                                           |                                                                                                                            |                                                                                                                                                                                                                     |                                                                                                                           |                                                                       |                                                                                                      |                                             |

| R = Readable     |                                                                                                                                                                                                                                                                                                           | W = Writable bit                                                                                                           |                                                                                                                                                                                                                     | •                                                                                                                         | nted bit, read as '0'                                                 |                                                                                                      |                                             |

| u = Bit is unch  | 0                                                                                                                                                                                                                                                                                                         | x = Bit is unknow                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                           | OR and BOR/Value                                                      |                                                                                                      |                                             |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                           | '0' = Bit is cleared                                                                                                       | d                                                                                                                                                                                                                   | HS = Bit is set b                                                                                                         | y hardware                                                            | C = User cleared                                                                                     |                                             |

| bit 7            | 0 = No collisior<br><u>Slave mode:</u>                                                                                                                                                                                                                                                                    | he SSPxBUF regisi<br>ו<br>UF register is writter                                                                           | ·                                                                                                                                                                                                                   |                                                                                                                           | ditions were not valio<br>s word (must be clear                       | d for a transmission<br>ed in software)                                                              | o be started                                |

| bit 6            | In SPI mode:<br>1 = A new byte<br>Overflow ca<br>setting over<br>SSPxBUF rr<br>0 = No overflow<br>In I <sup>2</sup> C mode:<br>1 = A byte is re                                                                                                                                                           | an only occur in Slav<br>flow. In Master mode<br>register (must be cle<br>w<br>eccived while the S<br>leared in software). | e SSPxBUF registe<br>ve mode. In Slave<br>e, the overflow bit i<br>vared in software).                                                                                                                              | mode, the user mus<br>is not set since each                                                                               | st read the SSPxBUF<br>new reception (and t                           | of overflow, the data<br>, even if only transmit<br>ransmission) is initiate<br>OV is a "don't care" | ting data, to avoid<br>ed by writing to the |

| bit 5            | In both modes, w<br>In <u>SPI mode:</u><br>1 = Enables se<br>0 = Disables se<br>In I <sup>2</sup> C mode:<br>1 = Enables the                                                                                                                                                                              | erial port and config                                                                                                      | e pins must be pro<br>res SCKx, SDOx,<br>gures these pins a<br>figures the SDAx a                                                                                                                                   | SDIx and SSx as the as I/O port pins as the                                                                               | s input or output<br>e source of the serial<br>e source of the serial |                                                                                                      |                                             |

| bit 4            | CKP: Clock Pola<br>In <u>SPI mode</u> :<br>1 = Idle state for<br>0 = Idle state for<br>In I <sup>2</sup> C Slave mod<br>SCLx release co<br>1 = Enable clock                                                                                                                                               | rity Select bit<br>clock is a high leve<br>clock is a low level<br><u>le:</u><br>ntrol<br>ow (clock stretch).              | 1                                                                                                                                                                                                                   |                                                                                                                           |                                                                       |                                                                                                      |                                             |

| bit 3-0          | 0000 = SPI Mas<br>0001 = SPI Mas<br>0010 = SPI Mas<br>0011 = SPI Mas<br>0100 = SPI Slav<br>0101 = SPI Slav<br>0101 = I <sup>2</sup> C Slave<br>1000 = I <sup>2</sup> C Mas<br>1001 = Reservet<br>1010 = SPI Mas<br>1011 = I <sup>2</sup> C firmw<br>1100 = Reservet<br>1101 = Reservet<br>1101 = Reservet | e mode, 7-bit addre<br>e mode, 10-bit addr<br>er mode, clock = F<br>d<br>ter mode, clock = F<br>vare controlled Mas<br>d   | osc/4<br>osc/16<br>osc/64<br>2_match/2<br>Xx pin, <u>SS</u> pin co<br>Xx pin, <u>SS</u> pin co<br>Xx pin, <u>SS</u> pin co<br>Ss<br>cosc/(4 * (SSPxAI<br>osc/(4 * (SSPxAI<br>ter mode (Slave i<br>ss with Start and | ontrol enabled<br>ontrol disabled, SS:<br>DD+1)) <sup>(4)</sup><br>DD+1)) <sup>(5)</sup><br>dle)<br>Stop bit interrupts ( |                                                                       | ) pin                                                                                                |                                             |

| 2:<br>3:         | In Master mode, the ov<br>When enabled, these p<br>When enabled, the SD/<br>SSPxADD values of 0,                                                                                                                                                                                                          | erflow bit is not set<br>ins must be proper<br>Ax and SCLx pins r                                                          | since each new i<br>ly configured as i<br>nust be configure                                                                                                                                                         | reception (and trans<br>nput or output.<br>d as inputs.                                                                   |                                                                       | by writing to the SS                                                                                 | PxBUF register.                             |

- 5: SSPxADD value of '0' is not supported. Use SSPM = 0000 instead.

## REGISTER 21-5: SSPxMSK: SSP MASK REGISTER

| R/W-1/1          | R/W-1/1                                  | R/W-1/1                                                                                  | R/W-1/1                           | R/W-1/1                                         | R/W-1/1                               | R/W-1/1                    | R/W-1/1      |

|------------------|------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------|---------------------------------------|----------------------------|--------------|

|                  |                                          |                                                                                          | MSK                               | <<7:0>                                          |                                       |                            |              |

| bit 7            |                                          |                                                                                          |                                   |                                                 |                                       |                            | bit 0        |

|                  |                                          |                                                                                          |                                   |                                                 |                                       |                            |              |

| Legend:          |                                          |                                                                                          |                                   |                                                 |                                       |                            |              |

| R = Readable     | e bit                                    | W = Writable                                                                             | bit                               | U = Unimpler                                    | nented bit, read                      | l as '0'                   |              |

| u = Bit is unc   | u = Bit is unchanged x = Bit is unknown  |                                                                                          |                                   | -n/n = Value a                                  | at POR and BO                         | R/Value at all o           | other Resets |

| '1' = Bit is set |                                          | '0' = Bit is cle                                                                         | ared                              |                                                 |                                       |                            |              |

| bit 7-1          | MSK<7:1>:                                | Mack bite                                                                                |                                   |                                                 |                                       |                            |              |

| DIL 7-1          | 1 = The rec                              | eived address b<br>eived address b                                                       | it n is compar<br>it n is not use | red to SSPxADI<br>ed to detect I <sup>2</sup> C | D <n> to detect<br/>address match</n> | I <sup>2</sup> C address m | atch         |

| bit 0            | I <sup>2</sup> C Slave me<br>1 = The rec | ask bit for I <sup>2</sup> C S<br>ode, 10-bit addr<br>eived address b<br>eived address b | ess (SSPM<3<br>it 0 is compar     | 3:0> = 0111 or<br>red to SSPxADI                | D<0> to detect                        |                            | atch         |

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

## REGISTER 21-6: SSPxADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0                                 | R/W-0/0                           | R/W-0/0           | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-----------------------------------------|-----------------------------------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|--|

|                                         |                                   |                   | ADD                                                   | <7:0>                              |         |         |         |  |  |

| bit 7                                   |                                   |                   |                                                       |                                    |         |         | bit 0   |  |  |

|                                         |                                   |                   |                                                       |                                    |         |         |         |  |  |

| Legend:                                 |                                   |                   |                                                       |                                    |         |         |         |  |  |

| R = Readable                            | R = Readable bit W = Writable bit |                   | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |                                   | iown              | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |  |

| '1' = Bit is set                        |                                   | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |  |

#### Master mode:

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits SCLx pin clock period = ((ADD<7:0> + 1) \*4)/Fosc

#### <u>10-Bit Slave mode – Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### 10-Bit Slave mode – Least Significant Address Byte:

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

### 24.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 24-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

TABLE 24-2: DATA GATING LOGIC

| CLCxGLS0 | LCxG1POL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 24-5)

- Gate 2: CLCxGLS1 (Register 24-6)

- Gate 3: CLCxGLS2 (Register 24-7)

- Gate 4: CLCxGLS3 (Register 24-8)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 24-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

### 24.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 24-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

## 24.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

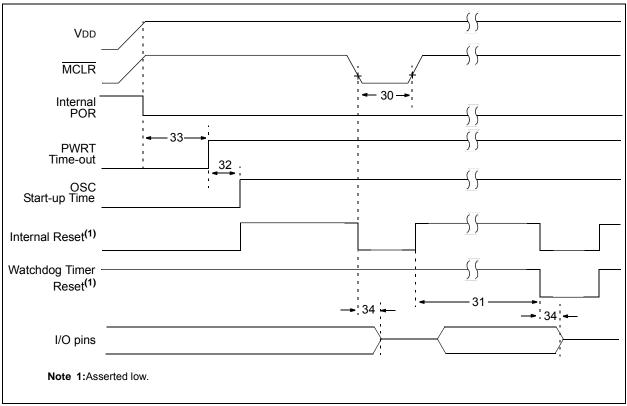

## FIGURE 29-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

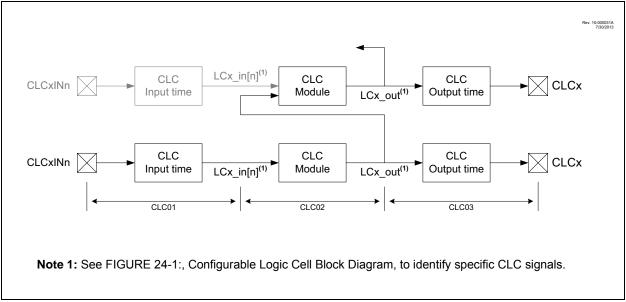

| TABLE 29-12: | CONFIGURATION LOGIC CELL (CLC) CHARACTERISTICS |

|--------------|------------------------------------------------|

|--------------|------------------------------------------------|

| Standard Operating Conditions (unless otherwise stated) |         |                                             |   |          |      |          |                          |  |

|---------------------------------------------------------|---------|---------------------------------------------|---|----------|------|----------|--------------------------|--|

| Param.<br>No. Sym.                                      |         | Characteristic                              |   | Тур†     | Max. | Units    | Conditions               |  |

| CLC01*                                                  | TCLCIN  | CLC input time                              |   | 7        | _    | ns       |                          |  |

| CLC02*                                                  | TCLC    | CLC module input to output propagation time |   | 24<br>12 |      | ns<br>ns | VDD = 1.8V<br>VDD > 3.6V |  |

| CLC03*                                                  | TCLCOUT | CLC output time Rise Time                   |   | OS18     |      |          | (Note 1)                 |  |

|                                                         |         | Fall Time                                   | _ | OS19     |      | —        | (Note 1)                 |  |

| CLC04*                                                  | FCLCMAX | CLC maximum switching frequency             |   | 45       | _    | MHz      |                          |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1:See Table 29-9 for OS18 and OS19 rise and fall times.

## DS40001609E-page 340

FIGURE 30-35: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC16LF1508/9 ONLY

## APPENDIX A: DATA SHEET REVISION HISTORY

## Revision A (10/2011)

Original release.

## Revision B (6/2013)

Updated Electrical Specifications and added Characterization Data.

## Revision C (7/2013)

Corrected upper and lower bit definitions of address, Section 3.2. Added clarification of Buffer Gain Selection bits, Section 13.2. Removed "Preliminary" status from Section 30. Updated Figures 15-1, 29-9. Clarified information in Registers 7-1,13-1, 15-2. Clarified information in Tables 29-5, 29-10, 29-13. Removed Index.

### **Revision D (10/2014)**

Document re-release.

### **Revision E (10/2015)**

Added Section 3.2 High-Endurance Flash. Updated Figure 26-1; Registers 4-2, 7-5, and 26-3; Sections 22.4.2, 24.1.5, 26.9.1.2, 26.11.1, and 29.1; and Table 26-2.

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-63277-918-2

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370