Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1509-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

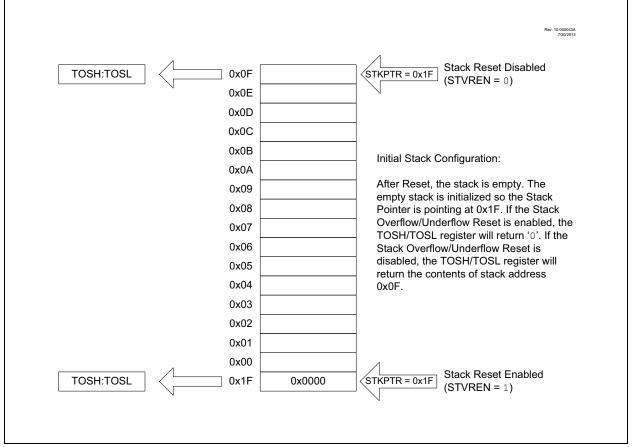

#### 3.5 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figures 3-4 through 3-7). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

#### 3.5.1 ACCESSING THE STACK

The stack is available through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is 5 bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time STKPTR can be inspected to see how much stack is left. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will unload the PC and then decrement the STKPTR.

Reference Figure 3-4 through Figure 3-7 for examples of accessing the stack.

## FIGURE 3-4: ACCESSING THE STACK EXAMPLE 1

#### REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1 (CONTINUED)

- bit 2-0 FOSC<2:0>: Oscillator Selection bits

- 111 = ECH:External clock, High-Power mode: on CLKIN pin

- 110 = ECM: External clock, Medium Power mode: on CLKIN pin

- 101 = ECL: External clock, Low-Power mode: on CLKIN pin

- 100 = INTOSC oscillator: I/O function on CLKIN pin

- 011 = EXTRC oscillator: External RC circuit connected to CLKIN pin

- 010 = HS oscillator: High-speed crystal/resonator connected between OSC1 and OSC2 pins

- 001 = XT oscillator: Crystal/resonator connected between OSC1 and OSC2 pins

- 000 = LP oscillator: Low-power crystal connected between OSC1 and OSC2 pins

#### Note 1: When FSCM is enabled, Two-Speed Start-up will be automatically enabled, regardless of the IESO bit value.

- 2: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 3: Once enabled, code-protect can only be disabled by bulk erasing the device.

#### SCS<1:0> = 00:

Change the SCS bits in the OSCCON register to select the FOSC Configuration Word clock selection. Since the OST is not applicable with external clocks, the clock module will immediately switch to the external clock, and the fail-safe condition will be cleared.

If the Fail-Safe condition still exists, the OSFIF bit will again be set by hardware.

#### 5.5.3.3 Secondary Oscillator with SCS<1:0> = 01

When a Fail-Safe condition occurs with the clock switch selected to run from the Secondary Oscillator selection (SCS < 1:0 > = 01), regardless of the FOSC selection, the condition is cleared by performing the following procedure.

#### SCS<1:0> = 01 (Secondary Oscillator)

SCS<1:0> = 1x:

Change the SCS bits in the OSCCON register to select the internal oscillator block.

OSFIF = 0:

Clear the OSFIF bit in the PIR2 register.

Read SOSCR:

The OST is not used with the secondary oscillator, therefore, the user must determine if the secondary oscillator is ready by monitoring the SOSCR bit in the OSCSTAT register. When the SOSCR bit is set, the secondary oscillator is ready.

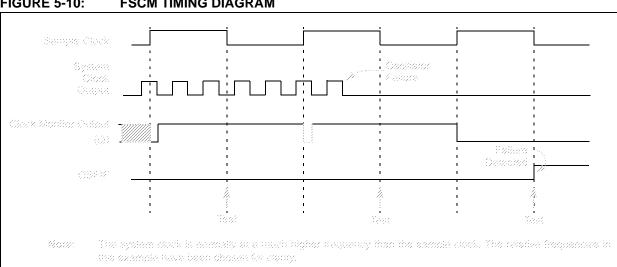

#### **FIGURE 5-10:** FSCM TIMING DIAGRAM

SCS<1:0> = 01:

Change the SCS bits in the OSCCON register to select the secondary oscillator. The clock module will immediately switch to the secondary oscillator and the fail-safe condition will be cleared.

If the Fail-Safe condition still exists, the OSFIF bit will again be set by hardware.

#### RESET OR WAKE-UP FROM SLEEP 5.5.4

The FSCM is designed to detect external oscillator or external clock failures.

When FSCM is used with an external oscillator, the Oscillator Start-up Timer (OST) count must expire before the FSCM becomes active. The OST is used after waking up from Sleep and after any type of Reset.

When the FSCM is used with external clocks, the OST is not used and the FSCM will be active as soon as the Reset or wake-up has completed.

When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Due to the wide range of oscillator start-up Note: times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep).

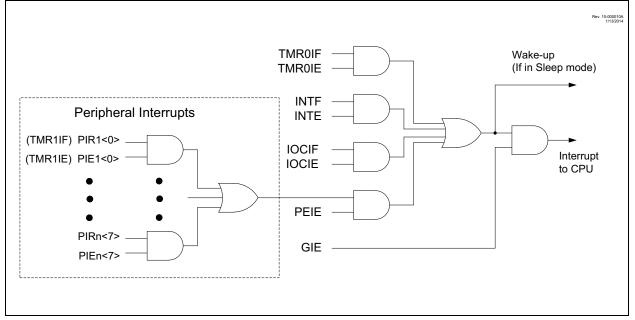

# 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

# PIC16(L)F1508/9

| Fosc      | VVVV<br>Q1 Q2 Q3 Q4 | \\\\\<br> a1 a2 a3 a4 | /////<br> a1 a2 a3 a4 | \_\_\_<br> a1 a2 a3 a4 |                                       | /////<br>  Q1   Q2   Q3   Q4 | \<br> 01 02 03 04 | MMM<br> Q1 Q2 Q3 Q4 |

|-----------|---------------------|-----------------------|-----------------------|------------------------|---------------------------------------|------------------------------|-------------------|---------------------|

|           |                     |                       | Interru<br>during     | pt Sampled<br>Q1       |                                       |                              |                   |                     |

| Interrupt |                     |                       |                       |                        |                                       |                              |                   |                     |

| GIE       |                     |                       |                       |                        |                                       |                              |                   |                     |

| PC        | PC-1                | РС                    | PC                    | +1                     | 0004h                                 | 0005h                        |                   |                     |

| Execute   | 1-Cycle Insti       | ruction at PC         | Inst(PC)              | NOP                    | NOP                                   | Inst(0004h)                  |                   |                     |

|           |                     |                       |                       |                        |                                       |                              |                   |                     |

| Interrupt |                     |                       |                       |                        |                                       |                              |                   |                     |

| GIE       |                     |                       |                       |                        |                                       |                              |                   |                     |

|           | (                   |                       | PC+1/FSR              | \<br>/ New PC/         | · · · · · · · · · · · · · · · · · · · |                              |                   | ,                   |

| PC        | PC-1                | PC                    | ADDR                  | PC+1                   | 0004h                                 | 0005h                        |                   | ·<br>               |

| Execute   | 2-Cycle Inst        | ruction at PC         | Inst(PC)              | NOP                    | NOP                                   | Inst(0004h)                  |                   |                     |

|           |                     |                       |                       |                        |                                       |                              |                   |                     |

| Interrupt |                     |                       |                       |                        |                                       |                              |                   |                     |

| GIE       |                     |                       |                       |                        |                                       |                              |                   |                     |

| 50        |                     |                       |                       |                        |                                       | 000.41                       | 00055             | ,                   |

| PC        | PC-1                | PC                    | FSR ADDR              | PC+1                   | PC+2                                  | 0004h                        | 0005h             | ۱ <u> </u>          |

| Execute   | 3-Cycle Inst        | ruction at PC         | INST(PC)              | NOP                    | NOP                                   | NOP                          | Inst(0004h)       | Inst(0005h)         |

| Interrupt |                     |                       |                       |                        | /                                     |                              |                   |                     |

| GIE       |                     |                       |                       |                        |                                       | +                            |                   |                     |

|           | PC-1                |                       |                       |                        |                                       | 0+2                          | 0004h             | 0005h               |

| PC        |                     | PC                    | FSR ADDR              | PC+1                   | M                                     | Y' <sup>2</sup>              | 000411            | 000511              |

| Execute   | 3-Cycle Inst        | ruction at PC         | INST(PC)              | NOP                    | NOP                                   | NOP                          | NOP               | Inst(0004h)         |

|           |                     |                       |                       |                        |                                       |                              |                   |                     |

| R/W-0/0          | R/W-0/0                                                                                                       | R/W-0/0                                                                       | R/W-0/0          | R/W-0/0          | U-0              | R/W-0/0          | R/W-0/0     |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------|------------------|------------------|------------------|-------------|--|--|--|

| TMR1GIE          | ADIE                                                                                                          | RCIE                                                                          | TXIE             | SSP1IE           | —                | TMR2IE           | TMR1IE      |  |  |  |

| bit 7            |                                                                                                               |                                                                               |                  |                  |                  |                  | bit (       |  |  |  |

| Legend:          |                                                                                                               |                                                                               |                  |                  |                  |                  |             |  |  |  |

| R = Readable     | hit                                                                                                           | W = Writable                                                                  | hit              | II – Unimpler    | nented bit, read | 1 26 (0)         |             |  |  |  |

| u = Bit is unch  |                                                                                                               | x = Bit is unkr                                                               |                  | •                |                  | R/Value at all o | thar Resots |  |  |  |

| '1' = Bit is set | ungeu                                                                                                         | '0' = Bit is cle                                                              |                  |                  |                  |                  |             |  |  |  |

|                  |                                                                                                               |                                                                               |                  |                  |                  |                  |             |  |  |  |

| bit 7            | TMR1GIE: T                                                                                                    | imer1 Gate Inte                                                               | errupt Enable I  | oit              |                  |                  |             |  |  |  |

|                  | 1 = Enables                                                                                                   | the Timer1 gate                                                               | e acquisition ir | nterrupt         |                  |                  |             |  |  |  |

|                  | 0 = Disables                                                                                                  | the Timer1 gate                                                               | e acquisition i  | nterrupt         |                  |                  |             |  |  |  |

| bit 6            | t 6 ADIE: Analog-to-Digital Converter (ADC) Interrupt Enable bit                                              |                                                                               |                  |                  |                  |                  |             |  |  |  |

|                  |                                                                                                               | the ADC interru                                                               |                  |                  |                  |                  |             |  |  |  |

|                  | 0 = Disables the ADC interrupt                                                                                |                                                                               |                  |                  |                  |                  |             |  |  |  |

| bit 5            |                                                                                                               | RCIE: USART Receive Interrupt Enable bit                                      |                  |                  |                  |                  |             |  |  |  |

|                  | <ul> <li>1 = Enables the USART receive interrupt</li> <li>0 = Disables the USART receive interrupt</li> </ul> |                                                                               |                  |                  |                  |                  |             |  |  |  |

| bit 4            |                                                                                                               |                                                                               | -                |                  |                  |                  |             |  |  |  |

|                  |                                                                                                               | : USART Transmit Interrupt Enable bit<br>Enables the USART transmit interrupt |                  |                  |                  |                  |             |  |  |  |

|                  | 0 = Disables the USART transmit interrupt                                                                     |                                                                               |                  |                  |                  |                  |             |  |  |  |

| bit 3            | SSP1IE: Syr                                                                                                   | nchronous Seria                                                               | I Port (MSSP     | ) Interrupt Enat | ole bit          |                  |             |  |  |  |

|                  | 1 = Enables the MSSP interrupt                                                                                |                                                                               |                  |                  |                  |                  |             |  |  |  |

|                  |                                                                                                               | the MSSP inter                                                                | •                |                  |                  |                  |             |  |  |  |

| bit 2            | -                                                                                                             | nted: Read as '                                                               |                  |                  |                  |                  |             |  |  |  |

| bit 1            |                                                                                                               | IR2 to PR2 Mat                                                                |                  |                  |                  |                  |             |  |  |  |

|                  |                                                                                                               | the Timer2 to P                                                               |                  |                  |                  |                  |             |  |  |  |

| bit 0            |                                                                                                               | the Timer2 to F                                                               |                  | •                |                  |                  |             |  |  |  |

|                  |                                                                                                               | ner1 Overflow Ir<br>the Timer1 over                                           | •                |                  |                  |                  |             |  |  |  |

|                  |                                                                                                               | the Timer1 ove                                                                |                  |                  |                  |                  |             |  |  |  |

|                  |                                                                                                               |                                                                               |                  |                  |                  |                  |             |  |  |  |

| Note: Bit        | PEIE of the IN                                                                                                | ITCON register                                                                | must he          |                  |                  |                  |             |  |  |  |

|                  |                                                                                                               | peripheral inter                                                              |                  |                  |                  |                  |             |  |  |  |

#### REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0/0          | R/W-0/0         | R/W-0/0                                                          | U-0           | R/W-0/0          | R/W-0/0          | U-0              | U-0          |  |  |  |

|------------------|-----------------|------------------------------------------------------------------|---------------|------------------|------------------|------------------|--------------|--|--|--|

| OSFIE            | C2IE            | C1IE                                                             | —             | BCL1IE           | NCO1IE           | _                | _            |  |  |  |

| bit 7            |                 |                                                                  |               |                  | 1 1              |                  | bit 0        |  |  |  |

|                  |                 |                                                                  |               |                  |                  |                  |              |  |  |  |

| Legend:          |                 |                                                                  |               |                  |                  |                  |              |  |  |  |

| R = Readable     | e bit           | W = Writable                                                     | bit           | U = Unimpler     | mented bit, read | as '0'           |              |  |  |  |

| u = Bit is unch  | nanged          | x = Bit is unkr                                                  | nown          | -n/n = Value a   | at POR and BOF   | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set |                 | '0' = Bit is clea                                                | ared          |                  |                  |                  |              |  |  |  |

|                  |                 |                                                                  |               |                  |                  |                  |              |  |  |  |

| bit 7            |                 | lator Fail Interru                                               | •             | t                |                  |                  |              |  |  |  |

|                  |                 | the Oscillator F<br>the Oscillator F                             |               |                  |                  |                  |              |  |  |  |

| bit 6            |                 |                                                                  |               | t                |                  |                  |              |  |  |  |

| bit o            | •               | parator C2 Interrupt Enable bit<br>s the Comparator C2 interrupt |               |                  |                  |                  |              |  |  |  |

|                  |                 | the Comparate                                                    | •             |                  |                  |                  |              |  |  |  |

| bit 5            | C1IE: Compa     | arator C1 Interru                                                | upt Enable bi | t                |                  |                  |              |  |  |  |

|                  |                 | the Comparato                                                    |               |                  |                  |                  |              |  |  |  |

|                  |                 | the Comparato                                                    | •             | ot               |                  |                  |              |  |  |  |

| bit 4            | Unimplemen      | Unimplemented: Read as '0'                                       |               |                  |                  |                  |              |  |  |  |

| bit 3            |                 | SP Bus Collisio                                                  |               |                  |                  |                  |              |  |  |  |

|                  |                 | the MSSP Bus                                                     |               |                  |                  |                  |              |  |  |  |

| bit 2            |                 | the MSSP Bus                                                     |               | •                | bla bit          |                  |              |  |  |  |

| DIL 2            |                 | the NCO interr                                                   |               | or Interrupt Ena |                  |                  |              |  |  |  |

|                  |                 | the NCO interr                                                   |               |                  |                  |                  |              |  |  |  |

| bit 1-0          |                 | ted: Read as '                                                   | •             |                  |                  |                  |              |  |  |  |

|                  | -               |                                                                  |               |                  |                  |                  |              |  |  |  |

| Note: Bit        | PEIE of the IN  | TCON register                                                    | must he       |                  |                  |                  |              |  |  |  |

|                  | t to enable any | •                                                                |               |                  |                  |                  |              |  |  |  |

set to enable any peripheral interrupt.

| R/W-0/0      | ) R/W-0/0                                                                     | R-0/0                                                                                                                                        | R/W-0/0                                        | R/W-0/0          | U-0             | R/W-0/0           | R/W-0/0      |

|--------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------|-----------------|-------------------|--------------|

| TMR1G        | F ADIF                                                                        | RCIF                                                                                                                                         | TXIF                                           | SSP1IF           | _               | TMR2IF            | TMR1IF       |

| bit 7        |                                                                               | ·                                                                                                                                            |                                                |                  |                 |                   | bit 0        |

|              |                                                                               |                                                                                                                                              |                                                |                  |                 |                   |              |

| Legend:      |                                                                               |                                                                                                                                              |                                                |                  |                 |                   |              |

| R = Reada    | ıble bit                                                                      | W = Writable                                                                                                                                 | bit                                            | U = Unimpler     | nented bit, rea | id as '0'         |              |

| u = Bit is u | nchanged                                                                      | x = Bit is unk                                                                                                                               | nown                                           | -n/n = Value a   | at POR and B    | OR/Value at all o | other Resets |

| '1' = Bit is | set                                                                           | '0' = Bit is cle                                                                                                                             | ared                                           |                  |                 |                   |              |

| bit 7        | TMR1GIF:                                                                      | Timer1 Gate Inte                                                                                                                             | errupt Flag bit                                |                  |                 |                   |              |

|              |                                                                               | ot is pending<br>ot is not pending                                                                                                           |                                                |                  |                 |                   |              |

| bit 6        | ADIF: ADC                                                                     | Interrupt Flag b                                                                                                                             | it                                             |                  |                 |                   |              |

|              |                                                                               | ot is pending ot is not pending                                                                                                              |                                                |                  |                 |                   |              |

| bit 5        | RCIF: USA                                                                     | RT Receive Inte                                                                                                                              | rrupt Flag bit                                 |                  |                 |                   |              |

|              |                                                                               | ot is pending<br>ot is not pending                                                                                                           |                                                |                  |                 |                   |              |

| bit 4        | TXIF: USA                                                                     | RT Transmit Inte                                                                                                                             | rrupt Flag bit                                 |                  |                 |                   |              |

|              |                                                                               | ot is pending<br>ot is not pending                                                                                                           |                                                |                  |                 |                   |              |

| bit 3        | SSP1IF: S                                                                     | ynchronous Seria                                                                                                                             | al Port (MSSP)                                 | ) Interrupt Flag | bit             |                   |              |

|              |                                                                               | ot is pending<br>ot is not pending                                                                                                           |                                                |                  |                 |                   |              |

| bit 2        | Unimplem                                                                      | ented: Read as                                                                                                                               | ʻ0'                                            |                  |                 |                   |              |

| bit 1        | TMR2IF: ⊺                                                                     | imer2 to PR2 Inte                                                                                                                            | errupt Flag bit                                |                  |                 |                   |              |

|              |                                                                               | ot is pending<br>ot is not pending                                                                                                           |                                                |                  |                 |                   |              |

| bit 0        | TMR1IF: ⊺                                                                     | imer1 Overflow I                                                                                                                             | nterrupt Flag b                                | oit              |                 |                   |              |

|              |                                                                               | ot is pending<br>ot is not pending                                                                                                           |                                                |                  |                 |                   |              |

|              |                                                                               |                                                                                                                                              |                                                |                  |                 |                   |              |

| Note:        | condition occurs<br>its correspondin<br>Interrupt Enable<br>register. User se | s are set when ar<br>, regardless of th<br>g enable bit or th<br>e bit, GIE of the<br>oftware should en<br>rupt flag bits are o<br>tterrupt. | e state of<br>ne Global<br>INTCON<br>nsure the |                  |                 |                   |              |

#### REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

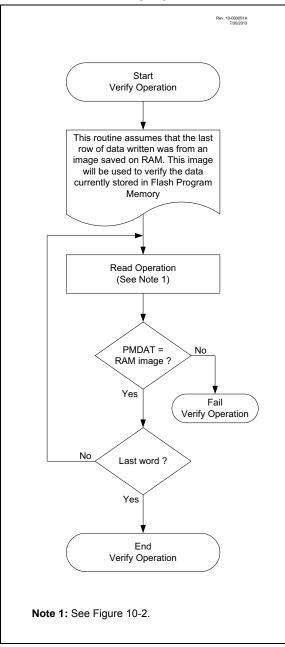

### 10.5 Write Verify

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

#### FIGURE 10-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

-n/n = Value at POR and BOR/Value at all other Resets

| U-0            | U-0                               | R/W-1/1 | R/W-1/1 | R/W-1/1                            | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |

|----------------|-----------------------------------|---------|---------|------------------------------------|---------|---------|---------|--|--|

| _              |                                   | WPUA5   | WPUA4   | WPUA3                              | WPUA2   | WPUA1   | WPUA0   |  |  |

| bit 7          |                                   |         |         |                                    |         |         | bit 0   |  |  |

|                |                                   |         |         |                                    |         |         |         |  |  |

| Legend:        |                                   |         |         |                                    |         |         |         |  |  |

| R = Readable b | R = Readable bit W = Writable bit |         |         | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| REGISTER 11-6: | WPUA: WEAK PULL-UP PORTA REGISTER |

|----------------|-----------------------------------|

|                |                                   |

x = Bit is unknown

'0' = Bit is cleared

| bit 7-6 | Unimplemented: Read as '0'                           |

|---------|------------------------------------------------------|

| bit 5-0 | WPUA<5:0>: Weak Pull-up Register bits <sup>(3)</sup> |

|         | 1 = Pull-up enabled                                  |

|         | 0 = Pull-up disabled                                 |

u = Bit is unchanged

'1' = Bit is set

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is configured as an output.

- **3:** For the WPUA3 bit, when MCLRE = 1, weak pull-up is internally enabled, but not reported here.

| Name       | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|------------|-------|--------|--------|--------|--------|--------|---------|---------|---------------------|

| ANSELA     | _     | _      | _      | ANSA4  | _      | ANSA2  | ANSA1   | ANSA0   | 110                 |

| APFCON     | _     | -      | -      | SSSEL  | T1GSEL | _      | CLC1SEL | NCO1SEL | 107                 |

| LATA       | _     | _      | LATA5  | LATA4  | _      | LATA2  | LATA1   | LATA0   | 110                 |

| OPTION_REG | WPUEN | INTEDG | TMR0CS | TMR0SE | PSA    |        | PS<2:0> |         | 154                 |

| PORTA      | _     | _      | RA5    | RA4    | RA3    | RA2    | RA1     | RA0     | 109                 |

| TRISA      | _     | _      | TRISA5 | TRISA4 | _(1)   | TRISA2 | TRISA1  | TRISA0  | 109                 |

| WPUA       | _     | _      | WPUA5  | WPUA4  | WPUA3  | WPUA2  | WPUA1   | WPUA0   | 111                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA. **Note 1:** Unimplemented, read as '1'.

TABLE 11-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2   | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|------------|-----------|---------|---------------------|

| 0015104 | 13:8 |         | 1       | FCMEN    | IESO      | CLKOUTEN | BOREN<1:0> |           | —       | 44                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          |            | FOSC<2:0> |         | 41                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

| R/W-0/0         | R/W-0                                                                        |                                                                                                                                                                                                   | R/W-0/0                               | U-0            | U-0              | U-0              | U-0         |

|-----------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|------------------|------------------|-------------|

|                 | TRIC                                                                         | GSEL<3:0> <sup>(1)</sup>                                                                                                                                                                          |                                       | _              | —                | —                | _           |

| bit 7           |                                                                              |                                                                                                                                                                                                   |                                       |                |                  |                  | bit 0       |

| Legend:         |                                                                              |                                                                                                                                                                                                   |                                       |                |                  |                  |             |

| R = Readab      | ole bit                                                                      | W = Writable                                                                                                                                                                                      | bit                                   | U = Unimplen   | nented bit, read | as '0'           |             |

| u = Bit is un   | changed                                                                      | x = Bit is unkr                                                                                                                                                                                   | nown                                  | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is se | et                                                                           | '0' = Bit is cle                                                                                                                                                                                  | ared                                  |                |                  |                  |             |

|                 | 0011 =<br>0100 =<br>0101 =<br>0110 =<br>1000 =<br>1001 =<br>1010 =<br>1011 = | Reserved<br>Timer0 – T0_overf<br>Timer1 – T1_overf<br>Timer2 – T2_matc<br>Comparator C1 – C<br>CLC1 – LC1_out<br>CLC2 – LC2_out<br>CLC3 – LC2_out<br>CLC3 – LC3_out<br>CLC4 – LC4_out<br>Reserved | low <sup>(2)</sup><br>h<br>C1OUT_sync |                |                  |                  |             |

| bit 3-0         | 1110 <b>=</b><br>1111 <b>=</b>                                               | Reserved<br>Reserved<br>Reserved<br>mented: Read as '                                                                                                                                             | 0'                                    |                |                  |                  |             |

- Note 1: This is a rising edge sensitive input for all sources.

- 2: Signal also sets its corresponding interrupt flag.

The  $I^2C$  interface supports the following modes and features:

- Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- Clock stretching

- Bus collision detection

- General call address matching

- Address masking

- · Address Hold and Data Hold modes

- · Selectable SDAx hold times

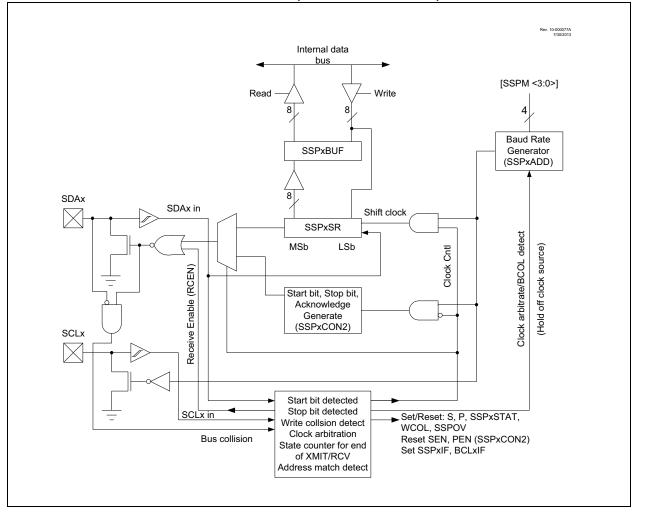

Figure 21-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 21-3 is a diagram of the  $I^2C$  interface module in Slave mode.

Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSPxCON1 and SSPxCON2 registers control different operational aspects of the same module, while SSPxCON1 and SSP2CON1 control the same features for two different modules.

2: Throughout this section, generic references to an MSSPx module in any of its operating modes may be interpreted as being equally applicable to MSSPx or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

#### FIGURE 21-2: MSSPX BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

### 21.3 I<sup>2</sup>C MODE OVERVIEW

The Inter-Integrated Circuit Bus (I<sup>2</sup>C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A slave device is controlled through addressing.

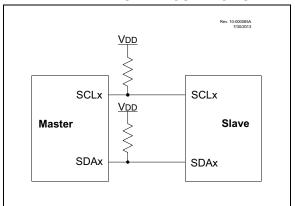

The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCLx)

- Serial Data (SDAx)

Figure 21-2 and Figure 21-3 show the block diagrams of the MSSP module when operating in I<sup>2</sup>C mode.

Both the SCLx and SDAx connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 21-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode (master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDAx line while the SCLx line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

#### FIGURE 21-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit (ACK) is an active-low signal, which holds the SDAx line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCLx line is held low. Transitions that occur while the SCLx line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overrightarrow{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDAx line while the SCLx line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

# PIC16(L)F1508/9

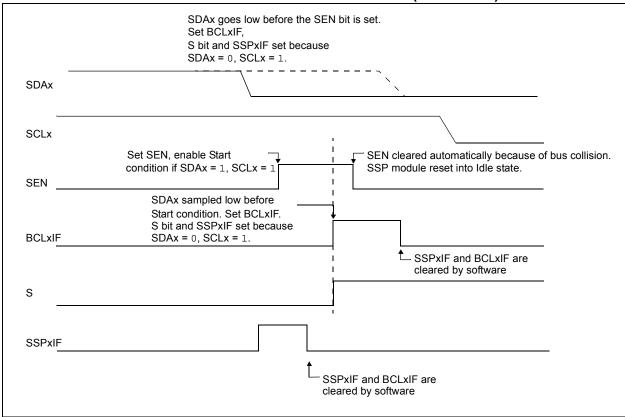

#### 21.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 21-33).

- b) SCL is sampled low before SDAx is asserted low (Figure 21-34).

During a Start condition, both the SDAx and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- · the BCL1IF flag is set and

- the MSSP module is reset to its Idle state (Figure 21-33).

The Start condition begins with the SDAx and SCLx pins deasserted. When the SDAx pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCLx pin is sampled low while SDAx is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDAx pin is sampled low during this count, the BRG is reset and the SDAx line is asserted early (Figure 21-35). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDAx before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 21-33: BUS COLLISION DURING START CONDITION (SDAX ONLY)

#### 25.9 Register Definitions: NCOx Control Registers

#### REGISTER 25-1: NCOxCON: NCOx CONTROL REGISTER

| R/W-0/0                                           | R/W-0/0                                              | R-0/0                                     | R/W-0/0       | U-0             | U-0                | U-0               | R/W-0/0    |

|---------------------------------------------------|------------------------------------------------------|-------------------------------------------|---------------|-----------------|--------------------|-------------------|------------|

| NxEN                                              | NxOE                                                 | NxOUT                                     | NxPOL         | —               | —                  | —                 | NxPFM      |

| bit 7                                             |                                                      | •                                         |               |                 |                    |                   | bit 0      |

| Legend:                                           |                                                      |                                           |               |                 |                    |                   |            |

| R = Readable b                                    | <b>.</b> it                                          | W = Writable bi                           | •             |                 | ented bit, read as | · 'O'             |            |

|                                                   |                                                      |                                           |               | •               |                    |                   | <b>D</b> ( |

| u = Bit is uncha                                  | inged                                                | x = Bit is unkno                          |               | -n/n = Value at | POR and BOR/V      | alue at all other | Resets     |

| '1' = Bit is set                                  |                                                      | '0' = Bit is clear                        | ed            |                 |                    |                   |            |

|                                                   |                                                      |                                           |               |                 |                    |                   |            |

| bit 7                                             | NxEN: NCOx E                                         | Enable bit                                |               |                 |                    |                   |            |

|                                                   | 1 = NCOx mod                                         |                                           |               |                 |                    |                   |            |

|                                                   | 0 = NCOx mod                                         |                                           |               |                 |                    |                   |            |

| bit 6                                             |                                                      | Output Enable bi                          |               |                 |                    |                   |            |

|                                                   |                                                      | out pin is enabled<br>out pin is disabled |               |                 |                    |                   |            |

| 5 H F                                             |                                                      |                                           | I             |                 |                    |                   |            |

| bit 5                                             | NxOUT: NCOx                                          | •                                         |               |                 |                    |                   |            |

| 1 = NCOx output is high<br>0 = NCOx output is low |                                                      |                                           |               |                 |                    |                   |            |

| bit 4                                             | NxPOL: NCOx Polarity bit                             |                                           |               |                 |                    |                   |            |

| bit 4                                             | 1 = NCOx output signal is active low (inverted)      |                                           |               |                 |                    |                   |            |

|                                                   | 0 = NCOx output signal is active high (non-inverted) |                                           |               |                 |                    |                   |            |

| bit 3-1                                           | Unimplemented: Read as '0'                           |                                           |               |                 |                    |                   |            |

| bit 0                                             | NxPFM: NCOx                                          | Pulse Frequenc                            | v Mode bit    |                 |                    |                   |            |

| -                                                 |                                                      | rates in Pulse Fre                        |               |                 |                    |                   |            |

|                                                   | 0 = NCOx oper                                        | rates in Fixed Du                         | ty Cycle mode |                 |                    |                   |            |

|                                                   |                                                      |                                           |               |                 |                    |                   |            |

#### REGISTER 25-2: NCOxCLK: NCOx INPUT CLOCK CONTROL REGISTER

| NxPWS<2:0>(1, 2)         —         —         —         NxCKS<1:0>           bit 7           bit            bit </th <th>R/W-0/0</th> <th>R/W-0/0</th> <th>R/W-0/0</th> <th>U-0</th> <th>U-0</th> <th>U-0</th> <th>R/W-0/0</th> <th>R/W-0/0</th> | R/W-0/0 | R/W-0/0          | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|---------|-----|-----|-----|---------|---------|

| bit 7 bit                                                                                                                                                                                                                                       |         | NxPWS<2:0>(1, 2) |         | —   | —   | —   | NxCKS   | S<1:0>  |

|                                                                                                                                                                                                                                                 | bit 7   |                  |         |     |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 NxPWS<2:0>: NCOx Output Pulse Width Select bits<sup>(1, 2)</sup>

- 111 = 128 NCOx clock periods

- 110 = 64 NCOx clock periods

- 101 = 32 NCOx clock periods

- 100 = 16 NCOx clock periods

- 011 = 8 NCOx clock periods 010 = 4 NCOx clock periods

- 010 = 4 NCOx clock periods 001 = 2 NCOx clock periods

- 001 2 NCOX clock periods

- 000 = 1 NCOx clock periods

- bit 4-2 Unimplemented: Read as '0'

- bit 1-0 NxCKS<1:0>: NCOx Clock Source Select bits

- 11 = NCO1CLK pin

- 10 = LC1\_out

- 01 = Fosc

- 00 = HFINTOSC (16 MHz)

Note 1: NxPWS applies only when operating in Pulse Frequency mode.

2: If NCOx pulse width is greater than NCO\_overflow period, operation is indeterminate.

| IABLE Z                                | ABLE 28-3: ENHANCED MID-RANGE INSTRUCTION SET |                               |              |       |        |        |        |          | 1     |

|----------------------------------------|-----------------------------------------------|-------------------------------|--------------|-------|--------|--------|--------|----------|-------|

| Mnemonic,<br>Operands                  |                                               | Description                   | Cycles       |       | 14-Bit | Opcode | Status | Notes    |       |

|                                        |                                               | Description                   | Cycles       | MSb   |        |        | LSb    | Affected | Notes |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |                                               |                               |              |       |        |        |        |          |       |

| ADDWF                                  | f, d                                          | Add W and f                   | 1            | 00    | 0111   | dfff   | ffff   | C, DC, Z | 2     |

| ADDWFC                                 | f, d                                          | Add with Carry W and f        | 1            | 11    | 1101   | dfff   | ffff   | C, DC, Z | 2     |

| ANDWF                                  | f, d                                          | AND W with f                  | 1            | 00    | 0101   | dfff   | ffff   | Z        | 2     |

| ASRF                                   | f, d                                          | Arithmetic Right Shift        | 1            | 11    | 0111   | dfff   | ffff   | C, Z     | 2     |

| LSLF                                   | f, d                                          | Logical Left Shift            | 1            | 11    | 0101   | dfff   | ffff   | C, Z     | 2     |

| LSRF                                   | f, d                                          | Logical Right Shift           | 1            | 11    | 0110   | dfff   | ffff   | C, Z     | 2     |

| CLRF                                   | f                                             | Clear f                       | 1            | 00    | 0001   | lfff   | ffff   | Z        | 2     |

| CLRW                                   | _                                             | Clear W                       | 1            | 00    | 0001   | 0000   | 00xx   | Z        |       |

| COMF                                   | f, d                                          | Complement f                  | 1            | 00    | 1001   | dfff   | ffff   | Z        | 2     |

| DECF                                   | f, d                                          | Decrement f                   | 1            | 00    | 0011   | dfff   | ffff   | z        | 2     |

| INCF                                   | f. d                                          | Increment f                   | 1            | 00    | 1010   | dfff   | ffff   | z        | 2     |

| IORWF                                  | f. d                                          | Inclusive OR W with f         | 1            | 00    | 0100   |        | ffff   | z        | 2     |

| MOVF                                   | f. d                                          | Move f                        | 1            | 00    | 1000   |        | ffff   | z        | 2     |

| MOVWF                                  | f                                             | Move W to f                   | 1            | 00    | 0000   |        | ffff   | _        | 2     |

| RLF                                    | f, d                                          | Rotate Left f through Carry   | 1            | 00    |        | dfff   |        | С        | 2     |

| RRF                                    | f, d                                          | Rotate Right f through Carry  | 1            | 00    | 1100   |        |        | C        | 2     |

| SUBWF                                  | f, d                                          | Subtract W from f             | 1            | 00    | 0010   |        | ffff   | -        | 2     |

| SUBWFB                                 | f, d                                          | Subtract with Borrow W from f | 1            | 11    |        | dfff   |        | C, DC, Z | 2     |

| SWAPF                                  | f, d                                          | Swap nibbles in f             | 1            | 00    | 1110   | dfff   | ffff   | 0, 00, 2 | 2     |

| XORWF                                  | f. d                                          | Exclusive OR W with f         | 1            | 00    | 0110   |        | ffff   | z        | 2     |

| XOINWI                                 | 1, U                                          | BYTE ORIENTED                 | •            |       | 0110   | uIII   | LLLL   | 2        | 2     |

| 550507                                 | f, d                                          | Decrement f, Skip if 0        | 1(2)         | 00    | 1011   | dfff   | ffff   |          | 1, 2  |

| DECFSZ                                 | f, d                                          | Increment f, Skip if 0        | 1(2)         | 00    | 11111  | dfff   | ffff   |          | 1, 2  |

| INCFSZ                                 | 1, U                                          | Increment 1, Skip ir 0        | 1(2)         | 00    |        | alli   | LILL   |          | 1, 2  |

|                                        |                                               | BIT-ORIENTED FILE R           | EGISTER OPER | NOITA | IS     |        |        |          |       |

| BCF                                    | f, b                                          | Bit Clear f                   | 1            | 01    | 00bb   | bfff   | ffff   |          | 2     |

| BSF                                    | f, b                                          | Bit Set f                     | 1            | 01    | 01bb   | bfff   | ffff   |          | 2     |

|                                        |                                               | BIT-ORIENTED S                | KIP OPERATIO | NS    |        |        |        |          |       |

| BTFSC                                  | f, b                                          | Bit Test f, Skip if Clear     | 1 (2)        | 01    | 10bb   | bfff   | ffff   |          | 1, 2  |

| BTFSS                                  | f, b                                          | Bit Test f, Skip if Set       | 1 (2)        | 01    | 11bb   | bfff   | ffff   |          | 1, 2  |

|                                        |                                               |                               | PERATIONS    | 1     |        |        |        |          |       |

| ADDLW                                  | k                                             | Add literal and W             | 1            | 11    | 1110   | kkkk   |        | C, DC, Z |       |

| ANDLW                                  | k                                             | AND literal with W            | 1            | 11    |        | kkkk   |        | Z        |       |

| IORLW                                  | k                                             | Inclusive OR literal with W   | 1            | 11    |        | kkkk   |        | Z        |       |

| MOVLB                                  | k                                             | Move literal to BSR           | 1            | 00    | 0000   | 001k   |        |          |       |

| MOVLP                                  | k                                             | Move literal to PCLATH        | 1            | 11    |        | 1kkk   |        |          |       |

| MOVLW                                  | k                                             | Move literal to W             | 1            | 11    | 0000   | kkkk   | kkkk   |          |       |

| SUBLW                                  | k                                             | Subtract W from literal       | 1            | 11    | 1100   | kkkk   | kkkk   | C, DC, Z |       |

| XORLW                                  | k                                             | Exclusive OR literal with W   | 1            | 11    |        | kkkk   |        | Z        | 1     |

### TABLE 28-3: ENHANCED MID-RANGE INSTRUCTION SET

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

# TABLE 29-13: ANALOG-TO-DIGITAL CONVERTER (ADC) CHARACTERISTICS<sup>(1,2,3)</sup>

| Param.<br>No. | Sym. | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                               |

|---------------|------|---------------------------------------------------|------|------|------|-------|--------------------------------------------------------------------------|

| AD01          | NR   | Resolution                                        | —    | _    | 10   | bit   |                                                                          |

| AD02          | Eı∟  | Integral Error                                    | _    | ±1   | ±1.7 | LSb   | VREF = 3.0V                                                              |

| AD03          | Edl  | Differential Error                                | —    | ±1   | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                          |

| AD04          | EOFF | Offset Error                                      |      | ±1   | ±2.5 | LSb   | VREF = 3.0V                                                              |

| AD05          | Egn  | Gain Error                                        | _    | ±1   | ±2.0 | LSb   | VREF = 3.0V                                                              |

| AD06          | VREF | Reference Voltage                                 | 1.8  | _    | VDD  | V     | VREF = (VRPOS - VRNEG) (Note 4)                                          |

| AD07          | VAIN | Full-Scale Range                                  | Vss  | _    | VREF | V     |                                                                          |

| AD08          | ZAIN | Recommended Impedance of<br>Analog Voltage Source | —    | _    | 10   | kΩ    | Can go higher if external $0.01\mu F$ capacitor is present on input pin. |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

Note 1:Total Absolute Error includes integral, differential, offset and gain errors.

2: The ADC conversion result never decreases with an increase in the input voltage and has no missing codes.

3: See Section 30.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

4: ADC VREF is selected by ADPREF<0> bit.

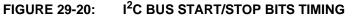

#### TABLE 29-20: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Param.<br>No. | Symbol  | Charao          | Min.         | Тур  | Max. | Units | Conditions |                                                       |  |

|---------------|---------|-----------------|--------------|------|------|-------|------------|-------------------------------------------------------|--|

| SP90*         | TSU:STA | Start condition | 100 kHz mode | 4700 | -    | —     | ns         | Only relevant for Repeated                            |  |

|               |         | Setup time      | 400 kHz mode | 600  | _    | _     |            | Start condition                                       |  |

| SP91*         | THD:STA | Start condition | 100 kHz mode | 4000 | _    | —     | ns         | After this period, the first clock pulse is generated |  |

|               |         | Hold time       | 400 kHz mode | 600  | _    | —     |            |                                                       |  |

| SP92*         | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _    | —     | ns         |                                                       |  |

|               |         | Setup time      | 400 kHz mode | 600  | _    | —     |            |                                                       |  |

| SP93          | THD:STO | Stop condition  | 100 kHz mode | 4000 | _    | —     | ns         |                                                       |  |

|               |         | Hold time       | 400 kHz mode | 600  | _    | _     |            |                                                       |  |

#### St. -1-. . .... 1. ..... -1 ~ .... - 1 .... ....

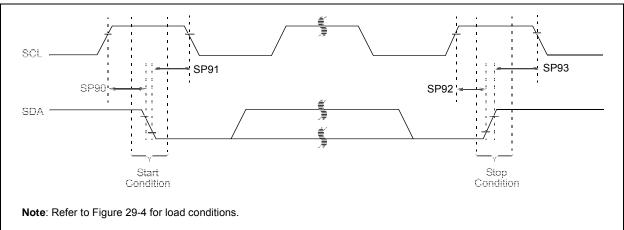

#### I<sup>2</sup>C BUS DATA TIMING **FIGURE 29-21:**

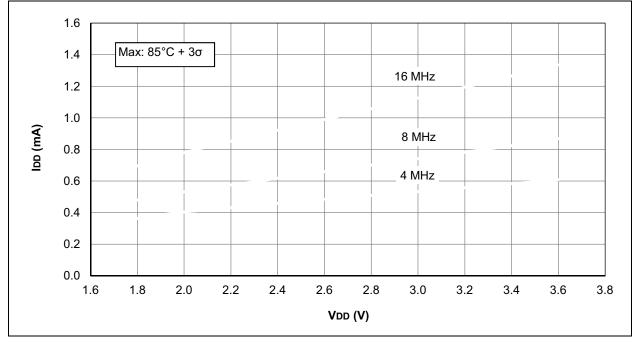

## 32.0 PACKAGING INFORMATION

#### 32.1 Package Marking Information