Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1509-i-so |

TABLE 1-2: PIC16(L)F1508/9 PINOUT DESCRIPTION (CONTINUED)

| Name                        | Function | Input<br>Type    | Output<br>Type | Description                                         |

|-----------------------------|----------|------------------|----------------|-----------------------------------------------------|

| RB4/AN10/CLC3IN0/SDA/SDI    | RB4      | TTL              | CMOS           | General purpose I/O.                                |

|                             | AN10     | AN               | _              | ADC Channel input.                                  |

|                             | CLC3IN0  | ST               |                | Configurable Logic Cell source input.               |

|                             | SDA      | I <sup>2</sup> C | OD             | I <sup>2</sup> C data input/output.                 |

|                             | SDI      | CMOS             | _              | SPI data input.                                     |

| RB5/AN11/CLC4IN0/RX/DT      | RB5      | TTL              | CMOS           | General purpose I/O.                                |

|                             | AN11     | AN               | _              | ADC Channel input.                                  |

|                             | CLC4IN0  | ST               | _              | Configurable Logic Cell source input.               |

|                             | RX       | ST               |                | USART asynchronous input.                           |

|                             | DT       | ST               | CMOS           | USART synchronous data.                             |

| RB6/SCL/SCK                 | RB6      | TTL              | CMOS           | General purpose I/O.                                |

|                             | SCL      | I <sup>2</sup> C | OD             | I <sup>2</sup> C clock.                             |

|                             | SCK      | ST               | CMOS           | SPI clock.                                          |

| RB7/CLC3/TX/CK              | RB7      | TTL              | CMOS           | General purpose I/O.                                |

|                             | CLC3     | _                | CMOS           | Configurable Logic Cell source output.              |

|                             | TX       | _                | CMOS           | USART asynchronous transmit.                        |

|                             | CK       | ST               | CMOS           | USART synchronous clock.                            |

| RC0/AN4/CLC2/C2IN+          | RC0      | TTL              | CMOS           | General purpose I/O.                                |

|                             | AN4      | AN               | _              | ADC Channel input.                                  |

|                             | CLC2     | _                | CMOS           | Configurable Logic Cell source output.              |

|                             | C2IN+    | AN               | _              | Comparator positive input.                          |

| RC1/AN5/C1IN1-/C2IN1-/PWM4/ | RC1      | TTL              | CMOS           | General purpose I/O.                                |

| NCO1                        | AN5      | AN               | _              | ADC Channel input.                                  |

|                             | C1IN1-   | AN               | _              | Comparator negative input.                          |

|                             | C2IN1-   | AN               | _              | Comparator negative input.                          |

|                             | PWM4     | _                | CMOS           | PWM output.                                         |

|                             | NCO1     | _                | CMOS           | Numerically Controlled Oscillator is source output. |

| RC2/AN6/C1IN2-/C2IN2-       | RC2      | TTL              | CMOS           | General purpose I/O.                                |

|                             | AN6      | AN               | _              | ADC Channel input.                                  |

|                             | C1IN2-   | AN               | _              | Comparator negative input.                          |

|                             | C2IN2-   | AN               | _              | Comparator negative input.                          |

| RC3/AN7/C1IN3-/C2IN3-/PWM2/ | RC3      | TTL              | CMOS           | General purpose I/O.                                |

| CLC2IN0                     | AN7      | AN               | _              | ADC Channel input.                                  |

|                             | C1IN3-   | AN               | _              | Comparator negative input.                          |

|                             | C2IN3-   | AN               | _              | Comparator negative input.                          |

|                             | PWM2     | _                | CMOS           | PWM output.                                         |

|                             | CLC2IN0  | ST               | _              | Configurable Logic Cell source input.               |

| RC4/C2OUT/CLC2IN1/CLC4/     | RC4      | TTL              | CMOS           | General purpose I/O.                                |

| CWG1B                       | C2OUT    | _                | CMOS           | Comparator output.                                  |

|                             | CLC2IN1  | ST               | _              | Configurable Logic Cell source input.               |

|                             | CLC4     | _                | CMOS           | Configurable Logic Cell source output.              |

|                             | CWG1B    | _                | CMOS           | CWG complementary output.                           |

|                             |          |                  |                |                                                     |

**Legend:** AN = Analog input or output CMOS = CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$  HV = High Voltage XTAL = Crystal levels

Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

# PIC16(L)F1508/9

# 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- · 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.6 "Indirect Addressing"** for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-8.

TABLE 3-2: CORE REGISTERS

| Addresses    | BANKx    |

|--------------|----------|

| x00h or x80h | INDF0    |

| x01h or x81h | INDF1    |

| x02h or x82h | PCL      |

| x03h or x83h | STATUS   |

| x04h or x84h | FSR0L    |

| x05h or x85h | FSR0H    |

| x06h or x86h | FSR1L    |

| x07h or x87h | FSR1H    |

| x08h or x88h | BSR      |

| x09h or x89h | WREG     |

| x0Ah or x8Ah | n PCLATH |

| x0Bh or x8Bh | n INTCON |

# PIC16(L)F1508/9

# 6.13 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

The PCON register bits are shown in Register 6-2.

# 6.14 Register Definitions: Power Control

### REGISTER 6-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | _   | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |            |            |            |            | bit 0      |

| Legend:                     |                      |                                                       |  |  |  |

|-----------------------------|----------------------|-------------------------------------------------------|--|--|--|

| HC = Bit is cleared by hard | ware                 | HS = Bit is set by hardware                           |  |  |  |

| R = Readable bit            | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |  |  |

| u = Bit is unchanged        | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |

| '1' = Bit is set            | '0' = Bit is cleared | q = Value depends on condition                        |  |  |  |

| bit 7 | STKOVF: Stack Overflow Flag bit                                                                                                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = A Stack Overflow occurred                                                                                                   |

|       | 0 = A Stack Overflow has not occurred or cleared by firmware                                                                    |

| bit 6 | STKUNF: Stack Underflow Flag bit                                                                                                |

|       | 1 = A Stack Underflow occurred                                                                                                  |

|       | 0 = A Stack Underflow has not occurred or cleared by firmware                                                                   |

| bit 5 | Unimplemented: Read as '0'                                                                                                      |

| bit 4 | RWDT: Watchdog Timer Reset Flag bit                                                                                             |

|       | 1 = A Watchdog Timer Reset has not occurred or set by firmware                                                                  |

|       | 0 = A Watchdog Timer Reset has occurred (cleared by hardware)                                                                   |

| bit 3 | RMCLR: MCLR Reset Flag bit                                                                                                      |

|       | 1 = A MCLR Reset has not occurred or set by firmware                                                                            |

|       | 0 = A MCLR Reset has occurred (cleared by hardware)                                                                             |

| bit 2 | RI: RESET Instruction Flag bit                                                                                                  |

|       | 1 = A RESET instruction has not been executed or set by firmware                                                                |

|       | 0 = A RESET instruction has been executed (cleared by hardware)                                                                 |

| bit 1 | POR: Power-On Reset Status bit                                                                                                  |

|       | 1 = No Power-on Reset occurred                                                                                                  |

|       | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                           |

| bit 0 | BOR: Brown-Out Reset Status bit                                                                                                 |

|       | 1 = No Brown-out Reset occurred                                                                                                 |

|       | <ul><li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset<br/>occurs)</li></ul> |

#### REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | _   | _   | CLC4IF  | CLC3IF  | CLC2IF  | CLC1IF  |

| bit 7 |     |     |     |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 Unimplemented: Read as '0' bit 3 CLC4IF: Configurable Logic Block 4 Interrupt Flag bit 1 = Interrupt is pending 0 = Interrupt is not pending bit 2 CLC3IF: Configurable Logic Block 3 Interrupt Flag bit 1 = Interrupt is pending 0 = Interrupt is not pending bit 1 CLC2IF: Configurable Logic Block 2 Interrupt Flag bit 1 = Interrupt is pending 0 = Interrupt is not pending bit 0 CLC1IF: Configurable Logic Block 1 Interrupt Flag bit 1 = Interrupt is pending 0 = Interrupt is not pending

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### 8.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- WDT will be cleared but keeps running, if enabled for operation during Sleep.

- PD bit of the STATUS register is cleared.

- TO bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Timer1 oscillator

- ADC is unaffected, if the dedicated FRC oscillator is selected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- · I/O pins should not be floating

- · External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- · CWG, NCO and CLC modules using HFINTOSC

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include the FVR module. See **Section 13.0 "Fixed Voltage Reference (FVR)"** for more information on this module.

# 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.12** "Determining the Cause of a Reset".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

#### 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

#### **EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY**

```

; This row erase routine assumes the following:

; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM)

BCF

INTCON, GIE

; Disable ints so required sequences will execute properly

BANKSEL

PMADRL

MOVF

ADDRL,W

; Load lower 8 bits of erase address boundary

MOVWF

PMADRL

MOVF

ADDRH,W

; Load upper 6 bits of erase address boundary

MOVWF

PMADRH

BCF

PMCON1,CFGS

; Not configuration space

BSF

PMCON1, FREE

; Specify an erase operation

BSF

PMCON1, WREN

; Enable writes

; Start of required sequence to initiate erase

MOVLW

55h

MOVWF

PMCON2

; Write 55h

MOVLW

0AAh

MOVWF

PMCON2

; Write AAh

BSF

PMCON1,WR

; Set WR bit to begin erase

NOP

; NOP instructions are forced as processor starts

NOP

; row erase of program memory.

; The processor stalls until the erase process is complete

; after erase processor continues with 3rd instruction

BCF

PMCON1,WREN

; Disable writes

INTCON, GIE

BSF

; Enable interrupts

```

#### REGISTER 11-9: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| LATB7   | LATB6   | LATB5   | LATB4   | _   | _   | _   | _     |

| bit 7   |         |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 LATB<7:4>: RB<7:4> Output Latch Value bits<sup>(1)</sup>

bit 3-0 **Unimplemented:** Read as '0'

Note 1: Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is

return of actual I/O pin values.

#### REGISTER 11-10: ANSELB: PORTB ANALOG SELECT REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|---------|---------|-----|-----|-----|-------|

| _     | _   | ANSB5   | ANSB4   | _   | _   | _   | _     |

| bit 7 |     |         |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 ANSB<5:4>: Analog Select between Analog or Digital Function on pins RB<5:4>, respectively

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

0 = Digital I/O. Pin is assigned to port or digital special function.

bit 3-0 **Unimplemented:** Read as '0'

Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to

allow external control of the voltage on the pin.

# 12.6 Register Definitions: Interrupt-on-Change Control

#### REGISTER 12-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7 | •   |         | •       | •       |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **IOCAP<5:0>:** Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 12-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOCAN<5:0>:** Interrupt-on-Change PORTA Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set

upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 12-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| _     | _   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared HS - Bit is set in hardware

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOCAF<5:0>:** Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

#### 15.2.6 ADC CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- Disable weak pull-ups either globally (Refer to the OPTION\_REG register) or individually (Refer to the appropriate WPUx register).

- 2. Configure the ADC module:

- · Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- Read ADC Result.

- Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 15.4 "ADC Acquisition Requirements".

#### **EXAMPLE 15-1: ADC CONVERSION**

```

; This code block configures the ADC

;for polling, Vdd and Vss references, FRC

; oscillator and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL

ADCON1

B'11110000' ; Right justify, FRC

MOVLW

;oscillator

MOVWF

ADCON1

; Vdd and Vss Vref+

BANKSEL

TRISA

TRISA,0

;Set RAO to input

BSF

BANKSEL

ANSEL

BSF

ANSEL, 0

;Set RAO to analog

BANKSEL

WPUA

BCF

WPUA,0

;Disable weak

pull-up on RA0

BANKSEL

ADCON0

B'00000001' ;Select channel AN0

MOVLW

MOVWF

ADCON0

;Turn ADC On

SampleTime ;Acquisiton delay

CALL

ADCON0, ADGO ; Start conversion

BSF

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

;No, test again

$-1

BANKSEL

ADRESH

MOVF

ADRESH,W ;Read upper 2 bits

MOVWF

RESULTHI ;store in GPR space

BANKSEL

ADRESL

ADRESL, W

;Read lower 8 bits

MOVF

MOVWF

RESULTLO

;Store in GPR space

```

### 16.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACxCON1 register.

The DAC output voltage can be determined by using Equation 16-1.

### 16.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 29-14.

### 16.3 DAC Voltage Reference Output

The unbuffered DAC voltage can be output to the DACxOUTn pin(s) by setting the respective DACOEn bit(s) of the DACxCON0 register. Selecting the DAC reference voltage for output on either DACxOUTn pin automatically overrides the digital output buffer, the weak pull-up and digital input threshold detector functions of that pin.

Reading the DACxOUTn pin when it has been configured for DAC reference voltage output will

### 16.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the DACxCON0 register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 16.5 Effects of a Reset

A device Reset affects the following:

- · DACx is disabled.

- DACx output voltage is removed from the DACxOUTn pin(s).

- The DACR<4:0> range select bits are cleared.

#### **EQUATION 16-1: DAC OUTPUT VOLTAGE**

#### IF DACEN = 1

$$DACx\_output = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE-$$

Note: See the DACxCON0 register for the available VSOURCE+ and VSOURCE- selections.

#### 17.2.5 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 17-2 shows the output state versus input conditions, including polarity control.

TABLE 17-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVn > CxVp     | 0     | 0     |

| CxVn < CxVp     | 0     | 1     |

| CxVn > CxVp     | 1     | 1     |

| CxVn < CxVp     | 1     | 0     |

# 17.2.6 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the Normal-Speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

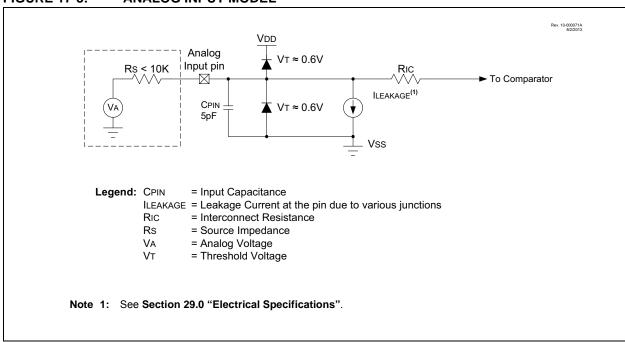

# 17.3 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 17-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

FIGURE 17-3: ANALOG INPUT MODEL

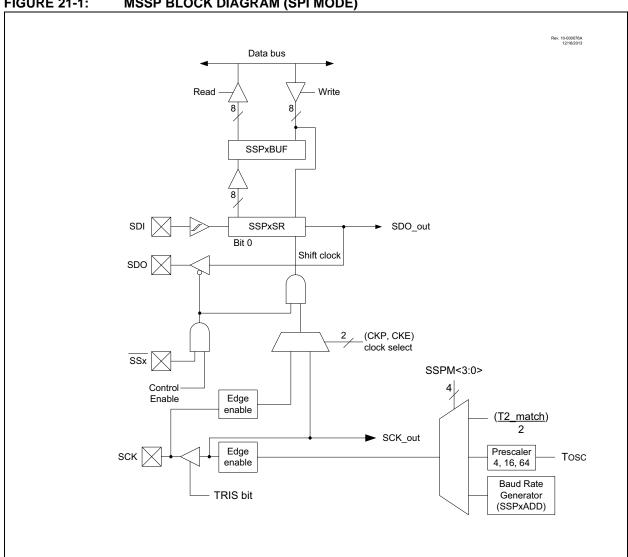

#### 21.0 **MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE**

#### **MSSP Module Overview** 21.1

The Master Synchronous Serial Port (MSSPx) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSPx module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C™)

The SPI interface supports the following modes and features:

- · Master mode

- · Slave mode

- · Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 21-1 is a block diagram of the SPI interface module.

**FIGURE 21-1:** MSSP BLOCK DIAGRAM (SPI MODE)

# 21.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an I<sup>2</sup>C slave in 10-bit Addressing mode.

Figure 21-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish I<sup>2</sup>C communication.

- 1. Bus starts idle.

- Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching high address with R/W bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- 5. Software clears the SSPxIF bit.

- Software reads received address from SSPxBUF clearing the BF flag.

- Slave loads low address into SSPxADD, releasing SCLx.

- Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

Slave sends ACK and SSPxIF is set.

**Note:** If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- Master clocks a data byte to the slave and clocks out the slaves ACK on the ninth SCLx pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCI x.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

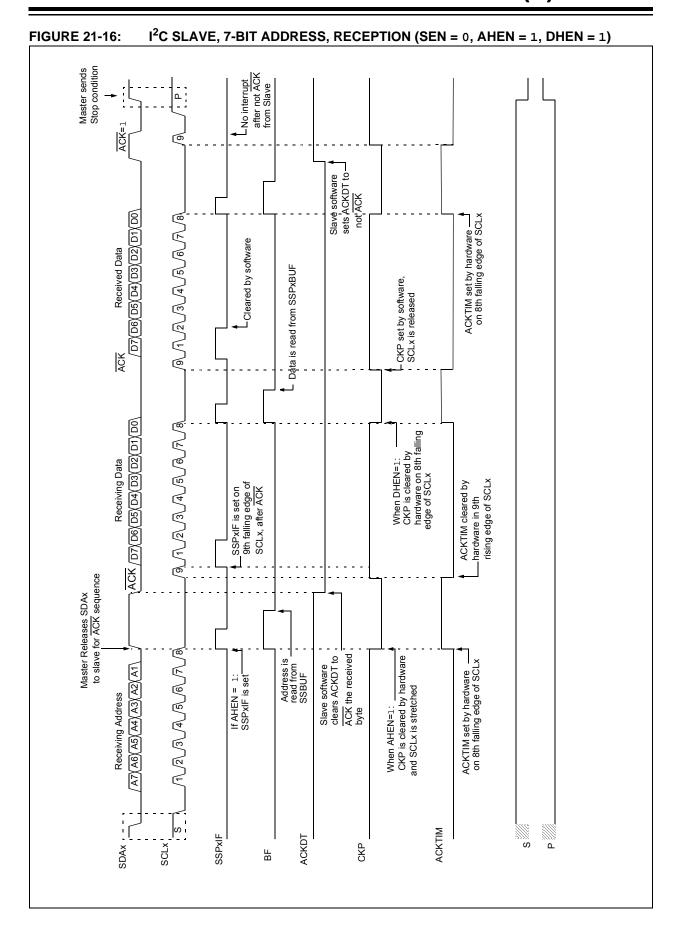

# 21.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCLx line is held low are the same. Figure 21-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 21-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

#### REGISTER 24-3: CLCxSEL0: MULTIPLEXER DATA 1 AND 2 SELECT REGISTER

| U-0   | R/W-x/u | R/W-x/u                  | R/W-x/u | U-0 | R/W-x/u | R/W-x/u                   | R/W-x/u |

|-------|---------|--------------------------|---------|-----|---------|---------------------------|---------|

| _     | L       | CxD2S<2:0> <sup>(1</sup> | )       | _   | L       | CxD1S<2:0> <sup>(1)</sup> |         |

| bit 7 |         |                          |         |     |         |                           | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 Unimplemented: Read as '0' LCxD2S<2:0>: Input Data 2 Selection Control bits(1) bit 6-4 111 = LCx in[11] is selected for lcxd2 110 = LCx\_in[10] is selected for lcxd2 101 = LCx in[9] is selected for lcxd2 100 = LCx in[8] is selected for lcxd2 011 = LCx in[7] is selected for lcxd2 010 = LCx in[6] is selected for lcxd2 001 = LCx in[5] is selected for lcxd2 000 = LCx\_in[4] is selected for lcxd2 bit 3 Unimplemented: Read as '0' LCxD1S<2:0>: Input Data 1 Selection Control bits(1) bit 2-0 111 = LCx in[7] is selected for lcxd1 110 = LCx\_in[6] is selected for lcxd1 101 = LCx\_in[5] is selected for lcxd1 100 = LCx\_in[4] is selected for lcxd1 011 = LCx in[3] is selected for lcxd1 010 = LCx in[2] is selected for lcxd1 001 = LCx in[1] is selected for lcxd1 000 = LCx\_in[0] is selected for lcxd1

Note 1: See Table 24-1 for signal names associated with inputs.

| BCF              | Bit Clear f                         |

|------------------|-------------------------------------|

| Syntax:          | [ label ] BCF f,b                   |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$   |

| Operation:       | $0 \rightarrow (f < b >)$           |

| Status Affected: | None                                |

| Description:     | Bit 'b' in register 'f' is cleared. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                |

| Operands:        | $\begin{aligned} 0 &\leq f \leq 127 \\ 0 &\leq b \leq 7 \end{aligned}$                                                                                                                                          |

| Operation:       | skip if (f < b >) = 0                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.  If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BRA label<br>[ label ] BRA \$+k                                                                                                                                                                                     |

| Operands:        | -256 ≤ label - PC + 1 ≤ 255<br>-256 ≤ k ≤ 255                                                                                                                                                                                 |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$                                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.  If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2-cycle instruction. |

| Syntax:          | [ label ] BRW                                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                           |

| Operation:       | $(PC) + (W) \rightarrow PC$                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                           |

| Description:     | Add the contents of W (unsigned) to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + (W). This instruction is a 2-cycle instruction. |

Relative Branch with W

**BRW**

| BSF              | Bit Set f                            |

|------------------|--------------------------------------|

| Syntax:          | [ label ] BSF f,b                    |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$ |

| Operation:       | $1 \rightarrow (f < b >)$            |

| Status Affected: | None                                 |

| Description:     | Bit 'b' in register 'f' is set.      |

# 29.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

dt

io

mc

|   | •         |                                    |     |          |

|---|-----------|------------------------------------|-----|----------|

|   | F         | Frequency                          | Т   | Time     |

|   | Lowercase | e letters (pp) and their meanings: |     |          |

| I | рр        |                                    |     |          |

|   | CC        | CCP1                               | osc | CLKIN    |

|   | ck        | CLKOUT                             | rd  | RD       |

|   | CS        | CS                                 | rw  | RD or WR |

|   | di        | SDIx                               | SC  | SCKx     |

|   | do        | SDO                                | ss  | SS       |

t0

t1

wr

T0CKI

T1CKI

WR

Uppercase letters and their meanings:

Data in

**MCLR**

I/O PORT

| S   |                          |   |                |  |

|-----|--------------------------|---|----------------|--|

| F   | Fall                     | Р | Period         |  |

| Н   | High                     | R | Rise           |  |

| - 1 | Invalid (High-impedance) | V | Valid          |  |

| L   | Low                      | Z | High-impedance |  |

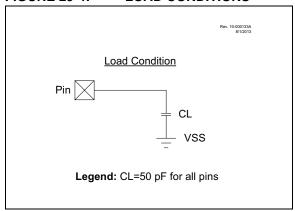

# FIGURE 29-4: LOAD CONDITIONS

# PIC16(L)F1508/9

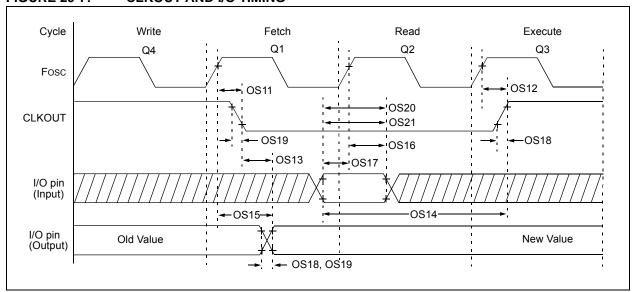

FIGURE 29-7: CLKOUT AND I/O TIMING

TABLE 29-9: CLKOUT AND I/O TIMING PARAMETERS

| Standard      | Standard Operating Conditions (unless otherwise stated) |                                                            |               |      |      |       |                                     |

|---------------|---------------------------------------------------------|------------------------------------------------------------|---------------|------|------|-------|-------------------------------------|

| Param.<br>No. | Sym.                                                    | Characteristic                                             | Min.          | Тур† | Max. | Units | Conditions                          |

| OS11          | TosH2ckL                                                | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                            | _             | _    | 70   | ns    | $3.3V \leq V_{DD} \leq 5.0V$        |

| OS12          | TosH2ckH                                                | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                            | _             | _    | 72   | ns    | $3.3 V \leq V \text{DD} \leq 5.0 V$ |

| OS13          | TckL2ioV                                                | CLKOUT↓ to Port out valid <sup>(1)</sup>                   | _             | _    | 20   | ns    |                                     |

| OS14          | TioV2ckH                                                | Port input valid before CLKOUT <sup>(1)</sup>              | Tosc + 200 ns | _    | _    | ns    |                                     |

| OS15          | TosH2ioV                                                | Fosc↑ (Q1 cycle) to Port out valid                         | _             | 50   | 70*  | ns    | $3.3V \leq V_{DD} \leq 5.0V$        |

| OS16          | TosH2ioI                                                | Fosc↑ (Q2 cycle) to Port input invalid (I/O in setup time) | 50            | _    | _    | ns    | $3.3V \leq VDD \leq 5.0V$           |

| OS17          | TioV2osH                                                | Port input valid to Fosc↑ (Q2 cycle) (I/O in setup time)   | 20            | _    | _    | ns    |                                     |

| OS18*         | TioR                                                    | Port output rise time                                      | _             | 40   | 72   | ns    | VDD = 1.8V                          |

|               |                                                         |                                                            | _             | 15   | 32   |       | $3.3V \leq V_{DD} \leq 5.0V$        |

| OS19*         | TioF                                                    | Port output fall time                                      | _             | 28   | 55   | ns    | VDD = 1.8V                          |

|               |                                                         |                                                            | _             | 15   | 30   |       | $3.3V \leq V_{DD} \leq 5.0V$        |

| OS20*         | Tinp                                                    | INT pin input high or low time                             | 25            | _    | _    | ns    |                                     |

| OS21*         | Tioc                                                    | Interrupt-on-change new input level time                   | 25            | _    | _    | ns    |                                     |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in EXTRC mode where CLKOUT output is 4 x Tosc.

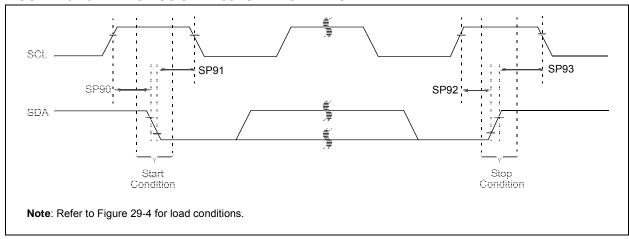

FIGURE 29-20: I<sup>2</sup>C BUS START/STOP BITS TIMING

TABLE 29-20: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Param.<br>No. | Symbol  | Charac          | cteristic    | Min. | Тур | Max. | Units | Conditions                                            |

|---------------|---------|-----------------|--------------|------|-----|------|-------|-------------------------------------------------------|

| SP90*         | Tsu:sta | Start condition | 100 kHz mode | 4700 | _   | _    | ns    | Only relevant for Repeated                            |

|               |         | Setup time      | 400 kHz mode | 600  | _   | _    |       | Start condition                                       |

| SP91*         | THD:STA | Start condition | 100 kHz mode | 4000 | _   | _    | ns    | After this period, the first clock pulse is generated |

|               |         | Hold time       | 400 kHz mode | 600  | _   | _    |       |                                                       |

| SP92*         | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   | _    | ns    |                                                       |

|               |         | Setup time      | 400 kHz mode | 600  | _   | _    |       |                                                       |

| SP93          | THD:STO | Stop condition  | 100 kHz mode | 4000 | _   | _    | ns    |                                                       |

|               |         | Hold time       | 400 kHz mode | 600  | _   | _    |       |                                                       |

<sup>\*</sup> These parameters are characterized but not tested.

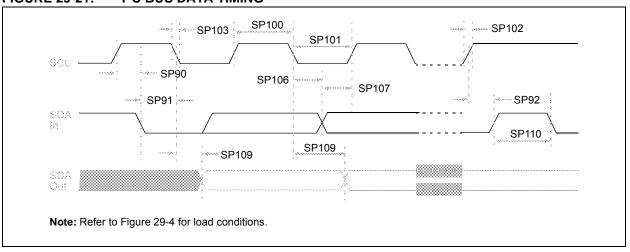

# FIGURE 29-21: I<sup>2</sup>C BUS DATA TIMING

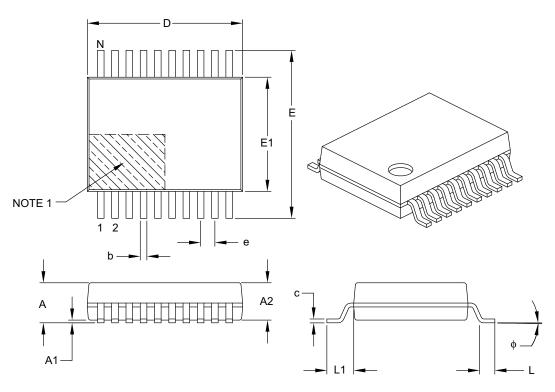

# 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |          | MILLIMETERS |      |  |

|--------------------------|-------|----------|-------------|------|--|

| Dimension Limits         |       | MIN      | NOM         | MAX  |  |

| Number of Pins           | N     | 20       |             |      |  |

| Pitch                    | е     | 0.65 BSC |             |      |  |

| Overall Height           | Α     | _        | _           | 2.00 |  |

| Molded Package Thickness | A2    | 1.65     | 1.75        | 1.85 |  |

| Standoff                 | A1    | 0.05     | _           | _    |  |

| Overall Width            | Е     | 7.40     | 7.80        | 8.20 |  |

| Molded Package Width     | E1    | 5.00     | 5.30        | 5.60 |  |

| Overall Length           | D     | 6.90     | 7.20        | 7.50 |  |

| Foot Length              | L     | 0.55     | 0.75        | 0.95 |  |

| Footprint                | L1    | 1.25 REF |             |      |  |

| Lead Thickness           | С     | 0.09     | _           | 0.25 |  |

| Foot Angle               | ф     | 0°       | 4°          | 8°   |  |

| Lead Width               | b     | 0.22     | _           | 0.38 |  |

## Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

$\label{eq:REF:Reference Dimension, usually without tolerance, for information purposes only. \\$

Microchip Technology Drawing C04-072B