#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 17                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 12x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 20-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1509t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

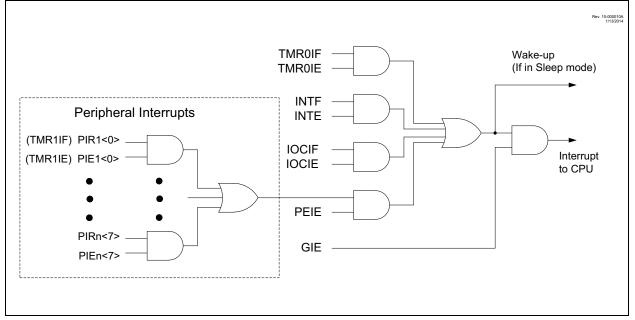

A block diagram of the interrupt logic is shown in Figure 7-1.

| R/W-0/0          | R/W-0/0                                                                                                       | R/W-0/0                      | R/W-0/0          | R/W-0/0          | U-0              | R/W-0/0          | R/W-0/0     |  |

|------------------|---------------------------------------------------------------------------------------------------------------|------------------------------|------------------|------------------|------------------|------------------|-------------|--|

| TMR1GIE          | ADIE                                                                                                          | RCIE                         | TXIE             | SSP1IE           | —                | TMR2IE           | TMR1IE      |  |

| bit 7            |                                                                                                               |                              |                  |                  |                  |                  | bit (       |  |

| Legend:          |                                                                                                               |                              |                  |                  |                  |                  |             |  |

| R = Readable     | hit                                                                                                           | W = Writable                 | hit              | II – Unimpler    | nented bit, read | 1 26 (0)         |             |  |

| u = Bit is unch  |                                                                                                               | x = Bit is unknown           |                  | •                |                  | R/Value at all o | thar Resots |  |

| '1' = Bit is set | ungeu                                                                                                         | '0' = Bit is cle             |                  |                  |                  |                  |             |  |

|                  |                                                                                                               |                              |                  |                  |                  |                  |             |  |

| bit 7            | TMR1GIE: T                                                                                                    | imer1 Gate Inte              | errupt Enable I  | oit              |                  |                  |             |  |

|                  | 1 = Enables                                                                                                   | the Timer1 gate              | e acquisition ir | nterrupt         |                  |                  |             |  |

|                  | 0 = Disables                                                                                                  | the Timer1 gate              | e acquisition i  | nterrupt         |                  |                  |             |  |

| bit 6            | ADIE: Analo                                                                                                   | g-to-Digital Con             | verter (ADC)     | Interrupt Enabl  | e bit            |                  |             |  |

|                  | 1 = Enables the ADC interrupt                                                                                 |                              |                  |                  |                  |                  |             |  |

|                  |                                                                                                               | the ADC interru              | -                | .,               |                  |                  |             |  |

| bit 5            |                                                                                                               | RT Receive Inter             |                  | it               |                  |                  |             |  |

|                  | <ul> <li>1 = Enables the USART receive interrupt</li> <li>0 = Disables the USART receive interrupt</li> </ul> |                              |                  |                  |                  |                  |             |  |

| bit 4            |                                                                                                               | T Transmit Inte              | -                |                  |                  |                  |             |  |

|                  |                                                                                                               | the USART transmit interrupt |                  |                  |                  |                  |             |  |

|                  |                                                                                                               | the USART tra                |                  |                  |                  |                  |             |  |

| bit 3            | SSP1IE: Syr                                                                                                   | nchronous Seria              | I Port (MSSP     | ) Interrupt Enat | ole bit          |                  |             |  |

|                  |                                                                                                               | the MSSP inter               | •                |                  |                  |                  |             |  |

|                  |                                                                                                               | the MSSP inter               | •                |                  |                  |                  |             |  |

| bit 2            | -                                                                                                             | nted: Read as '              |                  |                  |                  |                  |             |  |

| bit 1            |                                                                                                               | IR2 to PR2 Mat               |                  |                  |                  |                  |             |  |

|                  | 1 = Enables the Timer2 to PR2 match interrupt                                                                 |                              |                  |                  |                  |                  |             |  |

| bit 0            | 0 = Disables the Timer2 to PR2 match interrupt                                                                |                              |                  |                  |                  |                  |             |  |

|                  | <b>TMR1IE:</b> Timer1 Overflow Interrupt Enable bit<br>1 = Enables the Timer1 overflow interrupt              |                              |                  |                  |                  |                  |             |  |

|                  |                                                                                                               | the Timer1 ove               |                  |                  |                  |                  |             |  |

|                  |                                                                                                               |                              |                  |                  |                  |                  |             |  |

| Note: Bit        | PEIE of the IN                                                                                                | ITCON register               | must he          |                  |                  |                  |             |  |

|                  |                                                                                                               | peripheral inter             |                  |                  |                  |                  |             |  |

# REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

#### 10.4 User ID, Device ID and Configuration Word Access

Instead of accessing program memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the PMCON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 10-2.

When read access is initiated on an address outside the parameters listed in Table 10-2, the PMDATH:PMDATL register pair is cleared, reading back '0's.

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### EXAMPLE 10-4: CONFIGURATION WORD AND DEVICE ID ACCESS

| * PROG_ADD | This code block will read 1 word of program memory at the memory address:<br>PROG_ADDR_LO (must be 00h-08h) data will be returned in the variables;<br>PROG_DATA_HI, PROG_DATA_LO |                              |  |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|--|--|--|

| BANKSEL    | PMADRL                                                                                                                                                                            | ; Select correct Bank        |  |  |  |  |  |  |

| MOVLW      | PROG_ADDR_LO                                                                                                                                                                      | ;                            |  |  |  |  |  |  |

| MOVWF      | PMADRL                                                                                                                                                                            | ; Store LSB of address       |  |  |  |  |  |  |

| CLRF       | PMADRH                                                                                                                                                                            | ; Clear MSB of address       |  |  |  |  |  |  |

|            |                                                                                                                                                                                   |                              |  |  |  |  |  |  |

| BSF        | PMCON1,CFGS                                                                                                                                                                       | ; Select Configuration Space |  |  |  |  |  |  |

| BCF        | INTCON,GIE                                                                                                                                                                        | ; Disable interrupts         |  |  |  |  |  |  |

| BSF        | PMCON1,RD                                                                                                                                                                         | ; Initiate read              |  |  |  |  |  |  |

| NOP        |                                                                                                                                                                                   | ; Executed (See Figure 10-2) |  |  |  |  |  |  |

| NOP        |                                                                                                                                                                                   | ; Ignored (See Figure 10-2)  |  |  |  |  |  |  |

| BSF        | INTCON, GIE                                                                                                                                                                       | ; Restore interrupts         |  |  |  |  |  |  |

| MOVF       | PMDATL,W                                                                                                                                                                          | ; Get LSB of word            |  |  |  |  |  |  |

| MOVWF      |                                                                                                                                                                                   | ; Store in user location     |  |  |  |  |  |  |

| MOVF       |                                                                                                                                                                                   | ; Get MSB of word            |  |  |  |  |  |  |

| MOVWF      |                                                                                                                                                                                   | ; Store in user location     |  |  |  |  |  |  |

# 11.8 Register Definitions: PORTC

#### REGISTER 11-12: PORTC: PORTC REGISTER

| R/W-x/u                                                                               | R/W-x/u | R/W-x/u           | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------------------------------------------------------------------------------------|---------|-------------------|-------------|---------|---------|---------|---------|

| RC7                                                                                   | RC6     | RC5               | RC4         | RC3     | RC2     | RC1     | RC0     |

| bit 7                                                                                 |         |                   |             |         |         |         | bit 0   |

|                                                                                       |         |                   |             |         |         |         |         |

| Legend:                                                                               |         |                   |             |         |         |         |         |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                  |         |                   |             |         |         |         |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all othe |         |                   | ther Resets |         |         |         |         |

| '1' = Bit is set                                                                      |         | '0' = Bit is clea | ared        |         |         |         |         |

bit 7-0 **RC<7:0>**: PORTC General Purpose I/O Pin bits 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

#### REGISTER 11-13: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### REGISTER 11-14: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

#### 19.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 19-1 displays the Timer1 enable selections.

| TABLE 19-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

#### **19.2 Clock Source Selection**

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 19-2 displays the clock source selections.

#### 19.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- · C1 or C2 comparator input to Timer1 gate

#### 19.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI. The external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TABLE 19-2:         CLOCK SOURCE SELECTIONS |  |

|---------------------------------------------|--|

|---------------------------------------------|--|

|                                     | TMR1CS<1:0> | T1OSCEN                        | Clock Source                                     |

|-------------------------------------|-------------|--------------------------------|--------------------------------------------------|

|                                     | 11          | х                              | LFINTOSC                                         |

|                                     | 10          | 1                              | Secondary Oscillator Circuit on SOSCI/SOSCO Pins |

| 10 0 External Clocking on T1CKI Pin |             | External Clocking on T1CKI Pin |                                                  |

|                                     | 01          | х                              | System Clock (Fosc)                              |

|                                     | 00          | х                              | Instruction Clock (Fosc/4)                       |

# PIC16(L)F1508/9

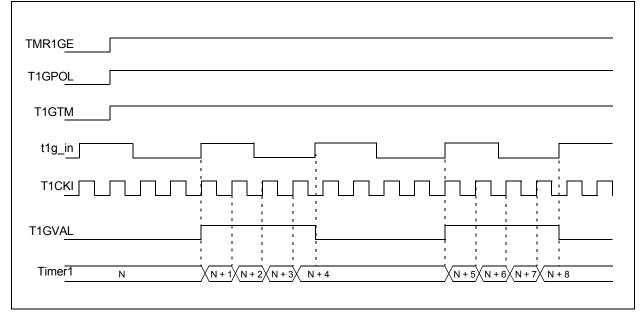

| TMR1GE   |   |               |       |             |

|----------|---|---------------|-------|-------------|

| T1GPOL   |   |               |       |             |

| t1g_in   | 7 |               |       |             |

| Т1СКІ    |   |               |       |             |

| T1GVAL   |   |               |       |             |

| Timer1 N |   | <u> N + 1</u> | N + 2 | N + 3 N + 4 |

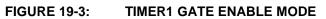

#### FIGURE 19-4: TIMER1 GATE TOGGLE MODE

#### 20.1 Timer2 Operation

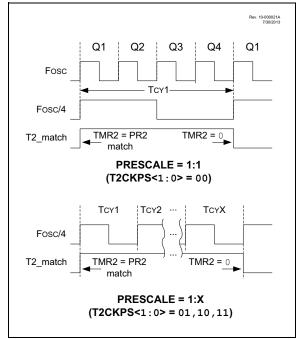

The clock input to the Timer2 module is the system instruction clock (Fosc/4).

TMR2 increments from 00h on each clock edge.

A 4-bit counter/prescaler on the clock input allows direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> of the T2CON register. The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/ postscaler (see **Section 20.2 "Timer2 Interrupt"**).

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, whereas the PR2 register initializes to FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- · a write to the T2CON register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: TMR2 is not cleared when T2CON is written.

# 20.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (T2\_match) provides the input for the 4-bit counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF of the PIR1 register. The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0>, of the T2CON register.

#### 20.3 Timer2 Output

The output of TMR2 is T2\_match. T2\_match is available to the following peripherals:

- Configurable Logic Cell (CLC)

- Master Synchronous Serial Port (MSSP)

- Numerically Controlled Oscillator (NCO)

- Pulse Width Modulator (PWM)

The T2\_match signal is synchronous with the system clock. Figure 20-3 shows two examples of the timing of the T2\_match signal relative to Fosc and prescale value, T2CKPS<1:0>. The upper diagram illustrates 1:1 prescale timing and the lower diagram, 1:X prescale timing.

# FIGURE 20-3: T2

T2\_MATCH TIMING DIAGRAM

# 20.4 Timer2 Operation During Sleep

Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and PR2 registers will remain unchanged while the processor is in Sleep mode.

# PIC16(L)F1508/9

| Name    | Bit 7     | Bit 6  | Bit 5  | Bit 4      | Bit 3       | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-----------|--------|--------|------------|-------------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF    | RCIDL  | _      | SCKP       | BRG16       |        | WUE    | ABDEN  | 235                 |

| INTCON  | GIE       | PEIE   | TMR0IE | INTE       | IOCIE       | TMR0IF | INTF   | IOCIF  | 75                  |

| PIE1    | TMR1GIE   | ADIE   | RCIE   | TXIE       | SSP1IE      | _      | TMR2IE | TMR1IE | 76                  |

| PIR1    | TMR1GIF   | ADIF   | RCIF   | TXIF       | SSP1IF      | _      | TMR2IF | TMR1IF | 79                  |

| RCREG   |           |        | EUS    | ART Receiv | ve Data Reg | jister |        |        | 228*                |

| RCSTA   | SPEN      | RX9    | SREN   | CREN       | ADDEN       | FERR   | OERR   | RX9D   | 234*                |

| SPBRGL  |           |        |        | BRG        | <7:0>       |        |        |        | 236*                |

| SPBRGH  | BRG<15:8> |        |        |            |             |        |        |        | 236*                |

| TRISB   | TRISB7    | TRISB6 | TRISB5 | TRISB4     | TRISB3      | TRISB2 | TRISB1 | TRISB0 | 113                 |

| TXSTA   | CSRC      | TX9    | TXEN   | SYNC       | SENDB       | BRGH   | TRMT   | TX9D   | 233                 |

#### TABLE 22-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

#### 24.1.5 CLCx SETUP STEPS

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 and CLCxSEL1 registers (See Table 24-1).

- Clear any associated ANSEL bits.

- · Set all TRIS bits associated with inputs.

- · Clear all TRIS bits associated with outputs.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxPOLy bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving a device, set the LCxOE bit in the CLCxCON register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register or falling event.

- Set the CLCxIE bit of the associated PIE registers.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

# 24.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR registers will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- · LCxON bit of the CLCxCON register

- · CLCxIE bit of the associated PIE registers

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the associated PIR registers, must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

# 24.3 Output Mirror Copies

Mirror copies of all LCxCON output bits are contained in the CLCxDATA register. Reading this register reads the outputs of all CLCs simultaneously. This prevents any reading skew introduced by testing or reading the CLCxOUT bits in the individual CLCxCON registers.

# 24.4 Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

# 24.5 Operation During Sleep

The CLC module operates independently from the system clock and will continue to run during Sleep, provided that the input sources selected remain active.

The HFINTOSC remains active during Sleep when the CLC module is enabled and the HFINTOSC is selected as an input source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and as a CLC input source, when the CLC is enabled, the CPU will go idle during Sleep, but the CLC will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

#### 25.2 Fixed Duty Cycle (FDC) Mode

In Fixed Duty Cycle (FDC) mode, every time the accumulator overflows (NCO\_overflow), the output is toggled. This provides a 50% duty cycle, provided that the increment value remains constant. For more information, see Figure 25-2.

The FDC mode is selected by clearing the NxPFM bit in the NCOxCON register.

#### 25.3 Pulse Frequency (PF) Mode

In Pulse Frequency (PF) mode, every time the accumulator overflows (NCO\_overflow), the output becomes active for one or more clock periods. Once the clock period expires, the output returns to an inactive state. This provides a pulsed output.

The output becomes active on the rising clock edge immediately following the overflow event. For more information, see Figure 25-2.

The value of the active and inactive states depends on the polarity bit, NxPOL in the NCOxCON register.

The PF mode is selected by setting the NxPFM bit in the NCOxCON register.

25.3.1 OUTPUT PULSE WIDTH CONTROL

When operating in PF mode, the active state of the output can vary in width by multiple clock periods. Various pulse widths are selected with the NxPWS<2:0> bits in the NCOxCLK register.

When the selected pulse width is greater than the accumulator overflow time frame, the output of the NCOx operation is indeterminate.

#### 25.4 Output Polarity Control

The last stage in the NCOx module is the output polarity. The NxPOL bit in the NCOxCON register selects the output polarity. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

The NCOx output can be used internally by source code or other peripherals. Accomplish this by reading the NxOUT (read-only) bit of the NCOxCON register.

The NCOx output signal is available to the following peripherals:

- CLC

- CWG

#### 25.5 Interrupts

When the accumulator overflows (NCO\_overflow), the NCOx Interrupt Flag bit, NCOxIF, of the PIRx register is set. To enable the interrupt event (NCO\_interrupt), the following bits must be set:

- NxEN bit of the NCOxCON register

- · NCOxIE bit of the PIEx register

- · PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt must be cleared by software by clearing the NCOxIF bit in the Interrupt Service Routine.

#### 25.6 Effects of a Reset

All of the NCOx registers are cleared to zero as the result of a Reset.

# 25.7 Operation In Sleep

The NCO module operates independently from the system clock and will continue to run during Sleep, provided that the clock source selected remains active.

The HFINTOSC remains active during Sleep when the NCO module is enabled and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the NCO clock source, when the NCO is enabled, the CPU will go idle during Sleep, but the NCO will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

#### 25.8 Alternate Pin Locations

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 11.1 "Alternate Pin Function**" for more information.

#### REGISTER 25-3: NCOxACCL: NCOx ACCUMULATOR REGISTER – LOW BYTE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | NCOxA   | CC<7:0> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

|         | 1.11    |         |         |         |         |         |         |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| Accumulator, Low Byte |

|-----------------------|

| ŀ                     |

#### **REGISTER 25-4:** NCOxACCH: NCOx ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0                           | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-----------------------------------|---------|---------|---------|------------------------------------|---------|---------|---------|--|--|

|                                   |         |         | NCOxAC  | C<15:8>                            |         |         |         |  |  |

| bit 7                             |         |         |         |                                    |         |         | bit 0   |  |  |

|                                   |         |         |         |                                    |         |         |         |  |  |

| Legend:                           |         |         |         |                                    |         |         |         |  |  |

| R = Readable bit W = Writable bit |         |         | bit     | U = Unimplemented bit, read as '0' |         |         |         |  |  |

|                                   |         |         |         |                                    |         |         |         |  |  |

#### bit 7-0 NCOxACC<15:8>: NCOx Accumulator, High Byte

'0' = Bit is cleared

#### REGISTER 25-5: NCOxACCU: NCOx ACCUMULATOR REGISTER – UPPER BYTE

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|----------|---------|

| —     | —   | —   | —   |         | NCOXAC  | C<19:16> |         |

| bit 7 |     |     |     |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCOxACC<19:16>: NCOx Accumulator, Upper Byte

'1' = Bit is set

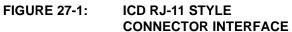

# 27.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "*PIC12(L)F1501/PIC16(L)F150X Memory Programming Specification*" (DS41573).

#### 27.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

#### 27.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the ICSP Low-Voltage Programming Entry mode is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.5** "**MCLR**" for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

# 27.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 27-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 27-2.

# 29.0 ELECTRICAL SPECIFICATIONS

# 29.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias             | -40°C to +125°C |

|--------------------------------------------|-----------------|

| Storage temperature                        |                 |

| Voltage on pins with respect to Vss        |                 |

| on VDD pin                                 |                 |

| PIC16F1508/9                               | -0.3V to +6.5V  |

| PIC16LF1508/9                              |                 |

| on MCLR pin                                |                 |

| on all other pins                          |                 |

| Maximum current                            |                 |

| on Vss pin <sup>(1)</sup>                  |                 |

| -40°C $\leq$ TA $\leq$ +85°C               | 250 mA          |

| +85°C $\leq$ TA $\leq$ +125°C              |                 |

| on VDD pin <sup>(1)</sup>                  |                 |

| -40°C $\leq$ TA $\leq$ +85°C               | 250 mA          |

| +85°C $\leq$ TA $\leq$ +125°C              | 85 mA           |

| Sunk by any standard I/O pin               | 50 mA           |

| Sourced by any standard I/O pin            | 50 mA           |

| Clamp current, Ik (VPIN < 0 or VPIN > VDD) | ±20 mA          |

| Total power dissipation <sup>(2)</sup>     |                 |

**Note 1:** Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Table 29-6 to calculate device specifications.

2: Power dissipation is calculated as follows: PDIS = VDD x {IDD  $-\Sigma$  IOH} +  $\Sigma$  {(VDD - VOH) x IOH} +  $\Sigma$ (VOI x IOL).

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

# 29.3 DC Characteristics

#### TABLE 29-1: SUPPLY VOLTAGE

| PIC16LF            | 1508/9 |                                                                                  | Standard             | d Opera | ating Con            | ditions ( | unless otherwise stated)                                                                                                                                                                                                                                                                |  |  |

|--------------------|--------|----------------------------------------------------------------------------------|----------------------|---------|----------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16F1            | 508/9  |                                                                                  |                      |         |                      |           |                                                                                                                                                                                                                                                                                         |  |  |

| Param. Sym.<br>No. |        | Sym. Characteristic                                                              | Min.                 | Тур†    | Max.                 | Units     | Conditions                                                                                                                                                                                                                                                                              |  |  |

| D001               | Vdd    | Supply Voltage                                                                   |                      |         |                      |           |                                                                                                                                                                                                                                                                                         |  |  |

|                    |        |                                                                                  | VDDMIN<br>1.8<br>2.5 | _       | VDDMAX<br>3.6<br>3.6 | V<br>V    | Fosc ≤ 16 MHz<br>Fosc ≤ 20 MHz                                                                                                                                                                                                                                                          |  |  |

| D001               |        |                                                                                  | 2.3<br>2.5           | _       | 5.5<br>5.5           | V<br>V    | Fosc ≤ 16 MHz<br>Fosc ≤ 20 MHz                                                                                                                                                                                                                                                          |  |  |

| D002*              | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                        |                      |         |                      |           |                                                                                                                                                                                                                                                                                         |  |  |

|                    |        |                                                                                  | 1.5                  |         | _                    | V         | Device in Sleep mode                                                                                                                                                                                                                                                                    |  |  |

| D002*              |        |                                                                                  | 1.7                  |         | —                    | V         | Device in Sleep mode                                                                                                                                                                                                                                                                    |  |  |

| D002A*             | VPOR   | Power-on Reset Release Voltage                                                   | (2)                  |         |                      |           |                                                                                                                                                                                                                                                                                         |  |  |

|                    |        |                                                                                  | _                    | 1.6     | —                    | V         |                                                                                                                                                                                                                                                                                         |  |  |

| D002A*             |        |                                                                                  | —                    | 1.6     | —                    | V         |                                                                                                                                                                                                                                                                                         |  |  |

| D002B*             | VPORR* | Power-on Reset Rearm Voltage <sup>(2)</sup>                                      | )                    |         |                      |           |                                                                                                                                                                                                                                                                                         |  |  |

|                    |        |                                                                                  | —                    | 0.8     | _                    | V         |                                                                                                                                                                                                                                                                                         |  |  |

| D002B*             |        |                                                                                  | _                    | 1.5     | _                    | V         |                                                                                                                                                                                                                                                                                         |  |  |

| D003               | VFVR   | Fixed Voltage Reference Voltage                                                  |                      |         |                      |           |                                                                                                                                                                                                                                                                                         |  |  |

|                    |        | 1x gain (1.024V nominal)<br>2x gain (2.048V nominal)<br>4x gain (4.096V nominal) | -4<br>-3             | _       | +4<br>+7             | %<br>%    | $ \begin{array}{l} V{\rm DD} \geq 2.5V, \ -40^{\circ}{\rm C} \leq {\rm TA} \leq +85^{\circ}{\rm C} \\ V{\rm DD} \geq 2.5V, \ -40^{\circ}{\rm C} \leq {\rm TA} \leq +85^{\circ}{\rm C} \\ V{\rm DD} \geq 4.75V, \ -40^{\circ}{\rm C} \leq {\rm TA} \leq +85^{\circ}{\rm C} \end{array} $ |  |  |

| D004*              | SVDD   | VDD Rise Rate <sup>(2)</sup>                                                     | 0.05                 | —       | —                    | V/ms      | Ensures that the Power-on Reset signal is released properly.                                                                                                                                                                                                                            |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: See Figure 29-3, POR and POR REARM with Slow Rising VDD.

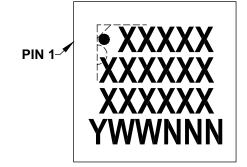

Example

**PIC16F1508**

-E/SS @3

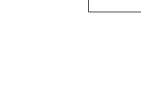

#### Package Marking Information (Continued)

20-Lead SSOP (5.30 mm)

20-Lead QFN (4x4x0.9 mm) 20-Lead UQFN (4x4x0.5 mm)

PIN 1-

• PIC16 F1508 E/ML @3

120123

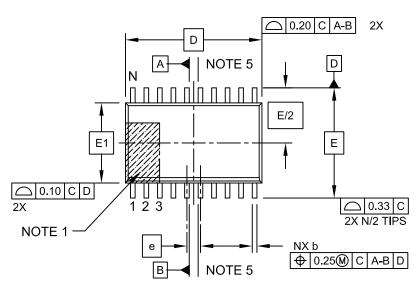

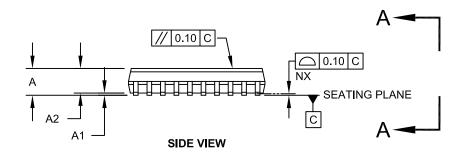

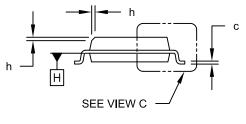

#### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW A-A

Microchip Technology Drawing C04-094C Sheet 1 of 2

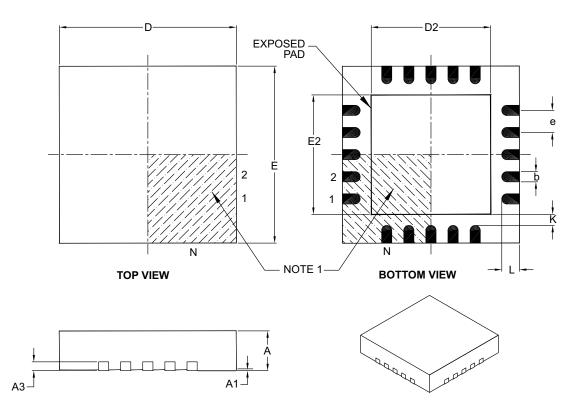

# 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |      |      |

|------------------------|------------------|-------------|------|------|

| Dimensio               | Dimension Limits |             | NOM  | MAX  |

| Number of Pins         | Ν                | 20          |      |      |

| Pitch                  | е                | 0.50 BSC    |      |      |

| Overall Height         | А                | 0.80        | 0.90 | 1.00 |

| Standoff               | A1               | 0.00        | 0.02 | 0.05 |

| Contact Thickness      | A3               | 0.20 REF    |      |      |

| Overall Width          | E                | 4.00 BSC    |      |      |

| Exposed Pad Width      | E2               | 2.60        | 2.70 | 2.80 |

| Overall Length         | D                | 4.00 BSC    |      |      |

| Exposed Pad Length     | D2               | 2.60        | 2.70 | 2.80 |

| Contact Width          | b                | 0.18        | 0.25 | 0.30 |

| Contact Length         | L                | 0.30        | 0.40 | 0.50 |

| Contact-to-Exposed Pad | К                | 0.20        | _    | _    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B

20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

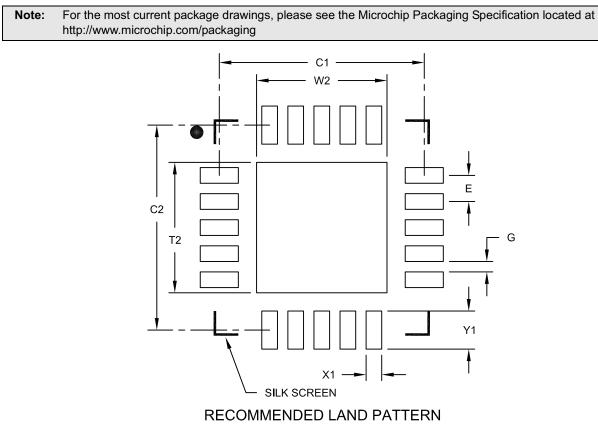

| Units                      |    | MILLIMETERS |          |      |  |

|----------------------------|----|-------------|----------|------|--|

| Dimension Limits           |    | MIN         | NOM      | MAX  |  |

| Contact Pitch              | E  |             | 0.50 BSC |      |  |

| Optional Center Pad Width  | W2 |             |          | 2.50 |  |

| Optional Center Pad Length | T2 |             |          | 2.50 |  |

| Contact Pad Spacing        | C1 |             | 3.93     |      |  |

| Contact Pad Spacing        | C2 |             | 3.93     |      |  |

| Contact Pad Width          | X1 |             |          | 0.30 |  |

| Contact Pad Length         | Y1 |             |          | 0.73 |  |

| Distance Between Pads      | G  | 0.20        |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820