Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 57                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                  |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 8.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                       |

| Data Converters            | A/D 16x10b/12b                                                    |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 80-TQFP                                                           |

| Supplier Device Package    | 80-TQFP (12x12)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f960-b-gqr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 32.9. Timer 3 Capture Mode Block Diagram        | 462 |

|--------------------------------------------------------|-----|

| Figure 33.1. PCA Block Diagram                         |     |

| Figure 33.2. PCA Counter/Timer Block Diagram           | 468 |

| Figure 33.3. PCA Interrupt Block Diagram               | 469 |

| Figure 33.4. PCA Capture Mode Diagram                  | 471 |

| Figure 33.5. PCA Software Timer Mode Diagram           | 472 |

| Figure 33.6. PCA High-Speed Output Mode Diagram        | 473 |

| Figure 33.7. PCA Frequency Output Mode                 | 474 |

| Figure 33.8. PCA 8-Bit PWM Mode Diagram                | 475 |

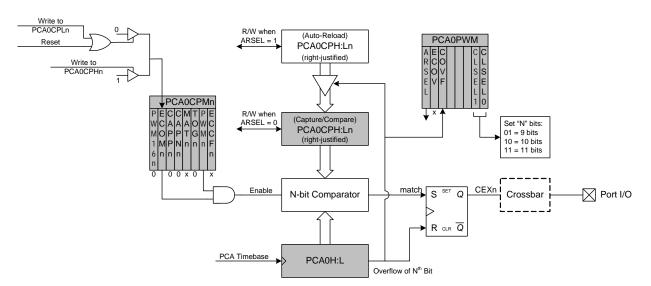

| Figure 33.9. PCA 9, 10 and 11-Bit PWM Mode Diagram     | 476 |

| Figure 33.10. PCA 16-Bit PWM Mode                      | 477 |

| Figure 33.11. PCA Module 5 with Watchdog Timer Enabled | 478 |

| Figure 34.1. Typical C2 Pin Sharing                    | 489 |

#### **Table 4.7. Power Management Electrical Specifications**

$V_{BAT}$  = 1.8 to 3.8 V, -40 to +85 °C unless otherwise specified.

| Parameter                 | Conditions                                   | Min | Тур | Max | Units   |

|---------------------------|----------------------------------------------|-----|-----|-----|---------|

| Idle Mode Wake-up Time    |                                              | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time | CLKDIV = 0x00<br>Low Power or Precision Osc. | _   | 400 | _   | ns      |

| Sleep Mode Wake-up Time   |                                              |     | 2   |     | μs      |

#### **Table 4.8. Flash Electrical Characteristics**

V<sub>BAT</sub> = 1.8 to 3.8 V, -40 to +85 °C unless otherwise specified.,

| Parameter        | Conditions      | Min    | Тур  | Max | Units                 |

|------------------|-----------------|--------|------|-----|-----------------------|

| Flash Size       | C8051F960/1/2/3 | 131072 | _    |     | bytes                 |

|                  | C8051F964/5     | 65536  | _    |     | bytes                 |

|                  | C8051F966/7     | 32768  |      |     | bytes                 |

|                  | C8051F968/9     | 16384  | _    |     | bytes                 |

| Endurance        |                 | 20 k   | 100k | _   | Erase/Write<br>Cycles |

| Erase Cycle Time |                 | 28     | 32   | 36  | ms                    |

| Write Cycle Time |                 | 57     | 64   | 71  | μs                    |

#### **Table 4.9. Internal Precision Oscillator Electrical Characteristics**

$V_{BAT}$  = 1.8 to 3.8 V;  $T_A$  = -40 to +85 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                                                           | Conditions                                     | Тур  | Max  | Units |     |  |  |

|---------------------------------------------------------------------|------------------------------------------------|------|------|-------|-----|--|--|

| Oscillator Frequency                                                | −40 to +85 °C,<br>V <sub>BAT</sub> = 1.8−3.8 V | 24   | 24.5 | 25    | MHz |  |  |

| Oscillator Supply Current<br>(from V <sub>BAT</sub> )               |                                                | 300* | _    | μA    |     |  |  |

| *Note: Does not include clock divider or clock tree supply current. |                                                |      |      |       |     |  |  |

#### Table 4.10. Internal Low-Power Oscillator Electrical Characteristics

$V_{BAT}$  = 1.8 to 3.8 V;  $T_A$  = -40 to +85 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                                                           | Conditions                                     | Min | Тур  | Max | Units |  |  |

|---------------------------------------------------------------------|------------------------------------------------|-----|------|-----|-------|--|--|

| Oscillator Frequency                                                | -40 to +85 °C,<br>V <sub>BAT</sub> = 1.8-3.8 V |     | 20   | 22  | MHz   |  |  |

| Oscillator Supply Current<br>(from V <sub>BAT</sub> )               | 25 °C<br>No separate bias current<br>required  | _   | 100* | _   | μA    |  |  |

| *Note: Does not include clock divider or clock tree supply current. |                                                |     |      |     |       |  |  |

# Table 4.16. Comparator Electrical Characteristics

$V_{BAT}$  = 1.8 to 3.8 V, –40 to +85 °C unless otherwise noted.

| Parameter                                         | Conditions               | Min   | Тур  | Max                     | Units |

|---------------------------------------------------|--------------------------|-------|------|-------------------------|-------|

| Response Time:                                    | CP0+ - CP0- = 100 mV     |       | 120  |                         | ns    |

| Mode 0, $V_{BAT}$ = 2.4 V, $V_{CM}^{*}$ = 1.2 V   | CP0+ - CP0- = -100 mV    |       | 110  | _                       | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV     | _     | 180  |                         | ns    |

| Mode 1, $V_{BAT}$ = 2.4 V, $V_{CM}^*$ = 1.2 V     | CP0+ - CP0- = -100 mV    |       | 220  | _                       | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV     | _     | 350  |                         | ns    |

| Mode 2, $V_{BAT}$ = 2.4 V, $V_{CM}^{*}$ = 1.2 V   | CP0+ - CP0- = -100 mV    |       | 600  | —                       | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV     | _     | 1240 |                         | ns    |

| Mode 3, $V_{BAT}$ = 2.4 V, $V_{CM}^*$ = 1.2 V     | CP0+ - CP0- = -100 mV    | _     | 3200 | —                       | ns    |

| Common-Mode Rejection Ratio                       |                          |       | 1.5  | _                       | mV/V  |

| Inverting or Non-Inverting Input<br>Voltage Range |                          | -0.25 | _    | V <sub>BAT</sub> + 0.25 | V     |

| Input Capacitance                                 |                          |       | 12   | _                       | pF    |

| Input Bias Current                                |                          |       | 1    | —                       | nA    |

| Input Offset Voltage                              |                          | -10   |      | +10                     | mV    |

| Power Supply                                      |                          |       |      |                         |       |

| Power Supply Rejection                            |                          | _     | 0.1  | _                       | mV/V  |

|                                                   | V <sub>BAT</sub> = 3.8 V | _     | 0.6  | —                       | μs    |

| Power-up Time                                     | V <sub>BAT</sub> = 3.0 V |       | 1.0  | —                       | μs    |

| i owei-up nine                                    | V <sub>BAT</sub> = 2.4 V |       | 1.8  | —                       | μs    |

|                                                   | V <sub>BAT</sub> = 1.8 V | _     | 10   | —                       | μs    |

|                                                   | Mode 0                   | _     | 23   | —                       | μA    |

| Supply Current at DC                              | Mode 1                   | —     | 8.8  |                         | μA    |

| Supply Surrent at DS                              | Mode 2                   | _     | 2.6  | —                       | μA    |

|                                                   | Mode 3                   |       | 0.4  |                         | μA    |

| *Note: Vcm is the common-mode voltage             | e on CP0+ and CP0        |       |      |                         |       |

# SFR Definition 5.3. ADC0AC: ADC0 Accumulator Configuration

| Bit   | 7       | 6     | 5 | 4          | 3  | 2 | 1          | 0 |

|-------|---------|-------|---|------------|----|---|------------|---|

| Name  | AD012BE | AD0AE | Ą | D0SJST[2:0 | )] | , | ADORPT[2:0 | ] |

| Туре  | R/W     | W     |   | R/W        |    |   | R/W        |   |

| Reset | 0       | 0     | 0 | 0          | 0  | 0 | 0          | 0 |

#### SFR Page = 0x0; SFR Address = 0xBA

| Bit | Name         | Function                                                                                                                                                          |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AD012BE      | ADC0 12-Bit Mode Enable.                                                                                                                                          |

|     |              | Enables 12-bit Mode.                                                                                                                                              |

|     |              | 0: 12-bit Mode Disabled.                                                                                                                                          |

|     |              | 1: 12-bit Mode Enabled.                                                                                                                                           |

| 6   | AD0AE        | ADC0 Accumulate Enable.                                                                                                                                           |

|     |              | Enables multiple conversions to be accumulated when burst mode is disabled.                                                                                       |

|     |              | 0: ADC0H:ADC0L contain the result of the latest conversion when Burst Mode is disabled.                                                                           |

|     |              | 1: ADC0H:ADC0L contain the accumulated conversion results when Burst Mode is disabled. Software must write 0x0000 to ADC0H:ADC0L to clear the accumulated result. |

|     |              | This bit is write-only. Always reads 0b.                                                                                                                          |

| 5:3 | AD0SJST[2:0] | ADC0 Accumulator Shift and Justify.                                                                                                                               |

|     |              | Specifies the format of data read from ADC0H:ADC0L.                                                                                                               |

|     |              | 000: Right justified. No shifting applied.                                                                                                                        |

|     |              | 001: Right justified. Shifted right by 1 bit.                                                                                                                     |

|     |              | 010: Right justified. Shifted right by 2 bits.                                                                                                                    |

|     |              | 011: Right justified. Shifted right by 3 bits.                                                                                                                    |

|     |              | 100: Left justified. No shifting applied.<br>All remaining bit combinations are reserved.                                                                         |

|     |              |                                                                                                                                                                   |

| 2:0 | AD0RPT[2:0]  | ADC0 Repeat Count.                                                                                                                                                |

|     |              | Selects the number of conversions to perform and accumulate in Burst Mode.<br>This bit field must be set to 000 if Burst Mode is disabled.                        |

|     |              | 000: Perform and Accumulate 1 conversion.                                                                                                                         |

|     |              | 001: Perform and Accumulate 4 conversions.                                                                                                                        |

|     |              | 010: Perform and Accumulate 8 conversions.                                                                                                                        |

|     |              | 011: Perform and Accumulate 16 conversions.                                                                                                                       |

|     |              | 100: Perform and Accumulate 32 conversions.                                                                                                                       |

|     |              | 101: Perform and Accumulate 64 conversions.                                                                                                                       |

|     |              | All remaining bit combinations are reserved.                                                                                                                      |

# SFR Definition 11.7. DMA0NCF: DMA Channel Configuration

| Bit   | 7     | 6      | 5     | 4      | 3           | 2   | 1 | 0 |

|-------|-------|--------|-------|--------|-------------|-----|---|---|

| Name  | INTEN | MINTEN | STALL | ENDIAN | PERIPH[3:0] |     |   |   |

| Туре  | R/W   | R/W    | R/W   | R/W    | R           | R/W |   |   |

| Reset | 0     | 0      | 0     | 0      | 0           | 0   | 0 | 0 |

SFR Page = 0x2; SFR Address = 0xC9

| Bit   | Name                   | Function                                                                                                                                                                                                                                                                                                         |

|-------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | INTEN                  | Full-Length Interrupt Enable.                                                                                                                                                                                                                                                                                    |

|       |                        | 0: Disable the full-length interrupt of the selected channel.                                                                                                                                                                                                                                                    |

|       |                        | 1: Enable the full-length interrupt of the selected channel.                                                                                                                                                                                                                                                     |

| 6     | MINTEN                 | Mid-Point Interrupt Enable.                                                                                                                                                                                                                                                                                      |

|       |                        | 0: Disable the mid-point interrupt of the selected channel.                                                                                                                                                                                                                                                      |

|       |                        | 1: Enable the mid-point interrupt of the selected channel.                                                                                                                                                                                                                                                       |

| 5     | STALL                  | DMA0 Stall.                                                                                                                                                                                                                                                                                                      |

|       |                        | <ul><li>Setting this bit stalls the DMA0 transfer on the selected channel. After a Stall, this bit must be cleared by software to resume normal operation.</li><li>0: The DMA0 transfer of the selected channel is not being stalled.</li><li>1: The DMA0 transfer of the selected channel is stalled.</li></ul> |

| 4     | ENDIAN                 | Data Transfer Endianness.                                                                                                                                                                                                                                                                                        |

|       |                        | <ul><li>This bit sets the byte order for multi-byte transfers. This is only relevant for two or three byte transfers. The value of this bit does not matter for single byte transfers.</li><li>0: Little Endian</li><li>1: Big Endian</li></ul>                                                                  |

| 3:0   | PERIPH[2:0]            | Peripheral Selection of The Selected Channel.                                                                                                                                                                                                                                                                    |

|       |                        | These bits choose one of the nine DMA0 transfer functions for the selected channel.<br>0000: XRAM to ENC0L/M/H<br>0001: ENC0L/M/H sfrs to XRAM<br>0010: XRAM to CRC1IN sfr<br>0011: XRAM to SPI1DAT sfr<br>0100: SPI1DAT sfr to XRAM<br>0101: XRAM to AES0KIN sfr                                                |

|       |                        | 0110: XRAM to AES0BIN sfr                                                                                                                                                                                                                                                                                        |

|       |                        | 0111: XRAM to AES0XIN sfr<br>1000: AES0YOUT sfr to XRAM                                                                                                                                                                                                                                                          |

|       |                        |                                                                                                                                                                                                                                                                                                                  |

| Note: | This sfr is a DMA chan | nel indirect register. Select the desired channel first using the DMA0SEL sfr.                                                                                                                                                                                                                                   |

### 12.2. 32-bit CRC Algorithm

The C8051F41x CRC unit calculates the 32-bit CRC using a poly of 0x04C11DB7. The CRC-32 algorithm is "reflected", meaning that all of the input bytes and the final 32-bit output are bit-reversed in the processing engine. The following is a description of a simplified CRC algorithm that produces results identical to the hardware:

- Step 1. XOR the least-significant byte of the current CRC result with the input byte. If this is the first iteration of the CRC unit, the current CRC result will be the set initial value (0x00000000 or 0xFFFFFFF).

- Step 2. Right-shift the CRC result.

- Step 3. If the LSB of the CRC result is set, XOR the CRC result with the reflected polynomial (0xEDB88320).

- Step 4. Repeat at Step 2 for the number of input bits (8).

For example, the 32-bit 'F41x CRC algorithm can be described by the following code:

```

unsigned long UpdateCRC (unsigned long CRC_acc, unsigned char CRC_input)

{

unsigned char i; // loop counter

#define POLY 0xEDB88320 // bit-reversed version of the poly 0x04C11DB7

// Create the CRC "dividend" for polynomial arithmetic (binary arithmetic

// with no carries)

CRC_acc = CRC_acc ^ CRC_input;

// "Divide" the poly into the dividend using CRC XOR subtraction

// CRC acc holds the "remainder" of each divide

11

// Only complete this division for 8 bits since input is 1 byte

for (i = 0; i < 8; i++)

{

// Check if the MSB is set (if MSB is 1, then the POLY can "divide"

// into the "dividend")

if ((CRC_acc & 0x0000001) == 0x0000001)

{

// if so, shift the CRC value, and XOR "subtract" the poly

CRC_acc = CRC_acc >> 1;

CRC_acc ^= POLY;

}

else

ł

// if not, just shift the CRC value

CRC_acc = CRC_acc >> 1;

}

}

// Return the final remainder (CRC value)

return CRC_acc;

}

```

The following table lists several input values and the associated outputs using the 32-bit 'F41x CRC algorithm (an initial value of 0xFFFFFFF is used):

# SFR Definition 12.4. CRC0AUTO: CRC0 Automatic Control

| Bit   | 7      | 6       | 5 | 4           | 3 | 2 | 1   | 0 |  |  |

|-------|--------|---------|---|-------------|---|---|-----|---|--|--|

| Name  | AUTOEN | CRCDONE |   | CRC0ST[5:0] |   |   |     |   |  |  |

| Туре  | R/W    |         |   |             |   |   | R/W |   |  |  |

| Reset | 0      | 1       | 0 | 0           | 0 | 0 | 0   | 0 |  |  |

#### SFR Page = 0xF; SFR Address = 0x96

| Bit | Name        | Function                                                                                                                                                                                                                                                                                            |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AUTOEN      | Automatic CRC Calculation Enable.                                                                                                                                                                                                                                                                   |

|     |             | When AUTOEN is set to 1, any write to CRC0CN will initiate an automatic CRC starting at flash sector CRC0ST and continuing for CRC0CNT sectors.                                                                                                                                                     |

| 6   | CRCDONE     | CRCDONE Automatic CRC Calculation Complete.                                                                                                                                                                                                                                                         |

|     |             | Set to 0 when a CRC calculation is in progress. Note that code execution is stopped during a CRC calculation, therefore reads from firmware will always return 1.                                                                                                                                   |

| 5:0 | CRC0ST[5:0] | Automatic CRC Calculation Starting Flash Sector.                                                                                                                                                                                                                                                    |

|     |             | These bits specify the flash sector to start the automatic CRC calculation. The starting address of the first flash sector included in the automatic CRC calculation is CRC0ST x 1024. For 128 kB devices, pages 32–63 access the upper code bank as selected by the IFBANK bits in the PSBANK SFR. |

# SFR Definition 12.5. CRC0CNT: CRC0 Automatic Flash Sector Count

| Bit   | 7   | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|--------------|---|---|---|---|---|---|--|

| Name  |     | CRC0CNT[5:0] |   |   |   |   |   |   |  |

| Туре  | R/W |              |   |   |   |   |   |   |  |

| Reset | 0   | 0            | 0 | 0 | 0 | 0 | 0 | 0 |  |

#### SFR Page = 0xF; SFR Address = 0x97

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                         |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused       | Read = 00b; Write = Don't Care.                                                                                                                                                                                                                                                                                                                                  |

| 5:0 | CRC0CNT[5:0] | Automatic CRC Calculation Flash Sector Count.                                                                                                                                                                                                                                                                                                                    |

|     |              | These bits specify the number of flash sectors to include in an automatic CRC cal-<br>culation. The starting address of the last flash sector included in the automatic<br>CRC calculation is (CRC0ST+CRC0CNT) x 1024. The last page should not<br>exceed page 63. Setting both CRC0ST and CRC0CNT to 0 will perform a CRC<br>over the 64kB banked memory space. |

#### 15.4. Three-out-of-Six Decoding

Three-out-of-Six decoding is a similar inverse process. Three bytes of encoded data are written to ENC2-0. The DEC bit is set to initiate decoding. The READY bit will be set when decoding is complete. The ERROR bit will be set if the input date is not valid Three-out-of-Six data.

The Three-out-of-Six encoder decode process is also symmetric. Two bytes of arbitrary data may be written to ENC0M-ENC0L, then encoded, then decoding will yield the original data.

|        | Input  |     | Decoded Output |     |      |  |

|--------|--------|-----|----------------|-----|------|--|

|        | Symbol |     | Nibble         |     |      |  |

| bin    | octal  | dec | dec            | hex | bin  |  |

| 001011 | 13     | 11  | 3              | 3   | 0011 |  |

| 001101 | 15     | 13  | 1              | 1   | 0001 |  |

| 001110 | 16     | 14  | 2              | 2   | 0010 |  |

| 010011 | 23     | 19  | 7              | 7   | 0111 |  |

| 010110 | 26     | 22  | 0              | 0   | 0000 |  |

| 011001 | 31     | 25  | 5              | 5   | 0101 |  |

| 011010 | 32     | 26  | 6              | 6   | 0110 |  |

| 011100 | 34     | 28  | 4              | 4   | 0100 |  |

| 100011 | 43     | 35  | 11             | В   | 1011 |  |

| 100101 | 45     | 37  | 9              | 9   | 1001 |  |

| 100110 | 46     | 38  | 10             | А   | 1010 |  |

| 101001 | 51     | 41  | 15             | F   | 1111 |  |

| 101100 | 54     | 44  | 8              | 8   | 1000 |  |

| 110001 | 61     | 49  | 13             | D   | 1101 |  |

| 110010 | 62     | 50  | 14             | Е   | 1110 |  |

| 110100 | 64     | 52  | 12             | С   | 1100 |  |

Table 15.5. Three-out-of-Six Decoding

# Table 16.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | SFR Page       | Description                 | Page |

|----------|---------|----------------|-----------------------------|------|

| TL0      | 0x8A    | 0x0            | Timer/Counter 0 Low         | 452  |

| TL1      | 0x8B    | 0x0            | Timer/Counter 1 Low         | 452  |

| TMOD     | 0x89    | 0x0            | Timer/Counter Mode          | 451  |

| TMR2CN   | 0xC8    | All Pages      | Timer/Counter 2 Control     | 457  |

| TMR2H    | 0xCD    | 0x0            | Timer/Counter 2 High        | 459  |

| TMR2L    | 0xCC    | 0x0            | Timer/Counter 2 Low         | 459  |

| TMR2RLH  | 0xCB    | 0x0            | Timer/Counter 2 Reload High | 458  |

| TMR2RLL  | 0xCA    | 0x0            | Timer/Counter 2 Reload Low  | 458  |

| TMR3CN   | 0x91    | 0x0            | Timer/Counter 3 Control     | 463  |

| TMR3H    | 0x95    | 0x0            | Timer/Counter 3 High        | 465  |

| TMR3L    | 0x94    | 0x0            | Timer/Counter 3 Low         | 465  |

| TMR3RLH  | 0x93    | 0x0            | Timer/Counter 3 Reload High | 464  |

| TMR3RLL  | 0x92    | 0x0            | Timer/Counter 3 Reload Low  | 464  |

| TOFFH    | 0xBB    | 0xF            | Temperature Offset High     | 99   |

| TOFFL    | 0xBD    | 0xF            | Temperature Offset Low      | 99   |

| VDM0CN   | 0xFF    | All Pages      | VDD Monitor Control         | 282  |

| XBR0     | 0xE1    | 0x0 and<br>0xF | Port I/O Crossbar Control 0 | 358  |

| XBR1     | 0xE2    | 0x0 and<br>0xF | Port I/O Crossbar Control 1 | 359  |

| XBR2     | 0xE3    | 0x0 and<br>0xF | Port I/O Crossbar Control 2 | 360  |

The level of flash security depends on the flash access method. The three flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 18.1 summarizes the flash security features of the C8051F96x devices.

| Action                                                                   | C2 Debug                | User Firmware executing from: |                   |  |  |

|--------------------------------------------------------------------------|-------------------------|-------------------------------|-------------------|--|--|

|                                                                          | Interface               | an unlocked page              | a locked page     |  |  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)      | Permitted               | Permitted                     | Permitted         |  |  |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)        | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Read or Write page containing Lock Byte<br>(if no pages are locked)      | Permitted               | Permitted                     | Permitted         |  |  |

| Read or Write page containing Lock Byte<br>(if any page is locked)       | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Read contents of Lock Byte<br>(if no pages are locked)                   | Permitted               | Permitted                     | Permitted         |  |  |

| Read contents of Lock Byte<br>(if any page is locked)                    | Not Permitted           | Flash Error Reset             | Permitted         |  |  |

| Erase page containing Lock Byte<br>(if no pages are locked)              | Permitted               | Flash Error Reset             | Flash Error Reset |  |  |

| Erase page containing Lock Byte—Unlock all pages (if any page is locked) | C2 Device Erase<br>Only | Flash Error Reset             | Flash Error Reset |  |  |

| Lock additional pages<br>(change 1s to 0s in the Lock Byte)              | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

| Unlock individual pages<br>(change 0s to 1s in the Lock Byte)            | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

| Read, Write or Erase Reserved Area                                       | Not Permitted           | Flash Error Reset             | Flash Error Reset |  |  |

| Table 18.1. | Flash   | Security | Summarv |

|-------------|---------|----------|---------|

|             | 1 10011 | occurry  | Gammary |

C2 Device Erase—Erases all flash pages including the page containing the Lock Byte.

Flash Error Reset—Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset).

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

# SFR Definition 19.2. PCLKEN: Peripheral Clock Enable

| Bit   | 7   | 6   | 5   | 4   | 3           | 2 | 1 | 0 |

|-------|-----|-----|-----|-----|-------------|---|---|---|

| Name  |     |     |     |     | PCLKEN[3:0] |   |   |   |

| Туре  | R/W | R/W | R/W | R/W | R/W         |   |   |   |

| Reset |     |     |     |     |             |   |   |   |

#### SFR Page = 0xF; SFR Address = 0xFE

| Bit | Name    | Function                                                                                                                                                                                                                                           |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Unused  | Read = 0b; Write = don't care.                                                                                                                                                                                                                     |

| 3   | PCLKEN3 | Clock Enable Controls for Peripherals in Low Power Idle Mode.<br>0: Disable clocks to the SmaRTClock, Pulse Counter, and PMU0 in Low Power Idle<br>Mode.<br>1: Enable clocks to the SmaRTClock, Pulse Counter, and PMU0 in Low Power Idle<br>Mode. |

| 2   | PCLKEN2 | Clock Enable Controls for Peripherals in Low Power Idle Mode.<br>0: Disable clocks to Timer 0, Timer 1, Timer 2, and CRC0 in Low Power Idle Mode.<br>1: Enable clocks to Timer 0, Timer 1, Timer 2, and CRC0 in Low Power Idle Mode.               |

| 1   | PCLKEN1 | Clock Enable Controls for Peripherals in Low Power Idle Mode.<br>0: Disableclocks to ADC0 and PCA0 in Low Power Idle Mode.<br>1: Enable clocks to ADC0 and PCA0 in Low Power Idle Mode.                                                            |

| 0   | PCLKEN0 | Clock Enable Controls for Peripherals in Low Power Idle Mode.<br>0: Disable clocks to UART0, Timer 3, SPI0, and the SMBus in Low Power Idle Mode.<br>1: Enable clocks to UART0, Timer 3, SPI0, and the SMBus in Low Power Idle Mode.               |

# SFR Definition 19.6. PMU0MD: Power Management Unit Mode

| Bit   | 7     | 6      | 5      | 4   | 3   | 2   | 1   | 0   |

|-------|-------|--------|--------|-----|-----|-----|-----|-----|

| Name  | RTCOE | WAKEOE | MONDIS |     |     |     |     |     |

| Туре  | R/W   | R/W    | R/W    | R/W | R/W | R/W | R/W | R/W |

| Reset | 0     | 0      | 0      | 0   | 0   | 0   | 0   | 0   |

#### SFR Page = 0x0; SFR Address = 0xB3

| Bit | Name   | Function                                                                                                                                               |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RTCOE  | Buffered SmaRTClock Output Enable.                                                                                                                     |

|     |        | Enables the buffered SmaRTClock oscillator output on P0.2.<br>0: Buffered SmaRTClock output not enabled.<br>1: Buffered SmaRTClock output not enabled. |

| 6   | WAKEOE | Wakeup Request Output Enable.                                                                                                                          |

|     |        | Enables the Sleep Mode wake-up request signal on P0.3.                                                                                                 |

|     |        | 0: Wake-up request signal is not enabled.                                                                                                              |

|     |        | 1: Wake-up request signal is enabled.                                                                                                                  |

| 5   | MONDIS | POR Supply Monitor Disable.                                                                                                                            |

|     |        | Writing a 1 to this bit disables the POR supply monitor.                                                                                               |

| 4:0 | Unused | Read = 00000b. Write = Don't Care.                                                                                                                     |

# SFR Definition 25.16. PC0CMP1H: PC0 Comparator 1 High (MSB)

| Bit   | 7            | 6                  | 5                          | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------|--------------------|----------------------------|---|---|---|---|---|--|--|

| Nam   | 9            | PC0CMP1H[23:16]    |                            |   |   |   |   |   |  |  |

| Туре  | )            | R/W                |                            |   |   |   |   |   |  |  |

| Rese  | et 0         | 0                  | 0                          | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A | ddress = 0xF | 3; SFR Page        | e = 0x2                    |   |   |   |   |   |  |  |

| Bit   | Name         | •                  | Function                   |   |   |   |   |   |  |  |

| 7:0   | PC0CMP1H     | [23:16] <b>P</b> ( | PC0 Comparator 1 High Byte |   |   |   |   |   |  |  |

Bits 23:16 of Counter 0.

### SFR Definition 25.17. PC0CMP1M: PC0 Comparator 1 Middle

| Bit     | 7            | 6           | 5                            | 4         | 3              | 2 | 1 | 0 |  |  |  |

|---------|--------------|-------------|------------------------------|-----------|----------------|---|---|---|--|--|--|

| Name PC |              |             |                              | PC0CMF    | PC0CMP1M[15:8] |   |   |   |  |  |  |

| Туре    | )            | R/W         |                              |           |                |   |   |   |  |  |  |

| Rese    | et 0         | 0           | 0                            | 0         | 0              | 0 | 0 | 0 |  |  |  |

| SFR A   | ddress = 0xF | 2; SFR Page | e = 0x2                      |           |                |   |   | - |  |  |  |

| Bit     | Name         | 9           | Function                     |           |                |   |   |   |  |  |  |

| 7:0     | PC0CMP1N     | A[15:8] P   | PC0 Comparator 1 Middle Byte |           |                |   |   |   |  |  |  |

|         |              | Bi          | ts 15:8 of Co                | ounter 0. |                |   |   |   |  |  |  |

# SFR Definition 25.18. PC0CMP1L: PC0 Comparator 1 Low (LSB)

| Bit   | 7 | 6             | 5 | 4  | 3 | 2 | 1 | 0 |

|-------|---|---------------|---|----|---|---|---|---|

| Name  |   | PC0CMP1L[7:0] |   |    |   |   |   |   |

| Туре  |   |               |   | R/ | W |   |   |   |

| Reset | 0 | 0             | 0 | 0  | 0 | 0 | 0 | 0 |

SFR Address = 0xF1; SFR Page = 0x2

| Bit | Name          | Function                  |

|-----|---------------|---------------------------|

| 7:0 | PC0CMP1L[7:0] | PC0 Comparator 1 Low Byte |

|     |               | Bits 7:0 of Counter 0.    |

**Note:** PC0CMP1L must be written last after writing PC0CMP1M and PC0CMP1H. After writing PC0CMP1L the synchronization into the PC clock domain can take 2 RTC clock cycles.

### 26.3. LCD Contrast Adjustment

The LCD Bias voltages which determine the LCD contrast are generated using the VBAT supply voltage or the on-chip charge pump. There are four contrast control modes to accomodate a wide variety of applications and supply voltages. The target contrast voltage is programmable in 60 mV steps from 1.9 to 3.72 V. The LCD contrast voltage is controlled by the LCD0CNTRST register and the contrast control mode is selected by setting the appropriate bits in the LCD0MSCN, LCD0MSCF, LCD0PWR, and LCD0VBMCN registers.

**Note:** An external 10 µF decoupling capacitor is required on the VLCD pin to create a charge reservoir at the output of the charge pump.

| Mode                                                  | LCD0MSCN.2 | LCD0MSCF.0 | LCD0PWR.3 | LCD0VBMCN.7 |  |  |  |  |

|-------------------------------------------------------|------------|------------|-----------|-------------|--|--|--|--|

| 1                                                     | 0          | 1          | 0         | 0           |  |  |  |  |

| 2                                                     | 0          | 1          | 1         | 1           |  |  |  |  |

| 3                                                     | 1*         | 0          | 1         | 1           |  |  |  |  |

| 4                                                     | 1*         | 0          | 0         | 1           |  |  |  |  |

| * May be set to 0 to support increased load currents. |            |            |           |             |  |  |  |  |

#### Table 26.1. Bit Configurations to select Contrast Control Modes

#### 26.3.1. Contrast Control Mode 1 (Bypass Mode)

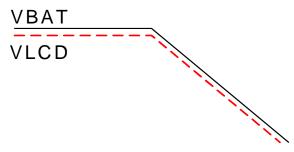

In Contrast Control Mode 1, the contrast control circuitry is disabled and the VLCD voltage follows the VBAT supply voltage, as shown in Figure 26.3. This mode is useful in systems where the VBAT voltage always remains constant and will provide the lowest LCD power consumption. Bypass Mode is selected using the following procedure:

- 1. Clear Bit 2 of the LCD0MSCN register to 0b (LCD0MSCN &= ~0x04)

- 2. Set Bit 0 of the LCD0MSCF register to 1b (LCD0MSCF |= 0x01)

- 3. Clear Bit 3 of the LCD0PWR register to 0b (LCD0PWR &= ~0x08)

- 4. Clear Bit 7 of the LCD0VBMCN register to 0b (LCD0VBMCN &= ~0x80)

Figure 26.3. Contrast Control Mode 1

# C8051F96x

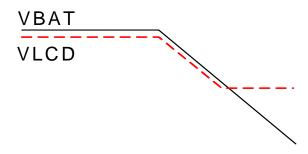

#### 26.3.2. Contrast Control Mode 2 (Minimum Contrast Mode)

In Contrast Control Mode 2, a minimum contrast voltage is maintained, as shown in Figure 26.4. The VLCD supply is powered directly from VBAT as long as VBAT is higher than the programmable VBAT monitor threshold voltage. As soon as the VBAT supply monitor detects that VBAT has dropped below the programmed value, the charge pump will be automatically enabled in order to acheive the desired minimum contrast voltage on VLCD. Minimum Contrast Mode is selected using the following procedure:

- 1. Clear Bit 2 of the LCD0MSCN register to 0b (LCD0MSCN &= ~0x04)

- 2. Set Bit 0 of the LCD0MSCF register to 1b (LCD0MSCF |= 0x01)

- 3. Set Bit 3 of the LCD0PWR register to 1b (LCD0PWR |= 0x08)

- 4. Set Bit 7 of the LCD0VBMCN register to 1b (LCD0VBMCN |= 0x80)

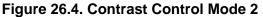

#### 26.3.3. Contrast Control Mode 3 (Constant Contrast Mode)

In Contrast Control Mode 3, a constant contrast voltage is maintained. The VLCD supply is regulated to the programmed contrast voltage using a variable resistor between VBAT and VLCD as long as VBAT is higher than the programmable VBAT monitor threshold voltage. As soon as the VBAT supply monitor detects that VBAT has dropped below the programmed value, the charge pump will be automatically enabled in order to acheive the desired contrast voltage on VLCD. Constant Contrast Mode is selected using the following procedure:

- 1. Set Bit 2 of the LCD0MSCN register to 1b (LCD0MSCN |= 0x04)

- 2. Clear Bit 0 of the LCD0MSCF register to 0b (LCD0MSCF &= ~0x01)

- 3. Set Bit 3 of the LCD0PWR register to 1b (LCD0PWR |= 0x08)

- 4. Set Bit 7 of the LCD0VBMCN register to 1b (LCD0VBMCN |= 0x80)

Figure 26.5. Contrast Control Mode 3

# 26.6. Blinking LCD Segments

The LCD driver supports blinking LCD applications such as clock applications where the ":" separator toggles on and off once per second. If the LCD is only displaying the hours and minutes, then the device only needs to wake up once per minute to update the display. The once per second blinking is automatically handled by the C8051F96x.

The LCD0BLINK register can be used to enable blinking on any LCD segment connected to the LCD0 or LCD1 segment pin. In static mode, a maximum of 2 segments can blink. In 2-mux mode, a maximum of 4 segments can blink; in 3-mux mode, a maximum of 6 segments can blink; and in 4-mux mode, a maximum of 8 segments can blink. The LCD0BLINK mask register targets the same LCD segments as the LCD0D0 register. If an LCD0BLINK bit corresponding to an LCD segment is set to 1, then that segment will toggle at the frequency set by the LCD0TOGR register without any software intervention.

#### SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask

| Bit   | 7   | 6              | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|----------------|-----|-----|-----|-----|-----|-----|

| Name  |     | LCD0BLINK[7:0] |     |     |     |     |     |     |

| Туре  | R/W | R/W            | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0              | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Page = 0x2; SFR Address = 0x9E

| Bit | Name | Function                                                                                                                                                                                                                                                                                      |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 |      | <b>LCD0 Blink Mask.</b><br>Each bit maps to a specific LCD segment connected to the LCD0 and LCD1 segment pins. A value of 1 indicates that the segment is blinking. A value of 0 indicates that the segment is not blinking. This bit to segment mapping is the same as the LCD0D0 register. |

# SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration

| Bit   | 7             | 6           | 5        | 4   | 3   | 2   | 1   | 0   |

|-------|---------------|-------------|----------|-----|-----|-----|-----|-----|

| Name  | e             |             |          |     |     |     |     |     |

| Туре  | R/W           | R/W         | R/W      | R/W | R/W | R/W | R/W | R/W |

| Rese  | <b>t</b> 0    | 0           | 1        | 1   | 0   | 0   | 1   | 0   |

| SFR P | age = 0xF; SF | R Address : | = 0xAC   |     |     |     |     |     |

| Bit   | Name          |             | Function |     |     |     |     |     |

| 7:0   | Reserved      | Must write  | e 0x32.  |     |     |     |     |     |

# SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode

| Bit   | 7              | 6         | 5       | 4   | 3        | 2   | 1   | 0   |

|-------|----------------|-----------|---------|-----|----------|-----|-----|-----|

| Nam   | e              |           |         |     |          |     |     |     |

| Туре  | e R/W          | R/W       | R/W     | R/W | R/W      | R/W | R/W | R/W |

| Rese  | et O           | 1         | 0       | 0   | 1        | 0   | 1   | 0   |

| SFR F | Page = 0x2; SF | R Address | = 0xB6  |     |          |     |     |     |

| Bit   | Name           |           |         |     | Function |     |     |     |

| 7:0   | Reserved       | Must writ | e 0x4A. |     |          |     |     |     |

# SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name  |     |     |     |     |     |     |     |     |

| Туре  | R/W |

| Reset | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 1   |

#### SFR Page = 0x2; SFR Address = 0xAF

| Bit | Name     | Function         |

|-----|----------|------------------|

| 7:0 | Reserved | Must write 0x0B. |

# SFR Definition 27.16. P1MDOUT: Port1 Output Mode

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|--------------|---|---|---|---|---|---|

| Name  |   | P1MDOUT[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W          |   |   |   |   |   |   |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xA5

| Bit | Name         | Function                                                                                                                                                                                                                      |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDOUT[7:0] | Output Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                       |

|     |              | <ul><li>These bits control the digital driver even when the corresponding bit in register P1MDIN is logic 0.</li><li>0: Corresponding P1.n Output is open-drain.</li><li>1: Corresponding P1.n Output is push-pull.</li></ul> |

# SFR Definition 27.17. P1DRV: Port1 Drive Strength

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | P1DRV[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0xA5

| Bit | Name       | Function                                                                                                                                                                                               |  |  |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |  |  |  |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |  |  |  |

| Parameter                | Description                                                     | Min                          | Max                     | Units |

|--------------------------|-----------------------------------------------------------------|------------------------------|-------------------------|-------|

| Master Mode              | Timing (See Figure 31.8 and Figure 31.9)                        |                              |                         |       |

| Т <sub>МСКН</sub>        | SCK High Time                                                   | 1 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>MCKL</sub>        | SCK Low Time                                                    | 1 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>MIS</sub>         | MISO Valid to SCK Shift Edge                                    | 1 x T <sub>SYSCLK</sub> + 20 | _                       | ns    |

| Т <sub>МІН</sub>         | SCK Shift Edge to MISO Change                                   | 0                            | _                       | ns    |

| Slave Mode 1             | Fiming (See Figure 31.10 and Figure 31.11)                      |                              | L                       |       |

| T <sub>SE</sub>          | NSS Falling to First SCK Edge                                   | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SD</sub>          | Last SCK Edge to NSS Rising                                     | 2 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>SEZ</sub>         | NSS Falling to MISO Valid                                       | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>         | NSS Rising to MISO High-Z                                       | _                            | 4 x T <sub>SYSCLK</sub> | ns    |

| Т <sub>СКН</sub>         | SCK High Time                                                   | 5 x T <sub>SYSCLK</sub>      |                         | ns    |

| T <sub>CKL</sub>         | SCK Low Time                                                    | 5 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SIS</sub>         | MOSI Valid to SCK Sample Edge                                   | 2 x T <sub>SYSCLK</sub>      | _                       | ns    |

| T <sub>SIH</sub>         | SCK Sample Edge to MOSI Change                                  | 2 x T <sub>SYSCLK</sub>      |                         | ns    |

| Т <sub>SOH</sub>         | SCK Shift Edge to MISO Change                                   | —                            | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SLH</sub>         | Last SCK Edge to MISO Change<br>(CKPHA = 1 ONLY)                | 6 x T <sub>SYSCLK</sub>      | 8 x T <sub>SYSCLK</sub> | ns    |

| Note: T <sub>SYSCL</sub> | $_{\rm c}$ is equal to one period of the device system clock (S | YSCLK).                      | 1                       | L     |

Table 31.1. SPI Slave Timing Parameters

# C8051F96x

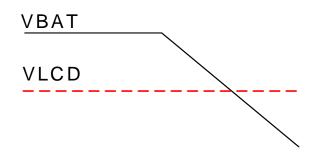

Figure 33.9. PCA 9, 10 and 11-Bit PWM Mode Diagram

#### 33.3.6. 16-Bit Pulse Width Modulator Mode

A PCA module may also be operated in 16-Bit PWM mode. 16-bit PWM mode is independent of the other (8/9/10/11-bit) PWM modes. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. If the MATn bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF flag in PCA0CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 33.4.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Duty Cycle =

$$\frac{(65536 - PCA0CPn)}{65536}$$

#### Equation 33.4. 16-Bit PWM Duty Cycle

Using Equation 33.4, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.