# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 34                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                  |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 8.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                       |

| Data Converters            | A/D 16x10b/12b                                                    |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 40-VFQFN Exposed Pad                                              |

| Supplier Device Package    | 40-QFN (6x6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f961-b-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Registers

| SFR | Definition 5.1. ADC0CN: ADC0 Control                            | 86 |

|-----|-----------------------------------------------------------------|----|

| SFR | Definition 5.2. ADC0CF: ADC0 Configuration                      | 87 |

|     | Definition 5.3. ADC0AC: ADC0 Accumulator Configuration          |    |

| SFR | Definition 5.4. ADC0PWR: ADC0 Burst Mode Power-Up Time          | 89 |

|     | Definition 5.5. ADC0TK: ADC0 Burst Mode Track Time              |    |

| SFR | Definition 5.6. ADC0H: ADC0 Data Word High Byte                 | 91 |

|     | Definition 5.7. ADC0L: ADC0 Data Word Low Byte                  |    |

|     | Definition 5.8. ADC0GTH: ADC0 Greater-Than High Byte            |    |

| SFR | Definition 5.9. ADC0GTL: ADC0 Greater-Than Low Byte             | 92 |

| SFR | Definition 5.10. ADC0LTH: ADC0 Less-Than High Byte              | 93 |

| SFR | Definition 5.11. ADC0LTL: ADC0 Less-Than Low Byte               | 93 |

| SFR | Definition 5.12. ADC0MX: ADC0 Input Channel Select              | 96 |

| SFR | Definition 5.13. TOFFH: Temperature Sensor Offset High Byte     | 99 |

| SFR | Definition 5.14. TOFFL: Temperature Sensor Offset Low Byte      | 99 |

|     | Definition 5.15. REF0CN: Voltage Reference Control              |    |

|     | Definition 6.1. IREF0CN: Current Reference Control              |    |

| SFR | Definition 6.2. IREF0CF: Current Reference Configuration        | 04 |

|     | Definition 7.1. CPT0CN: Comparator 0 Control                    |    |

|     | Definition 7.2. CPT0MD: Comparator 0 Mode Selection             |    |

|     | Definition 7.3. CPT1CN: Comparator 1 Control1                   |    |

| SFR | Definition 7.4. CPT1MD: Comparator 1 Mode Selection             | 11 |

|     | Definition 7.5. CPT0MX: Comparator0 Input Channel Select        |    |

|     | Definition 7.6. CPT1MX: Comparator1 Input Channel Select        |    |

|     | Definition 8.1. DPL: Data Pointer Low Byte1                     |    |

| SFR | Definition 8.2. DPH: Data Pointer High Byte1                    | 21 |

|     | Definition 8.3. SP: Stack Pointer 1                             |    |

|     | Definition 8.4. ACC: Accumulator 12                             |    |

|     | Definition 8.5. B: B Register 1                                 |    |

|     | Definition 8.6. PSW: Program Status Word1                       |    |

|     | Definition 9.1. PSBANK: Program Space Bank Select               |    |

|     | Definition 10.1. EMI0CN: External Memory Interface Control      |    |

|     | Definition 10.2. EMI0CF: External Memory Configuration          |    |

|     | Definition 10.3. EMI0TC: External Memory Timing Control         |    |

|     | Definition 11.1. DMA0EN: DMA0 Channel Enable                    |    |

|     | Definition 11.2. DMA0INT: DMA0 Full-Length Interrupt            |    |

|     | Definition 11.3. DMA0MINT: DMA0 Mid-Point Interrupt             |    |

|     | Definition 11.4. DMA0BUSY: DMA0 Busy 1                          |    |

|     | Definition 11.5. DMA0SEL: DMA0 Channel Select for Configuration |    |

|     | Definition 11.6. DMA0NMD: DMA Channel Mode                      |    |

|     | Definition 11.7. DMA0NCF: DMA Channel Configuration             |    |

|     | Definition 11.8. DMA0NBAH: Memory Base Address High Byte 1      |    |

|     | Definition 11.9. DMA0NBAL: Memory Base Address Low Byte         |    |

| SFR | Definition 11.10. DMA0NAOH: Memory Address Offset High Byte     | 58 |

| SFR Definition 25.19. PC0HIST: PC0 History       331         SFR Definition 25.21. PC0INT1: PC0 Interrupt 0       332         SFR Definition 25.21. PC0INT1: PC0 Interrupt 1       333         SFR Definition 26.1. LCD0CNT: LCD0 Control Register       335         SFR Definition 26.1. LCD0CNT: LCD0 Contrast Adjustment       341         SFR Definition 26.4. LCD0MSCN: LCD0 Master Control       342         SFR Definition 26.5. LCD0MSCF: LCD0 Master Configuration       343         SFR Definition 26.6. LCD0PWR: LCD0 VBAT Monitor Control       344         SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.8. LCD0CLKDIVL: LCD Refresh Rate Prescaler Ligh Byte       345         SFR Definition 26.10. LCD0EXDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.11. LCD0TGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCN: LCD0 Charge Pump Control       349         SFR Definition 26.15. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.14. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 27.1. XBR0: Port //O Crossbar Register 1       35                                                                |                                                                       |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|

| SFR Definition 25.21. PC0INT1: PC0 Interrupt 1       333         SFR Definition 26.1. LCD0DN: LCD0 Data       335         SFR Definition 26.3. LCD0CNTRST: LCD0 Control Register       337         SFR Definition 26.4. LCD0MSCN: LCD0 Master Control       342         SFR Definition 26.6. LCD0PWRS: LCD0 Master Configuration       343         SFR Definition 26.6. LCD0PWR: LCD0 VBAT Monitor Control       343         SFR Definition 26.6. LCD0CKDIV: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.9. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask.       346         SFR Definition 26.11. LCD0TGR: LCD0 Charge Pump Control       348         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Control       349         SFR Definition 26.15. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Mode       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       350         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       350         SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2       360 <td>SFR Definition 25.19. PC0HIST: PC0 History</td> <td> 331</td> | SFR Definition 25.19. PC0HIST: PC0 History                            | 331 |

| SFR Definition 26.1. LCD0Dn: LCD0 Data       335         SFR Definition 26.2. LCD0CN: LCD0 Control Register       337         SFR Definition 26.3. LCD0NSCF: LCD0 Master Control       341         SFR Definition 26.4. LCD0WSCN: LCD0 Master Control       342         SFR Definition 26.5. LCD0WSCF: LCD0 VBATE Monitor Control       343         SFR Definition 26.6. LCD0VBKCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.8. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Bink Mask       346         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCF: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Control       349         SFR Definition 26.15. LCD0CHPCF: LCD0 Charge Pump Mode       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.17. LCD00KF: LCD0 Buffer Control       349         SFR Definition 26.19. LCD0VBMCF: LCD0 Buffer Control       349         SFR Definition 27.1 XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 2       360                                                                                    | SFR Definition 25.20. PC0INT0: PC0 Interrupt 0                        | 332 |

| SFR Definition 26.2. LCD0CN: LCD0 Control Register       337         SFR Definition 26.3. LCD0CNTRST: LCD0 Contrast Adjustment       341         SFR Definition 26.4. LCD0MSCN: LCD0 Master Control       342         SFR Definition 26.6. LCD0PWR: LCD0 Power       343         SFR Definition 26.6. LCD0VBMCN: LCD0 Power       343         SFR Definition 26.6. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.0. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Toggle Rate       347         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Charge Pump Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.14. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Configuration       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       350         SFR Definition 26.17. LCD0BUFCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 1       350         SFR Definition 27.1. XBR2: Port I/O Crossbar Register 2       360         SFR Definition 27.5. P0MAT: Port0 Match Register       361         SFR Definition 27.7. P1MASK: Port1 Mask R                                                       | SFR Definition 25.21. PC0INT1: PC0 Interrupt 1                        | 333 |

| SFR Definition 26.3. LCD0CNTRST: LCD0 Contrast Adjustment       341         SFR Definition 26.4. LCD0MSCN: LCD0 Master Configuration       343         SFR Definition 26.6. LCD0WSCF: LCD0 VBAT Monitor Control       343         SFR Definition 26.6. LCD0VBMCN: LCD0 VBAT Monitor Control       343         SFR Definition 26.7. LCD0VBMCN: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.8. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Control       348         SFR Definition 26.15. LCD0CHPCN: LCD0 Charge Pump Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       349         SFR Definition 26.17. LCD0BUFCN: LCD0 Buffer Configuration       350         SFR Definition 26.18. LCD0BUFCN: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1 XBR: Port I/O Crossbar Register 0       358         SFR Definition 27.2 XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4 PMASK: Port0 Mask Register       361         SFR Definition 27.7 P1MASK: Port1 Mask Register       362         SFR Defini                                                       |                                                                       |     |

| SFR Definition 26.3. LCD0CNTRST: LCD0 Contrast Adjustment       341         SFR Definition 26.4. LCD0MSCN: LCD0 Master Configuration       343         SFR Definition 26.6. LCD0WSCF: LCD0 VBAT Monitor Control       343         SFR Definition 26.6. LCD0VBMCN: LCD0 VBAT Monitor Control       343         SFR Definition 26.7. LCD0VBMCN: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.8. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Control       348         SFR Definition 26.15. LCD0CHPCN: LCD0 Charge Pump Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       349         SFR Definition 26.17. LCD0BUFCN: LCD0 Buffer Configuration       350         SFR Definition 26.18. LCD0BUFCN: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1 XBR: Port I/O Crossbar Register 0       358         SFR Definition 27.2 XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4 PMASK: Port0 Mask Register       361         SFR Definition 27.7 P1MASK: Port1 Mask Register       362         SFR Defini                                                       | SFR Definition 26.2. LCD0CN: LCD0 Control Register                    | 337 |

| SFR Definition 26.4. LCD0MSCF: LCD0 Master Configuration       342         SFR Definition 26.5. LCD0MSCF: LCD0 Power       343         SFR Definition 26.6. LCD0VWR: LCD0 Power       343         SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.9. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD00HPCN: LCD0 Charge Pump Mode       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. POMASK: Port0 Mask Register       361         SFR Definition 27.7. PMAT: Port1 Mask Register       362         SFR Definition 27.7. P1MASK: Port1 Mask Register       362                                                                         | SFR Definition 26.3. LCD0CNTRST: LCD0 Contrast Adjustment             | 341 |

| SFR Definition 26.6. LCD0PWR: LCD0 Power       343         SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.8. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.9. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Control       349         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.7. P1MAT: Port0 Match Register       362         SFR Definition 27.7.9. POSKIP: Port0 Skip       364                                                                               | SFR Definition 26.4. LCD0MSCN: LCD0 Master Control                    | 342 |

| SFR Definition 26.6. LCD0PWR: LCD0 Power       343         SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.8. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.9. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Control       349         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.7. P1MAT: Port0 Match Register       362         SFR Definition 27.7.9. POSKIP: Port0 Skip       364                                                                               | SFR Definition 26.5. LCD0MSCF: LCD0 Master Configuration              | 343 |

| SFR Definition 26.8. LCDOCLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.9. LCDOCLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCDOBLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCDOTOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Configuration       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. PUMASK: Port0 Mask Register       361         SFR Definition 27.5. POMAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Mask Register       362         SFR Definition 27.10. POMDIN: Port0 Otuput Mode       365         SFR Definition 27.11. POMDOUT: Port0 Otuput Mode       3                                                                | SFR Definition 26.6. LCD0PWR: LCD0 Power                              | 343 |

| SFR Definition 26.8. LCDOCLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.9. LCDOCLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCDOBLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCDOTOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Configuration       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. PUMASK: Port0 Mask Register       361         SFR Definition 27.5. POMAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Mask Register       362         SFR Definition 27.10. POMDIN: Port0 Otuput Mode       365         SFR Definition 27.11. POMDOUT: Port0 Otuput Mode       3                                                                | SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control             | 344 |

| SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Configuration       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1 XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2 XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2       360         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.5. POMAT: Port0 Match Register       362         SFR Definition 27.7. P1MAT: Port1 Match Register       362         SFR Definition 27.8. P0: Port0       364         SFR Definition 27.10. POMDUN: Port0 Dutput Mode       365         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition                                                                                           |                                                                       |     |

| SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Mode       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration       350         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2 XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2       360         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.5. P0MAT: Port0 Match Register       362         SFR Definition 27.7. P1MASK: Port1 Mask Register       362         SFR Definition 27.8. P0: Port0       364         SFR Definition 27.1. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.10. P0MDIN: Port0 Input Mode       364         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.12. P0DRV: Port0 Skip       364         SFR Definition 27.14. P1SKIP: Port1 Skip                                                                                                 | SFR Definition 26.9. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte | 345 |

| SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Mode       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.15. LCD0BUFCF: LCD0 Buffer Configuration       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration       350         SFR Definition 26.18. LCD0BUFCF: LCD0 Buffer Mode       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. POMASK: Port0 Mask Register       360         SFR Definition 27.5. P0MAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Match Register       362         SFR Definition 27.7. P1MAT: Port1 Match Register       362         SFR Definition 27.8. P0: Port0       364         SFR Definition 27.10. P0MDIN: Port0 Input Mode       365         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.12. P0DRV: Port1 Output Mode       366         SFR Definition 27.13. P1: Port1       366         SFR Definition 27.14. P1SKIP: Port1 Skip       366         SFR Definition 27.15. P1MDIN: Port1 Input Mode       367 <td>SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask</td> <td> 346</td>                               | SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask                      | 346 |

| SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Mode       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.15. LCD0BUFCF: LCD0 Buffer Configuration       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration       350         SFR Definition 26.18. LCD0BUFCF: LCD0 Buffer Mode       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. POMASK: Port0 Mask Register       360         SFR Definition 27.5. P0MAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Match Register       362         SFR Definition 27.7. P1MAT: Port1 Match Register       362         SFR Definition 27.8. P0: Port0       364         SFR Definition 27.10. P0MDIN: Port0 Input Mode       365         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.12. P0DRV: Port1 Output Mode       366         SFR Definition 27.13. P1: Port1       366         SFR Definition 27.14. P1SKIP: Port1 Skip       366         SFR Definition 27.15. P1MDIN: Port1 Input Mode       367 <td>SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate</td> <td> 347</td>                               | SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate                      | 347 |

| SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       350         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Mode       350         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.3. XBR2: Port I/O Crossbar Register 1       359         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.5. P0MAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Mask Register       362         SFR Definition 27.7. P1MAT: Port1 Match Register       362         SFR Definition 27.10. P0MDIN: Port0 Skip       364         SFR Definition 27.10. P0MDIN: Port0 Output Mode       365         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.12. P0DRV: Port0 Drive Strength       366         SFR Definition 27.14. P1SKIP: Port1 Skip       367         SFR Definition 27.15. P1MDIN: Port1 Input Mode       368         SFR Definition 27.16. P1MDO                                                                                          | SFR Definition 26.12. LCD0CF: LCD0 Configuration                      | 348 |

| SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       350         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Mode       350         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.3. XBR2: Port I/O Crossbar Register 1       359         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.5. P0MAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Mask Register       362         SFR Definition 27.7. P1MAT: Port1 Match Register       362         SFR Definition 27.10. P0MDIN: Port0 Skip       364         SFR Definition 27.10. P0MDIN: Port0 Output Mode       365         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.12. P0DRV: Port0 Drive Strength       366         SFR Definition 27.14. P1SKIP: Port1 Skip       367         SFR Definition 27.15. P1MDIN: Port1 Input Mode       368         SFR Definition 27.16. P1MDO                                                                                          | SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control             | 348 |

| SFR Definition 26.15. LCD0CHPMD: LCD0 Charge Pump Mode349SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control349SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration350SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode350SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration350SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0358SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. POMASK: Port0 Mask Register361SFR Definition 27.5. POMAT: Port0 Match Register362SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register364SFR Definition 27.10. POMDIN: Port0 Skip364SFR Definition 27.11. POMDOUT: Port0 Output Mode365SFR Definition 27.12. PODRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port1 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Input Mode370SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                              |                                                                       |     |

| SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration350SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode350SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration350SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0358SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register362SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode366SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode368SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode </td <td></td> <td></td>                                                                                         |                                                                       |     |

| SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode350SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration350SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0358SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1367SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Ioutput Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Output Mode368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                            |                                                                       |     |

| SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode350SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration350SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0358SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1367SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Ioutput Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Output Mode368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                            | SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration            | 350 |

| SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0358SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode368SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Input Mode370SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                 |                                                                       |     |

| SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Net2369SFR Definition 27.19. P2SKIP: Port2 Net2369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                 | SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration      | 350 |

| SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Input Mode370SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0               | 358 |

| SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Input Mode370SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1               | 359 |

| SFR Definition 27.5. POMAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Input Mode370SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                       |     |

| SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SFR Definition 27.4. P0MASK: Port0 Mask Register                      | 361 |

| SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SFR Definition 27.5. P0MAT: Port0 Match Register                      | 361 |

| SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SFR Definition 27.6. P1MASK: Port1 Mask Register                      | 362 |

| SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SFR Definition 27.7. P1MAT: Port1 Match Register                      | 362 |

| SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SFR Definition 27.8. P0: Port0                                        | 364 |

| SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                       |     |

| SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SFR Definition 27.10. P0MDIN: Port0 Input Mode                        | 365 |

| SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                       |     |

| SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SFR Definition 27.12. P0DRV: Port0 Drive Strength                     | 366 |

| SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SFR Definition 27.13. P1: Port1                                       | 366 |

| SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SFR Definition 27.14. P1SKIP: Port1 Skip                              | 367 |

| SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SFR Definition 27.15. P1MDIN: Port1 Input Mode                        | 367 |

| SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                       |     |

| SFR Definition 27.19. P2SKIP: Port2 Skip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                       |     |

| SFR Definition 27.20. P2MDIN: Port2 Input Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                       |     |

| SFR Definition 27.20. P2MDIN: Port2 Input Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SFR Definition 27.19. P2SKIP: Port2 Skip                              | 369 |

| SFR Definition 27.21. P2MDOUT: Port2 Output Mode 370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SFR Definition 27.20. P2MDIN: Port2 Input Mode                        | 370 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                       |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                       |     |

| SFR Definition 27.23. P3: Port3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                       |     |

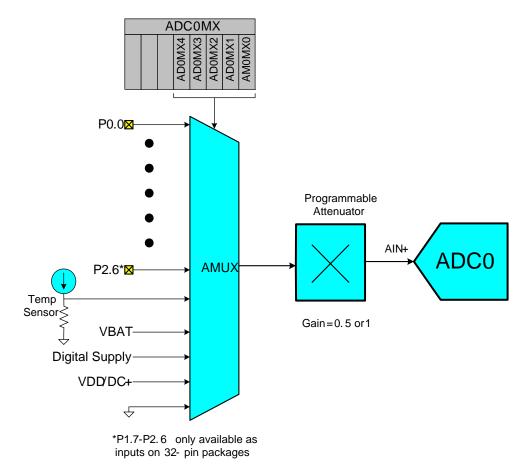

Figure 1.14. ADC0 Multiplexer Block Diagram

## 1.6. Programmable Current Reference (IREF0)

C8051F96x devices include an on-chip programmable current reference (source or sink) with two output current settings: low power mode and high current mode. The maximum current output in low power mode is 63  $\mu$ A (1  $\mu$ A steps) and the maximum current output in high current mode is 504  $\mu$ A (8  $\mu$ A steps).

#### 1.7. Comparators

C8051F96x devices include two on-chip programmable voltage comparators: Comparator 0 (CPT0) which is shown in Figure 1.15; Comparator 1 (CPT1) which is shown in Figure 1.16. The two comparators operate identically but may differ in their ability to be used as reset or wake-up sources. See Section "22. Reset Sources" on page 278 and the Section "19. Power Management" on page 257 for details on reset sources and low power mode wake-up sources, respectively.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0, CP1), or an asynchronous "raw" output (CP0A, CP1A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output when the device is in some low power modes.