Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | I²C, SPI, UART/USART                                             |

| Peripherals                | DMA, POR, PWM, WDT                                               |

| Number of I/O              | 57                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                 |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 8.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                      |

| Data Converters            | A/D 16x10b/12b                                                   |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 80-TQFP                                                          |

| Supplier Device Package    | 80-TQFP (12x12)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f962-b-gq |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name  | Pi     | Pin Numbers |       |                  | Description                                                |

|-------|--------|-------------|-------|------------------|------------------------------------------------------------|

| Name  | DQFN76 | TQFP80      | QFN40 | Туре             | Description                                                |

| P6.2  | B12    | 35          |       | D I/O or<br>A In | Port 6.2. See Port I/O Section for a complete description. |

| LCD26 |        |             |       | AO               | LCD Segment Pin 26                                         |

| P6.3  | B11    | 33          |       | D I/O or<br>A In | Port 6.3. See Port I/O Section for a complete description. |

| LCD27 |        |             |       | AO               | LCD Segment Pin 27                                         |

| P6.4  | B10    | 29          |       | D I/O or<br>A In | Port 6.4. See Port I/O Section for a complete description. |

| LCD28 |        |             |       | ΑO               | LCD Segment Pin 28                                         |

| P6.5  | B9     | 27          |       | D I/O or<br>A In | Port 6.5. See Port I/O Section for a complete description. |

| LCD29 |        |             |       | AO               | LCD Segment Pin 29                                         |

| P6.6  | B8     | 25          |       | D I/O or<br>A In | Port 6.6. See Port I/O Section for a complete description. |

| LCD30 |        |             |       | ΑO               | LCD Segment Pin 30                                         |

| P6.7  | D2     | 18          |       | D I/O or<br>A In | Port 6.7. See Port I/O Section for a complete description. |

| LCD31 |        |             |       | AO               | LCD Segment Pin 31                                         |

Table 3.1. Pin Definitions for the C8051F96x (Continued)

| Dimension | Min  | Nominal | Max |  |  |

|-----------|------|---------|-----|--|--|

| Θ         | 0°   | 3.5°    | 7°  |  |  |

| aaa       |      | 0.20    |     |  |  |

| bbb       | 0.20 |         |     |  |  |

| ccc       | 0.08 |         |     |  |  |

| ddd       |      | 0.08    |     |  |  |

| eee       |      | 0.05    |     |  |  |

#### Table 3.7. TQFP-80 Package Dimensions

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This package outline conforms to JEDEC MS-026, variant ADD.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# SFR Definition 6.2. IREF0CF: Current Reference Configuration

| Bit   | 7     | 6   | 5   | 4   | 3   | 2   | 1          | 0 |

|-------|-------|-----|-----|-----|-----|-----|------------|---|

| Name  | PWMEN |     |     |     |     |     | PWMSS[2:0] | ] |

| Туре  | R/W   | R/W | R/W | R/W | R/W | R/W |            |   |

| Reset | 0     | 0   | 0   | 0   | 0   | 0   | 0          | 0 |

#### SFR Page = 0xF; SFR Address = 0xB9

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PWMEN      | PWM Enhanced Mode Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | Enables the PWM Enhanced Mode.<br>0: PWM Enhanced Mode disabled.<br>1: PWM Enhanced Mode enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6:3 | Unused     | Read = 0000b, Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2:0 | PWMSS[2:0] | <b>PWM Source Select.</b> Selects the PCA channel to use for the fine-tuning control signal.         000: CEX0 selected as fine-tuning control signal.         001: CEX1 selected as fine-tuning control signal.         010: CEX2 selected as fine-tuning control signal.         011: CEX3 selected as fine-tuning control signal.         011: CEX3 selected as fine-tuning control signal.         100: CEX4 selected as fine-tuning control signal.         101: CEX5 selected as fine-tuning control signal.         101: CEX5 selected as fine tuning control signal.         All Other Values: Reserved. |

# 6.2. IREF0 Specifications

See Table 4.15 on page 73 for a detailed listing of IREF0 specifications.

#### 15.1. Manchester Encoding

To encode Manchester Data, first clear the MODE bit for Manchester encoding or decoding.

To encode, one byte of data is written to the data register ENCOL.

Setting the ENC bit will initiate encoding. After encoding, the encoded data will be in ENCOM and ENCOL. The upper nibble of the input data is encoded and placed in ENCOM. The lower nibble is encoded and placed in ENCOL.

Note that the input data should be readable in the data register until the encode bit is set. Once the READY bit is set, the input data has been replaced by the output data.

The ENC and DEC bits are self clearing. The READY bit is not cleared by hardware and must be cleared manually. The control register does not need to be bit addressable. The READY bit can be cleared while setting the ENC or DEC bit using a direct or immediate SFR mov instruction.

|     | Input Dat | a    | Encoded Output |     |     |  |  |

|-----|-----------|------|----------------|-----|-----|--|--|

|     | nibble    |      | byte           |     |     |  |  |

| dec | hex       | bin  | bin            | hex | dec |  |  |

| 0   | 0         | 0000 | 10101010       | AA  | 170 |  |  |

| 1   | 1         | 0001 | 10101001       | A9  | 169 |  |  |

| 2   | 2         | 0010 | 10100110       | A6  | 166 |  |  |

| 3   | 3         | 0011 | 10100101       | A5  | 165 |  |  |

| 4   | 4         | 0100 | 10011010       | 9A  | 154 |  |  |

| 5   | 5         | 0101 | 10011001       | 99  | 153 |  |  |

| 6   | 6         | 0110 | 10010110       | 96  | 150 |  |  |

| 7   | 7         | 0111 | 10010101       | 95  | 149 |  |  |

| 8   | 8         | 1000 | 01101010       | 6A  | 106 |  |  |

| 9   | 9         | 1001 | 01101001       | 69  | 105 |  |  |

| 10  | А         | 1010 | 01100110       | 66  | 102 |  |  |

| 11  | В         | 1011 | 01100101       | 65  | 101 |  |  |

| 12  | С         | 1100 | 01011010       | 5A  | 90  |  |  |

| 13  | D         | 1101 | 01011001       | 59  | 89  |  |  |

| 14  | Е         | 1110 | 01010110       | 56  | 86  |  |  |

| 15  | F         | 1111 | 01010101       | 55  | 85  |  |  |

Table 15.2. Manchester Encoding

# SFR Definition 16.1. SFRPGCN: SFR Page Control

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

| Name  |   |   |   |   |   |   |   | SFRPGEN |

| Туре  | R | R | R | R | R | R | R | R/W     |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1       |

#### ;SFR Page = 0xF; SFR Address = 0x8E

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | Unused  | Read = 0000000b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                          |

| 0   | SFRPGEN | SFR Automatic Page Control Enable.                                                                                                                                                                                                                                                                                                                                                                           |

|     |         | Upon interrupt, the C8051 Core will vector to the specified interrupt service routine. This bit controls the automatic preservation and restoration of the SFRPAGE by hard-ware.                                                                                                                                                                                                                             |

|     |         | 0: SFR Automatic Paging disabled. The C8051 core will neither preserve the SRF-<br>PAGE upon entering an interrupt service routine, nor restore the SFRPAGE upon<br>exiting the interrupt service routine. The interrupt service routine should preserve and<br>restore the active SFRPAGE in firmware.                                                                                                      |

|     |         | 1: SFR Automatic Paging enabled. The C8051 core will preserve the SFRPAGE upon<br>entering an interrupt service routine and restore the SFRPAGE upon exiting the Inter-<br>rupt service routine. The firmware does not need to preserve and restore the SFRP-<br>AGE in the interrupt service routing. However, firmware must set the SFRPAGE<br>within the interrupt service routine before accessing SFRs. |

# Table 16.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | SFR Page  | Description                         | Page |

|----------|---------|-----------|-------------------------------------|------|

| PC0INT0  | 0xFB    | 0x2       | PC0 Interrupt 0                     | 332  |

| PC0INT1  | 0xFC    | 0x2       | PC0 Interrupt 1                     | 333  |

| PC0MD    | 0xD9    | 0x2       | PC0 Mode                            | 321  |

| PC0PCF   | 0xD7    | 0x2       | PC0 Pull-up Configuration           | 322  |

| PC0STAT  | 0xC1    | 0x2       | PC0 Status                          | 324  |

| PC0TH    | 0xE4    | 0x2       | PC0 Threshold                       | 323  |

| PCA0CN   | 0xD8    | All Pages | PCA0 Control                        | 480  |

| PCA0CPH0 | 0xFC    | 0x0       | PCA0 Capture 0 High                 | 485  |

| PCA0CPH1 | 0xEA    | 0x0       | PCA0 Capture 1 High                 | 485  |

| PCA0CPH2 | 0xEC    | 0x0       | PCA0 Capture 2 High                 | 485  |

| PCA0CPH3 | 0xEE    | 0x0       | PCA0 Capture 3 High                 | 485  |

| PCA0CPH4 | 0xFE    | 0x0       | PCA0 Capture 4 High                 | 485  |

| PCA0CPH5 | 0xD3    | 0x0       | PCA0 Capture 5 High                 | 485  |

| PCA0CPL0 | 0xFB    | 0x0       | PCA0 Capture 0 Low                  | 485  |

| PCA0CPL1 | 0xE9    | 0x0       | PCA0 Capture 1 Low                  | 485  |

| PCA0CPL2 | 0xEB    | 0x0       | PCA0 Capture 2 Low                  | 485  |

| PCA0CPL3 | 0xED    | 0x0       | PCA0 Capture 3 Low                  | 485  |

| PCA0CPL4 | 0xFD    | 0x0       | PCA0 Capture 4 Low                  | 485  |

| PCA0CPL5 | 0xD2    | 0x0       | PCA0 Capture 5 Low                  | 485  |

| PCA0CPM0 | 0xDA    | 0x0       | PCA0 Module 0 Mode Register         | 483  |

| PCA0CPM1 | 0xDB    | 0x0       | PCA0 Module 1 Mode Register         | 483  |

| PCA0CPM2 | 0xDC    | 0x0       | PCA0 Module 2 Mode Register         | 483  |

| PCA0CPM3 | 0xDD    | 0x0       | PCA0 Module 3 Mode Register         | 483  |

| PCA0CPM4 | 0xDE    | 0x0       | PCA0 Module 4 Mode Register         | 483  |

| PCA0CPM5 | 0xCE    | 0x0       | PCA0 Module 5 Mode Register         | 483  |

| PCA0H    |         | 0x0       | PCA0 Counter High                   | 484  |

| PCA0L    | 0xF9    | 0x0       | PCA0 Counter Low                    | 484  |

| PCA0MD   | 0xD9    | 0x0       | PCA0 Mode                           | 481  |

| PCA0PWM  | 0xDF    | 0x0       | PCA0 PWM Configuration              | 482  |

| PCLKACT  | 0xF5    | 0xF       | Peripheral Clock Enable Active Mode | 260  |

| PCLKEN   | 0xFE    | 0xF       | Peripheral Clock Enables (LP Idle)  | 261  |

| PCON     | 0x87    | All Pages | Power Control                       | 268  |

| PMU0CF   | 0xB5    | 0x0       | PMU0 Configuration 0                | 265  |

| PMU0FL   | 0xB6    | 0x0       | PMU0 flag                           | 266  |

| Interrupt Source              | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                               | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|-------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|------------------|----------------|--------------------|---------------------|

| SmaRTClock Oscillator<br>Fail | 0x008B              | 17                | OSCFAIL<br>(RTC0CN.5) <sup>2</sup>                                         | Ν                | N              | ERTC0F<br>(EIE2.2) | PFRTC0F<br>(EIP2.2) |

| SPI1                          | 0x0093              | 18                | SPIF (SPI1CN.7)<br>WCOL (SPI1CN.6)<br>MODF (SPI1CN.5)<br>RXOVRN (SPI1CN.4) | N                | N              | ESPI1<br>(EIE2.3)  | PSPI1<br>(EIP2.3)   |

| Pulse Counter                 | 0x009B              | 19                | C0ZF (PC0CN.4)<br>C1ZF (PC0CN.6)                                           | Ν                | Ν              | EPC0<br>(EIE2.4)   | PPC0<br>(EIP2.4)    |

| DMA0                          | 0x00A3              | 20                | DMAINT07<br>DMAMINT07                                                      | Ν                | N              | EDMA0<br>(EIE2.5)  | PDMA0<br>(EIP2.5)   |

| Encoder0                      | 0x00AB              | 21                | ENCERR(ENCCN.6)                                                            | Ν                | N              | EENC0<br>(EIE2.6)  | PENC0<br>(EIP2.6)   |

| AES                           | 0x00B3              | 22                | AESDONE<br>(AESBCF.5)                                                      | Ν                | N              | EAES0<br>(EIE2.7)  | PAES0<br>(EIP2.7)   |

Table 17.1. Interrupt Summary

Notes:

1. Indicates a read-only interrupt pending flag. The interrupt enable may be used to prevent software from vectoring to the associated interrupt service routine.

2. Indicates a register located in an indirect memory space.

# 17.5. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described in the following register descriptions. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

# 19.1. Normal Mode

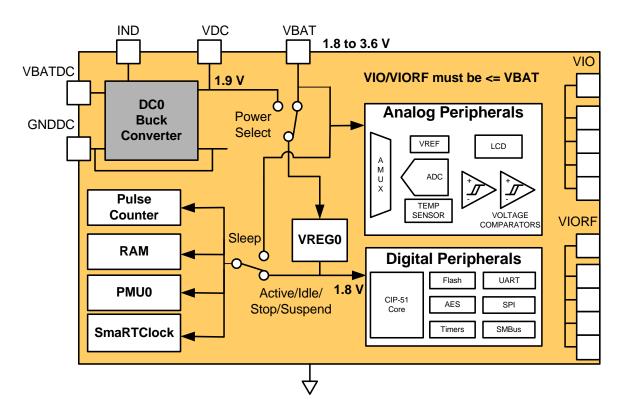

The MCU is fully functional in Normal Mode. Figure 19.1 shows the on-chip power distribution to various peripherals. There are three supply voltages powering various sections of the chip: VBAT, DCOUT, and the 1.8 V internal core supply (output of VREG0). All analog peripherals are directly powered from the VBAT pin. All digital peripherals and the CIP-51 core are powered from the 1.8 V internal core supply (output of VREG0). The Pulse counter, RAM, PMU0, and the SmaRTClock are powered from the internal core supply when the device is in normal mode. The input to VREG0 is controlled by software and depends on the settings of the power select switch. The power select switch may be configured to power VREG0 from VBAT or from the output of the DC0.

Figure 19.1. C8051F96x Power Distribution

# 19.2. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event

# SFR Definition 20.3. DC0MD: DC-DC Converter Mode

| Bit   | 7        | 6 | 5      | 4 | 3      | 2       | 1        | 0     |

|-------|----------|---|--------|---|--------|---------|----------|-------|

| Name  | Reserved |   | ILIMIT |   | FORBYP | AUTOBYP | Reserved | DC0EN |

| Туре  | R/W      |   | R/W    |   | R/W    | R/W     | R/W      | R/W   |

| Reset | 0        | 1 | 0      | 1 | 0      | 0       | 0        | 0     |

SFR Page = 0x2; SFR Address = 0xB3

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                        |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved | Read = 0b; Must write 0b.                                                                                                                                                                                                                                                                                                                       |

| 6:4 | ILIMIT   | Peak Current Limit Threshold.<br>000: Reserved<br>001: Peak Inductor current is limited to 200 mA<br>010: Peak Inductor current is limited to 300 mA<br>011: Peak Inductor current is limited to 400 mA<br>100: Peak Inductor current is limited to 500 mA<br>101: Peak Inductor current is limited to 600 mA<br>110: Reserved<br>111: Reserved |

| 3   | FORBYP   | Enable Forced Bypass Mode.<br>0: Forced bypass mode is disabled.<br>1: Forced bypass mode is enabled.                                                                                                                                                                                                                                           |

| 2   | AUTOBYP  | Enable Automatic Bypass Mode.<br>0: Automatic Bypass mode is disabled.<br>1: Automatic bypass mode is enabled.                                                                                                                                                                                                                                  |

| 1   | Reserved | Read = 1b; Must write 1b.                                                                                                                                                                                                                                                                                                                       |

| 0   | DC0EN    | DC-DC Converter Enable.<br>0: DC-DC converter is disabled.<br>1: DC-DC converter is enabled.                                                                                                                                                                                                                                                    |

# 22.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 4.6 for complete RST pin specifications. The external reset remains functional even when the device is in the low power suspend and sleep modes. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

# 22.4. Missing Clock Detector Reset

The missing clock detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The missing clock detector reset is automatically disabled when the device is in the low power suspend or sleep mode. Upon exit from either low power state, the enabled/disabled state of this reset source is restored to its previous value. The state of the RST pin is unaffected by this reset.

# 22.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The Comparator0 reset source remains functional even when the device is in the low power suspend and sleep states as long as Comparator0 is also enabled as a wake-up source. The state of the RST pin is unaffected by this reset.

# 22.6. PCA Watchdog Timer Reset

The programmable watchdog timer (WDT) function of the programmable counter array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "33.4. Watchdog Timer Mode" on page 477; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The PCA Watchdog Timer reset source is automatically disabled when the device is in the low power suspend or sleep mode. Upon exit from either low power state, the enabled/disabled state of this reset source is restored to its previous value. The state of the RST pin is unaffected by this reset.

# C8051F96x

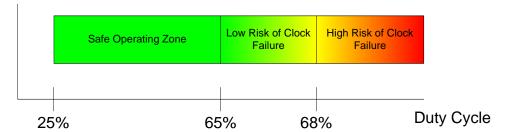

ness. As shown in Figure 24.2, duty cycles less than 65% indicate a robust oscillation. As the duty cycle approaches 68%, oscillation becomes less reliable and the risk of clock failure increases. Increasing the bias current (by disabling AGC) will always improve oscillation robustness and will reduce the output clock's duty cycle. This test should be performed at the worst case system conditions, as results at very low temperatures or high supply voltage will vary from results taken at room temperature or low supply voltage.

Figure 24.2. Interpreting Oscillation Robustness (Duty Cycle) Test Results

As an alternative to performing the oscillation robustness test, Automatic Gain Control may be disabled at the cost of increased power consumption (approximately 200 nA). Disabling Automatic Gain Control will provide the crystal oscillator with higher immunity against external factors which may lead to clock failure. Automatic Gain Control must be disabled if using the SmaRTClock oscillator in self-oscillate mode.

Table 24.3 shows a summary of the oscillator bias settings. The SmaRTClock Bias Doubling feature allows the self-oscillation frequency to be increased (almost doubled) and allows a higher crystal drive strength in crystal mode. High crystal drive strength is recommended when the crystal is exposed to poor environmental conditions such as excessive moisture. SmaRTClock Bias Doubling is enabled by setting BIASX2 (RTC0XCN.5) to 1.

| Mode           | Setting                  | Power<br>Consumption |

|----------------|--------------------------|----------------------|

| Crystal        | Bias Double Off, AGC On  | Lowest               |

|                | Bias Double Off, AGC Off | Low                  |

|                | Bias Double On, AGC On   | High                 |

|                | Bias Double On, AGC Off  | Highest              |

| Self-Oscillate | Bias Double Off          | Low                  |

|                | Bias Double On           | High                 |

Table 24.3. SmaRTClock Bias Settings

# SFR Definition 25.6. PC0DCL: PC0 Debounce Configuration Low

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-------------|---|---|---|---|---|---|--|

| Name  |   | PC0DCL[7:0] |   |   |   |   |   |   |  |

| Туре  |   | R/W         |   |   |   |   |   |   |  |

| Reset | 0 | 0           | 0 | 0 | 0 | 1 | 0 | 0 |  |

SFR Address = 0xF9; SFR Page = 0x2

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | PC0DCL[7:0] | Pulse Counter Debounce Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |             | Number of cumulative good samples seen by the integrator before recogniz-<br>ing the input as low. Setting PC0DCL to 0x00 will disable integrators on both<br>PC0 and PC1. The actual value used is PC0DCL plus one. Sampling a low<br>decrements while sampling a high increments the count. Switch bounce<br>produces a random looking signal. The worst case would be to bounce high<br>at each sample point and not start decrementing the integrator until the<br>switch bounce settled. Therefore, minimum pulse width should account for<br>twice the debounce time. For example, using a sample rate of 1 ms and a<br>PC0DCL value of 0x09 will look for 10 cumulative lows before recognizing<br>the input as low (1 ms x 10 = 10 ms). The minimum pulse width should be<br>20 ms or greater for this example. If PC0DCL has a value of 0x03 and the<br>sample rate is 500 µs, the integrator would need to see 4 cumulative lows<br>before recognizing the low (500 µs x 4 = 2 ms). The minimum pulse width<br>should be 4 ms for this example. |

# SFR Definition 25.10. PC0CTR1H: PC0 Counter 1 High (MSB)

| Bit   | 7            | 7 6 5 4 3 2 1 0  |                         |  |  |  |   |  |  |

|-------|--------------|------------------|-------------------------|--|--|--|---|--|--|

| Nam   | e            | PC0CTR1H[23:16]  |                         |  |  |  |   |  |  |

| Туре  | •            | R                |                         |  |  |  |   |  |  |

| Rese  | <b>t</b> 0   | 0 0 0 0 0 0 0 0  |                         |  |  |  | 0 |  |  |

| SFR A | ddress = 0xD | F; SFR Pag       | e = 0x2                 |  |  |  |   |  |  |

| Bit   | Name         | •                | Function                |  |  |  |   |  |  |

| 7:0   | PC0CTR1H     | [23:16] <b>P</b> | PC0 Counter 1 High Byte |  |  |  |   |  |  |

# SFR Definition 25.11. PC0CTR1M: PC0 Counter 1 Middle

Bits 23:16 of Counter 1.

| Bit   | 7             | 6              | 5                                                    | 4 | 3     | 2   | 1 | 0        |  |

|-------|---------------|----------------|------------------------------------------------------|---|-------|-----|---|----------|--|

| Nam   | e             | PC0CTR1M[15:8] |                                                      |   |       |     |   |          |  |

| Туре  | •             | R              |                                                      |   |       |     |   |          |  |

| Rese  | et 0          | 0              | 0                                                    | 0 | 0     | 0   | 0 | 0        |  |

| SFR A | Address = 0xD | E; SFR Page    | e = 0x2                                              |   |       |     |   | <u> </u> |  |

| Bit   | Name          | 9              |                                                      |   | Funct | ion |   |          |  |

| 7:0   | PC0CTR1N      |                | PC0 Counter 1 Middle Byte<br>Bits 15:8 of Counter 1. |   |       |     |   |          |  |

# SFR Definition 25.12. PC0CTR1L: PC0 Counter 1 Low (LSB)

| Bit   | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------------|---|---|---|---|---|---|---|

| Name  | PC0CTR1L[7:0] |   |   |   |   |   |   |   |

| Туре  | R             |   |   |   |   |   |   |   |

| Reset | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | Name          | Function               |

|-----|---------------|------------------------|

| 7:0 | PC0CTR1L[7:0] | PC0 Counter 1 Low Byte |

|     |               | Bits 7:0 of Counter 1. |

Note: PC0CTR1L must be read before PC0CTR1M and PC0CTR1H to latch the count for reading.

# 26.3. LCD Contrast Adjustment

The LCD Bias voltages which determine the LCD contrast are generated using the VBAT supply voltage or the on-chip charge pump. There are four contrast control modes to accomodate a wide variety of applications and supply voltages. The target contrast voltage is programmable in 60 mV steps from 1.9 to 3.72 V. The LCD contrast voltage is controlled by the LCD0CNTRST register and the contrast control mode is selected by setting the appropriate bits in the LCD0MSCN, LCD0MSCF, LCD0PWR, and LCD0VBMCN registers.

**Note:** An external 10 µF decoupling capacitor is required on the VLCD pin to create a charge reservoir at the output of the charge pump.

| Mode         | LCD0MSCN.2                                            | LCD0MSCF.0 | LCD0PWR.3 | LCD0VBMCN.7 |  |  |  |  |  |

|--------------|-------------------------------------------------------|------------|-----------|-------------|--|--|--|--|--|

| 1            | 0                                                     | 1          | 0         | 0           |  |  |  |  |  |

| 2            | 0                                                     | 1          | 1         | 1           |  |  |  |  |  |

| 3            | 1*                                                    | 0          | 1         | 1           |  |  |  |  |  |

| 4            | 1*                                                    | 0          | 0         | 1           |  |  |  |  |  |

| * May be set | * May be set to 0 to support increased load currents. |            |           |             |  |  |  |  |  |

#### Table 26.1. Bit Configurations to select Contrast Control Modes

#### 26.3.1. Contrast Control Mode 1 (Bypass Mode)

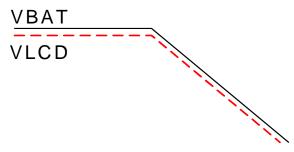

In Contrast Control Mode 1, the contrast control circuitry is disabled and the VLCD voltage follows the VBAT supply voltage, as shown in Figure 26.3. This mode is useful in systems where the VBAT voltage always remains constant and will provide the lowest LCD power consumption. Bypass Mode is selected using the following procedure:

- 1. Clear Bit 2 of the LCD0MSCN register to 0b (LCD0MSCN &= ~0x04)

- 2. Set Bit 0 of the LCD0MSCF register to 1b (LCD0MSCF |= 0x01)

- 3. Clear Bit 3 of the LCD0PWR register to 0b (LCD0PWR &= ~0x08)

- 4. Clear Bit 7 of the LCD0VBMCN register to 0b (LCD0VBMCN &= ~0x80)

Figure 26.3. Contrast Control Mode 1

# SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate

| Bit   | 7   | 6   | 5   | 4   | 3   | 2    | 1      | 0 |

|-------|-----|-----|-----|-----|-----|------|--------|---|

| Name  |     |     |     |     |     | TOGI | R[3:0] |   |

| Туре  | R/W | R/W | R/W | R/W | R/W |      |        |   |

| Reset | 0   | 0   | 0   | 0   | 0   | 0    | 0      | 0 |

#### SFR Page = 0x2; SFR Address = 0x9F

| Name      | Function                                                                                                     |

|-----------|--------------------------------------------------------------------------------------------------------------|

| Unused    | Read = 0000. Write = Don't Care.                                                                             |

| TOGR[3:0] | LCD Toggle Rate Divider.                                                                                     |

|           | Sets the LCD Toggle Rate according to the following equation:                                                |

|           |                                                                                                              |

|           | LCD Toggle Rate = $\frac{\text{Refresh Rate} \times \text{mux}_{\text{mode}} \times 2}{\text{Tracels Rate}}$ |

|           | Toggle Rate Divider                                                                                          |

|           | 0000: Reserved.                                                                                              |

|           | 0001: Reserved.                                                                                              |

|           | 0010: Toggle Rate Divider is set to divide by 2.                                                             |

|           | 0011: Toggle Rate Divider is set to divide by 4.                                                             |

|           | 0100: Toggle Rate Divider is set to divide by 8.                                                             |

|           | 0101: Toggle Rate Divider is set to divide by 16.                                                            |

|           | 0110: Toggle Rate Divider is set to divide by 32.                                                            |

|           | 0111: Toggle Rate Divider is set to divide by 64.                                                            |

|           | 1000: Toggle Rate Divider is set to divide by 128.                                                           |

|           | 1001: Toggle Rate Divider is set to divide by 256.                                                           |

|           | 1010: Toggle Rate Divider is set to divide by 512.                                                           |

|           | 1011: Toggle Rate Divider is set to divide by 1024.                                                          |

|           | 1100: Toggle Rate Divider is set to divide by 2048.                                                          |

|           | 1101: Toggle Rate Divider is set to divide by 4096.                                                          |

|           | All other values reserved.                                                                                   |

|           | Unused                                                                                                       |

# 27. Port Input/Output

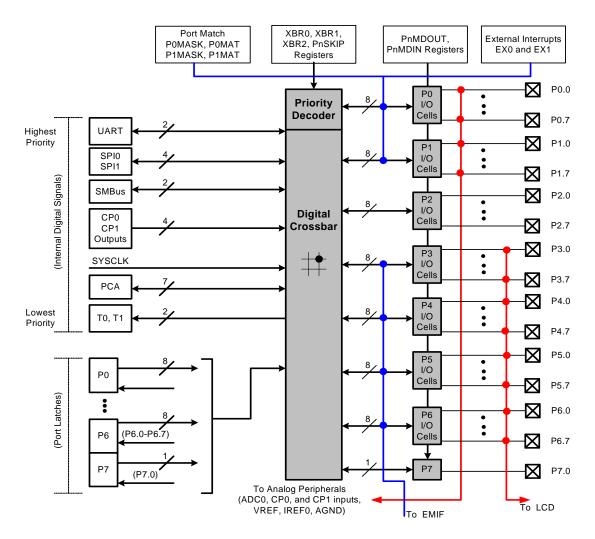

Digital and analog resources are available through 57 I/O pins (C8051F960/2/4/6/8) or 34 I/O pins (C8051F961/3/5/7/9). Port pins are organized as eight byte-wide ports. Port pins can be defined as digital or analog I/O. Digital I/O pins can be assigned to one of the internal digital resources or used as general purpose I/O (GPIO). Analog I/O pins are used by the internal analog resources. P7.0 can be used as GPIO and is shared with the C2 Interface Data signal (C2D). See Section "34. C2 Interface" on page 486 for more details.

The designer has complete control over which digital and analog functions are assigned to individual port pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. See Section 27.3 for more information on the Crossbar.

For Port I/Os configured as push-pull outputs, current is sourced from the VIO or VIORF supply pin. On 40pin devices, the VIO and VIORF supply pins are internally tied to VBAT. See Section 27.1 for more information on Port I/O operating modes and the electrical specifications chapter for detailed electrical specifications.

Figure 27.1. Port I/O Functional Block Diagram

# 27.3. Priority Crossbar Decoder

The Priority Crossbar Decoder assigns a Port I/O pin to each software selected digital function using the fixed peripheral priority order shown in Figure 27.3. The registers XBR0, XBR1, and XBR2 defined in SFR Definition 27.1, SFR Definition 27.2, and SFR Definition 27.3 are used to select digital functions in the Crossbar. The Port pins available for assignment by the Crossbar include all Port pins (P0.0–P2.6) which have their corresponding bit in PnSKIP set to 0.

From Figure 27.3, the highest priority peripheral is UART0. If UART0 is selected in the Crossbar (using the XBRn registers), then P0.4 and P0.5 will be assigned to UART0. The next highest priority peripheral is SPI1. If SPI1 is selected in the Crossbar, then P2.0–P2.2 will be assigned to SPI1. P2.3 will be assigned if SPI1 is configured for 4-wire mode. The user should ensure that the pins to be assigned by the Crossbar have their PnSKIP bits set to 0.

For all remaining digital functions selected in the Crossbar, starting at the top of Figure 27.3 going down, the least-significant unskipped, unassigned Port pin(s) are assigned to that function. If a Port pin is already assigned (e.g., UART0 or SPI1 pins), or if its PnSKIP bit is set to 1, then the Crossbar will skip over the pin and find next available unskipped, unassigned Port pin. All Port pins used for analog functions, GPIO, or dedicated digital functions such as the EMIF should have their PnSKIP bit set to 1.

Figure 27.3 shows the Crossbar Decoder priority with no Port pins skipped (P0SKIP, P1SKIP, P2SKIP = 0x00); Figure 27.4 shows the Crossbar Decoder priority with the External Oscillator pins (XTAL1 and XTAL2) skipped (P0SKIP = 0x0C).

Important Notes:

- The Crossbar must be enabled (XBARE = 1) before any Port pin is used as a digital output. Port output drivers are disabled while the Crossbar is disabled.

- When SMBus is selected in the Crossbar, the pins associated with SDA and SCL will automatically be forced into open-drain output mode regardless of the PnMDOUT setting.

- SPI0 can be operated in either 3-wire or 4-wire modes, depending on the state of the NSSMD1-NSSMD0 bits in register SPI0CN. The NSS signal is only routed to a Port pin when 4-wire mode is selected. When SPI0 is selected in the Crossbar, the SPI0 mode (3-wire or 4-wire) will affect the pinout of all digital functions lower in priority than SPI0.

- For given XBRn, PnSKIP, and SPInCN register settings, one can determine the I/O pin-out of the device using Figure 27.3 and Figure 27.4.

# SFR Definition 27.12. P0DRV: Port0 Drive Strength

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | P0DRV[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Page = 0xF; SFR Address = 0xA4

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0DRV[7:0] | Drive Strength Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P0.n Output has low output drive strength.<br>1: Corresponding P0.n Output has high output drive strength. |

# SFR Definition 27.13. P1: Port1

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P1[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = All Pages; SFR Address = 0x90; Bit-Addressable

| Bit | Name    | Description                                                                                                                                   | Write                                                                         | Read |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| 7:0 | P1[7:0] | <b>Port 1 Data.</b><br>Sets the Port latch logic<br>value or reads the Port pin<br>logic state in Port cells con-<br>figured for digital I/O. | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW. |

# SFR Definition 27.34. P5DRV: Port5 Drive Strength

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | P5DRV[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0xA3

| Bit | Name       | Function                                                                                                                                                                                               |  |  |  |  |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0 | P5DRV[7:0] | Drive Strength Configuration Bits for P5.7–P5.0 (respectively).                                                                                                                                        |  |  |  |  |  |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P5.n Output has low output drive strength.<br>1: Corresponding P5.n Output has high output drive strength. |  |  |  |  |  |

# SFR Definition 27.35. P6: Port6

| Bit   | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| Name  | P6[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W     |   |   |   |   |   |   |   |

| Reset | 1       | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

SFR Page = 0xF; SFR Address = 0xDB

| Bit | Name | Description               | Write                                                                         | Read |

|-----|------|---------------------------|-------------------------------------------------------------------------------|------|

| 7:0 |      | Sets the Port latch logic | 0: Set output latch to logic<br>LOW.<br>1: Set output latch to logic<br>HIGH. | LOW. |

# 29.1. Enhanced Baud Rate Generation

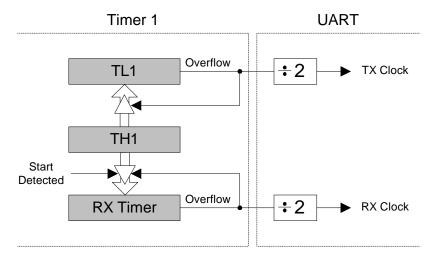

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 29.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 29.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "32.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 447). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, the external oscillator clock / 8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation -A and Equation -B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "32.1. Timer 0 and Timer 1" on page 446. A quick reference for typical baud rates and system clock frequencies is given in Table 29.1 through Table 29.2. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.