# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                          |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | DMA, POR, PWM, WDT                                                |

| Number of I/O              | 34                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                  |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 8.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                       |

| Data Converters            | A/D 16x10b/12b                                                    |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 40-VFQFN Exposed Pad                                              |

| Supplier Device Package    | 40-QFN (6x6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f963-a-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 5.10. External Voltage Reference                     |     |

|----|------------------------------------------------------|-----|

|    | 5.11. Internal Voltage Reference                     |     |

|    | 5.12. Analog Ground Reference                        | 101 |

|    | 5.13. Temperature Sensor Enable                      |     |

|    | 5.14. Voltage Reference Electrical Specifications    |     |

| 6. | Programmable Current Reference (IREF0)               |     |

|    | 6.1. PWM Enhanced Mode                               | 103 |

|    | 6.2. IREF0 Specifications                            |     |

| 7. | Comparators                                          |     |

|    | 7.1. Comparator Inputs                               | 105 |

|    | 7.2. Comparator Outputs                              |     |

|    | 7.3. Comparator Response Time                        |     |

|    | 7.4. Comparator Hysterisis                           | 107 |

|    | 7.5. Comparator Register Descriptions                |     |

|    | 7.6. Comparator0 and Comparator1 Analog Multiplexers | 112 |

| 8. | CIP-51 Microcontroller                               | 115 |

|    | 8.1. Instruction Set                                 | 116 |

|    | 8.1.1. Instruction and CPU Timing                    | 116 |

|    | 8.2. CIP-51 Register Descriptions                    | 121 |

| 9. | Memory Organization                                  |     |

|    | 9.1. Program Memory                                  | 124 |

|    | 9.1.1. MOVX Instruction and Program Memory           | 127 |

|    | 9.2. Data Memory                                     |     |

|    | 9.2.1. Internal RAM                                  | 127 |

|    | 9.2.2. External RAM                                  | 128 |

| 10 | . External Data Memory Interface and On-Chip XRAM    | 129 |

|    | 10.1. Accessing XRAM                                 | 129 |

|    | 10.1.1. 16-Bit MOVX Example                          |     |

|    | 10.1.2. 8-Bit MOVX Example                           | 129 |

|    | 10.2. Configuring the External Memory Interface      |     |

|    | 10.3. Port Configuration                             |     |

|    | 10.4. Multiplexed and Non-multiplexed Selection      | 134 |

|    | 10.4.1. Multiplexed Configuration                    | 134 |

|    | 10.4.2. Non-multiplexed Configuration                |     |

|    | 10.5. Memory Mode Selection                          |     |

|    | 10.5.1. Internal XRAM Only                           | 136 |

|    | 10.5.2. Split Mode without Bank Select               |     |

|    | 10.5.3. Split Mode with Bank Select                  |     |

|    | 10.5.4. External Only                                |     |

|    | 10.6. Timing                                         |     |

|    | 10.6.1. Non-Multiplexed Mode                         |     |

|    | 10.6.2. Multiplexed Mode                             |     |

| 11 | . Direct Memory Access (DMA0)                        |     |

|    | 11.1. DMA0 Architecture                              |     |

|    | 11.2. DMA0 Arbitration                               |     |

|    |                                                      |     |

### Table 4.15. IREF0 Electrical Characteristics

$V_{BAT}$  = 1.8 to 3.8 V, –40 to +85 °C, unless otherwise specified.

| Parameter                                                                                           | Conditions                                                                                                                                                                                                                                                | Min                  | Тур                                  | Max                                                 | Units                      |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------|-----------------------------------------------------|----------------------------|

| Static Performance                                                                                  |                                                                                                                                                                                                                                                           | L                    | •                                    |                                                     |                            |

| Resolution                                                                                          |                                                                                                                                                                                                                                                           |                      | 6                                    |                                                     | bits                       |

| Output Compliance Range                                                                             | Low Power Mode, Source<br>High Current Mode, Source<br>Low Power Mode, Sink<br>High Current Mode, Sink                                                                                                                                                    | 0<br>0<br>0.3<br>0.8 |                                      | $V_{BAT} - 0.4$ $V_{BAT} - 0.8$ $V_{BAT}$ $V_{BAT}$ | V                          |

| Integral Nonlinearity                                                                               |                                                                                                                                                                                                                                                           | _                    | <±0.2                                | ±1.0                                                | LSB                        |

| Differential Nonlinearity                                                                           |                                                                                                                                                                                                                                                           |                      | <±0.2                                | ±1.0                                                | LSB                        |

| Offset Error                                                                                        |                                                                                                                                                                                                                                                           | _                    | <±0.1                                | ±0.5                                                | LSB                        |

|                                                                                                     | Low Power Mode, Source                                                                                                                                                                                                                                    |                      |                                      | ±5                                                  | %                          |

| Full Scale Error                                                                                    | High Current Mode, Source                                                                                                                                                                                                                                 |                      |                                      | ±6                                                  | %                          |

|                                                                                                     | Low Power Mode, Sink                                                                                                                                                                                                                                      | _                    |                                      | ±8                                                  | %                          |

|                                                                                                     | High Current Mode, Sink                                                                                                                                                                                                                                   | _                    |                                      | ±8                                                  | %                          |

| Absolute Current Error                                                                              | Low Power Mode<br>Sourcing 20 µA                                                                                                                                                                                                                          | _                    | <±1                                  | ±3                                                  | %                          |

| Dynamic Performance                                                                                 |                                                                                                                                                                                                                                                           |                      |                                      |                                                     |                            |

| Output Settling Time to 1/2 LSB                                                                     |                                                                                                                                                                                                                                                           |                      | 300                                  |                                                     | ns                         |

| Startup Time                                                                                        |                                                                                                                                                                                                                                                           |                      | 1                                    | —                                                   | μs                         |

| Power Consumption                                                                                   |                                                                                                                                                                                                                                                           |                      | 1                                    |                                                     |                            |

| Net Power Supply Current<br>(V <sub>BAT</sub> supplied to IREF0 minus<br>any output source current) | Low Power Mode, Source<br>IREF0DAT = 000001<br>IREF0DAT = 111111<br>High Current Mode, Source<br>IREF0DAT = 000001<br>IREF0DAT = 111111<br>Low Power Mode, Sink<br>IREF0DAT = 000001<br>IREF0DAT = 111111<br>High Current Mode, Sink<br>IREF0DAT = 000001 |                      | 10<br>10<br>10<br>10<br>1<br>1<br>11 |                                                     | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |

|                                                                                                     | IREF0DAT = 111111                                                                                                                                                                                                                                         |                      | 81                                   | —                                                   | μΑ                         |

| Note: Refer to "6.1. PWM Enhance                                                                    | d Mode" on page 103 for informatio                                                                                                                                                                                                                        | n on how t           | o improve                            | IREF0 resoluti                                      | on.                        |

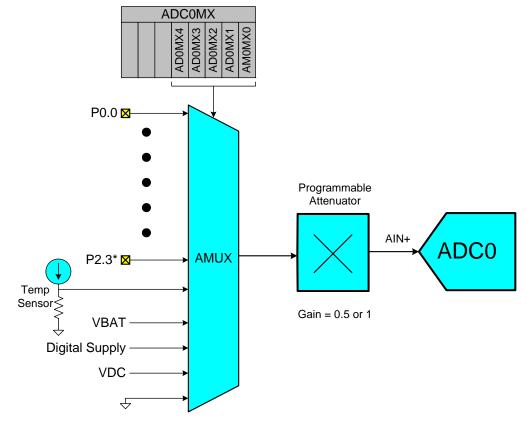

### 5.7. ADC0 Analog Multiplexer

ADC0 on C8051F96x has an analog multiplexer, referred to as AMUX0.

AMUX0 selects the positive inputs to the single-ended ADC0. Any of the following may be selected as the positive input: Port I/O pins, the on-chip temperature sensor, the VBAT Power Supply, Regulated Digital Supply Voltage (Output of VREG0), VDC Supply, or the positive input may be connected to GND. The ADC0 input channels are selected in the ADC0MX register described in SFR Definition 5.12.

\*P1.0 – P1.3 are not available as analog inputs Figure 5.7. ADC0 Multiplexer Block Diagram

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to 0 the corresponding bit in register PnMDIN and disable the digital driver (PnMDOUT = 0 and Port Latch = 1). To force the Crossbar to skip a Port pin, set to 1 the corresponding bit in register PnSKIP. See Section "27. Port Input/Output" on page 351 for more Port I/O configuration details.

## SFR Definition 5.13. TOFFH: Temperature Sensor Offset High Byte

| Bit   | 7         | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|-----------|--------|--------|--------|--------|--------|--------|--------|

| Name  | TOFF[9:2] |        |        |        |        |        |        |        |

| Туре  | R         | R      | R      | R      | R      | R      | R      | R      |

| Reset | Varies    | Varies | Varies | Varies | Varies | Varies | Varies | Varies |

SFR Page = 0xF; SFR Address = 0x86

| Bit | Name | Function                                                                   |

|-----|------|----------------------------------------------------------------------------|

| 7:0 |      | Temperature Sensor Offset High Bits.                                       |

|     |      | Most Significant Bits of the 10-bit temperature sensor offset measurement. |

## SFR Definition 5.14. TOFFL: Temperature Sensor Offset Low Byte

| Bit   | 7         | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|--------|---|---|---|---|---|---|

| Name  | TOFF[1:0] |        |   |   |   |   |   |   |

| Туре  | R         | R      |   |   |   |   |   |   |

| Reset | Varies    | Varies | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0x85

| Bit | Name      | Function                                                                                                           |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------|

| 7:6 | TOFF[1:0] | Temperature Sensor Offset Low Bits.<br>Least Significant Bits of the 10-bit temperature sensor offset measurement. |

| 5:0 | Unused    | Read = 0; Write = Don't Care.                                                                                      |

## SFR Definition 7.5. CPT0MX: Comparator0 Input Channel Select

| Bit   | 7   | 6    | 5      | 4   | 3          | 2   | 1   | 0   |

|-------|-----|------|--------|-----|------------|-----|-----|-----|

| Name  |     | CMX0 | N[3:0] |     | CMX0P[3:0] |     |     |     |

| Туре  | R/W | R/W  | R/W    | R/W | R/W        | R/W | R/W | R/W |

| Reset | 1   | 1    | 1      | 1   | 1          | 1   | 1   | 1   |

SFR Page = 0x0; SFR Address = 0x9F

| Bit | Name  |       | Fui                                                                  | nction     |                        |

|-----|-------|-------|----------------------------------------------------------------------|------------|------------------------|

| 7:4 | CMX0N | -     | <b>O Negative Input Selection.</b><br>negative input channel for Cor |            |                        |

|     |       | 0000: | P0.1                                                                 | 1000:      | P2.1                   |

|     |       | 0001: | P0.3                                                                 | 1001:      | P2.3                   |

|     |       | 0010: | P0.5                                                                 | 1010:      | Reserved               |

|     |       | 0011: | Reserved                                                             | 1011:      | Reserved               |

|     |       | 0100: | Reserved                                                             | 1100:      | Compare                |

|     |       | 0101: | Reserved                                                             | 1101:      | VBAT divided by 2      |

|     |       | 0110: | P1.5                                                                 | 1110:      | Digital Supply Voltage |

|     |       | 0111: | P1.7                                                                 | 1111:      | Ground                 |

| 3:0 | CMX0P |       | <b>O Positive Input Selection.</b>                                   | nparator0. |                        |

|     |       | 0000: | P0.0                                                                 | 1000:      | P2.0                   |

|     |       | 0001: | P0.2                                                                 | 1001:      | P2.2                   |

|     |       | 0010: | P0.4                                                                 | 1010:      | Reserved               |

|     |       | 0011: | P0.6                                                                 | 1011:      | Reserved               |

|     |       | 0100: | Reserved                                                             | 1100:      | Compare                |

|     |       | 0101: | Reserved                                                             | 1101:      | VBAT divided by 2      |

|     |       | 0110: | P1.4                                                                 | 1110:      | VBAT Supply Voltage    |

|     |       | 0111: | P1.6                                                                 | 1111:      | VBAT Supply Voltage    |

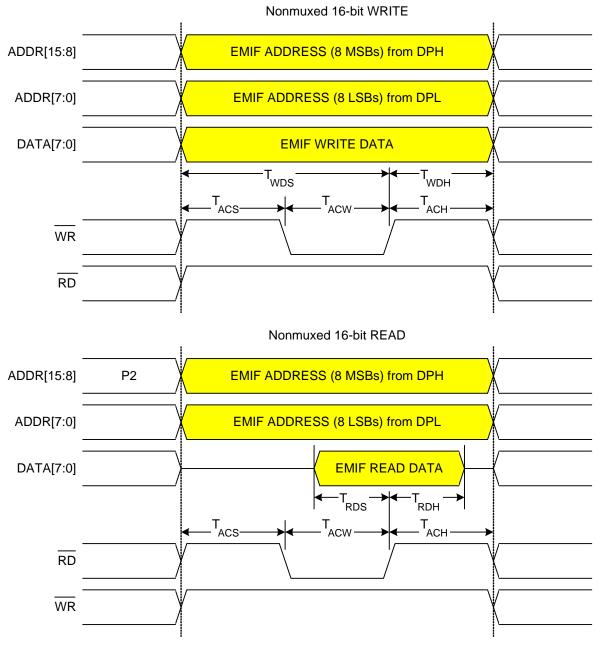

#### 10.6.1. Non-Multiplexed Mode 10.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111

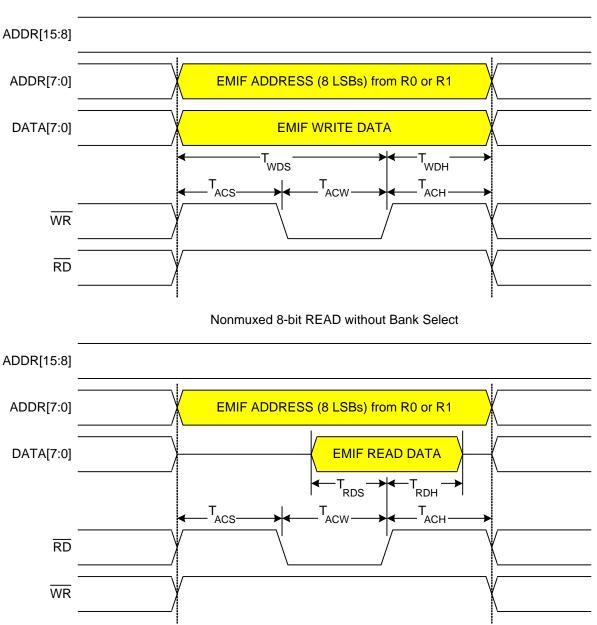

#### 10.6.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111

Nonmuxed 8-bit WRITE without Bank Select

Figure 10.5. Non-multiplexed 8-bit MOVX without Bank Select Timing

#### 14.5.2. AES Block Cipher Decryption using SFRs

- First Configure AES Module for AES Block Cipher

- Reset AES module by writing 0x00 to AES0BCFG.

- Configure the AES Module data flow for AES Block Cipher by writing 0x00 to the AES0DCFG sfr.

- Write key size to bits 1 and 0 of the AES0BCFG.

- Configure the AES core for decryption by setting bit 2 of AES0BCFG.

- Enable the AES core by setting bit 3 of AES0BCFG.

- Repeat alternating write sequence 16 times

- Write ciphertext byte to AES0BIN.

- Write decryption key byte to AES0KIN.

- Write remaining decryption key bytes to AES0KIN for 192-bit and 256-bit decryption only.

- Wait on AES done interrupt or poll bit 5 of AES0BCFG.

- Read 16 plaintext bytes from the AES0YOUT sfr.

If decrypting multiple blocks, this process may be repeated. It is not necessary reconfigure the AES module for each block.

## SFR Definition 14.2. AES0DCFG: AES Data Configuration

| Bit   | 7 | 6 | 5 | 4 | 3 | 2     | 1       | 0     |

|-------|---|---|---|---|---|-------|---------|-------|

| Name  |   |   |   |   |   | OUTSI | EL[1:0] | XORIN |

| Туре  | R | R | R | R | R | R/W   |         | R/W   |

| Reset | 0 | 0 | 0 | 0 | 0 | 0     | 0       | 0     |

SFR Address = 0xEA; SFR page = 0x2; Not bit-Addressable

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:1 | OUTSEL[1:0] | DATA Select.                                                                                                                                                                                                                                                                                                       |

|     |             | These bits select the output data source for the AES0YOUT sfr.                                                                                                                                                                                                                                                     |

|     |             | 00: Direct AES Data                                                                                                                                                                                                                                                                                                |

|     |             | 01: AES Data XOR with AES0XIN                                                                                                                                                                                                                                                                                      |

|     |             | 10: Inverse Key                                                                                                                                                                                                                                                                                                    |

|     |             | 11: reserved                                                                                                                                                                                                                                                                                                       |

| 0   | XORIN       | XOR Input Enable.                                                                                                                                                                                                                                                                                                  |

|     |             | Setting this bit with enable the XOR data path on the AES input. If enabled,<br>AES0BIN will be XORed with the AES0XIN and the results will feed into the AES<br>data input. Clearing this bit to 0 will disable the XOR gate on the input. The con-<br>tents of AES0BIN will go directly into the AES data input. |

### Table 16.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | SFR Page       | Description                 | Page |

|----------|---------|----------------|-----------------------------|------|

| TL0      | 0x8A    | 0x0            | Timer/Counter 0 Low         | 452  |

| TL1      | 0x8B    | 0x0            | Timer/Counter 1 Low         | 452  |

| TMOD     | 0x89    | 0x0            | Timer/Counter Mode          | 451  |

| TMR2CN   | 0xC8    | All Pages      | Timer/Counter 2 Control     | 457  |

| TMR2H    | 0xCD    | 0x0            | Timer/Counter 2 High        | 459  |

| TMR2L    | 0xCC    | 0x0            | Timer/Counter 2 Low         | 459  |

| TMR2RLH  | 0xCB    | 0x0            | Timer/Counter 2 Reload High | 458  |

| TMR2RLL  | 0xCA    | 0x0            | Timer/Counter 2 Reload Low  | 458  |

| TMR3CN   | 0x91    | 0x0            | Timer/Counter 3 Control     | 463  |

| TMR3H    | 0x95    | 0x0            | Timer/Counter 3 High        | 465  |

| TMR3L    | 0x94    | 0x0            | Timer/Counter 3 Low         | 465  |

| TMR3RLH  | 0x93    | 0x0            | Timer/Counter 3 Reload High | 464  |

| TMR3RLL  | 0x92    | 0x0            | Timer/Counter 3 Reload Low  | 464  |

| TOFFH    | 0xBB    | 0xF            | Temperature Offset High     | 99   |

| TOFFL    | 0xBD    | 0xF            | Temperature Offset Low      | 99   |

| VDM0CN   | 0xFF    | All Pages      | VDD Monitor Control         | 282  |

| XBR0     | 0xE1    | 0x0 and<br>0xF | Port I/O Crossbar Control 0 | 358  |

| XBR1     | 0xE2    | 0x0 and<br>0xF | Port I/O Crossbar Control 1 | 359  |

| XBR2     | 0xE3    | 0x0 and<br>0xF | Port I/O Crossbar Control 2 | 360  |

#### 22.2. Power-Fail Reset

C8051F96x devices have two Active Mode Supply Monitors that can hold the system in reset if the supply voltage drops below  $V_{RST}$ . The first of the two identical supply monitors is connected to the output of the supply select switch (which chooses the VBAT or VDC pin as the source of the digital supply voltage) and is enabled and selected as a reset source after each power-on or power-fail reset. This supply monitor will be referred to as the digital supply monitor. The second supply monitor is connected directly to the VBAT pin and is disabled after each power-on or power-fail reset. This supply monitor will be referred to as the analog supply monitor. The analog supply monitor should be enabled any time the supply select switch is set to the VDC pin to ensure that the VBAT supply does not drop below  $V_{RST}$ .

When enabled and selected as a reset source, any power down transition or power irregularity that causes the monitored supply voltage to drop below  $V_{RST}$  will cause the RST pin to be driven low and the CIP-51 will be held in a reset state (see Figure 22.2). When the supply voltage returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state.

After a power-fail reset, the PORSF flag reads 1, the contents of RAM are invalid, and the digital supply monitor is enabled and selected as a reset source. The enable state of either supply monitor and its selection as a reset source is only altered by power-on and power-fail resets. For example, if the supply monitor is de-selected as a reset source and disabled by software, then a software reset is performed, the supply monitor will remain disabled and de-selected after the reset.

In battery-operated systems, the contents of RAM can be preserved near the end of the battery's usable life if the device is placed in Sleep Mode prior to a power-fail reset occurring. When the device is in Sleep Mode, the power-fail reset is automatically disabled, both active mode supply monitors are turned off, and the contents of RAM are preserved as long as the supply does not fall below  $V_{POR}$ . A large capacitor can be used to hold the power supply voltage above  $V_{POR}$  while the user is replacing the battery. Upon waking from Sleep mode, the enable and reset source select state of the  $V_{DD}$  supply monitor are restored to the value last set by the user.

To allow software early notification that a power failure is about to occur, the VDDOK bit is cleared when the supply falls below the  $V_{WARN}$  threshold. The VDDOK bit can be configured to generate an interrupt. Each of the active mode supply montiors have their independent VDDOK and  $V_{WARN}$  flags. See Section "17. Interrupt Handler" on page 232 for more details.

**Important Note:** To protect the integrity of Flash contents, **the active mode supply monitor(s) must be enabled and selected as a reset source if software contains routines which erase or write Flash memory.** If the digital supply monitor is not enabled, any erase or write performed on Flash memory will cause a Flash Error device reset.

## SFR Definition 24.3. RTC0DAT: SmaRTClock Data

| Bit     | 7                                                                                          | 6                                                                                                                | 5    | 4     | 3        | 2 | 1 | 0 |

|---------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|-------|----------|---|---|---|

| Name    |                                                                                            |                                                                                                                  |      | RTC0D | AT[7:0]  |   |   |   |

| Туре    |                                                                                            |                                                                                                                  |      | R/    | W        |   |   |   |

| Reset   | 0                                                                                          | 0                                                                                                                | 0    | 0     | 0        | 0 | 0 | 0 |

| SFR Pa  | ge= 0x0; SF                                                                                | R Address =                                                                                                      | 0xAD |       |          |   |   |   |

| Bit     | Name                                                                                       |                                                                                                                  |      |       | Function |   |   |   |

| 7:0     | RTC0DAT                                                                                    | SmaRTClock Data Bits.<br>Holds data transferred to/from the internal SmaRTClock register selected by<br>RTC0ADR. |      |       |          |   |   |   |

| Note: F | Note: Read-modify-write instructions (orl, anl, etc.) should not be used on this register. |                                                                                                                  |      |       |          |   |   |   |

#### 24.2.6. Missing SmaRTClock Detector

The missing SmaRTClock detector is a one-shot circuit enabled by setting MCLKEN (RTC0CN.6) to 1. When the SmaRTClock Missing Clock Detector is enabled, OSCFAIL (RTC0CN.5) is set by hardware if SmaRTClock oscillator remains high or low for more than 100  $\mu$ s.

A SmaRTClock Missing Clock detector timeout can trigger an interrupt, wake the device from a low power mode, or reset the device. See Section "17. Interrupt Handler" on page 232, Section "19. Power Management" on page 257, and Section "22. Reset Sources" on page 278 for more information.

**Note:** The SmaRTClock Missing Clock Detector should be disabled when making changes to the oscillator settings in RTC0XCN.

#### 24.2.7. SmaRTClock Oscillator Crystal Valid Detector

The SmaRTClock oscillator crystal valid detector is an oscillation amplitude detector circuit used during crystal startup to determine when oscillation has started and is nearly stable. The output of this detector can be read from the CLKVLD bit (RTX0XCN.4).

#### Notes:

- 1. The CLKVLD bit has a blanking interval of 2 ms. During the first 2 ms after turning on the crystal oscillator, the output of CLKVLD is not valid.

- This SmaRTClock crystal valid detector (CLKVLD) is not intended for detecting an oscillator failure. The missing SmaRTClock detector (CLKFAIL) should be used for this purpose.

- **3.** The CLKVLD bit output is driven low when BIASX2 is disabled.

#### 24.3. SmaRTClock Timer and Alarm Function

The SmaRTClock timer is a 32-bit counter that, when running (RTC0TR = 1), is incremented every SmaRTClock oscillator cycle. The timer has an alarm function that can be set to generate an interrupt, wake the device from a low power mode, or reset the device at a specific time. See Section "17. Interrupt Handler" on page 232, Section "19. Power Management" on page 257, and Section "22. Reset Sources" on page 278 for more information.

The SmaRTClock timer includes an Auto Reset feature, which automatically resets the timer to zero one SmaRTClock cycle after the alarm 0 signal is deasserted. When using Auto Reset, the Alarm match value should always be set to 2 counts less than the desired match value. When using the LFO in combination with Auto Reset, the right-justified Alarm match value should be set to 4 counts less than the desired match value. Auto Reset can be enabled by writing a 1 to ALRM (RTCOCN.2).

#### 24.3.1. Setting and Reading the SmaRTClock Timer Value

The 32-bit SmaRTClock timer can be set or read using the six CAPTUREn internal registers. Note that the timer does not need to be stopped before reading or setting its value. The following steps can be used to set the timer value:

- 1. Write the desired 32-bit set value to the CAPTUREn registers.

- 2. Write 1 to RTC0SET. This will transfer the contents of the CAPTUREn registers to the SmaRTClock timer.

- 3. Operation is complete when RTC0SET is cleared to 0 by hardware.

The following steps can be used to read the current timer value:

- 1. Write 1 to RTC0CAP. This will transfer the contents of the timer to the CAPTUREn registers.

- 2. Poll RTC0CAP until it is cleared to 0 by hardware.

- 3. A snapshot of the timer value can be read from the CAPTUREn registers

Notes:

- 1. If the system clock is faster than 4x the SmaRTClock, then the HSMODE bit should be set to allow the set and capture operations to be concluded quickly (system clock used for transfers).

- 2. If the system clock is slower than 4x the SmaRTClock, then HSMODE should be set to zero, and RTC must be

LCD0CF Register.

- 8. Set the LCD contrast using the LCD0CNTRST register.

- 9. Set the desired threshold for the VBAT Supply Monitor.

- 10. Set the LCD refresh rate using the LCD0DIVH:LCD0DIVL registers.

- 11. Write a pattern to the LCD0Dn registers.

- 12. Enable the LCD by setting bit 0 of LCD0MSCN to logic 1 (LCD0MSCN |= 0x01).

#### 26.2. Mapping Data Registers to LCD Pins

The LCD0 data registers are organized as 16 byte-wide special function registers (LCD0Dn), each halfbyte or nibble in these registers controls 1 LCD output pin. There are 32 nibbbles used to control the 32 segment pins.

Each LCD0 segment pin can control 1, 2, 3, or 4 LCD segments depending on the selected mux mode. The least significant bit of each nibble controls the segment connected to the backplane signal COM0. The next to least significant bit controls the segment associated with COM1, the next bit controls the segment associated with COM2, and the most significant bit in the 4-bit nibble controls the segment associated with COM3.

In static mode, only the least significant bit in each nibble is used and the three remaining bits in each nibble are ignored. In 2-mux mode, only the two least significant bits are used; in 3-mux mode, only the three least significant bits are used, and in 4-mux mode, each of the 4 bits in the nibble controls one LCD segment. Bits with a value of 1 turn on the associated segment and bits with a value of 0 turn off the associated segment.

| Bit   | 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------|-----|-----|-----|-----|-----|-----|-----|

| Name  | LCD0Dn |     |     |     |     |     |     |     |

| Туре  | R/W    | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

### SFR Definition 26.1. LCD0Dn: LCD0 Data

SFR Page: 0x2

Addresses: LCD0D0 = 0x89, LCD0D1 = 0x8A, LCD0D2 = 0x8B, LCD0D3 = 0x8C, LCD0D4 = 0x8D, LCD0D5 = 0x8E, LCD0D6 = 0x91, LCD0D7 = 0x92, LCD0D8 = 0x93, LCD0D9 = 0x94, LCD0DA = 0x95, LCD0DB = 0x96, LCD0DC = 0x97, LCD0DD = 0x99, LCD0DE = 0x9A, LCD0DF = 0x9B.

| Bit | Name   | Function                                                                                                              |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------|

| 7:0 | LCD0Dn | LCD Data.                                                                                                             |

|     |        | Each nibble controls one LCD pin.<br>See "Mapping Data Registers to LCD Pins" on page 335 for additional information. |

## SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0

| Bit   | 7     | 6    | 5     | 4    | 3      | 2     | 1     | 0     |

|-------|-------|------|-------|------|--------|-------|-------|-------|

| Name  | CP1AE | CP1E | CP0AE | CP0E | SYSCKE | SMB0E | SPI0E | URT0E |

| Туре  | R/W   | R/W  | R/W   | R/W  | R/W    | R/W   | R/W   | R/W   |

| Reset | 0     | 0    | 0     | 0    | 0      | 0     | 0     | 0     |

#### SFR Page = 0x0; SFR Address = 0xE1

| Bit     | Name         | Function                                                                                                                                                                                                                                |

|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | CP1AE        | Comparator1 Asynchronous Output Enable.<br>0: Asynchronous CP1 output unavailable at Port pin.<br>1: Asynchronous CP1 output routed to Port pin.                                                                                        |

| 6       | CP1E         | Comparator1 Output Enable.<br>0: CP1 output unavailable at Port pin.<br>1: CP1 output routed to Port pin.                                                                                                                               |

| 5       | CP0AE        | Comparator0 Asynchronous Output Enable.<br>0: Asynchronous CP0 output unavailable at Port pin.<br>1: Asynchronous CP0 output routed to Port pin.                                                                                        |

| 4       | CP0E         | Comparator0 Output Enable.<br>0: CP1 output unavailable at Port pin.<br>1: CP1 output routed to Port pin.                                                                                                                               |

| 3       | SYSCKE       | SYSCLK Output Enable.0: SYSCLK output unavailable at Port pin.1: SYSCLK output routed to Port pin.                                                                                                                                      |

| 2       | SMB0E        | SMBus I/O Enable.0: SMBus I/O unavailable at Port pin.1: SDA and SCL routed to Port pins.                                                                                                                                               |

| 1       | SPI0E        | <ul> <li>SPI0 I/O Enable</li> <li>0: SPI0 I/O unavailable at Port pin.</li> <li>1: SCK, MISO, and MOSI (for SPI0) routed to Port pins.</li> <li>NSS (for SPI0) routed to Port pin only if SPI0 is configured to 4-wire mode.</li> </ul> |

| 0       | URT0E        | UART0 Output Enable.<br>0: UART I/O unavailable at Port pin.<br>1: TX0 and RX0 routed to Port pins P0.4 and P0.5.                                                                                                                       |

| Note: S | PI0 can be a | ssigned either 3 or 4 Port I/O pins.                                                                                                                                                                                                    |

## SFR Definition 27.16. P1MDOUT: Port1 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P1MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xA5

| Bit | Name         | Function                                                                                                                                                                                                                          |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDOUT[7:0] | Output Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                           |

|     |              | <ul> <li>These bits control the digital driver even when the corresponding bit in register P1MDIN is logic 0.</li> <li>0: Corresponding P1.n Output is open-drain.</li> <li>1: Corresponding P1.n Output is push-pull.</li> </ul> |

## SFR Definition 27.17. P1DRV: Port1 Drive Strength

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | P1DRV[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0xA5

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |

## SFR Definition 31.2. SPI1CN: SPI1 Control

| Bit   | 7    | 6    | 5    | 4      | 3          | 2 | 1     | 0     |

|-------|------|------|------|--------|------------|---|-------|-------|

| Name  | SPIF | WCOL | MODF | RXOVRN | NSSMD[1:0] |   | TXBMT | SPIEN |

| Туре  | R/W  | R/W  | R/W  | R/W    | R/W        |   | R     | R/W   |

| Reset | 0    | 0    | 0    | 0      | 0          | 1 | 1     | 0     |

## SFR Page = 0x0; SFR Address = 0xB0; Bit-Addressable

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SPIF       | SPI1 Interrupt Flag.                                                                                                                                                                                                                                                                                                                                                                         |

|     |            | This bit is set to logic 1 by hardware at the end of a data transfer. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                                                                                     |

| 6   | WCOL       | Write Collision Flag.                                                                                                                                                                                                                                                                                                                                                                        |

|     |            | This bit is set to logic 1 if a write to SPI1DAT is attempted when TXBMT is 0. When this occurs, the write to SPI1DAT will be ignored, and the transmit buffer will not be written. If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                       |

| 5   | MODF       | Mode Fault Flag.                                                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when a master mode collision is detected (NSS is low, MSTEN = 1, and NSSMD[1:0] = 01). If SPI interrupts are enabled, an interrupt will be generated. This bit is not automatically cleared by hardware, and must be cleared by software.                                                                                                             |

| 4   | RXOVRN     | Receive Overrun Flag (valid in slave mode only).                                                                                                                                                                                                                                                                                                                                             |

|     |            | This bit is set to logic 1 by hardware when the receive buffer still holds unread data<br>from a previous transfer and the last bit of the current transfer is shifted into the<br>SPI1 shift register. If SPI interrupts are enabled, an interrupt will be generated. This<br>bit is not automatically cleared by hardware, and must be cleared by software.                                |

| 3:2 | NSSMD[1:0] | Slave Select Mode.                                                                                                                                                                                                                                                                                                                                                                           |

|     |            | Selects between the following NSS operation modes:<br>(See Section 31.2 and Section 31.3).<br>00: 3-Wire Slave or 3-Wire Master Mode. NSS signal is not routed to a port pin.<br>01: 4-Wire Slave or Multi-Master Mode (Default). NSS is an input to the device.<br>1x: 4-Wire Single-Master Mode. NSS signal is mapped as an output from the<br>device and will assume the value of NSSMD0. |

| 1   | TXBMT      | Transmit Buffer Empty.                                                                                                                                                                                                                                                                                                                                                                       |

|     |            | This bit will be set to logic 0 when new data has been written to the transmit buffer.<br>When data in the transmit buffer is transferred to the SPI shift register, this bit will<br>be set to logic 1, indicating that it is safe to write a new byte to the transmit buffer.                                                                                                              |

| 0   | SPIEN      | SPI1 Enable.                                                                                                                                                                                                                                                                                                                                                                                 |

|     |            | 0: SPI disabled.<br>1: SPI enabled.                                                                                                                                                                                                                                                                                                                                                          |