# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 34                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 8.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                       |

| Data Converters            | A/D 16x10b/12b                                                    |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 40-VFQFN Exposed Pad                                              |

| Supplier Device Package    | 40-QFN (6x6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f965-b-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 5.10. External Voltage Reference                     |     |

|----|------------------------------------------------------|-----|

|    | 5.11. Internal Voltage Reference                     |     |

|    | 5.12. Analog Ground Reference                        | 101 |

|    | 5.13. Temperature Sensor Enable                      |     |

|    | 5.14. Voltage Reference Electrical Specifications    |     |

| 6. | Programmable Current Reference (IREF0)               |     |

|    | 6.1. PWM Enhanced Mode                               | 103 |

|    | 6.2. IREF0 Specifications                            |     |

| 7. | Comparators                                          |     |

|    | 7.1. Comparator Inputs                               | 105 |

|    | 7.2. Comparator Outputs                              |     |

|    | 7.3. Comparator Response Time                        |     |

|    | 7.4. Comparator Hysterisis                           | 107 |

|    | 7.5. Comparator Register Descriptions                |     |

|    | 7.6. Comparator0 and Comparator1 Analog Multiplexers | 112 |

| 8. | CIP-51 Microcontroller                               | 115 |

|    | 8.1. Instruction Set                                 | 116 |

|    | 8.1.1. Instruction and CPU Timing                    | 116 |

|    | 8.2. CIP-51 Register Descriptions                    | 121 |

| 9. | Memory Organization                                  |     |

|    | 9.1. Program Memory                                  | 124 |

|    | 9.1.1. MOVX Instruction and Program Memory           | 127 |

|    | 9.2. Data Memory                                     |     |

|    | 9.2.1. Internal RAM                                  | 127 |

|    | 9.2.2. External RAM                                  | 128 |

| 10 | . External Data Memory Interface and On-Chip XRAM    | 129 |

|    | 10.1. Accessing XRAM                                 | 129 |

|    | 10.1.1. 16-Bit MOVX Example                          |     |

|    | 10.1.2. 8-Bit MOVX Example                           | 129 |

|    | 10.2. Configuring the External Memory Interface      |     |

|    | 10.3. Port Configuration                             |     |

|    | 10.4. Multiplexed and Non-multiplexed Selection      | 134 |

|    | 10.4.1. Multiplexed Configuration                    | 134 |

|    | 10.4.2. Non-multiplexed Configuration                |     |

|    | 10.5. Memory Mode Selection                          |     |

|    | 10.5.1. Internal XRAM Only                           | 136 |

|    | 10.5.2. Split Mode without Bank Select               |     |

|    | 10.5.3. Split Mode with Bank Select                  |     |

|    | 10.5.4. External Only                                |     |

|    | 10.6. Timing                                         |     |

|    | 10.6.1. Non-Multiplexed Mode                         |     |

|    | 10.6.2. Multiplexed Mode                             |     |

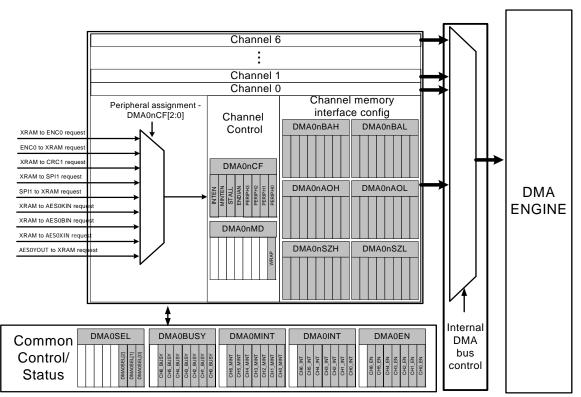

| 11 | . Direct Memory Access (DMA0)                        |     |

|    | 11.1. DMA0 Architecture                              |     |

|    | 11.2. DMA0 Arbitration                               |     |

|    |                                                      |     |

| SFR Definition 25.19. PC0HIST: PC0 History       331         SFR Definition 25.21. PC0INT1: PC0 Interrupt 0       332         SFR Definition 25.21. PC0INT1: PC0 Interrupt 1       333         SFR Definition 26.1. LCD0CNT: LCD0 Control Register       335         SFR Definition 26.1. LCD0CNT: LCD0 Contrast Adjustment       341         SFR Definition 26.4. LCD0MSCN: LCD0 Master Control       342         SFR Definition 26.5. LCD0MSCF: LCD0 Master Configuration       343         SFR Definition 26.6. LCD0PWR: LCD0 VBAT Monitor Control       344         SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.8. LCD0CLKDIVL: LCD Refresh Rate Prescaler Ligh Byte       345         SFR Definition 26.10. LCD0EXDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.11. LCD0TGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCN: LCD0 Charge Pump Control       349         SFR Definition 26.15. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.14. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 27.1. XBR0: Port //O Crossbar Register 1       35                                                                    |                                                                       |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|

| SFR Definition 25.21. PC0INT1: PC0 Interrupt 1       333         SFR Definition 26.1. LCD0DN: LCD0 Data       335         SFR Definition 26.3. LCD0CNTRST: LCD0 Control Register       337         SFR Definition 26.4. LCD0MSCN: LCD0 Master Control       342         SFR Definition 26.6. LCD0PWRS: LCD0 Master Configuration       343         SFR Definition 26.6. LCD0PWR: LCD0 VBAT Monitor Control       343         SFR Definition 26.6. LCD0CKDIV: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.9. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask.       346         SFR Definition 26.11. LCD0TGR: LCD0 Charge Pump Control       348         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Control       349         SFR Definition 26.15. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Mode       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       350         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       350         SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2       360 <td>SFR Definition 25.19. PC0HIST: PC0 History</td> <td> 331</td>     | SFR Definition 25.19. PC0HIST: PC0 History                            | 331 |

| SFR Definition 26.1. LCD0Dn: LCD0 Data       335         SFR Definition 26.2. LCD0CN: LCD0 Control Register       337         SFR Definition 26.3. LCD0NSCF: LCD0 Master Control       341         SFR Definition 26.4. LCD0WSCN: LCD0 Master Control       342         SFR Definition 26.5. LCD0WSCF: LCD0 VBATE Monitor Control       343         SFR Definition 26.6. LCD0VBKCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.8. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Bink Mask       346         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCF: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Control       349         SFR Definition 26.15. LCD0CHPCF: LCD0 Charge Pump Mode       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.17. LCD00KF: LCD0 Buffer Control       349         SFR Definition 26.19. LCD0VBMCF: LCD0 Buffer Control       349         SFR Definition 27.1 XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 2       360                                                                                        | SFR Definition 25.20. PC0INT0: PC0 Interrupt 0                        | 332 |

| SFR Definition 26.2. LCD0CN: LCD0 Control Register       337         SFR Definition 26.3. LCD0CNTRST: LCD0 Contrast Adjustment       341         SFR Definition 26.4. LCD0MSCN: LCD0 Master Control       342         SFR Definition 26.6. LCD0PWR: LCD0 Power       343         SFR Definition 26.6. LCD0VBMCN: LCD0 Power       343         SFR Definition 26.6. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.0. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Toggle Rate       347         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Charge Pump Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.14. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Configuration       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       350         SFR Definition 26.17. LCD0BUFCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 1       350         SFR Definition 27.1. XBR2: Port I/O Crossbar Register 1       350         SFR Definition 27.5. P0MAT: Port0 Match Register       361         SFR Definition 27.7. P1MASK: Port1 Mask R                                                           | SFR Definition 25.21. PC0INT1: PC0 Interrupt 1                        | 333 |

| SFR Definition 26.3. LCD0CNTRST: LCD0 Contrast Adjustment       341         SFR Definition 26.4. LCD0MSCN: LCD0 Master Configuration       343         SFR Definition 26.6. LCD0WSCF: LCD0 VBAT Monitor Control       343         SFR Definition 26.6. LCD0VBMCN: LCD0 VBAT Monitor Control       343         SFR Definition 26.7. LCD0VBMCN: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.8. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Control       348         SFR Definition 26.15. LCD0CHPCN: LCD0 Charge Pump Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       349         SFR Definition 26.17. LCD0BUFCN: LCD0 Buffer Configuration       350         SFR Definition 26.18. LCD0BUFCN: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1 XBR: Port I/O Crossbar Register 0       358         SFR Definition 27.2 XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4 PMASK: Port0 Mask Register       361         SFR Definition 27.7 P1MASK: Port1 Mask Register       362         SFR Defini                                                           |                                                                       |     |

| SFR Definition 26.3. LCD0CNTRST: LCD0 Contrast Adjustment       341         SFR Definition 26.4. LCD0MSCN: LCD0 Master Configuration       343         SFR Definition 26.6. LCD0WSCF: LCD0 VBAT Monitor Control       343         SFR Definition 26.6. LCD0VBMCN: LCD0 VBAT Monitor Control       343         SFR Definition 26.7. LCD0VBMCN: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.8. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Control       348         SFR Definition 26.15. LCD0CHPCN: LCD0 Charge Pump Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       349         SFR Definition 26.17. LCD0BUFCN: LCD0 Buffer Configuration       350         SFR Definition 26.18. LCD0BUFCN: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1 XBR: Port I/O Crossbar Register 0       358         SFR Definition 27.2 XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4 PMASK: Port0 Mask Register       361         SFR Definition 27.7 P1MASK: Port1 Mask Register       362         SFR Defini                                                           | SFR Definition 26.2. LCD0CN: LCD0 Control Register                    | 337 |

| SFR Definition 26.4. LCD0MSCF: LCD0 Master Configuration       342         SFR Definition 26.5. LCD0MSCF: LCD0 Power       343         SFR Definition 26.6. LCD0VWR: LCD0 Power       343         SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.9. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD00HPCN: LCD0 Charge Pump Mode       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. POMASK: Port0 Mask Register       361         SFR Definition 27.7. PMAT: Port1 Mask Register       362         SFR Definition 27.7. P1MASK: Port1 Mask Register       362                                                                             | SFR Definition 26.3. LCD0CNTRST: LCD0 Contrast Adjustment             | 341 |

| SFR Definition 26.6. LCD0PWR: LCD0 Power       343         SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.8. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.9. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Control       349         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.5. P0MAT: Port0 Mask Register       362         SFR Definition 27.7. P1MAT: Port0 Input Mode       365 <td>SFR Definition 26.4. LCD0MSCN: LCD0 Master Control</td> <td> 342</td>       | SFR Definition 26.4. LCD0MSCN: LCD0 Master Control                    | 342 |

| SFR Definition 26.6. LCD0PWR: LCD0 Power       343         SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control       344         SFR Definition 26.8. LCD0CLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.9. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Control       349         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.5. P0MAT: Port0 Mask Register       362         SFR Definition 27.7. P1MAT: Port0 Input Mode       365 <td>SFR Definition 26.5. LCD0MSCF: LCD0 Master Configuration</td> <td> 343</td> | SFR Definition 26.5. LCD0MSCF: LCD0 Master Configuration              | 343 |

| SFR Definition 26.8. LCDOCLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.9. LCDOCLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCDOBLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCDOTOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Configuration       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. PUMASK: Port0 Mask Register       361         SFR Definition 27.5. POMAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Mask Register       362         SFR Definition 27.10. POMDIN: Port0 Otuput Mode       365         SFR Definition 27.11. POMDOUT: Port0 Otuput Mode       3                                                                    | SFR Definition 26.6. LCD0PWR: LCD0 Power                              | 343 |

| SFR Definition 26.8. LCDOCLKDIVH: LCD0 Refresh Rate Prescaler High Byte       345         SFR Definition 26.9. LCDOCLKDIVL: LCD Refresh Rate Prescaler Low Byte       345         SFR Definition 26.10. LCDOBLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCDOTOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Configuration       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. PUMASK: Port0 Mask Register       361         SFR Definition 27.5. POMAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Mask Register       362         SFR Definition 27.10. POMDIN: Port0 Otuput Mode       365         SFR Definition 27.11. POMDOUT: Port0 Otuput Mode       3                                                                    | SFR Definition 26.7. LCD0VBMCN: LCD0 VBAT Monitor Control             | 344 |

| SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask       346         SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPCN: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Configuration       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1 XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2 XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2       360         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.5. POMAT: Port0 Match Register       362         SFR Definition 27.7. P1MAT: Port1 Match Register       362         SFR Definition 27.8. P0: Port0       364         SFR Definition 27.10. POMDUN: Port0 Dutput Mode       365         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition                                                                                               |                                                                       |     |

| SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate       347         SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Configuration       349         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Mode       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCF: LCD0 Buffer Control       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration       350         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2 XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2       360         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.5. P0MAT: Port0 Match Register       362         SFR Definition 27.7. P1MASK: Port1 Mask Register       362         SFR Definition 27.8. P0: Port0       364         SFR Definition 27.1. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.10. P0MDIN: Port0 Input Mode       364         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.12. P0DRV: Port0 Skip       364         SFR Definition 27.14. P1SKIP: Port1 Skip                                                                                                     | SFR Definition 26.9. LCD0CLKDIVL: LCD Refresh Rate Prescaler Low Byte | 345 |

| SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Mode       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.15. LCD0BUFCF: LCD0 Buffer Configuration       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration       350         SFR Definition 26.18. LCD0BUFCF: LCD0 Buffer Mode       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. POMASK: Port0 Mask Register       360         SFR Definition 27.5. P0MAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Match Register       362         SFR Definition 27.7. P1MAT: Port1 Match Register       362         SFR Definition 27.8. P0: Port0       364         SFR Definition 27.10. P0MDIN: Port0 Input Mode       365         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.12. P0DRV: Port1 Output Mode       366         SFR Definition 27.13. P1: Port1       366         SFR Definition 27.14. P1SKIP: Port1 Skip       366         SFR Definition 27.15. P1MDIN: Port1 Input Mode       367 <td>SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask</td> <td> 346</td>                                   | SFR Definition 26.10. LCD0BLINK: LCD0 Blink Mask                      | 346 |

| SFR Definition 26.12. LCD0CF: LCD0 Configuration       348         SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control       348         SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Mode       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.15. LCD0BUFCF: LCD0 Buffer Configuration       349         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration       350         SFR Definition 26.18. LCD0BUFCF: LCD0 Buffer Mode       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.4. POMASK: Port0 Mask Register       360         SFR Definition 27.5. P0MAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Match Register       362         SFR Definition 27.7. P1MAT: Port1 Match Register       362         SFR Definition 27.8. P0: Port0       364         SFR Definition 27.10. P0MDIN: Port0 Input Mode       365         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.12. P0DRV: Port1 Output Mode       366         SFR Definition 27.13. P1: Port1       366         SFR Definition 27.14. P1SKIP: Port1 Skip       366         SFR Definition 27.15. P1MDIN: Port1 Input Mode       367 <td>SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate</td> <td> 347</td>                                   | SFR Definition 26.11. LCD0TOGR: LCD0 Toggle Rate                      | 347 |

| SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       350         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Mode       350         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.3. XBR2: Port I/O Crossbar Register 1       359         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.5. P0MAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Mask Register       362         SFR Definition 27.7. P1MAT: Port1 Match Register       362         SFR Definition 27.10. P0MDIN: Port0 Skip       364         SFR Definition 27.10. P0MDIN: Port0 Output Mode       365         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.12. P0DRV: Port0 Drive Strength       366         SFR Definition 27.14. P1SKIP: Port1 Skip       367         SFR Definition 27.15. P1MDIN: Port1 Input Mode       368         SFR Definition 27.16. P1MDO                                                                                              | SFR Definition 26.12. LCD0CF: LCD0 Configuration                      | 348 |

| SFR Definition 26.14. LCD0CHPCF: LCD0 Charge Pump Configuration       349         SFR Definition 26.15. LCD0CHPMD: LCD0 Buffer Control       349         SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Configuration       350         SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Mode       350         SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode       350         SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration       350         SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0       358         SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1       359         SFR Definition 27.3. XBR2: Port I/O Crossbar Register 1       359         SFR Definition 27.4. P0MASK: Port0 Mask Register       361         SFR Definition 27.5. P0MAT: Port0 Match Register       361         SFR Definition 27.6. P1MASK: Port1 Mask Register       362         SFR Definition 27.7. P1MAT: Port1 Match Register       362         SFR Definition 27.10. P0MDIN: Port0 Skip       364         SFR Definition 27.10. P0MDIN: Port0 Output Mode       365         SFR Definition 27.11. P0MDOUT: Port0 Output Mode       365         SFR Definition 27.12. P0DRV: Port0 Drive Strength       366         SFR Definition 27.14. P1SKIP: Port1 Skip       367         SFR Definition 27.15. P1MDIN: Port1 Input Mode       368         SFR Definition 27.16. P1MDO                                                                                              | SFR Definition 26.13. LCD0CHPCN: LCD0 Charge Pump Control             | 348 |

| SFR Definition 26.15. LCD0CHPMD: LCD0 Charge Pump Mode349SFR Definition 26.16. LCD0BUFCN: LCD0 Buffer Control349SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration350SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode350SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration350SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0358SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. POMASK: Port0 Mask Register361SFR Definition 27.5. POMAT: Port0 Match Register362SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register364SFR Definition 27.10. POMDIN: Port0 Skip364SFR Definition 27.11. POMDOUT: Port0 Output Mode365SFR Definition 27.12. PODRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port1 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Input Mode370SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                  |                                                                       |     |

| SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration350SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode350SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration350SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0358SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register362SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode366SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode368SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode </td <td></td> <td></td>                                                                                             |                                                                       |     |

| SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode350SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration350SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0358SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1367SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Ioutput Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Output Mode368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                |                                                                       |     |

| SFR Definition 26.18. LCD0BUFMD: LCD0 Buffer Mode350SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration350SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0358SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1367SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Ioutput Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Output Mode368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                | SFR Definition 26.17. LCD0BUFCF: LCD0 Buffer Configuration            | 350 |

| SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0358SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode368SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Input Mode370SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                     |                                                                       |     |

| SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1359SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Net2369SFR Definition 27.19. P2SKIP: Port2 Net2369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                     | SFR Definition 26.19. LCD0VBMCF: LCD0 VBAT Monitor Configuration      | 350 |

| SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Input Mode370SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SFR Definition 27.1. XBR0: Port I/O Crossbar Register 0               | 358 |

| SFR Definition 27.3. XBR2: Port I/O Crossbar Register 2360SFR Definition 27.4. P0MASK: Port0 Mask Register361SFR Definition 27.5. P0MAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Input Mode370SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SFR Definition 27.2. XBR1: Port I/O Crossbar Register 1               | 359 |

| SFR Definition 27.5. POMAT: Port0 Match Register361SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.19. P2SKIP: Port2 Input Mode370SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                       |     |

| SFR Definition 27.6. P1MASK: Port1 Mask Register362SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SFR Definition 27.4. P0MASK: Port0 Mask Register                      | 361 |

| SFR Definition 27.7. P1MAT: Port1 Match Register362SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SFR Definition 27.5. P0MAT: Port0 Match Register                      | 361 |

| SFR Definition 27.8. P0: Port0364SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SFR Definition 27.6. P1MASK: Port1 Mask Register                      | 362 |

| SFR Definition 27.9. P0SKIP: Port0 Skip364SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SFR Definition 27.7. P1MAT: Port1 Match Register                      | 362 |

| SFR Definition 27.10. P0MDIN: Port0 Input Mode365SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SFR Definition 27.8. P0: Port0                                        | 364 |

| SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                       |     |

| SFR Definition 27.11. P0MDOUT: Port0 Output Mode365SFR Definition 27.12. P0DRV: Port0 Drive Strength366SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SFR Definition 27.10. P0MDIN: Port0 Input Mode                        | 365 |

| SFR Definition 27.13. P1: Port1366SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                       |     |

| SFR Definition 27.14. P1SKIP: Port1 Skip367SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SFR Definition 27.12. P0DRV: Port0 Drive Strength                     | 366 |

| SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SFR Definition 27.13. P1: Port1                                       | 366 |

| SFR Definition 27.15. P1MDIN: Port1 Input Mode367SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SFR Definition 27.14. P1SKIP: Port1 Skip                              | 367 |

| SFR Definition 27.16. P1MDOUT: Port1 Output Mode368SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SFR Definition 27.15. P1MDIN: Port1 Input Mode                        | 367 |

| SFR Definition 27.17. P1DRV: Port1 Drive Strength368SFR Definition 27.18. P2: Port2369SFR Definition 27.19. P2SKIP: Port2 Skip369SFR Definition 27.20. P2MDIN: Port2 Input Mode370SFR Definition 27.21. P2MDOUT: Port2 Output Mode370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                       |     |

| SFR Definition 27.19. P2SKIP: Port2 Skip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                       |     |

| SFR Definition 27.20. P2MDIN: Port2 Input Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                       |     |

| SFR Definition 27.20. P2MDIN: Port2 Input Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SFR Definition 27.19. P2SKIP: Port2 Skip                              | 369 |

| SFR Definition 27.21. P2MDOUT: Port2 Output Mode 370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SFR Definition 27.20. P2MDIN: Port2 Input Mode                        | 370 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                       |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                       |     |

| SFR Definition 27.23. P3: Port3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                       |     |

## SFR Definition 5.4. ADC0PWR: ADC0 Burst Mode Power-Up Time

| Bit   | 7      | 6 | 5 | 4 | 3           | 2 | 1 | 0 |

|-------|--------|---|---|---|-------------|---|---|---|

| Name  | AD0LPM |   |   |   | AD0PWR[3:0] |   |   |   |

| Туре  | R/W    | R | R | R | R/W         |   |   |   |

| Reset | 0      | 0 | 0 | 0 | 1           | 1 | 1 | 1 |

#### SFR Page = 0xF; SFR Address = 0xBA

| Bit | Name        | Function                                                                                                                               |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AD0LPM      | ADC0 Low Power Mode Enable.                                                                                                            |

|     |             | Enables Low Power Mode Operation.                                                                                                      |

|     |             | 0: Low Power Mode disabled.                                                                                                            |

|     |             | 1: Low Power Mode enabled.                                                                                                             |