# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 34                                                                |

| Program Memory Size        | 16KB (16K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 4.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                       |

| Data Converters            | A/D 16x10b/12b                                                    |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 40-VFQFN Exposed Pad                                              |

| Supplier Device Package    | 40-QFN (6x6)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f969-b-gmr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

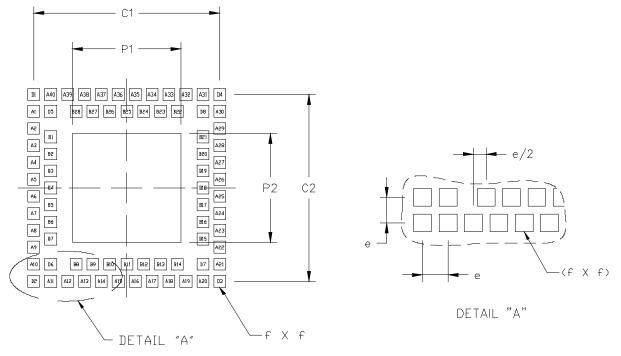

#### 3.1.2. Land Pattern

|                 | Dimension (mm)                                                                    |                       |  |  |

|-----------------|-----------------------------------------------------------------------------------|-----------------------|--|--|

| Symbol          | Тур                                                                               | Мах                   |  |  |

| C1              | 5.50                                                                              |                       |  |  |

| C2              | 5.50                                                                              |                       |  |  |

| е               | 0.50                                                                              | —                     |  |  |

| f               | —                                                                                 | 0.35                  |  |  |

| P1              | —                                                                                 | 3.20                  |  |  |

| P2              | —                                                                                 | 3.20                  |  |  |

| (MMC) and a car | shown are at Maximum I<br>rd fabrication tolerance o<br>id Tolerancing is per the | f 0.05 mm is assumed. |  |  |

#### Table 3.3. DQFN-76 Land Pattern Dimensions

- **2.** Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- **3.** This Land Pattern Design is based on the IPC-7351 guidelines.

| Dimension | Min | Nominal | Max |

|-----------|-----|---------|-----|

| Θ         | 0°  | 3.5°    | 7°  |

| aaa       |     | 0.20    |     |

| bbb       |     | 0.20    |     |

| ccc       |     | 0.08    |     |

| ddd       |     | 0.08    |     |

| eee       |     | 0.05    |     |

#### Table 3.7. TQFP-80 Package Dimensions

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This package outline conforms to JEDEC MS-026, variant ADD.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 4. Electrical Characteristics

Throughout the Electrical Characteristics chapter:

• "VIO" refers to the VIO or VIORF Supply Voltage.

#### 4.1. Absolute Maximum Specifications

#### Table 4.1. Absolute Maximum Ratings

| Parameter                                                                                                              | Condition                                                           | Min  | Тур | Max       | Unit |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|-----|-----------|------|

| Ambient Temperature under Bias                                                                                         |                                                                     | -55  | _   | 125       | °C   |

| Storage Temperature                                                                                                    |                                                                     | -65  | _   | 150       | °C   |

| Voltage on any VIO Port I/O Pin<br>(all Port I/O pins except P1.5/6/7<br>and P2.0/1/2/3) or RST with<br>respect to GND |                                                                     | -0.3 | _   | VIO + 2   | V    |

| Voltage on P1.5/6/7 or P2.0/1/2/3 with respect to GND.                                                                 |                                                                     | -0.3 | _   | VIORF + 2 | V    |

| Voltage on VBAT, VBATDC, VIO,<br>or VIORF with respect to GND                                                          |                                                                     | -0.3 | _   | 4.0       | V    |

| Maximum Total Current through<br>VBAT or GND                                                                           |                                                                     | _    | —   | 500       | mA   |

| Maximum Current through $\overline{RST}$ or any Port Pin                                                               |                                                                     | _    | _   | 100       | mA   |

| Maximum Total Current through all Port Pins                                                                            |                                                                     | —    | —   | 200       | mA   |

| Note: Stresses above those listed und<br>This is a stress rating only and                                              | der "Absolute Maximum Ratings"<br>functional operation of the devic | -    |     | -         |      |

This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### Table 4.4. Digital Supply Current with DC-DC Converter Disabled (Continued)

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                                    | Condition                    | Min | Тур | Max | Unit |  |  |

|--------------------------------------------------------------|------------------------------|-----|-----|-----|------|--|--|

| Digital Supply Current—Sleep Mode (LCD Enabled, RTC enabled) |                              |     |     |     |      |  |  |

| Digital Supply Current                                       | 1.8 V, T = 25 °C, static LCD | _   | 0.4 | —   | μA   |  |  |

| (Sleep Mode, SmaRTClock                                      | 3.0 V, T = 25 °C, static LCD |     | 0.6 |     |      |  |  |

| running, internal LFO, LCD                                   | 3.6 V, T = 25 °C, static LCD | —   | 0.8 | —   |      |  |  |

| Contrast Mode 1, charge                                      | 1.8 V, T = 25 °C, 2-Mux LCD  | _   | 0.7 | _   | μA   |  |  |

| pump disabled, 60 Hz                                         | 3.0 V, T = 25 °C, 2-Mux LCD  | —   | 1.0 | —   |      |  |  |

| refresh rate, driving 32 seg-                                | 3.6 V, T = 25 °C, 2-Mux LCD  | —   | 1.2 | —   |      |  |  |

| ment pins w/ no load)                                        | 1.8 V, T = 25 °C, 4-Mux LCD  | _   | 0.7 |     | μA   |  |  |

|                                                              | 3.0 V, T = 25 °C, 4-Mux LCD  | —   | 1.1 | —   | •    |  |  |

|                                                              | 3.6 V, T = 25 °C, 4-Mux LCD  | _   | 1.2 | —   |      |  |  |

| Digital Supply Current                                       | 1.8 V, T = 25 °C, static LCD | _   | 0.8 |     | μA   |  |  |

| (Sleep Mode, SmaRTClock                                      | 3.0 V, T = 25 °C, static LCD | _   | 1.1 | —   | •    |  |  |

| running, 32.768 kHz Crys-                                    | 3.6 V, T = 25 °C, static LCD | —   | 1.4 | —   |      |  |  |

| tal, LCD Contrast Mode 1,                                    | 1.8 V, T = 25 °C, 2-Mux LCD  | _   | 1.1 |     | μA   |  |  |

| charge pump disabled,                                        | 3.0 V, T = 25 °C, 2-Mux LCD  | _   | 1.5 | —   | •    |  |  |

| 60 Hz refresh rate, driving                                  | 3.6 V, T = 25 °C, 2-Mux LCD  | —   | 1.8 | —   |      |  |  |

| 32 segment pins w/ no load)                                  | 1.8 V, T = 25 °C, 4-Mux LCD  | _   | 1.2 |     | μA   |  |  |

|                                                              | 3.0 V, T = 25 °C, 4-Mux LCD  |     | 1.6 |     | •    |  |  |

|                                                              | 3.6 V, T = 25 °C, 4-Mux LCD  | —   | 1.9 | —   |      |  |  |

| Digital Supply Current                                       | 1.8 V, T = 25 °C, static LCD | _   | 1.2 | _   | μA   |  |  |

| (Sleep Mode, SmaRTClock                                      | 1.8 V, T = 25 °C, 2-Mux LCD  |     | 1.6 |     | •    |  |  |

| running, internal LFO, LCD                                   | 1.8 V, T = 25 °C, 3-Mux LCD  |     | 1.8 | —   |      |  |  |

| Contrast Mode 3 (2.7 V),                                     | 1.8 V, T = 25 °C, 4-Mux LCD  | —   | 2.0 | —   |      |  |  |

| charge pump enabled,                                         |                              |     |     |     |      |  |  |

| 60 Hz refresh rate, driving                                  |                              |     |     |     |      |  |  |

| 32 segment pins w/ no load)                                  |                              |     |     |     |      |  |  |

Notes:

- Active Current measure using typical code loop Digital Supply Current depends upon the particular code being executed. Digital Supply Current depends on the particular code being executed. The values in this table are obtained with the CPU executing a mix of instructions in two loops: djnz R1, \$, followed by a loop that accesses an SFR, and moves data around using the CPU (between accumulator and b-register). The supply current will vary slightly based on the physical location of this code in flash. As described in the Flash Memory chapter, it is best to align the jump addresses with a flash word address (byte location /4), to minimize flash accesses and power consumption.

- 2. Includes oscillator and regulator supply current.

- **3.** Based on device characterization data; Not production tested.

- 4. Measured with one-shot enabled.

- 5. Low-Power Idle mode current measured with CLKMODE = 0x04, PCON = 0x01, and PCLKEN = 0x0F.

- 6. Using SmaRTClock osillator with external 32.768 kHz CMOS clock. Does not include crystal bias current.

- 7. Low-Power Idle mode current measured with CLKMODE = 0x04, PCON = 0x01, and PCLKEN = 0x00.

## SFR Definition 11.5. DMA0SEL: DMA0 Channel Select for Configuration

| r     |   |     |     |     |     |              |   |   |

|-------|---|-----|-----|-----|-----|--------------|---|---|

| Bit   | 7 | 6   | 5   | 4   | 3   | 2            | 1 | 0 |

| Name  |   |     |     |     |     | DMA0SEL[2:0] |   |   |

| Туре  | R | R/W | R/W | R/W | R/W | R/W          |   |   |

| Reset | 0 | 0   | 0   | 0   | 0   | 0            | 0 | 0 |

SFR Page = 0x2; SFR Address = 0xD1

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Unused       | Read = 0b, Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2:0 | DMA0SEL[2:0] | Channel Select for Configuration.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |              | These bits select the channel for configuration of the DMA0 transfer. The first step to configure a channel for DMA0 transfer is to select the desired channel, and then write to channel specific registers DMA0NCF, DMA0NBAL/H, DMA0NAOL/H, DMA0NSZL/H.<br>000: Select channel 0<br>001: Select channel 1<br>010: Select channel 2<br>011: Select channel 3<br>100: Select channel 4<br>101: Select channel 5<br>110: Select channel 6<br>111: Invalid |

## SFR Definition 13.2. CRC1IN: CRC1 Data IN

| Bit   | 7   | 6           | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|-------------|-----|-----|-----|-----|-----|-----|--|--|

| Name  |     | CRC1IN[7:0] |     |     |     |     |     |     |  |  |

| Туре  | R/W | R/W         | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset | 0   | 0           | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

SFR Page = 0x2; SFR Address = 0xB9; Not Bit-Addressable

| Bit | Name        | Function                                                                                                                                                                                |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | CRC1IN[7:0] | CRC1Data IN.                                                                                                                                                                            |

|     |             | CRC Data should be sequentially written, one byte at a time, to the CRC1IN<br>Data input SFR.<br>When the CRC1 module is used with the DMA, the DMA will write directly to this<br>SFR. |

## SFR Definition 13.3. CRC1POLL: CRC1 Polynomial LSB

| Bit   | 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | CRC1POLL[7:0] |     |     |     |     |     |     |     |

| Туре  | R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0             | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Page = 0x2; SFR Address = 0xBC; Not Bit-Addressable

| Bit | Name          | Function             |

|-----|---------------|----------------------|

| 7:0 | CRC1POLL[7:0] | CRC1 Polynomial LSB. |

## SFR Definition 13.4. CRC1POLH: CRC1 Polynomial MSB

| Bit   | 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------------|-----|-----|-----|-----|-----|-----|-----|

| Name  | CRC1POLH[7:0] |     |     |     |     |     |     |     |

| Туре  | R/W           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0             | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Page = 0x2; SFR Address = 0xBD; Not Bit-Addressable

| Bit | Name          | Function             |  |

|-----|---------------|----------------------|--|

| 7:0 | CRC1POLH[7:0] | CRC1 Polynomial MSB. |  |

#### 14.6.2. CBC Encryption Initialization Vector Location

The first block to be encrypted uses the initialization vector for the AES0XIN data. Subsequent blocks will use the encrypted ciphertext from the previous block. The DMA is capable of encrypting multiple blocks. If the initialization is located at an arbitrary location in xram, the DMA base address location will need to be changed to the start of the encrypted ciphertext after encrypting the first block. However, if the initialization vector explicitly located in xram immediately before the encrypted ciphertext, the pointer will be advanced to the start of the encrypted ciphertext naturally and multiple blocks can be encrypted autonomously.

#### 14.6.3. CBC Encryption using DMA

Normally, the AES block is used with the DMA. This provides the best performance and lowest power consumption. Code examples are provided in 8051 compiler independent C code using the DMA. It is highly recommended to use with the code examples. The steps are documented in the datasheet for completeness.

Prepare encryption Key, initialization vector, and data to be encrypted in xram.

(The initialization vector should be located immediately before the data to be encrypted to encrypt multiple blocks.)

- Reset AES module by clearing bit 2 of AES0BCFG.

- Disable the first four DMA channels by clearing bits 0 to 3 in the DMA0EN sfr.

- Configure the first DMA channel for the AES0KIN sfr

- Select the first DMA channel by writing 0x00 to the DMA0SEL sfr

- Configure the first DMA channel to move xram to AES0KIN sfr by writing 0x05 to the DMA0NCF sfr

- Write 0x01 to DMA0NMD to enable wrapping

- Write the xram location of encryption key to the DMA0NBAH and DMA0NBAL sfrs.

- Write the key length in bytes to DMA0NSZL sfr

- Clear the DMA0NSZH sfr

- Clear the DMA0NAOH and DMA0NAOL sfrs

- Configure the second DMA channel for the AES0BIN sfr.

- Select the second DMA channel by writing 0x01 to the DMA0SEL sfr.

- Configure the second DMA channel to move xram to AES0BIN sfr by writing 0x06 to the DMA0NCF sfr.

- Clear DMA0NMD to disable wrapping.

- Write the xram address of the data to be encrypted to the DMA0NBAH and DMA0NBAL sfrs.

- Write the number of bytes to be encrypted in multiples of 16 bytes to the DMA0NSZH and DMA0NSZL sfrs.

- Clear the DMA0NAOH and DMA0NAOL sfrs.

- Configure the third DMA channel for the AES0XIN sfr.

- Select the third DMA channel by writing 0x02 to the DMA0SEL sfr.

- Configure the third DMA channel to move xram to AES0XIN sfr by writing 0x07 to the DMA0NCF sfr.

- Clear DMA0NMD to disable wrapping.

- Write the xram address of initialization vector to the DMA0NBAH and DMA0NBAL sfrs.

- Write the number of bytes to be encrypted in multiples of 16 bytes to the DMA0NSZH and DMA0NSZL sfrs.

- Clear the DMA0NAOH and DMA0NAOL sfrs.

- \* Configure the fourth DMA channel for the AES0YOUT sfr

- Select the fourth channel by writing 0x03 to the DMA0SEL sfr

- Configure the fourth DMA channel to move the contents of the AES0YOUT sfr to xram by writing 0x08 to the DMA0NCF sfr

- Enable transfer complete interrupt by setting bit 7 of DMA0NCF sfr

- Clear DMA0NMD to disable wrapping

- Write the xram address for encrypted data to the DMA0NBAH and DMA0NBAL sfrs.

- Write the number of bytes to be encrypted in multiples of 16 bytes to the DMA0NSZH and DMA0NSZL sfrs.

Clear the DMA0NAOH and DMA0NAOL sfrs.

- Clear first four DMA interrupts by clearing bits 0 to 2 in the DMA0INT sfr.

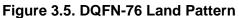

Figure 16.1. SFR Page Stack

Automatic hardware preserving and restoring of the SFR Page on interrupts may be enabled or disabled as desired using the SFR Automatic Page Control Enable Bit located in the SFR Page Control Register (SFR0CN). This function defaults to "enabled" upon reset. In this way, the autoswitching function will be enabled unless disabled in software.

A summary of the SFR locations (address and SFR page) are provided in Table 16.3 in the form of an SFR memory map. Each memory location in the map has an SFR page row, denoting the page in which that SFR resides. Certain SFRs are accessible from ALL SFR pages, and are denoted by the "(ALL PAGES)" designation. For example, the Port I/O registers P0, P1, P2, and P3 all have the "(ALL PAGES)" designation, indicating these SFRs are accessible from all SFR pages regardless of the SFRPAGE register value.

Table 16.2. SFR Map (0x80–0xBF)

| Addr. | Page | 0(8)  | 1(9)        | 2(A)        | 3(B)     | 4(C)       | 5(D)      | 6(E)      | 7(F)          |

|-------|------|-------|-------------|-------------|----------|------------|-----------|-----------|---------------|

| 0xB8  | 0x0  | IP    | IREF0CN     | ADC0AC      | ADC0MX   | ADC0CF     | ADC0L     | ADC0H     | P1MASK        |

|       | 0x2  |       | CRC1IN      | CRC1OUTL    | CRC10UTH | CRC1POLL   | CRC1POLH  | CRC1CN    |               |

|       | 0xF  |       | IREF0CF     | ADC0PWR     | ADC0TK   |            | TOFFL     | TOFFH     |               |

| 0xB0  | 0x0  | P3    | OSCXCN      | OSCICN      | PMU0MD   |            | PMU0CF    | PMU0FL    | FLKEY         |

|       | 0x2  |       | DC0CN       | DC0CF       | DC0MD    |            | LCD0CHPCN | LCD0BUFMD |               |

|       | 0xF  |       | P3MDOUT     | OSCIFL      | OSCICL   |            |           | FLSCL     |               |

| 0xA8  | 0x0  | IE    | CLKSEL      | EMIOCN      | EMI0CF   | RTC0ADR    | RTC0DAT   | RTC0KEY   | EMI0TC        |

|       | 0x2  |       | LCD0CLKDIVL | LCD0CLKDIVH | LCD0MSCN | LCD0MSCF   | LCD0CHPCF | LCD0CHPMD | LCD0VBMCF     |

|       | 0xF  |       | CLKSEL      | P6DRV       | P7DRV    | LCD0BUFCF  |           |           |               |

| 0xA0  | 0x0  | P2    | SPI0CFG     | SPI0CKR     | SPI0DAT  | POMDOUT    | P1MDOUT   | P2MDOUT   | SFRPAGE       |

|       | 0x2  |       | SPI1CFG     | SPI1CKR     | SPI1DAT  | LCD0PWR    | LCD0CF    | LCD0VBMCN |               |

|       | 0xF  |       | P3DRV       | P4DRV       | P5DRV    | P0DRV      | P1DRV     | P2DRV     |               |

| 0x98  | 0x0  | SCON0 | SBUF0       | CPT1CN      | CPT0CN   | CPT1MD     | CPT0MD    | CPT1MX    | <b>CPT0MX</b> |

|       | 0x2  |       | LCD0DD      | LCD0DE      | LCD0DF   | LCD0CNTRST | LCD0CN    | LCD0BLINK | LCD0TOGR      |

|       | 0xF  |       |             |             |          | LCD0BUFCN  |           |           |               |

| 0x90  | 0x0  | P1    | TMR3CN      | TMR3RLL     | TMR3RLH  | TMR3L      | ТМR3H     |           |               |

|       | 0x2  |       | LCD0D6      | LCD0D7      | LCD0D8   | LCD0D9     | LCD0DA    | LCD0DB    | LCD0DC        |

|       | 0xF  |       | CRC0DAT     | CRC0CN      | CRC0IN   | CRC0FLIP   |           | CRC0AUTO  | CRC0CNT       |

| 0x88  | 0x0  | TCON  | TMOD        | TL0         | TL1      | TH0        | TH1       | CKCON     | PSCTL         |

|       | 0x2  |       | LCD0D0      | LCD0D1      | LCD0D2   | LCD0D3     | LCD0D4    | LCD0D5    |               |

|       | 0xF  |       |             |             |          |            |           | SFRPGCN   |               |

| 0x80  | 0x0  | P0    | SP          | DPL         | DPH      | PSBANK     | SFRNEXT   | SFRLAST   | PCON          |

|       | 0x2  |       |             |             |          |            |           |           |               |

|       | 0xF  |       |             |             |          |            |           |           |               |

## Table 16.3. Special Function Registers (Continued)

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

| Register | Address | SFR Page  | Description                     | Page |

|----------|---------|-----------|---------------------------------|------|

| P2       | 0xA0    | All Pages | Port 2 Latch                    | 369  |

| P3DRV    | 0xA1    | 0xF       | Port 3 Drive Strength           | 373  |

| P3MDIN   | 0xF1    | 0xF       | Port 3 Input Mode Configuration | 372  |

| P3MDOUT  | 0xB1    | 0xF       | P3 Mode Out                     | 372  |

| P3       | 0xB0    | All Pages | Port 3                          | 371  |

| P4DRV    | 0xA2    | 0xF       | Port 4 Drive Strength           | 375  |

| P4MDIN   | 0xF2    | 0xF       | Port 4 Input Mode Configuration | 374  |

| P4MDOUT  | 0xF9    | 0xF       | P4 Mode Out                     | 374  |

| P4       | 0xD9    | 0xF       | Port 4 Latch                    | 373  |

| P5DRV    | 0xA3    | 0xF       | Port 5 Drive Strength           | 377  |

| P5MDIN   | 0xF3    | 0xF       | Port 5 Input Mode Configuration | 376  |

| P5MDOUT  | 0xFA    | 0xF       | P5 Mode Out                     | 376  |

| P5       | 0xDA    | 0xF       | Port 5 Latch                    | 375  |

| P6DRV    | 0xAA    | 0xF       | Port 6 Drive Strength           | 379  |

| P6MDIN   | 0xF4    | 0xF       | Port 6 Input Mode Configuration | 378  |

| P6MDOUT  | 0xFB    | 0xF       | P6 Mode Out                     | 378  |

| P6       | 0xDB    | 0xF       | Port 6 Latch                    | 377  |

| P7DRV    | 0xAB    | 0xF       | Port 7 Drive Strength           | 380  |

| P7MDOUT  | 0xFC    | 0xF       | P7 Mode Out                     | 380  |

| P7       | 0xDC    | 0xF       | Port 7 Latch                    | 379  |

| PC0CMP0H | 0xE3    | 0x2       | PC0 Comparator 0 High           | 329  |

| PC0CMP0L | 0xE1    | 0x2       | PC0 Comparator 0 Low            | 329  |

| PC0CMP0M | 0xE2    | 0x2       | PC0 Comparator 0 Middle         | 329  |

| PC0CMP1H | 0xF3    | 0x2       | PC0 Comparator 1 High           | 330  |

| PC0CMP1L | 0xF1    | 0x2       | PC0 Comparator 1 Low            | 330  |

| PC0CMP1M | 0xF2    | 0x2       | PC0 Comparator 1 Middle         | 330  |

| PC0CTR0H | 0xDC    | 0x2       | PC0 Counter 0 High              | 327  |

| PC0CTR0L | 0xDA    | 0x2       | PC0 Counter 0 Low               | 327  |

| PC0CTR0M | 0xD8    | 0x2       | PC0 Counter 0 Middle            | 327  |

| PC0CTR1H | 0xDF    | 0x2       | PC0 Counter 1 High              | 328  |

| PC0CTR1L | 0xDD    | 0x2       | PC0 Counter 1 Low               | 328  |

| PC0DCH   | 0xFA    | 0x2       | PC0 Debounce Configuration High | 325  |

| PC0DCL   | 0xF9    | 0x2       | PC0 Debounce Configuration Low  | 326  |

| PC0HIST  | 0xF4    | 0x2       | PC0 History                     | 331  |

#### 24.1.1. SmaRTClock Lock and Key Functions

The SmaRTClock Interface has an RTC0KEY register for legacy reasons, however, all writes to this register are ignored. The SmaRTClock interface is always unlocked on C8051F96x.

#### 24.1.2. Using RTC0ADR and RTC0DAT to Access SmaRTClock Internal Registers

The SmaRTClock internal registers can be read and written using RTC0ADR and RTC0DAT. The RTC0ADR register selects the SmaRTClock internal register that will be targeted by subsequent reads or writes. A SmaRTClock Write operation is initiated by writing to the RTC0DAT register. Below is an example of writing to a SmaRTClock internal register.

1. Write 0x05 to RTC0ADR. This selects the internal RTC0CN register at SmaRTClock Address 0x05.

2. Write 0x00 to RTC0DAT. This operation writes 0x00 to the internal RTC0CN register.

A SmaRTClock Read operation is initiated by writing the register address to RTC0ADR and reading from RTC0DAT. Below is an example of reading a SmaRTClock internal register.

1. Write 0x05 to RTC0ADR. This selects the internal RTC0CN register at SmaRTClock Address 0x05.

2. Read data from RTC0DAT. This data is a copy of the RTC0CN register.

#### 24.1.3. SmaRTClock Interface Autoread Feature

When Autoread is enabled, each read from RTC0DAT initiates the next indirect read operation on the SmaRTClock internal register selected by RTC0ADR. Software should set the register address once at the beginning of each series of consecutive reads. Autoread is enabled by setting AUTORD (RTC0ADR.6) to logic 1.

#### 24.1.4. RTC0ADR Autoincrement Feature

For ease of reading and writing the 32-bit CAPTURE and ALARM values, RTC0ADR automatically increments after each read or write to a CAPTUREn or ALARMn register. This speeds up the process of setting an alarm or reading the current SmaRTClock timer value. Autoincrement is always enabled.

Recommended Instruction Timing for a multi-byte register read with auto read enabled:

mov RTC0ADR, #040h

mov A, RTC0DAT

mov A, RTC0DAT

mov A, RTC0DAT

mov A, RTC0DAT

Recommended Instruction Timing for a multi-byte register write:

mov RTCOADR, #010h

mov RTCODAT, #05h

mov RTCODAT, #06h

mov RTCODAT, #07h

mov RTCODAT, #08h

## SFR Definition 25.16. PC0CMP1H: PC0 Comparator 1 High (MSB)

| Bit   | 7            | 6                  | 5                          | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|--------------|--------------------|----------------------------|---|---|---|---|---|--|--|

| Nam   | 9            | PC0CMP1H[23:16]    |                            |   |   |   |   |   |  |  |

| Туре  | e R/W        |                    |                            |   |   |   |   |   |  |  |

| Rese  | et 0         | 0                  | 0                          | 0 | 0 |   |   |   |  |  |

| SFR A | ddress = 0xF | 3; SFR Page        | e = 0x2                    |   |   |   |   |   |  |  |

| Bit   | Name         | •                  | Function                   |   |   |   |   |   |  |  |

| 7:0   | PC0CMP1H     | [23:16] <b>P</b> ( | PC0 Comparator 1 High Byte |   |   |   |   |   |  |  |

Bits 23:16 of Counter 0.

### SFR Definition 25.17. PC0CMP1M: PC0 Comparator 1 Middle

| Bit   | 7              | 7 6 5 4 3 2 1 0         |                                 |   |       |     |   |   |  |  |

|-------|----------------|-------------------------|---------------------------------|---|-------|-----|---|---|--|--|

| Nam   | PC0CMP1M[15:8] |                         |                                 |   |       |     |   | • |  |  |

| Туре  | )              | R/W                     |                                 |   |       |     |   |   |  |  |

| Rese  | et 0           | 0                       | 0                               | 0 | 0     | 0   | 0 | 0 |  |  |

| SFR A | ddress = 0xF   | 2; SFR Page             | e = 0x2                         |   |       |     |   | - |  |  |

| Bit   | Name           | 9                       |                                 |   | Funct | ion |   |   |  |  |

| 7:0   | PC0CMP1N       | A[15:8] P               | 8] PC0 Comparator 1 Middle Byte |   |       |     |   |   |  |  |

|       |                | Bits 15:8 of Counter 0. |                                 |   |       |     |   |   |  |  |

## SFR Definition 25.18. PC0CMP1L: PC0 Comparator 1 Low (LSB)

| Bit   | 7             | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---------------|-----------------|---|---|---|---|---|---|--|--|--|

| Name  | PC0CMP1L[7:0] |                 |   |   |   |   |   |   |  |  |  |

| Туре  |               | R/W             |   |   |   |   |   |   |  |  |  |

| Reset | 0             | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |  |  |

SFR Address = 0xF1; SFR Page = 0x2

| Bit | Name          | Function                  |

|-----|---------------|---------------------------|

| 7:0 | PC0CMP1L[7:0] | PC0 Comparator 1 Low Byte |

|     |               | Bits 7:0 of Counter 0.    |

**Note:** PC0CMP1L must be written last after writing PC0CMP1M and PC0CMP1H. After writing PC0CMP1L the synchronization into the PC clock domain can take 2 RTC clock cycles.

## SFR Definition 26.5. LCD0MSCF: LCD0 Master Configuration

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1       | 0      |

|-------|-----|-----|-----|-----|-----|-----|---------|--------|

| Name  |     |     |     |     |     |     | DCENSLP | CHPBYP |

| Туре  | R/W     | R/W    |

| Reset | 1   | 1   | 1   | 1   | 1   | 1   | 1       | 0      |

#### SFR Page = 0x2; SFR Address = 0xAC

| Bit | Name     | Function                                                            |

|-----|----------|---------------------------------------------------------------------|

| 7:2 | Reserved | Read = 111111b. Must write 111111b.                                 |

| 1   | DCENSLP  | DCDC Converter Enable in Sleep Mode                                 |

|     |          | 0: DCDC is disabled in Sleep Mode.                                  |

|     |          | 1: DCDC is enabled in Sleep Mode.                                   |

| 0   | CHPBYP   | LCD0 Charge Pump Bypass                                             |

|     |          | This bit should be set to 1b in Contrast Control Mode 1 and Mode 2. |

|     |          | 0: LCD0 Charge Pump is not bypassed.                                |

|     |          | 1: LCD0 Charge Pump is bypassed.                                    |

## SFR Definition 26.6. LCD0PWR: LCD0 Power

| Bit   | 7   | 6   | 5   | 4   | 3    | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|------|-----|-----|-----|

| Name  |     |     |     |     | MODE |     |     |     |

| Туре  | R/W | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |

| Reset | 0   | 0   | 0   | 0   | 1    | 0   | 0   | 1   |

#### SFR Page = 0x2; SFR Address = 0xA4

| Bit | Name     | Function                                               |  |  |  |  |

|-----|----------|--------------------------------------------------------|--|--|--|--|

| 7:4 | Unused   | Read = 0000b. Write = don't care.                      |  |  |  |  |

| 3   | MODE     | LCD0 Contrast Control Mode Selection.                  |  |  |  |  |

|     |          | LCD0 Contrast Control Mode 1 or Mode 4 is selected.    |  |  |  |  |

|     |          | 1: LCD0 Contrast Control Mode 2 or Mode 3 is selected. |  |  |  |  |

| 2:0 | Reserved | Read = 001b. Must write 001b.                          |  |  |  |  |

## SFR Definition 27.10. P0MDIN: Port0 Input Mode

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|-------------|---|---|---|---|---|---|--|--|

| Name  |   | P0MDIN[7:0] |   |   |   |   |   |   |  |  |

| Туре  |   | R/W         |   |   |   |   |   |   |  |  |

| Reset | 1 | 1           | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

#### SFR Page= 0x0; SFR Address = 0xF1

| Bit | Name        | Function                                                                                                                                                                                                                                                                                           |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDIN[7:0] | Analog Configuration Bits for P0.7–P0.0 (respectively).                                                                                                                                                                                                                                            |

|     |             | <ul><li>Port pins configured for analog mode have their weak pullup, and digital receiver disabled. The digital driver is not explicitly disabled.</li><li>0: Corresponding P0.n pin is configured for analog mode.</li><li>1: Corresponding P0.n pin is not configured for analog mode.</li></ul> |

## SFR Definition 27.11. P0MDOUT: Port0 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P0MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Page = 0x0; SFR Address = 0xA4

| Bit | Name         | Function                                                                                             |

|-----|--------------|------------------------------------------------------------------------------------------------------|

| 7:0 | P0MDOUT[7:0] | Output Configuration Bits for P0.7–P0.0 (respectively).                                              |

|     |              | These bits control the digital driver even when the corresponding bit in register P0MDIN is logic 0. |

|     |              | 0: Corresponding P0.n Output is open-drain.                                                          |

|     |              | 1: Corresponding P0.n Output is push-pull.                                                           |

## SFR Definition 27.16. P1MDOUT: Port1 Output Mode

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------------|---|---|---|---|---|---|---|

| Name  | P1MDOUT[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W          |   |   |   |   |   |   |   |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0x0; SFR Address = 0xA5

| Bit | Name         | Function                                                                                                                                                                                                                          |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1MDOUT[7:0] | Output Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                                                           |

|     |              | <ul> <li>These bits control the digital driver even when the corresponding bit in register P1MDIN is logic 0.</li> <li>0: Corresponding P1.n Output is open-drain.</li> <li>1: Corresponding P1.n Output is push-pull.</li> </ul> |

## SFR Definition 27.17. P1DRV: Port1 Drive Strength

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | P1DRV[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Page = 0xF; SFR Address = 0xA5

| Bit | Name       | Function                                                                                                                                                                                               |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P1DRV[7:0] | Drive Strength Configuration Bits for P1.7–P1.0 (respectively).                                                                                                                                        |

|     |            | Configures digital I/O Port cells to high or low output drive strength.<br>0: Corresponding P1.n Output has low output drive strength.<br>1: Corresponding P1.n Output has high output drive strength. |

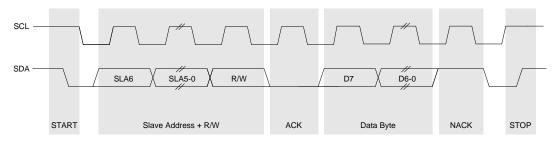

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 28.3 illustrates a typical SMBus transaction.

Figure 28.3. SMBus Transaction

#### 28.3.1. Transmitter Vs. Receiver

On the SMBus communications interface, a device is the "transmitter" when it is sending an address or data byte to another device on the bus. A device is a "receiver" when an address or data byte is being sent to it from another device on the bus. The transmitter controls the SDA line during the address or data byte. After each byte of address or data information is sent by the transmitter, the receiver sends an ACK or NACK bit during the ACK phase of the transfer, during which time the receiver controls the SDA line.

#### 28.3.2. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see Section "28.3.5. SCL High (SMBus Free) Timeout" on page 384). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

#### 28.3.3. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I<sup>2</sup>C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 28.3.4. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

When the SMBTOE bit in SMB0CF is set, Timer 3 is used to detect SCL low timeouts. Timer 3 is forced to reload when SCL is high, and allowed to count when SCL is low. With Timer 3 enabled and configured to

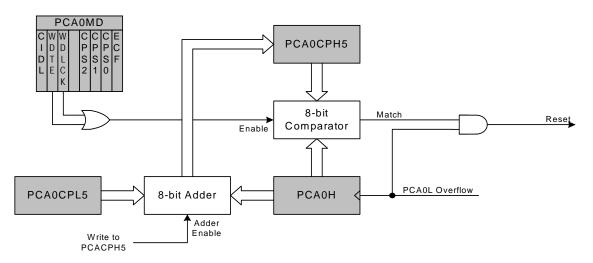

Figure 33.11. PCA Module 5 with Watchdog Timer Enabled

Note that the 8-bit offset held in PCA0CPH5 is compared to the upper byte of the 16-bit PCA counter. This offset value is the number of PCA0L overflows before a reset. Up to 256 PCA clocks may pass before the first PCA0L overflow occurs, depending on the value of the PCA0L when the update is performed. The total offset is then given (in PCA clocks) by Equation 33.5, where PCA0L is the value of the PCA0L register at the time of the update.

$Offset = (256 \times PCA0CPL5) + (256 - PCA0L)$

#### Equation 33.5. Watchdog Timer Offset in PCA Clocks

The WDT reset is generated when PCA0L overflows while there is a match between PCA0CPH5 and PCA0H. Software may force a WDT reset by writing a 1 to the CCF5 flag (PCA0CN.5) while the WDT is enabled.

#### 33.4.2. Watchdog Timer Usage

To configure the WDT, perform the following tasks:

- Disable the WDT by writing a 0 to the WDTE bit.

- Select the desired PCA clock source (with the CPS2–CPS0 bits).

- Load PCA0CPL5 with the desired WDT update offset value.

- Configure the PCA Idle mode (set CIDL if the WDT should be suspended while the CPU is in Idle mode).

- Enable the WDT by setting the WDTE bit to 1.

- Reset the WDT timer by writing to PCA0CPH5.

The PCA clock source and idle mode select cannot be changed while the WDT is enabled. The watchdog timer is enabled by setting the WDTE or WDLCK bits in the PCA0MD register. When WDLCK is set, the WDT cannot be disabled until the next system reset. If WDLCK is not set, the WDT is disabled by clearing the WDTE bit.

The WDT is enabled following any reset. The PCA0 counter clock defaults to the system clock divided by 12, PCA0L defaults to 0x00, and PCA0CPL5 defaults to 0x00. Using Equation 33.5, this results in a WDT timeout interval of 256 PCA clock cycles, or 3072 system clock cycles. Table 33.3 lists some example timeout intervals for typical system clocks.