Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IRSCI, SCI, SPI                                        |

| Peripherals                | LED, LVD, POR, PWM                                                       |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-QFP                                                                   |

| Supplier Device Package    | 44-QFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908ap16cfb |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table o          | f Contents                              |     |

|------------------|-----------------------------------------|-----|

| 17.3             | Functional Description                  | 271 |

| 17.4             | IRQ1 and IRQ2 Pins                      | 273 |

| 17.5             | IRQ Module During Break Interrupts      | 274 |

| 17.6             | IRQ Registers                           |     |

| 17.6.1           | IRQ1 Status and Control Register        |     |

| 17.6.2           | IRQ2 Status and Control Register        | 275 |

|                  | Chapter 18                              |     |

|                  | Keyboard Interrupt Module (KBI)         |     |

| 18.1             | Introduction                            |     |

| 18.2             | Features                                |     |

| 18.3             | I/O Pins                                |     |

| 18.4             | Functional Description                  |     |

| 18.4.1           | Keyboard Initialization                 |     |

| 18.5             | Keyboard Interrupt Registers            |     |

| 18.5.1<br>18.5.2 | Keyboard Status and Control Register    |     |

| 18.6             | Low-Power Modes                         |     |

| 18.6.1           | Wait Mode                               |     |

| 18.6.2           |                                         |     |

| 18.7             | Keyboard Module During Break Interrupts |     |

|                  |                                         |     |

|                  | Chapter 19                              |     |

| 10.1             | Computer Operating Properly (COP)       | 000 |

| 19.1             | Introduction                            |     |

| 19.2             | Functional Description                  |     |

| 19.3<br>19.3.1   | I/O Signals                             |     |

| 19.3.1           | ICLK                                    |     |

| 19.3.2           |                                         |     |

| 19.3.4           |                                         | 284 |

| 19.3.5           |                                         |     |

| 19.3.6           | Reset Vector Fetch                      | 284 |

| 19.3.7           |                                         |     |

| 19.3.8           | ,                                       |     |

| 19.4             | COP Control Register                    |     |

| 19.5             | Interrupts                              | 285 |

| 19.6             | Monitor Mode                            | 285 |

| 19.7             | Low-Power Modes                         |     |

| 19.7.1           | Wait Mode                               |     |

| 19.7.2           |                                         |     |

| 19.8             | COP Module During Break Mode            | 286 |

|                  | Chapter 20                              |     |

|                  | Low-Voltage Inhibit (LVI)               |     |

| 20.1             | Introduction                            | 287 |

16 Freescale Semiconductor

MC68HC908AP Family Data Sheet, Rev. 4

## **General Description**

- Timebase module

- Serial communications interface module 1 (SCI)

- Serial communications interface module 2 (SCI) with infrared (IR) encoder/decoder

- Serial peripheral interface module (SPI)

- System management bus (SMBus), version 1.0/1.1 (multi-master IIC bus)

- 8-channel, 10-bit analog-to-digital converter (ADC)

- IRQ1 external interrupt pin with integrated pullup

- IRQ2 external interrupt pin with programmable pullup

- 8-bit keyboard wakeup port with integrated pullup

- 32 general-purpose input/output (I/O) pins:

- 31 shared-function I/O pins

- 8 LED drivers (sink)

- 6 × 25mA open-drain I/O with pullup

- Low-power design (fully static with stop and wait modes)

- Master reset pin (with integrated pullup) and power-on reset

- System protection features

- Optional computer operating properly (COP) reset, driven by internal RC oscillator

- Low-voltage detection with optional reset or interrupt

- Illegal opcode detection with reset

- Illegal address detection with reset

- 48-pin low quad flat pack (LQFP), 44-pin quad flat pack (QFP), and 42-pin shrink dual-in-line package (SDIP)

- Specific features of the MC68HC908AP64 in 42-pin SDIP are:

- 30 general-purpose I/Os only

- External interrupt on IRQ1 only

#### Features of the CPU08 include the following:

- Enhanced HC05 programming model

- Extensive loop control functions

- 16 addressing modes (eight more than the HC05)

- 16-bit Index register and stack pointer

- Memory-to-memory data transfers

- Fast 8 × 8 multiply instruction

- Fast 16/8 divide instruction

- Binary-coded decimal (BCD) instructions

- Optimization for controller applications

- Efficient C language support

# 1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68HC908AP64.

#### **General Description**

Table 1-2. Pin Functions

| PIN NAME                 | PIN DESCRIPTION                                                                                                            | IN/OUT | VOLTAGE<br>LEVEL |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------|--------|------------------|

|                          | 8-bit general purpose I/O port; PTB0–PTB3 are open drain when configured as output. PTB4–PTB7 have schmitt trigger inputs. | In/Out | V <sub>DD</sub>  |

|                          | PTB0 as SDA of MMIIC.                                                                                                      | In/Out | V <sub>DD</sub>  |

| PTB0/SDA<br>PTB1/SCL     | PTB1 as SCL of MMIIC.                                                                                                      | In/Out | V <sub>DD</sub>  |

| PTB2/TxD<br>PTB3/RxD     | PTB2 as TxD of SCI; open drain output.                                                                                     | Out    | V <sub>DD</sub>  |

| PTB4/T1CH0               | PTB3 as RxD of SCI.                                                                                                        | In     | V <sub>DD</sub>  |

| PTB5/T1CH1<br>PTB6/T2CH0 | PTB4 as T1CH0 of TIM1.                                                                                                     | In/Out | V <sub>DD</sub>  |

| PTB7/T2CH1               | PTB5 as T1CH1 of TIM1.                                                                                                     | In/Out | V <sub>DD</sub>  |

|                          | PTB6 as T2CH0 of TIM2.                                                                                                     | In/Out | V <sub>DD</sub>  |

|                          | PTB7 as T2CH1 of TIM2.                                                                                                     | In/Out | V <sub>DD</sub>  |

|                          | 8-bit general purpose I/O port; PTC6 and PTC7 are open drain when configured as output.                                    | In/Out | V <sub>DD</sub>  |

| PTC0/IRQ2                | PTC0 is shared with IRQ2 and has schmitt trigger input.                                                                    | In     | V <sub>DD</sub>  |

| PTC1<br>PTC2/MISO        | PTC2 as MISO of SPI.                                                                                                       | In     | V <sub>DD</sub>  |

| PTC3/MOSI                | PTC3 as MOSI of SPI.                                                                                                       | Out    | V <sub>DD</sub>  |

| PTC4/SS<br>PTC5/SPSCK    | PTC4 as $\overline{SS}$ of SPI.                                                                                            | In     | V <sub>DD</sub>  |

| PTC6/SCTxD<br>PTC7/SCRxD | PTC5 as SPSCK of SPI.                                                                                                      | In/Out | V <sub>DD</sub>  |

|                          | PTC6 as SCTxD of IRSCI; open drain output.                                                                                 | Out    | V <sub>DD</sub>  |

|                          | PTC7 as SCRxD of IRSCI.                                                                                                    | In     | V <sub>DD</sub>  |

| PTD0/KBI0                | 8-bit general purpose I/O port with schmitt trigger inputs.                                                                | In/Out | V <sub>DD</sub>  |

| :<br>PTD7/KBI7           | Pins as keyboard interrupts (with pullup), KBI0-KBI7.                                                                      | In     | V <sub>DD</sub>  |

<sup>1.</sup> See Chapter 22 Electrical Specifications for  $V_{\mbox{\scriptsize REG}}$  tolerance.

# 1.6 Power Supply Bypassing (VDD, VDDA, VSS, VSSA)

$V_{\text{DD}}$  and  $V_{\text{SS}}$  are the power supply and ground pins, the MCU operates from a single power supply together with an on chip voltage regulator.

Fast signal transitions on MCU pins place high. short-duration current demands on the power supply. To prevent noise problems, take special care to provide power supply bypassing at the MCU as Figure 1-5 shows. Place the bypass capacitors as close to the MCU power pins as possible. Use high-frequency-response ceramic capacitor for  $C_{BYPASS}$ ,  $C_{BULK}$  are optional bulk current bypass capacitors for use in applications that require the port pins to source high current level.

| Addr.  | Register Name                         |                 | Bit 7 | 6            | 5      | 4    | 3      | 2          | 1    | Bit 0  |

|--------|---------------------------------------|-----------------|-------|--------------|--------|------|--------|------------|------|--------|

| \$0036 | PLL Control Register<br>(PTCL)        | Read:<br>Write: | PLLIE | PLLF         | PLLON  | BCS  | PRE1   | PRE0       | VPR1 | VPR0   |

|        | (FTOL)                                | Reset:          | 0     | 0            | 1      | 0    | 0      | 0          | 0    | 0      |

|        | PLL Bandwidth Control                 | Read:           | AUTO  | LOCK         | ACQ    | 0    | 0      | 0          | 0    | R      |

| \$0037 | Register                              | Write:          | AUTO  |              | ACQ    |      |        |            |      | n      |

|        | (PBWC)                                | Reset:          | 0     | 0            | 0      | 0    | 0      | 0          | 0    |        |

|        | PLL Multiplier Select                 | Read:           | 0     | 0            | 0      | 0    | MUL11  | MUL10      | MUL9 | MUL8   |

| \$0038 | Register High                         | Write:          |       |              |        |      | WIOLII | INIOLIO    | MOL9 | IVIULO |

|        | (PMSH)                                | Reset:          | 0     | 0            | 0      | 0    | 0      | 0          | 0    | 0      |

| \$0039 | PLL Multiplier Select<br>Register Low | Read:<br>Write: | MUL7  | MUL6         | MUL5   | MUL4 | MUL3   | MUL2       | MUL1 | MUL0   |

|        | (PMSL)                                | Reset:          | 0     | 1            | 0      | 0    | 0      | 0          | 0    | 0      |

| \$003A | PLL VCO Range Select<br>Register      | Read:<br>Write: | VRS7  | VRS6         | VRS5   | VRS4 | VRS3   | VRS2       | VRS1 | VRS0   |

|        | (PMRS)                                | Reset:          | 0     | 1            | 0      | 0    | 0      | 0          | 0    | 0      |

|        | PLL Reference Divider                 | Read:           | 0     | 0            | 0      | 0    | RDS3   | RDS2       | RDS1 | DDC0   |

| \$003B | Select Register                       | Write:          |       |              |        |      | นบอง   | ND92       | ופטא | RDS0   |

|        | (PMDS)                                | Reset:          | 0     | 0            | 0      | 0    | 0      | 0          | 0    | 1      |

|        |                                       |                 |       | ] = Unimpler | mented |      | R      | = Reserved |      |        |

#### NOTES:

- 1. When AUTO = 0, PLLIE is forced clear and is read-only.

- 2. When AUTO = 0, PLLF and LOCK read as clear.

- 3. When AUTO = 1,  $\overline{ACQ}$  is read-only.

- 4. When PLLON = 0 or VRS7:VRS0 = \$0, BCS is forced clear and is read-only.

- 5. When PLLON = 1, the PLL programming register is read-only.

- 6. When BCS = 1, PLLON is forced set and is read-only.

Figure 6-2. CGM I/O Register Summary

#### 6.3.1 Oscillator Module

The oscillator module provides two clock outputs CGMXCLK and CGMRCLK to the CGM module. CGMXCLK when selected, is driven to SIM module to generate the system bus clock. CGMRCLK is used by the phase-lock-loop to provide a higher frequency system bus clock. The oscillator module also provides the reference clock for the timebase module (TBM). See Chapter 5 Oscillator (OSC) for detailed oscillator circuit description. See Chapter 10 Timebase Module (TBM) for detailed description on TBM.

# 6.3.2 Phase-Locked Loop Circuit (PLL)

The PLL is a frequency generator that can operate in either acquisition mode or tracking mode, depending on the accuracy of the output frequency. The PLL can change between acquisition and tracking modes either automatically or manually.

#### 6.3.3 PLL Circuits

The PLL consists of these circuits:

- Voltage-controlled oscillator (VCO)

- Reference divider

- Frequency pre-scaler

- Modulo VCO frequency divider

MC68HC908AP Family Data Sheet, Rev. 4

During the software execution, it does not consume any dedicated RAM location, the run-time heap will extend the system stack, all other RAM location will not be affected.

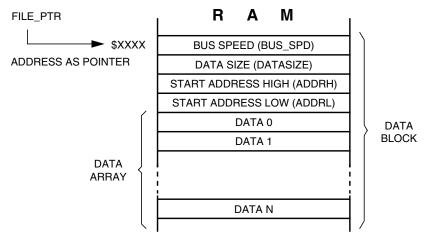

Figure 8-9. Data Block Format for ROM-Resident Routines

The control and data bytes are described below.

- **Bus speed** This one byte indicates the operating bus speed of the MCU. The value of this byte should be equal to 4 times the bus speed. E.g., for a 4MHz bus, the value is 16 (\$10). This control byte is useful where the MCU clock source is switched between the PLL clock and the crystal clock.

- Data size This one byte indicates the number of bytes in the data array that are to be

manipulated. The maximum data array size is 255. Routines EE\_WRITE and EE\_READ are

restricted to manipulate a data array between 7 to 15 bytes. Whereas routines ERARNGE and

MON\_ERARNGE do not manipulate a data array, thus, this data size byte has no meaning.

- **Start address** These two bytes, high byte followed by low byte, indicate the start address of the FLASH memory to be manipulated.

- **Data array** This data array contains data that are to be manipulated. Data in this array are programmed to FLASH memory by the programming routines: PRGRNGE, MON\_PRGRNGE, EE\_WRITE. For the read routines: LDRNGE and EE\_READ, data is read from FLASH and stored in this array.

## 8.5.1 PRGRNGE

PRGRNGE is used to program a range of FLASH locations with data loaded into the data array.

| Routine Name        | PRGRNGE                                                                                                                   |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Routine Description | Program a range of locations                                                                                              |  |  |  |

| Calling Address     | \$FC34                                                                                                                    |  |  |  |

| Stack Used          | 15 bytes                                                                                                                  |  |  |  |

| Data Block Format   | Bus speed (BUS_SPD) Data size (DATASIZE) Start address high (ADDRH) Start address (ADDRL) Data 1 (DATA1) : Data N (DATAN) |  |  |  |

**Table 8-11. PRGRNGE Routine**

MC68HC908AP Family Data Sheet, Rev. 4

## 9.9.2 TIM Counter Registers

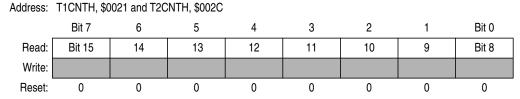

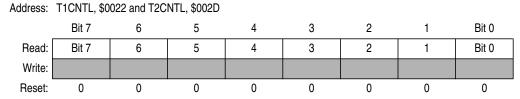

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

#### NOTE

If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

Figure 9-5. TIM Counter Registers High (TCNTH)

Figure 9-6. TIM Counter Registers Low (TCNTL)

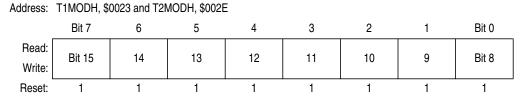

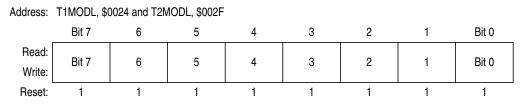

## 9.9.3 TIM Counter Modulo Registers

The read/write TIM modulo registers contain the modulo value for the TIM counter. When the TIM counter reaches the modulo value, the overflow flag (TOF) becomes set, and the TIM counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (TMODH) inhibits the TOF bit and overflow interrupts until the low byte (TMODL) is written. Reset sets the TIM counter modulo registers.

Figure 9-7. TIM Counter Modulo Register High (TMODH)

Figure 9-8. TIM Counter Modulo Register Low (TMODL)

## **NOTE**

Reset the TIM counter before writing to the TIM counter modulo registers.

MC68HC908AP Family Data Sheet, Rev. 4

#### **Timer Interface Module (TIM)**

#### NOTE

Before enabling a TIM channel register for input capture operation, make sure that the TCHx pin is stable for at least two bus clocks.

## **TOVx** — Toggle On Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the TIM counter overflows. When channel x is an input capture channel, TOVx has no effect.

Reset clears the TOVx bit.

- 1 = Channel x pin toggles on TIM counter overflow

- 0 = Channel x pin does not toggle on TIM counter overflow

#### NOTE

When TOVx is set, a TIM counter overflow takes precedence over a channel x output compare if both occur at the same time.

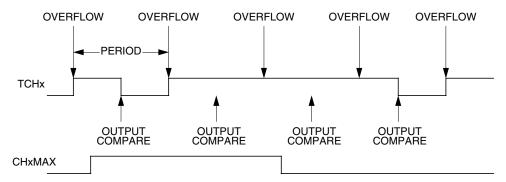

## CHxMAX — Channel x Maximum Duty Cycle Bit

When the TOVx bit is at logic 1, setting the CHxMAX bit forces the duty cycle of buffered and unbuffered PWM signals to 100%. As Figure 9-11 shows, the CHxMAX bit takes effect in the cycle after it is set or cleared. The output stays at the 100% duty cycle level until the cycle after CHxMAX is cleared.

Figure 9-11. CHxMAX Latency

## 9.9.5 TIM Channel Registers

These read/write registers contain the captured TIM counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

## TBR[2:0] — Timebase Rate Selection

These read/write bits are used to select the rate of timebase interrupts as shown in Table 10-1.

#### NOTE

Do not change TBR[2:0] bits while the timebase is enabled (TBON = 1).

Table 10-1. Timebase Rate Selection for OSCCLK = 32.768-kHz

| TBR2 | TBR1 | TBR0 | Divider | Timebase I | nterrupt Rate |

|------|------|------|---------|------------|---------------|

| IBNZ | IBNI | IBNU | Dividei | Hz         | ms            |

| 0    | 0    | 0    | 262144  | 0.125      | 8000          |

| 0    | 0    | 1    | 131072  | 0.25       | 4000          |

| 0    | 1    | 0    | 65536   | 0.5        | 2000          |

| 0    | 1    | 1    | 32768   | 1          | 1000          |

| 1    | 0    | 0    | 64      | 512        | ~2            |

| 1    | 0    | 1    | 32      | 1024       | ~1            |

| 1    | 1    | 0    | 16      | 2048       | ~0.5          |

| 1    | 1    | 1    | 8       | 4096       | ~0.24         |

## TACK — Timebase ACKnowledge

The TACK bit is a write-only bit and always reads as 0. Writing a logic 1 to this bit clears TBIF, the timebase interrupt flag bit. Writing a logic 0 to this bit has no effect.

- 1 = Clear timebase interrupt flag

- 0 = No effect

## TBIE — Timebase Interrupt Enabled

This read/write bit enables the timebase interrupt when the TBIF bit becomes set. Reset clears the TBIF bit

- 1 = Timebase interrupt enabled

- 0 = Timebase interrupt disabled

## **TBON** — Timebase Enabled

This read/write bit enables the timebase. Timebase may be turned off to reduce power consumption when its function is not necessary. The counter can be initialized by clearing and then setting this bit. Reset clears the TBON bit.

- 1 = Timebase enabled

- 0 = Timebase disabled and the counter initialized to 0's

#### **Serial Communications Interface Module (SCI)**

#### 11.4.2.4 Idle Characters

An idle character contains all logic 1s and has no start, stop, or parity bit. Idle character length depends on the M bit in SCC1. The preamble is a synchronizing idle character that begins every transmission.

If the TE bit is cleared during a transmission, the TxD pin becomes idle after completion of the transmission in progress. Clearing and then setting the TE bit during a transmission queues an idle character to be sent after the character currently being transmitted.

#### NOTE

When queueing an idle character, return the TE bit to logic 1 before the stop bit of the current character shifts out to the TxD pin. Setting TE after the stop bit appears on TxD causes data previously written to the SCDR to be lost.

Toggle the TE bit for a queued idle character when the SCTE bit becomes set and just before writing the next byte to the SCDR.

## 11.4.2.5 Inversion of Transmitted Output

The transmit inversion bit (TXINV) in SCI control register 1 (SCC1) reverses the polarity of transmitted data. All transmitted values, including idle, break, start, and stop bits, are inverted when TXINV is at logic 1. (See 11.8.1 SCI Control Register 1.)

## 11.4.2.6 Transmitter Interrupts

These conditions can generate CPU interrupt requests from the SCI transmitter:

- SCI transmitter empty (SCTE) The SCTE bit in SCS1 indicates that the SCDR has transferred

a character to the transmit shift register. SCTE can generate a transmitter CPU interrupt request.

Setting the SCI transmit interrupt enable bit, SCTIE, in SCC2 enables the SCTE bit to generate

transmitter CPU interrupt requests.

- Transmission complete (TC) The TC bit in SCS1 indicates that the transmit shift register and the SCDR are empty and that no break or idle character has been generated. The transmission complete interrupt enable bit, TCIE, in SCC2 enables the TC bit to generate transmitter CPU interrupt requests.

#### 11.4.3 Receiver

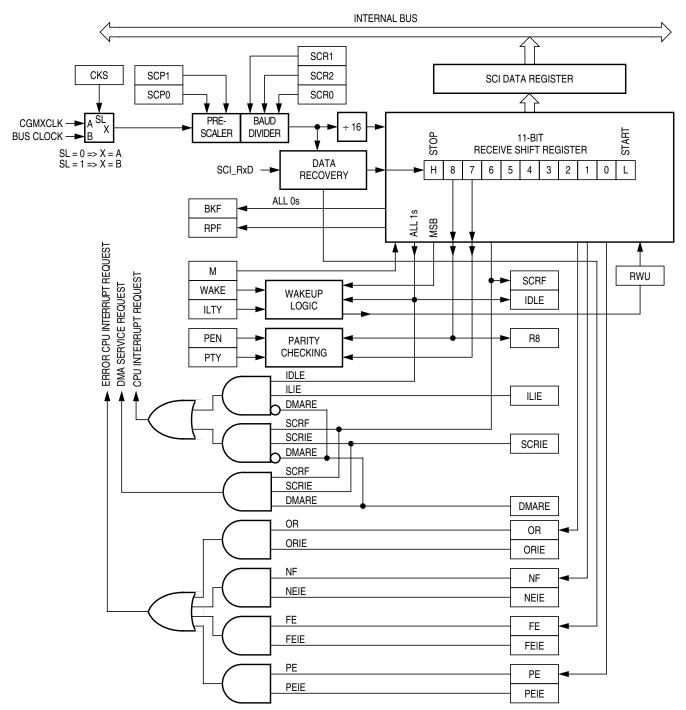

Figure 11-5 shows the structure of the SCI receiver.

## 11.4.3.1 Character Length

The receiver can accommodate either 8-bit or 9-bit data. The state of the M bit in SCI control register 1 (SCC1) determines character length. When receiving 9-bit data, bit R8 in SCI control register 2 (SCC2) is the ninth bit (bit 8). When receiving 8-bit data, bit R8 is a copy of the eighth bit (bit 7).

#### 11.4.3.2 Character Reception

During an SCI reception, the receive shift register shifts characters in from the RxD pin. The SCI data register (SCDR) is the read-only buffer between the internal data bus and the receive shift register.

After a complete character shifts into the receive shift register, the data portion of the character transfers to the SCDR. The SCI receiver full bit, SCRF, in SCI status register 1 (SCS1) becomes set, indicating that

MC68HC908AP Family Data Sheet, Rev. 4

Start bit verification is not successful if any two of the three verification samples are logic 1s. If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 11-3 summarizes the results of the data bit samples.

**Table 11-3. Data Bit Recovery**

| RT8, RT9, and RT10<br>Samples | Data Bit<br>Determination | Noise Flag |

|-------------------------------|---------------------------|------------|

| 000                           | 0                         | 0          |

| 001                           | 0                         | 1          |

| 010                           | 0                         | 1          |

| 011                           | 1                         | 1          |

| 100                           | 0                         | 1          |

| 101                           | 1                         | 1          |

| 110                           | 1                         | 1          |

| 111                           | 1                         | 0          |

## NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are logic 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit.

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 11-4 summarizes the results of the stop bit samples.

**Table 11-4. Stop Bit Recovery**

| RT8, RT9, and RT10<br>Samples | Framing<br>Error Flag | Noise Flag |

|-------------------------------|-----------------------|------------|

| 000                           | 1                     | 0          |

| 001                           | 1                     | 1          |

| 010                           | 1                     | 1          |

| 011                           | 0                     | 1          |

| 100                           | 1                     | 1          |

| 101                           | 0                     | 1          |

| 110                           | 0                     | 1          |

| 111                           | 0                     | 0          |

MC68HC908AP Family Data Sheet, Rev. 4

## Infrared Serial Communications Interface Module (IRSCI)

Figure 12-8. SCI Receiver Block Diagram

## 12.5.3.1 Character Length

The receiver can accommodate either 8-bit or 9-bit data. The state of the M bit in IRSCI control register 1 (IRSCC1) determines character length. When receiving 9-bit data, bit R8 in IRSCI control register 2 (IRSCC2) is the ninth bit (bit 8). When receiving 8-bit data, bit R8 is a copy of the eighth bit (bit 7).

MC68HC908AP Family Data Sheet, Rev. 4

**Infrared Serial Communications Interface Module (IRSCI)**

**Table 12-2. Start Bit Verification**

| RT3, RT5, and RT7<br>Samples | Start Bit<br>Verification | Noise Flag |

|------------------------------|---------------------------|------------|

| 011                          | No                        | 0          |

| 100                          | Yes                       | 1          |

| 101                          | No                        | 0          |

| 110                          | No                        | 0          |

| 111                          | No                        | 0          |

If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 12-3 summarizes the results of the data bit samples.

**Table 12-3. Data Bit Recovery**

| RT8, RT9, and RT10<br>Samples | Data Bit<br>Determination | Noise Flag |

|-------------------------------|---------------------------|------------|

| 000                           | 0                         | 0          |

| 001                           | 0                         | 1          |

| 010                           | 0                         | 1          |

| 011                           | 1                         | 1          |

| 100                           | 0                         | 1          |

| 101                           | 1                         | 1          |

| 110                           | 1                         | 1          |

| 111                           | 1                         | 0          |

#### NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are logic 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit.

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 12-4 summarizes the results of the stop bit samples.

Table 12-4. Stop Bit Recovery

| RT8, RT9, and RT10<br>Samples | Framing<br>Error Flag | Noise Flag |

|-------------------------------|-----------------------|------------|

| 000                           | 1                     | 0          |

| 001                           | 1                     | 1          |

MC68HC908AP Family Data Sheet, Rev. 4

- The shift register is cleared.

- The SPI state counter is cleared, making it ready for a new complete transmission.

- All the SPI port logic is defaulted back to being general-purpose I/O.

These items are reset only by a system reset:

- All control bits in the SPCR register

- All control bits in the SPSCR register (MODFEN, ERRIE, SPR1, and SPR0)

- The status flags SPRF, OVRF, and MODF

By not resetting the control bits when SPE is low, the user can clear SPE between transmissions without having to set all control bits again when SPE is set back high for the next transmission.

By not resetting the SPRF, OVRF, and MODF flags, the user can still service these interrupts after the SPI has been disabled. The user can disable the SPI by writing 0 to the SPE bit. The SPI can also be disabled by a mode fault occurring in an SPI that was configured as a master with the MODFEN bit set.

## 13.10 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 13.10.1 Wait Mode

The SPI module remains active after the execution of a WAIT instruction. In wait mode the SPI module registers are not accessible by the CPU. Any enabled CPU interrupt request from the SPI module can bring the MCU out of wait mode.

If SPI module functions are not required during wait mode, reduce power consumption by disabling the SPI module before executing the WAIT instruction.

To exit wait mode when an overflow condition occurs, enable the OVRF bit to generate CPU interrupt requests by setting the error interrupt enable bit (ERRIE). (See 13.8 Interrupts.)

## 13.10.2 Stop Mode

The SPI module is inactive after the execution of a STOP instruction. The STOP instruction does not affect register conditions. SPI operation resumes after an external interrupt. If stop mode is exited by reset, any transfer in progress is aborted, and the SPI is reset.

# 13.11 SPI During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear status bits during the break state. (See Chapter 7 System Integration Module (SIM).)

To allow software to clear status bits during a break interrupt, write a logic 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a 2-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at logic 0. After the break, doing the second step clears the status bit.

MC68HC908AP Family Data Sheet, Rev. 4

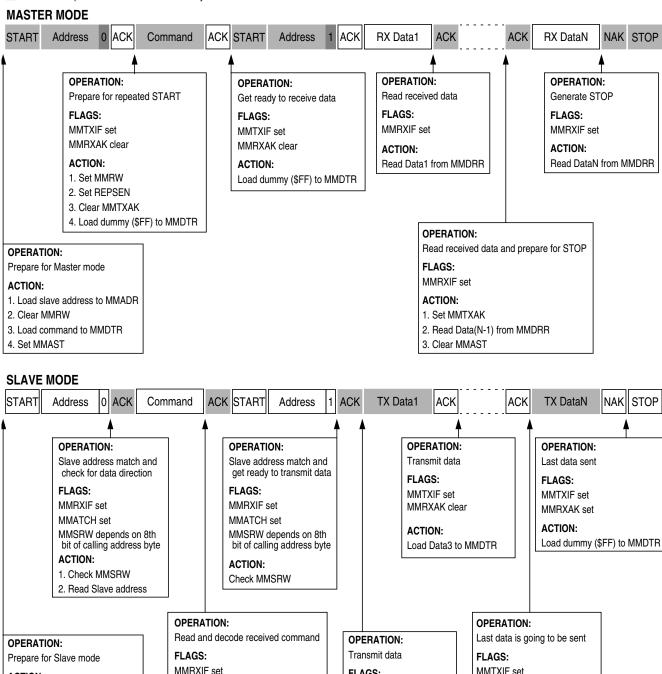

**ACTION:**

2. Clear MMTXAK

3. Clear MMAST

1. Load slave address to MMADR

Multi-Master IIC Interface (MMIIC)

# 14.9 SMBus Protocol Implementation

Shaded data packets indicate transmissions by the MCU

Figure 14-20. SMBus Protocol Implementation

MMATCH clear

Load Data1 to MMDTR

ACTION:

FLAGS:

ACTION:

MMTXIF set

Load Data2 to MMDTR

MMRXAK clear

Load dummy (\$FF) to MMDTR

ACTION:

MC68HC908AP Family Data Sheet, Rev. 4

# Chapter 17 External Interrupt (IRQ)

## 17.1 Introduction

The external interrupt (IRQ) module provides two maskable interrupt inputs: IRQ1 and IRQ2.

## 17.2 Features

Features of the IRQ module include:

- A dedicated external interrupt pin, IRQ1

- An external interrupt pin shared with a port pin, PTC0/IRQ2

- Separate IRQ interrupt control bits for IRQ1 and IRQ2

- Hysteresis buffers

- Programmable edge-only or edge and level interrupt sensitivity

- Automatic interrupt acknowledge

- Internal pullup resistor, with disable option on IRQ2

#### NOTE

References to either IRQ1 or IRQ2 may be made in the following text by omitting the IRQ number. For example, IRQF may refer generically to IRQ1F and IRQ2F, and IMASK may refer to IMASK1 and IMASK2.

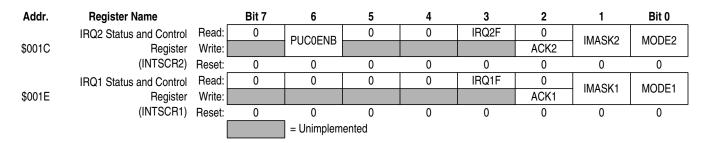

Figure 17-1. External Interrupt I/O Register Summary

# 17.3 Functional Description

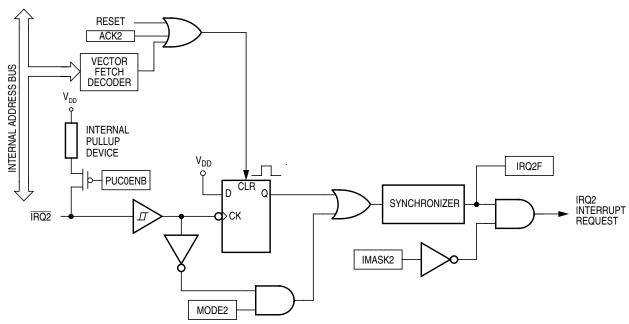

A logic 0 applied to the external interrupt pin can latch a CPU interrupt request. Figure 17-2 and Figure 17-3 shows the structure of the IRQ module.

Interrupt signals on the IRQ pin are latched into the IRQ latch. An interrupt latch remains set until one of the following actions occurs:

• Vector fetch — A vector fetch automatically generates an interrupt acknowledge signal that clears the latch that caused the vector fetch.

Figure 17-3. IRQ2 Block Diagram

# 17.4 IRQ1 and IRQ2 Pins

A logic 0 on the  $\overline{IRQ}$  pin can latch an interrupt request into the IRQ latch. A vector fetch, software clear, or reset clears the IRQ latch.

If the MODE bit is set, the  $\overline{IRQ}$  pin is both falling-edge-sensitive and low-level-sensitive. With MODE set, both of the following actions must occur to clear IRQ:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the latch. Software may generate the interrupt acknowledge signal by writing a logic 1 to the ACK bit in the interrupt status and control register (INTSCR). The ACK bit is useful in applications that poll the  $\overline{\text{IRQ}}$  pin and require software to clear the IRQ latch. Writing to the ACK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACK does not affect subsequent transitions on the  $\overline{\text{IRQ}}$  pin. A falling edge that occurs after writing to the ACK bit another interrupt request. If the IRQ mask bit, IMASK, is clear, the CPU loads the program counter with the vector address at location defined in Table 2-1. Vector Addresses.

- Return of the IRQ pin to logic 1 As long as the IRQ pin is at logic 0, IRQ remains active.

The vector fetch or software clear and the return of the  $\overline{IRQ}$  pin to logic 1 may occur in any order. The interrupt request remains pending as long as the  $\overline{IRQ}$  pin is at logic 0. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

If the MODE bit is clear, the  $\overline{IRQ}$  pin is falling-edge-sensitive only. With MODE clear, a vector fetch or software clear immediately clears the IRQ latch.

The IRQF bit in the INTSCR register can be used to check for pending interrupts. The IRQF bit is not affected by the IMASK bit, which makes it useful in applications where polling is preferred.

Use the BIH or BIL instruction to read the logic level on the IRQ1 pin.

#### NOTE

The BIH and BIL instructions do not read the logic level on the  $\overline{IRQ2}$  pin.

MC68HC908AP Family Data Sheet, Rev. 4

#### **External Interrupt (IRQ)**

#### NOTE

When using the level-sensitive interrupt trigger, avoid false interrupts by masking interrupt requests in the interrupt routine.

The  $\overline{IRQ1}$  pin has a permanent internal pullup device connected, while the  $\overline{IRQ2}$  pin has an optional pullup device that can be enabled or disabled by the PUC0ENB bit in the INTSCR2 register.

# 17.5 IRQ Module During Break Interrupts

The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear the latch during the break state. (See Chapter 21 Break Module (BRK).)

To allow software to clear the IRQ latch during a break interrupt, write a logic 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect CPU interrupt flags during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), writing to the ACK bit in the IRQ status and control register during the break state has no effect on the IRQ interrupt flags.

# 17.6 IRQ Registers

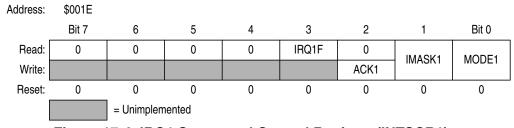

Each IRQ is controlled and monitored by an status and control register.

- IRQ1 Status and Control Register \$001E

- IRQ2 Status and Control Register \$001C

## 17.6.1 IRQ1 Status and Control Register

The IRQ1 status and control register (INTSCR1) controls and monitors operation of IRQ1. The INTSCR1 has the following functions:

- Shows the state of the IRQ1 flag

- Clears the IRQ1 latch

- Masks IRQ1 interrupt request

- Controls triggering sensitivity of the IRQ1 interrupt pin

Figure 17-4. IRQ1 Status and Control Register (INTSCR1)

## IRQ1F — IRQ1 Flag Bit

This read-only status bit is high when the IRQ1 interrupt is pending.

- $1 = \overline{IRQ1}$  interrupt pending

- $0 = \overline{IRQ1}$  interrupt not pending

## ACK1 — IRQ1 Interrupt Request Acknowledge Bit

Writing a logic 1 to this write-only bit clears the IRQ1 latch. ACK1 always reads as logic 0. Reset clears ACK1.

MC68HC908AP Family Data Sheet, Rev. 4

## 18.6 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 18.6.1 Wait Mode

The keyboard interrupt module remains active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

## **18.6.2 Stop Mode**

The keyboard interrupt module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

# 18.7 Keyboard Module During Break Interrupts

The system integration module (SIM) controls whether the keyboard interrupt latch can be cleared during the break state. The BCFE bit in the SIM break flag control register (BFCR) enables software to clear status bits during the break state.

To allow software to clear the keyboard interrupt latch during a break interrupt, write a logic 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latch during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect.

MC68HC908AP Family Data Sheet, Rev. 4 Freescale Semiconductor 281

## **Electrical Specifications**

# 22.8 5V ADC Electrical Characteristics

Table 22-7. ADC Electrical Characteristics (5 V)

| Characteristic <sup>(1)</sup>        | Symbol            | Min                    | Max                    | Unit                        | Notes                                                                                           |

|--------------------------------------|-------------------|------------------------|------------------------|-----------------------------|-------------------------------------------------------------------------------------------------|

| Supply voltage                       | V <sub>DDA</sub>  | 4.5                    | 5.5                    | V                           | $V_{DDA}$ is an dedicated pin and should be tied to $V_{DD}$ on the PCB with proper decoupling. |

| Input range                          | V <sub>ADIN</sub> | 0                      | V <sub>DDA</sub>       | V                           | $V_{ADIN} \le V_{DDA}$                                                                          |

| Resolution                           | B <sub>AD</sub>   | 10                     | 10                     | bits                        |                                                                                                 |

| Absolute accuracy                    | A <sub>AD</sub>   | _                      | ± 1.5                  | LSB                         | Includes quantization.<br>±0.5 LSB = ±1 ADC step.                                               |

| ADC internal clock                   | f <sub>ADIC</sub> | 500k                   | 1.048M                 | Hz                          | $t_{ADIC} = 1/f_{ADIC}$                                                                         |

| Conversion range                     | R <sub>AD</sub>   | V <sub>REFL</sub>      | V <sub>REFH</sub>      | V                           |                                                                                                 |

| ADC voltage reference high           | V <sub>REFH</sub> | _                      | V <sub>DDA</sub> + 0.1 | V                           |                                                                                                 |

| ADC voltage reference low            | V <sub>REFL</sub> | V <sub>SSA</sub> – 0.1 | _                      | V                           |                                                                                                 |

| Conversion time                      | t <sub>ADC</sub>  | 16                     | 17                     | t <sub>ADIC</sub> cycles    |                                                                                                 |

| Sample time                          | t <sub>ADS</sub>  | 5                      | _                      | t <sub>ADIC</sub><br>cycles |                                                                                                 |

| Monotonicity                         | M <sub>AD</sub>   |                        | Guaranteed             | •                           |                                                                                                 |

| Zero input reading                   | Z <sub>ADI</sub>  | 000                    | 001                    | HEX                         | V <sub>ADIN</sub> = V <sub>REFL</sub>                                                           |

| Full-scale reading                   | F <sub>ADI</sub>  | 3FD                    | 3FF                    | HEX                         | V <sub>ADIN</sub> = V <sub>REFH</sub>                                                           |

| Input capacitance                    | C <sub>ADI</sub>  | _                      | 20                     | pF                          | Not tested.                                                                                     |

| Input impedance                      | R <sub>ADI</sub>  | 20M                    | _                      | Ω                           |                                                                                                 |

| V <sub>REFH</sub> /V <sub>REFL</sub> | I <sub>VREF</sub> | _                      | 1.6                    | mA                          | Not tested.                                                                                     |

<sup>1.</sup>  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

## **Electrical Specifications**

## 22.15 5V SPI Characteristics

Table 22-15. SPI Characteristics (5V)

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                        | Symbol                                   | Min                                              | Max                                   | Unit             |

|----------------------------------|----------------------------------------------------------------------|------------------------------------------|--------------------------------------------------|---------------------------------------|------------------|

|                                  | Operating frequency Master Slave                                     | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub> | f <sub>OP</sub> /128<br>dc                       | f <sub>OP</sub> /2<br>f <sub>OP</sub> | MHz<br>MHz       |

| 1                                | Cycle time<br>Master<br>Slave                                        | t <sub>CYC(M)</sub> t <sub>CYC(S)</sub>  | 2<br>1                                           | 128<br>—                              | t <sub>CYC</sub> |

| 2                                | Enable lead time                                                     | t <sub>Lead(S)</sub>                     | 1                                                | _                                     | t <sub>CYC</sub> |

| 3                                | Enable lag time                                                      | t <sub>Lag(S)</sub>                      | 1                                                | _                                     | t <sub>CYC</sub> |

| 4                                | Clock (SPSCK) high time<br>Master<br>Slave                           | t <sub>SCKH(M)</sub>                     | t <sub>CYC</sub> -25<br>1/2 t <sub>CYC</sub> -25 | 64 t <sub>CYC</sub>                   | ns<br>ns         |

| 5                                | Clock (SPSCK) low time<br>Master<br>Slave                            | t <sub>SCKL(M)</sub>                     | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns         |

| 6                                | Data setup time (inputs) Master Slave                                | t <sub>SU(M)</sub>                       | 30<br>30                                         |                                       | ns<br>ns         |

| 7                                | Data hold time (inputs) Master Slave                                 | t <sub>H(M)</sub>                        | 30<br>30                                         | _<br>_                                | ns<br>ns         |

| 8                                | Access time, slave <sup>(3)</sup> CPHA = 0 CPHA = 1                  | t <sub>A(CP0)</sub>                      | 0                                                | 40<br>40                              | ns<br>ns         |

| 9                                | Disable time, slave <sup>(4)</sup>                                   | t <sub>DIS(S)</sub>                      | _                                                | 40                                    | ns               |

| 10                               | Data valid time, after enable edge<br>Master<br>Slave <sup>(5)</sup> | t <sub>V(M)</sub>                        |                                                  | 50<br>50                              | ns<br>ns         |

| 11                               | Data hold time, outputs, after enable edge<br>Master<br>Slave        | t <sub>HO(M)</sub>                       | 0<br>0                                           |                                       | ns<br>ns         |

Numbers refer to dimensions in Figure 22-3 and Figure 22-4.

All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins.

Time to data active from high-impedance state

Hold time to high-impedance state

With 100 pF on all SPI pins