# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | HC08                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IRSCI, SCI, SPI                                        |

| Peripherals                | LED, LVD, POR, PWM                                                       |

| Number of I/O              | 32                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 2K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-QFP                                                                   |

| Supplier Device Package    | 44-QFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908ap32cfb |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

\_\_\_\_\_

#### **Monitor ROM**

| Addr.  | Register Name                          |        | Bit 7        | 6       | 5       | 4          | 3       | 2       | 1          | Bit 0     |

|--------|----------------------------------------|--------|--------------|---------|---------|------------|---------|---------|------------|-----------|

|        | MMIIC Data Receive                     | Read:  | MMRD7        | MMRD6   | MMRD5   | MMRD4      | MMRD3   | MMRD2   | MMRD1      | MMRD0     |

| \$004D | Register                               | Write: |              |         |         |            |         |         |            |           |

|        | (MMDRR)                                | Reset: | 0            | 0       | 0       | 0          | 0       | 0       | 0          | 0         |

|        | MMIIC CRC Data Register                | Read:  | MMCRCD7      | MMCRCD6 | MMCRCD5 | MMCRCD4    | MMCRCD3 | MMCRCD2 | MMCRCD1    | MMCRCD0   |

| \$004E | (MMCRDR)                               | Write: |              |         |         |            |         |         |            |           |

|        |                                        | Reset: | 0            | 0       | 0       | 0          | 0       | 0       | 0          | 0         |

|        | MMIIC Frequency Divider                | Read:  | 0            | 0       | 0       | 0          | 0       | MMBR2   | MMBR1      | MMBR0     |

| \$004F | Register                               | Write: |              |         |         |            |         |         | IVIIVIDNI  | IVIIVIDOU |

|        | (MMFDR)                                | Reset: | 0            | 0       | 0       | 0          | 0       | 1       | 0          | 0         |

|        |                                        | Read:  | R            | R       | Р       | р          | D       | р       | R          | R         |

| \$0050 | Reserved                               | Write: |              | n       | R       | R          | R       | R       | n          | n         |

|        |                                        | Reset: |              |         |         |            |         |         |            |           |

|        | Timebase Control Register              | Read:  | TBIF         | TBR2    | TBR1    | TBR0       | 0       | TBIE    | TBON       | R         |

| \$0051 | (TBCR)                                 | Write: |              | TDNZ    | IDNI    | IDNU       | TACK    | IDE     | TBON       | n         |

|        |                                        | Reset: | 0            | 0       | 0       | 0          | 0       | 0       | 0          | 0         |

|        |                                        | Read:  |              |         |         |            |         |         |            |           |

| \$0052 | Unimplemented                          | Write: |              |         |         |            |         |         |            |           |

|        |                                        | Reset: |              |         |         |            |         |         |            |           |

|        |                                        | Read:  |              |         |         |            |         |         |            |           |

| \$0053 | Unimplemented                          | Write: |              |         |         |            |         |         |            |           |

|        |                                        | Reset: |              |         |         |            |         |         |            |           |

|        |                                        | Read:  |              |         |         |            |         |         |            |           |

| \$0054 | Unimplemented                          | Write: |              |         |         |            |         |         |            |           |

|        |                                        | Reset: |              |         |         |            |         |         |            |           |

|        |                                        | Read:  |              |         |         |            |         |         |            |           |

| \$0055 | Unimplemented                          | Write: |              |         |         |            |         |         |            |           |

|        |                                        | Reset: |              |         |         |            |         |         |            |           |

|        |                                        | Read:  |              |         |         |            |         |         |            |           |

| \$0056 | Unimplemented                          | Write: |              |         |         |            |         |         |            |           |

|        |                                        | Reset: |              |         |         |            |         |         |            |           |

|        | ADC Status and Control                 | Read:  | 0000         |         | ADCO    | ADCH4      | ADCH3   | ADCH2   |            | ADCH0     |

| \$0057 | Register                               | Write: |              | AIEN    | ADCO    | ADCH4      | ADCH3   | ADCHZ   | ADCH1      | ADCHU     |

|        | (ADSCR)                                | Reset: | 0            | 0       | 0       | 1          | 1       | 1       | 1          | 1         |

|        |                                        | Read:  |              |         |         |            |         | MODEO   | 0          | 0         |

| \$0058 | ADC Clock Control Register<br>(ADICLK) | Write: | ADIV2        | ADIV1   | ADIV0   | ADICLK     | MODE1   | MODE0   |            | R         |

|        |                                        | Reset: | 0            | 0       | 0       | 0          | 0       | 0       | 0          | 0         |

|        |                                        | Read:  | ADx          | ADx     | ADx     | ADx        | ADx     | ADx     | ADx        | ADx       |

| \$0059 | ADC Data Register High 0<br>(ADRH0)    | Write: | R            | R       | R       | R          | R       | R       | R          | R         |

|        | (סוווישה)                              | Reset: | 0            | 0       | 0       | 0          | 0       | 0       | 0          | 0         |

|        | U = Unaffected                         |        | X = Indeterm | inate   |         | = Unimplem | ented   | R       | = Reserved |           |

Figure 2-2. Control, Status, and Data Registers (Sheet 7 of 9)

**Central Processor Unit (CPU)**

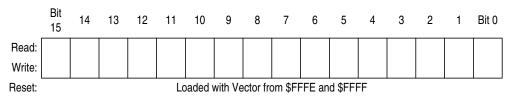

Figure 4-5. Program Counter (PC)

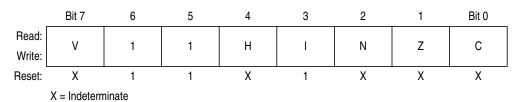

# 4.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to logic 1. The following paragraphs describe the functions of the condition code register.

Figure 4-6. Condition Code Register (CCR)

### V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

1 = Overflow

0 = No overflow

### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

1 = Carry between bits 3 and 4

0 = No carry between bits 3 and 4

### I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

1 = Interrupts disabled

0 = Interrupts enabled

### NOTE

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

| Source                                                                                         | Operation                                            | Description                                                  |   | E |   | ct (<br>CR |   |   | Address<br>Mode                                                                              | Opcode                                           | Operand                                            | Cycles                               |

|------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------|---|---|---|------------|---|---|----------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|--------------------------------------|

| Form                                                                                           |                                                      |                                                              | v | н | I | Ν          | z | С | PdA                                                                                          | do                                               | Ope                                                | ටි                                   |

| AND #opr<br>AND opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND ,X<br>AND opr,SP<br>AND opr,SP | Logical AND                                          | A ← (A) & (M)                                                | 0 | _ | _ | 0          | o | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh ll<br>ee ff<br>ff<br>ee ff          | 2<br>3<br>4<br>3<br>2<br>4<br>5      |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL opr,SP                                   | Arithmetic Shift Left<br>(Same as LSL)               | C ← ← 0<br>b7 b0                                             | 0 | _ | _ | 0          | 0 | 0 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                     | 4<br>1<br>4<br>3<br>5                |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                | Arithmetic Shift Right                               |                                                              | o | _ | _ | 0          | 0 | o | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                                     | 4<br>1<br>4<br>3<br>5                |

| BCC rel                                                                                        | Branch if Carry Bit Clear                            | $PC \leftarrow (PC) + 2 + rel ? (C) = 0$                     | - | - | _ | -          | - | - | REL                                                                                          | 24                                               | rr                                                 | 3                                    |

| BCLR n, opr                                                                                    | Clear Bit n in M                                     | Mn ← 0                                                       | _ | _ | _ | _          | _ | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b5)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 |

| BCS rel                                                                                        | Branch if Carry Bit Set (Same as BLO)                | PC ← (PC) + 2 + <i>rel</i> ? (C) = 1                         | - | - | - | -          | - | - | REL                                                                                          | 25                                               | rr                                                 | 3                                    |

| BEQ rel                                                                                        | Branch if Equal                                      | PC ← (PC) + 2 + <i>rel</i> ? (Z) = 1                         | - | - | - | -          | - | - | REL                                                                                          | 27                                               | rr                                                 | 3                                    |

| BGE opr                                                                                        | Branch if Greater Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 0$   | - | - | - | -          | - | - | REL                                                                                          | 90                                               | rr                                                 | 3                                    |

| BGT opr                                                                                        | Branch if Greater Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel? (Z) \mid (N \oplus V) = 0$    | - | _ | _ | -          | - | - | REL                                                                                          | 92                                               | rr                                                 | 3                                    |

| BHCC rel                                                                                       | Branch if Half Carry Bit Clear                       | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (H) = 0$            | - | - | - | -          | - | - | REL                                                                                          | 28                                               | rr                                                 | 3                                    |

| BHCS rel                                                                                       | Branch if Half Carry Bit Set                         | PC ← (PC) + 2 + <i>rel</i> ? (H) = 1                         | - | - | - | -          | - | - | REL                                                                                          | 29                                               | rr                                                 | 3                                    |

| BHI <i>rel</i>                                                                                 | Branch if Higher                                     | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 0$   | - | - | - | -          | - | - | REL                                                                                          | 22                                               | rr                                                 | 3                                    |

| BHS rel                                                                                        | Branch if Higher or Same<br>(Same as BCC)            | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 0$            | - | _ | _ | _          | _ | - | REL                                                                                          | 24                                               | rr                                                 | 3                                    |

| BIH <i>rel</i>                                                                                 | Branch if IRQ Pin High                               | $PC \leftarrow (PC) + 2 + \mathit{rel} ? \overline{IRQ} = 1$ | - | _ | _ | -          | _ | - | REL                                                                                          | 2F                                               | rr                                                 | 3                                    |

| BIL <i>rel</i>                                                                                 | Branch if IRQ Pin Low                                | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 0$          | - | - | _ | -          | - | - | REL                                                                                          | 2E                                               | rr                                                 | 3                                    |

**Central Processor Unit (CPU)**

| Source                                                                                         | Operation                                            | Description                                                         |   | E |   | ct o<br>CR | on |   | Address<br>Mode                                                                                          | Opcode                                           | Operand                                                                       | Cycles                                                   |

|------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------|---|---|---|------------|----|---|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------|

| Form                                                                                           | •                                                    |                                                                     | v | н | I | Ν          | z  | С | Ado                                                                                                      | ŎĎ                                               | ope                                                                           | ଧି                                                       |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT ,X<br>BIT opr,SP<br>BIT opr,SP | Bit Test                                             | (A) & (M)                                                           | 0 | _ | _ | o          | o  | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                                      | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9EE5<br>9ED5 | ii<br>dd<br>hh ll<br>ee ff<br>ff<br>ee ff                                     | 2<br>3<br>4<br>3<br>2<br>4<br>5                          |

| BLE opr                                                                                        | Branch if Less Than or Equal To<br>(Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 1$ | - | _ | _ | -          | -  | - | REL                                                                                                      | 93                                               | rr                                                                            | 3                                                        |

| BLO rel                                                                                        | Branch if Lower (Same as BCS)                        | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 1$                   | - | - | - | -          | -  | - | REL                                                                                                      | 25                                               | rr                                                                            | 3                                                        |

| BLS rel                                                                                        | Branch if Lower or Same                              | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 1$          | - | - | - | -          | -  | - | REL                                                                                                      | 23                                               | rr                                                                            | 3                                                        |

| BLT opr                                                                                        | Branch if Less Than (Signed Operands)                | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 1$          | - | - | - | -          | -  | - | REL                                                                                                      | 91                                               | rr                                                                            | 3                                                        |

| BMC rel                                                                                        | Branch if Interrupt Mask Clear                       | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (I) = 0$                   | - | - | - | -          | -  | - | REL                                                                                                      | 2C                                               | rr                                                                            | 3                                                        |

| BMI <i>rel</i>                                                                                 | Branch if Minus                                      | PC ← (PC) + 2 + <i>rel</i> ? (N) = 1                                | - | - | _ | -          | -  | - | REL                                                                                                      | 2B                                               | rr                                                                            | 3                                                        |

| BMS rel                                                                                        | Branch if Interrupt Mask Set                         | PC ← (PC) + 2 + <i>rel</i> ? (I) = 1                                | - | - | _ | -          | -  | - | REL                                                                                                      | 2D                                               | rr                                                                            | 3                                                        |

| BNE rel                                                                                        | Branch if Not Equal                                  | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) = 0$                   | - | - | _ | -          | -  | - | REL                                                                                                      | 26                                               | rr                                                                            | 3                                                        |

| BPL <i>rel</i>                                                                                 | Branch if Plus                                       | PC ← (PC) + 2 + <i>rel</i> ? (N) = 0                                | - | - | _ | -          | -  | - | REL                                                                                                      | 2A                                               | rr                                                                            | 3                                                        |

| BRA rel                                                                                        | Branch Always                                        | $PC \leftarrow (PC) + 2 + \mathit{rel}$                             | - | - | _ | -          | -  | - | REL                                                                                                      | 20                                               | rr                                                                            | 3                                                        |

| BRCLR n,opr,rel                                                                                | Branch if Bit <i>n</i> in M Clear                    | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 0                               | _ | _ | _ | _          | _  | o | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b5)<br>DIR (b6) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D<br>0F     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |

| BRN <i>rel</i>                                                                                 | Branch Never                                         | $PC \leftarrow (PC) + 2$                                            | - | - | _ | -          | -  | - | REL                                                                                                      | 21                                               | rr                                                                            | 3                                                        |

| BRSET n,opr,rel                                                                                | Branch if Bit <i>n</i> in M Set                      | PC ← (PC) + 3 + <i>rel</i> ? (Mn) = 1                               | _ | _ | _ | _          | _  | o | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b5)<br>DIR (b7) | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E     | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr          | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 |

| BSET n,opr                                                                                     | Set Bit <i>n</i> in M                                | Mn ← 1                                                              | _ | _ | _ | _          | _  | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b5)<br>DIR (b7)             | 10<br>12<br>14<br>16<br>18<br>1A<br>1C<br>1E     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                            | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4                |

| Source<br>Form                                                                                        | Operation                     | Description                                                                                                                                                                                                                                                                                                                                         |   | E |   | ct o<br>CR |   |   | Address<br>Mode                                     | Opcode                                           | Operand                                         | Cycles                          |

|-------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|------------|---|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|---------------------------------|

| Form                                                                                                  |                               |                                                                                                                                                                                                                                                                                                                                                     | v | н | I | N          | z | С | PA                                                  | do                                               | Ope                                             | S<br>S                          |

| BSR rel                                                                                               | Branch to Subroutine          | $\begin{array}{l} PC \leftarrow (PC) + 2;  push  (PCL) \\ SP \leftarrow (SP) - 1;  push  (PCH) \\ SP \leftarrow (SP) - 1 \\ PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                                          | - | _ | _ | _          | - | - | REL                                                 | AD                                               | rr                                              | 4                               |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal   | $\begin{array}{l} PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel ? (A) - (M) = \$00 \end{array}$       | - | _ | _ | _          | _ | _ | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1             | 31<br>41<br>51<br>61<br>71<br>9E61               | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr | 5<br>4<br>4<br>5<br>4<br>6      |

| CLC                                                                                                   | Clear Carry Bit               | $C \leftarrow 0$                                                                                                                                                                                                                                                                                                                                    | - | - | - | -          | - | 0 | INH                                                 | 98                                               |                                                 | 1                               |

| CLI                                                                                                   | Clear Interrupt Mask          | l ← 0                                                                                                                                                                                                                                                                                                                                               | - | - | 0 | -          | - | - | INH                                                 | 9A                                               |                                                 | 2                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR ,X<br>CLR opr,SP                                  | Clear                         | $\begin{array}{c} M \leftarrow \$00\\ A \leftarrow \$00\\ X \leftarrow \$00\\ H \leftarrow \$00\\ M \leftarrow \$00\\ M \leftarrow \$00\\ M \leftarrow \$00\\ M \leftarrow \$00\\ \end{array}$                                                                                                                                                      | 0 | _ | _ | 0          | 1 | _ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F         | dd<br>ff<br>ff                                  | 3<br>1<br>1<br>3<br>2<br>4      |

| CMP #opr<br>CMP opr<br>CMP opr<br>CMP opr,X<br>CMP opr,X<br>CMP ,X<br>CMP opr,SP<br>CMP opr,SP        | Compare A with M              | (A) – (M)                                                                                                                                                                                                                                                                                                                                           | o | _ | _ | o          | o | o | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>E1<br>F1<br>9EE1<br>9ED1       | ii<br>dd<br>hh ll<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>2<br>4<br>5 |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                          | Complement (One's Complement) | $\begin{split} M &\leftarrow (\overline{M}) = \$FF - (M) \\ A &\leftarrow (\overline{A}) = \$FF - (M) \\ X &\leftarrow (\overline{X}) = \$FF - (M) \\ M &\leftarrow (\overline{M}) = \$FF - (M) \end{split}$ | 0 | _ | _ | 0          | 0 | 1 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5           |

| CPHX # <i>opr</i><br>CPHX <i>opr</i>                                                                  | Compare H:X with M            | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                   | 0 | - | - | 0          | 0 | 0 | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3<br>4                          |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX ,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP        | Compare X with M              | (X) – (M)                                                                                                                                                                                                                                                                                                                                           | o | _ | _ | o          | o | 0 | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 | ii<br>dd<br>hh ll<br>ee ff<br>ff<br>ee ff       | 2<br>3<br>4<br>3<br>2<br>4<br>5 |

| DAA                                                                                                   | Decimal Adjust A              | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                   | υ | _ | - | 0          | 0 | 0 | INH                                                 | 72                                               |                                                 | 2                               |

|                                                                                                       | I                             | I                                                                                                                                                                                                                                                                                                                                                   | I |   | L | I          |   | I | I                                                   |                                                  | I                                               | 1                               |

| Source                                                                                         | Operation                           | Description                                                                                                                                                                                             |   | E |   | ct (<br>CR |   |   | Address<br>Mode                                     | Opcode                                           | erand                                           | Cycles                          |

|------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|------------|---|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|---------------------------------|

| Form                                                                                           |                                     |                                                                                                                                                                                                         | v | н | I | Ν          | z | С | Add                                                 | Ő                                                | do                                              | ပ်                              |

| LDX #opr<br>LDX opr<br>LDX opr<br>LDX opr,X<br>LDX opr,X<br>LDX ,X<br>LDX opr,SP<br>LDX opr,SP | Load X from M                       | X ← (M)                                                                                                                                                                                                 | 0 | _ | _ | 0          | o | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AE<br>BE<br>CE<br>DE<br>EE<br>FE<br>9EEE<br>9EDE | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2<br>3<br>4<br>3<br>2<br>4<br>5 |

| LSL opr<br>LSLA<br>LSLX<br>LSL opr,X<br>LSL ,X<br>LSL opr,SP                                   | Logical Shift Left<br>(Same as ASL) | C                                                                                                                                                                                                       | 0 | _ | _ | 0          | o | o | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5           |

| LSR opr<br>LSRA<br>LSRX<br>LSR opr,X<br>LSR ,X<br>LSR opr,SP                                   | Logical Shift Right                 |                                                                                                                                                                                                         | 0 | _ | _ | 0          | 0 | 0 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 34<br>44<br>54<br>64<br>74<br>9E64               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5           |

| MOV opr,opr<br>MOV opr,X+<br>MOV #opr,opr<br>MOV X+,opr                                        | Move                                | $(M)_{Destination} \leftarrow (M)_{Source}$<br>H:X $\leftarrow$ (H:X) + 1 (IX+D, DIX+)                                                                                                                  | 0 | _ | _ | 0          | 0 | _ | DD<br>DIX+<br>IMD<br>IX+D                           | 4E<br>5E<br>6E<br>7E                             | dd dd<br>dd<br>ii dd<br>dd                      | 5<br>4<br>4<br>4                |

| MUL                                                                                            | Unsigned multiply                   | $X:A \gets (X) \times (A)$                                                                                                                                                                              | - | 0 | - | -          | - | 0 | INH                                                 | 42                                               |                                                 | 5                               |

| NEG opr<br>NEGA<br>NEGX<br>NEG opr,X<br>NEG ,X<br>NEG opr,SP                                   | Negate (Two's Complement)           | $\begin{split} M &\leftarrow -(M) = \$00 - (M) \\ A &\leftarrow -(A) = \$00 - (A) \\ X &\leftarrow -(X) = \$00 - (X) \\ M &\leftarrow -(M) = \$00 - (M) \\ M &\leftarrow -(M) = \$00 - (M) \end{split}$ | 0 | _ | _ | 0          | o | o | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 30<br>40<br>50<br>60<br>70<br>9E60               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5           |

| NOP                                                                                            | No Operation                        | None                                                                                                                                                                                                    | - | - | - | -          | - | - | INH                                                 | 9D                                               |                                                 | 1                               |

| NSA                                                                                            | Nibble Swap A                       | A ← (A[3:0]:A[7:4])                                                                                                                                                                                     | - | - | - | -          | - | - | INH                                                 | 62                                               |                                                 | 3                               |

| ORA #opr<br>ORA opr<br>ORA opr<br>ORA opr,X<br>ORA opr,X<br>ORA ,X<br>ORA opr,SP<br>ORA opr,SP | Inclusive OR A and M                | A ← (A)   (M)                                                                                                                                                                                           | 0 | _ | _ | 0          | o | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AA<br>BA<br>CA<br>DA<br>EA<br>FA<br>9EEA<br>9EDA | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>2<br>4<br>5 |

| PSHA                                                                                           | Push A onto Stack                   | Push (A); SP $\leftarrow$ (SP) – 1                                                                                                                                                                      | - | - | - | -          | - | - | INH                                                 | 87                                               |                                                 | 2                               |

| PSHH                                                                                           | Push H onto Stack                   | Push (H); SP $\leftarrow$ (SP) – 1                                                                                                                                                                      | - | - | - | -          | - | - | INH                                                 | 8B                                               |                                                 | 2                               |

| PSHX                                                                                           | Push X onto Stack                   | Push (X); SP $\leftarrow$ (SP) – 1                                                                                                                                                                      | - | - | - | -          | - | - | INH                                                 | 89                                               |                                                 | 2                               |

| PULA                                                                                           | Pull A from Stack                   | $SP \leftarrow (SP + 1); Pull (A)$                                                                                                                                                                      | - | - | - | -          | - | - | INH                                                 | 86                                               |                                                 | 2                               |

#### **SIM Bus Clock Control and Generation**

|        |                                       | Read:  | IF6  | IF5       | IF4    | IF3  | IF2  | IF1  | 0    | 0    |

|--------|---------------------------------------|--------|------|-----------|--------|------|------|------|------|------|

| \$FE04 | Interrupt Status Register 1<br>(INT1) | Write: | R    | R         | R      | R    | R    | R    | R    | R    |

|        | ()                                    | Reset: | 0    | 0         | 0      | 0    | 0    | 0    | 0    | 0    |

|        | Interrupt Statue Degister 2           | Read:  | IF14 | IF13      | IF12   | IF11 | IF10 | IF9  | IF8  | IF7  |

| \$FE05 | Interrupt Status Register 2<br>(INT2) | Write: | R    | R         | R      | R    | R    | R    | R    | R    |

|        | ()                                    | Reset: | 0    | 0         | 0      | 0    | 0    | 0    | 0    | 0    |

|        | Interrupt Statue Degister 2           | Read:  | 0    | IF21      | IF20   | IF19 | IF18 | IF17 | IF16 | IF15 |

| \$FE06 | Interrupt Status Register 3<br>(INT3) | Write: | R    | R         | R      | R    | R    | R    | R    | R    |

|        | (                                     | Reset: | 0    | 0         | 0      | 0    | 0    | 0    | 0    | 0    |

|        |                                       |        |      | = Unimple | mented |      |      |      |      |      |

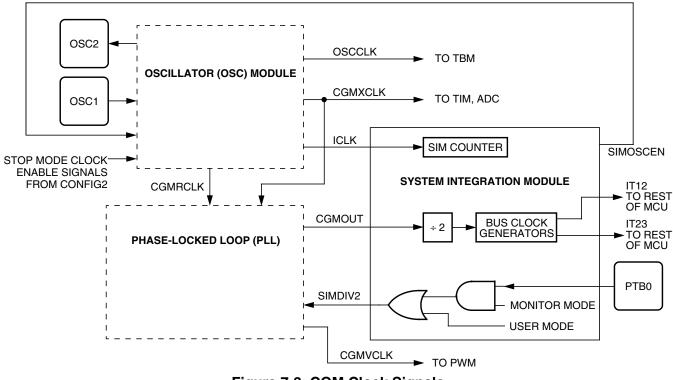

# 7.2 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, CGMOUT, as shown in Figure 7-3. This clock can come from either an external oscillator or from the on-chip PLL. (See Chapter 6 Clock Generator Module (CGM).)

Figure 7-3. CGM Clock Signals

# 7.2.1 Bus Timing

In user mode, the internal bus frequency is either the oscillator output (CGMXCLK) divided by four or the divided PLL output (CGMPCLK) divided by four.

# 8.5.2 ERARNGE

ERARNGE is used to erase a range of locations in FLASH.

| Routine Name        | ERARNGE                                                                                             |

|---------------------|-----------------------------------------------------------------------------------------------------|

| Routine Description | Erase a page or the entire array                                                                    |

| Calling Address     | \$FCE4                                                                                              |

| Stack Used          | 9 bytes                                                                                             |

| Data Block Format   | Bus speed (BUS_SPD)<br>Data size (DATASIZE)<br>Starting address (ADDRH)<br>Starting address (ADDRL) |

#### Table 8-12. ERARNGE Routine

There are two sizes of erase ranges: a page or the entire array. The ERARNGE will erase the page (512 consecutive bytes) in FLASH specified by the address ADDRH:ADDRL. This address can be any address within the page. Calling ERARNGE with ADDRH:ADDRL equal to \$FFFF will erase the entire FLASH array (mass erase). Therefore, care must be taken when calling this routine to prevent an accidental mass erase.

The ERARNGE routine do not use a data array. The DATASIZE byte is a dummy byte that is also not used.

The coding example below is to perform a page erase, from \$EE00-\$EFFF. The Initialization subroutine is the same as the coding example for PRGRNGE (see 8.5.1 PRGRNGE).

ERARNGE EQU \$FCE4 MAIN: BSR INITIALISATION : LDHX #FILE\_PTR JSR ERARNGE :

#### **Functional Description**

| Addr.           | Register Name                     | _               | Bit 7       | 6               | 5     | 4           | 3              | 2       | 1    | Bit 0      |

|-----------------|-----------------------------------|-----------------|-------------|-----------------|-------|-------------|----------------|---------|------|------------|

| *****           | TIM1 Status and Control           | Read:           | TOF         | TOIE            | TSTOP | 0           | 0              | PS2     | PS1  | PS0        |

| \$0020          | Register<br>(T1SC)                | Write:          | 0           | 0               | 1     | TRST<br>0   | 0              | 0       | 0    | 0          |

|                 | TIM1 Counter Register             | Reset:<br>Read: | Bit 15      | 14              | 13    | 12          | 11             | 10      | 9    | Bit 8      |

| \$0021          | High                              | Write:          | Dit 15      | 14              | 13    | 12          | 11             | 10      | 9    | Dit o      |

| ψ0021           | (T1CNTH)                          | Reset:          | 0           | 0               | 0     | 0           | 0              | 0       | 0    | 0          |

|                 | TIM1 Counter Register             | Read:           | Bit 7       | 6               | 5     | 4           | 3              | 2       | 1    | Bit 0      |

| \$0022          | Low                               | Write:          |             |                 |       |             |                |         |      |            |

|                 | (T1CNTL)                          | Reset:          | 0           | 0               | 0     | 0           | 0              | 0       | 0    | 0          |

|                 | TIM Counter Modulo                | Read:           | Bit 15      | 14              | 13    | 12          | 11             | 10      | 9    | Bit 8      |

| \$0023          | Register High                     | Write:          |             |                 |       |             |                |         |      |            |

|                 | (TMODH)                           | Reset:          | 1           | 1               | 1     | 1           | 1              | 1       | 1    | 1          |

|                 | TIM1 Counter Modulo               | Read:           | Bit 7       | 6               | 5     | 4           | 3              | 2       | 1    | Bit 0      |

| \$0024          | Register Low                      | Write:          |             | <br>            |       |             |                |         |      |            |

|                 | (T1MODL)<br>TIM1 Channel 0 Status | Reset:<br>Read: | 1<br>CH0F   | 1               | 1     | 1           | 1              | 1       | 1    | 1          |

| \$0025          | and Control Register              | Write:          | 0           | CHOIE           | MS0B  | MS0A        | ELS0B          | ELS0A   | TOV0 | CH0MAX     |

| \$00 <u></u> 20 | (T1SC0)                           | Reset:          | 0           | 0               | 0     | 0           | 0              | 0       | 0    | 0          |

|                 | TIM1 Channel 0                    | Read:           | Bit 15      | 14              | 13    | 12          | 11             | 10      | 0    | Bit 8      |

| \$0026          | Register High                     | Write:          | DIL TO      | 14              | 10    | 12          | 11             | 10      | 9    | DILO       |

|                 | (T1CH0H)                          | Reset:          |             |                 |       | Indetermina | te after reset |         |      |            |

|                 | TIM1 Channel 0                    | Read:           | Bit 7       | 6               | 5     | 4           | 3              | 2       | 1    | Bit 0      |

| \$0027          | Register Low                      | Write:          |             |                 |       |             |                |         |      |            |

|                 | (T1CH0L)<br>TIM1 Channel 1 Status | Reset:<br>Read: | CH1F        |                 | 0     | Indetermina | te after reset |         |      |            |

| \$0028          | and Control Register              | Write:          |             | CH1IE           | 0     | MS1A        | ELS1B          | ELS1A   | TOV1 | CH1MAX     |

| ψ0020           | (T1SC1)                           | Reset:          | 0           | 0               | 0     | 0           | 0              | 0       | 0    | 0          |

|                 | TIM1 Channel 1                    | Read:           | -           | -               |       | _           |                | -       | -    |            |

| \$0029          | Register High                     | Write:          | Bit 15      | 14              | 13    | 12          | 11             | 10      | 9    | Bit 8      |

|                 | (T1CH1H)                          | Reset:          |             |                 |       | Indetermina | te after reset |         |      |            |

|                 | TIM1 Channel 1                    | Read:           | Bit 7       | 6               | 5     | 4           | 3              | 2       | 1    | Bit 0      |

| \$002A          | Register Low                      | Write:          |             | 0               | 5     |             |                | 2       | I    | Dit U      |

|                 | (T1CH1L)                          | Reset:          |             | 1               | 1     | 1           | te after reset |         | 1    |            |

| #000B           | TIM2 Status and Control           | Read:           | TOF         | TOIE            | TSTOP |             | 0              | PS2     | PS1  | PS0        |

| \$002B          | Register<br>(T2SC)                | Write:          | 0           |                 | 4     | TRST        | 0              |         |      |            |

|                 | TIM2 Counter Register             | Read:           | 0<br>Bit 15 | 0               | 1     | 0           | 0              | 0<br>10 | 0    | 0<br>Bit 8 |

| \$002C          | High                              | Write:          | Dit 15      | 14              | 10    | 12          | 11             | 10      | 3    | Dit 0      |

| Ψ0020           | (T2CNTH)                          | Reset:          | 0           | 0               | 0     | 0           | 0              | 0       | 0    | 0          |

|                 | TIM2 Counter Register             | Read:           | Bit 7       | 6               | 5     | 4           | 3              | 2       | 1    | Bit 0      |

| \$002D          | Low                               | Write:          | -           |                 |       |             |                |         |      | -          |

|                 | (T2CNTL)                          | Reset:          | 0           | 0               | 0     | 0           | 0              | 0       | 0    | 0          |

| <b>****</b>     | TIM2 Counter Modulo               | Read:           | Bit 15      | 14              | 13    | 12          | 11             | 10      | 9    | Bit 8      |

| \$002E          | Register High                     | Write:          | 1           | <u>ا</u>        | 1     | 1           | 1              | 1       | -    | 1          |

|                 | (T2MODH)                          | Reset:          | 1           | ı<br>Unimplen = | •     | I           | I              | I       | 1    | I          |

|                 |                                   | L               |             |                 |       |             |                |         |      |            |

# Figure 9-2. TIM I/O Register Summary (Sheet 1 of 2)

#### Serial Communications Interface Module (SCI)

#### TE — Transmitter Enable Bit

Setting this read/write bit begins the transmission by sending a preamble of 10 or 11 logic 1s from the transmit shift register to the TxD pin. If software clears the TE bit, the transmitter completes any transmission in progress before the TxD returns to the idle condition (logic 1). Clearing and then setting TE during a transmission queues an idle character to be sent after the character currently being transmitted. Reset clears the TE bit.

1 = Transmitter enabled

0 = Transmitter disabled

#### NOTE

Writing to the TE bit is not allowed when the enable SCI bit (ENSCI) is clear. ENSCI is in SCI control register 1.

#### **RE** — Receiver Enable Bit

Setting this read/write bit enables the receiver. Clearing the RE bit disables the receiver but does not affect receiver interrupt flag bits. Reset clears the RE bit.

1 = Receiver enabled

0 = Receiver disabled

#### NOTE

Writing to the RE bit is not allowed when the enable SCI bit (ENSCI) is clear. ENSCI is in SCI control register 1.

#### **RWU** — Receiver Wakeup Bit

This read/write bit puts the receiver in a standby state during which receiver interrupts are disabled. The WAKE bit in SCC1 determines whether an idle input or an address mark brings the receiver out of the standby state and clears the RWU bit. Reset clears the RWU bit.

1 = Standby state

0 = Normal operation

#### SBK — Send Break Bit

Setting and then clearing this read/write bit transmits a break character followed by a logic 1. The logic 1 after the break character guarantees recognition of a valid start bit. If SBK remains set, the transmitter continuously transmits break characters with no logic 1s between them. Reset clears the SBK bit.

1 = Transmit break characters

0 = No break characters being transmitted

#### NOTE

Do not toggle the SBK bit immediately after setting the SCTE bit. Toggling SBK before the preamble begins causes the SCI to send a break character instead of a preamble.

SCI status register 2 contains flags to signal the following conditions:

- Break character detected •

- Incoming data •

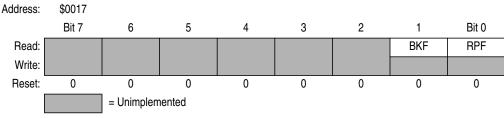

Figure 11-14. SCI Status Register 2 (SCS2)

### **BKF** — Break Flag Bit

This clearable, read-only bit is set when the SCI detects a break character on the RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after logic 1s again appear on the RxD pin followed by another break character. Reset clears the BKF bit.

1 = Break character detected

0 = No break character detected

### **RPF** — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a logic 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch) or when the receiver detects an idle character. Polling RPF before disabling the SCI module or entering stop mode can show whether a reception is in progress.

1 = Reception in progress

0 = No reception in progress

# 11.8.6 SCI Data Register

The SCI data register (SCDR) is the buffer between the internal data bus and the receive and transmit shift registers. Reset has no effect on data in the SCI data register.

| Address: | \$0018 |    |    |           |            |    |    |       |

|----------|--------|----|----|-----------|------------|----|----|-------|

|          | Bit 7  | 6  | 5  | 4         | 3          | 2  | 1  | Bit 0 |

| Read:    | R7     | R6 | R5 | R4        | R3         | R2 | R1 | R0    |

| Write:   | T7     | T6 | T5 | T4        | Т3         | T2 | T1 | T0    |

| Reset:   |        |    |    | Unaffecte | d by reset |    |    |       |

Figure 11-15. SCI Data Register (SCDR)

#### R7/T7–R0/T0 — Receive/Transmit Data Bits

Reading the SCDR accesses the read-only received data bits, R7–R0. Writing to the SCDR writes the data to be transmitted, T7–T0. Reset has no effect on the SCDR.

#### NOTE

Do not use read/modify/write instructions on the SCI data register.

Infrared Serial Communications Interface Module (IRSCI)

| RT3, RT5, and RT7<br>Samples | Start Bit<br>Verification | Noise Flag |

|------------------------------|---------------------------|------------|

| 011                          | No                        | 0          |

| 100                          | Yes                       | 1          |

| 101                          | No                        | 0          |

| 110                          | No                        | 0          |

| 111                          | No                        | 0          |

Table 12-2. Start Bit Verification

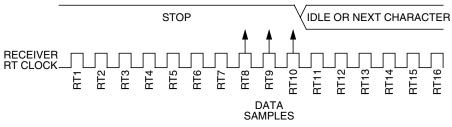

If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 12-3 summarizes the results of the data bit samples.

| RT8, RT9, and RT10<br>Samples | Data Bit<br>Determination | Noise Flag |

|-------------------------------|---------------------------|------------|

| 000                           | 0                         | 0          |

| 001                           | 0                         | 1          |

| 010                           | 0                         | 1          |

| 011                           | 1                         | 1          |

| 100                           | 0                         | 1          |

| 101                           | 1                         | 1          |

| 110                           | 1                         | 1          |

| 111                           | 1                         | 0          |

Table 12-3. Data Bit Recovery

### NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are logic 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit.

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 12-4 summarizes the results of the stop bit samples.

| RT8, RT9, and RT10<br>Samples | Framing<br>Error Flag | Noise Flag |

|-------------------------------|-----------------------|------------|

| 000                           | 1                     | 0          |

| 001                           | 1                     | 1          |

Table 12-4. Stop Bit Recovery

#### Infrared Serial Communications Interface Module (IRSCI)

The maximum percent difference between the receiver count and the transmitter count of a slow 8-bit character with no errors is

$$\left|\frac{154 - 147}{154}\right| \times 100 = 4.54\%$$

For a 9-bit character, data sampling of the stop bit takes the receiver 10 bit times  $\times$  16 RT cycles + 10 RT cycles = 170 RT cycles.

With the misaligned character shown in Figure 12-10, the receiver counts 170 RT cycles at the point when the count of the transmitting device is 10 bit times  $\times$  16 RT cycles + 3 RT cycles = 163 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a slow 9-bit character with no errors is

$$\left|\frac{170 - 163}{170}\right| \times 100 = 4.12\%$$

### **Fast Data Tolerance**

Figure 12-11 shows how much a fast received character can be misaligned without causing a noise error or a framing error. The fast stop bit ends at RT10 instead of RT16 but is still there for the stop bit data samples at RT8, RT9, and RT10.

Figure 12-11. Fast Data

For an 8-bit character, data sampling of the stop bit takes the receiver 9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 12-11, the receiver counts 154 RT cycles at the point when the count of the transmitting device is 10 bit times  $\times$  16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is

$$\left|\frac{154 - 160}{154}\right| \times 100 = 3.90\%$$

For a 9-bit character, data sampling of the stop bit takes the receiver 10 bit times  $\times$  16 RT cycles + 10 RT cycles = 170 RT cycles.

With the misaligned character shown in Figure 12-11, the receiver counts 170 RT cycles at the point when the count of the transmitting device is 11 bit times  $\times$  16 RT cycles = 176 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is

#### Infrared Serial Communications Interface Module (IRSCI)

- IRSCI status register 1 (IRSCS1)

- IRSCI status register 2 (IRSCS2)

- IRSCI data register (IRSCDR)

- IRSCI baud rate register (IRSCBR)

- IRSCI infrared control register (IRSCIRCR)

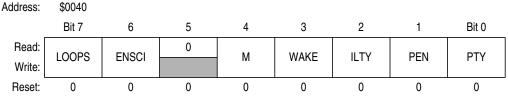

### 12.9.1 IRSCI Control Register 1

SCI control register 1:

- Enables loop mode operation

- Enables the SCI

- Controls output polarity

- Controls character length

- Controls SCI wakeup method

- Controls idle character detection

- Enables parity function

- Controls parity type

### Figure 12-12. IRSCI Control Register 1 (IRSCC1)

#### LOOPS — Loop Mode Select Bit

This read/write bit enables loop mode operation for the SCI only. In loop mode the RxD pin is disconnected from the SCI, and the transmitter output goes into the receiver input. Both the transmitter and the receiver must be enabled to use loop mode. The infrared encoder/decoder is not in the loop. Reset clears the LOOPS bit.

- 1 = Loop mode enabled

- 0 = Normal operation enabled

### ENSCI — Enable SCI Bit

This read/write bit enables the SCI and the SCI baud rate generator. Clearing ENSCI sets the SCTE and TC bits in SCI status register 1 and disables transmitter interrupts. Reset clears the ENSCI bit.

1 = SCI enabled

0 = SCI disabled

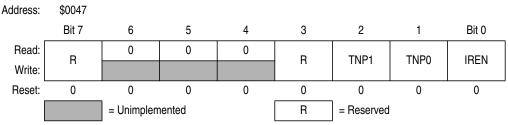

# 12.9.8 IRSCI Infrared Control Register

The infrared control register contains the control bits for the infrared sub-module.

- Enables the infrared sub-module

- Selects the infrared transmitter narrow pulse width

Figure 12-20. IRSCI Infrared Control Register (IRSCIRCR)

### TNP1 and TNP0 — Transmitter Narrow Pulse Bits

These read/write bits select the infrared transmitter narrow pulse width as shown in Table 12-10. Reset clears TNP1 and TNP0.

| TNP1 and TNP0 | Prescaler Divisor (PD)            |  |  |  |

|---------------|-----------------------------------|--|--|--|

| 00            | SCI transmits a 3/16 narrow pulse |  |  |  |

| 01            | SCI transmits a 1/16 narrow pulse |  |  |  |

| 10            | COL transmite a 1/20 narrow pulsa |  |  |  |

| 11            | SCI transmits a 1/32 narrow pulse |  |  |  |

Table 12-10. Infrared Narrow Pulse Selection

### IREN — Infrared Enable Bit

This read/write bit enables the infrared sub-module for encoding and decoding the SCI data stream. When this bit is clear, the infrared sub-module is disabled. Reset clears the IREN bit.

1 = infrared sub-module enabled

0 = infrared sub-module disabled

# 13.5.2 Transmission Format When CPHA = 0

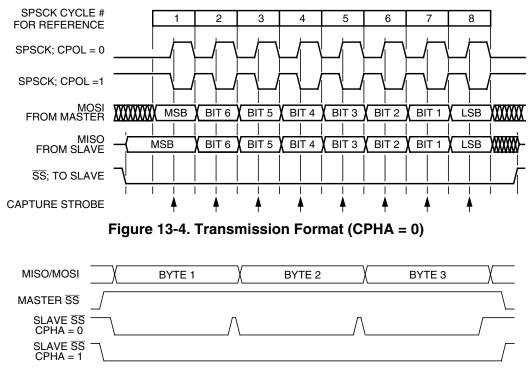

Figure 13-4 shows an SPI transmission in which CPHA is logic 0. The figure should not be used as a replacement for data sheet parametric information.

Two waveforms are shown for SPSCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram since the serial clock (SPSCK), master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The  $\overline{SS}$  line is the slave select input to the slave. The slave SPI drives its MISO output only when its slave select input ( $\overline{SS}$ ) is at logic 0, so that only the selected slave drives to the master. The  $\overline{SS}$  pin of the master is not shown but is assumed to be inactive. The  $\overline{SS}$  pin of the master must be high or must be reconfigured as general-purpose I/O not affecting the SPI. (See 13.7.2 Mode Fault Error.) When CPHA = 0, the first SPSCK edge is the MSB capture strobe. Therefore, the slave must begin driving its data before the first SPSCK edge, and a falling edge on the  $\overline{SS}$  pin is used to start the slave data transmission. The slave's  $\overline{SS}$  pin must be toggled back to high and then low again between each byte transmitted as shown in Figure 13-5.

When CPHA = 0 for a slave, the falling edge of  $\overline{SS}$  indicates the beginning of the transmission. This causes the SPI to leave its idle state and begin driving the MISO pin with the MSB of its data. Once the transmission begins, no new data is allowed into the shift register from the transmit data register. Therefore, the SPI data register of the slave must be loaded with transmit data before the falling edge of  $\overline{SS}$ . Any data written after the falling edge is stored in the transmit data register and transferred to the shift register after the current transmission.

#### Analog-to-Digital Converter (ADC)