Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 8MHz                                                         |

| Connectivity               | I <sup>2</sup> C, IRSCI, SCI, SPI                            |

| Peripherals                | LED, LVD, POR, PWM                                           |

| Number of I/O              | 30                                                           |

| Program Memory Size        | 64KB (64K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                |                                                              |

| RAM Size                   | 2K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                    |

| Supplier Device Package    | 42-PDIP                                                      |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908ap64cb |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC68HC908AP64 MC68HC908AP32 MC68HC908AP16 MC68HC908AP8

**Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

#### http://www.freescale.com

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005, 2007. All rights reserved.

| \$0000<br>↓<br>\$005E | I/O Registers<br>96 Bytes                               | MC68HC908AP32                 |                  | MC68HC908AP16                 |                  | MC68HC908AP8                 |                            |

|-----------------------|---------------------------------------------------------|-------------------------------|------------------|-------------------------------|------------------|------------------------------|----------------------------|

| \$005F<br>\$0060      | RAM<br>2,048 Bytes                                      | RAM                           | \$0060           | RAM<br>1,024 Bytes            | \$0060<br>\$045F | RAM<br>1,024 Bytes           | \$0060<br>\$045F           |

| ↓<br>\$085F           | (MC68HC908AP64)                                         | 2,048 Bytes                   | ↓<br>_\$085F     | Unimplemented<br>1,024 Bytes  |                  | Unimplemented<br>1,024 Bytes |                            |

| \$0860                |                                                         |                               | \$0860           | FLASH Memory<br>16,384 Bytes  | \$0860<br>↓      | FLASH Memory<br>8,192 Bytes  | \$0860<br>\$285F<br>\$2860 |

|                       |                                                         | FLASH Memory<br>32,768 Bytes  | $\downarrow$     |                               | \$485F<br>\$4860 |                              |                            |

| $\downarrow$          | FLASH Memory<br>62,368 Bytes<br>( <b>MC68HC908AP64)</b> |                               | \$885F<br>\$8860 |                               |                  | Unimplemented                | ↓                          |

|                       | (                                                       |                               |                  | Unimplemented<br>45,984 Bytes | $\downarrow$     | 54,176 Bytes                 | *                          |

|                       |                                                         | Unimplemented<br>29,600 Bytes | Ļ                |                               |                  |                              |                            |

| \$FBFF                |                                                         |                               | \$FBFF           |                               | \$FBFF           |                              | \$FBFF                     |

| \$FC00                | Monitor ROM 2                                           |                               |                  |                               |                  |                              |                            |

| \$FDFF                | 512 Bytes                                               |                               |                  |                               |                  |                              |                            |

| \$FE00                | SIM Break Status Register                               |                               |                  |                               |                  |                              |                            |

| \$FE01                | SIM Reset Status Register                               |                               |                  |                               |                  |                              |                            |

| \$FE02                | Reserved                                                |                               |                  |                               |                  |                              |                            |

| \$FE03                | SIM Break Flag Control Register                         |                               |                  |                               |                  |                              |                            |

| \$FE04                | Interrupt Status Register 1                             |                               |                  |                               |                  |                              |                            |

| \$FE05                | Interrupt Status Register 2                             |                               |                  |                               |                  |                              |                            |

| \$FE06                | Interrupt Status Register 3                             |                               |                  |                               |                  |                              |                            |

| \$FE07                | Reserved                                                |                               |                  |                               |                  |                              |                            |

| \$FE08                | FLASH Control Register                                  |                               |                  |                               |                  |                              |                            |

| \$FE09<br>\$FE0A      | FLASH Block Protect Register<br>Reserved                |                               |                  |                               |                  |                              |                            |

| \$FE0A<br>\$FE0B      | Reserved                                                |                               |                  |                               |                  |                              |                            |

| \$FE0C                | Break Address Register High                             |                               |                  |                               |                  |                              |                            |

| \$FE0D                | Break Address Register Low                              |                               |                  |                               |                  |                              |                            |

| \$FE0E                | Break Status and Control Register                       |                               |                  |                               |                  |                              |                            |

| \$FE0F                | LVI Status Register                                     |                               |                  |                               |                  |                              |                            |

| \$FE10                | Monitor ROM 1                                           |                               |                  |                               |                  |                              |                            |

| ↓<br>\$FFCE           | 447 Bytes                                               |                               |                  |                               |                  |                              |                            |

| \$FFCF                | Mask Option Register                                    |                               |                  |                               |                  |                              |                            |

| \$FFD0                | FLASH Vectors                                           |                               |                  |                               |                  |                              |                            |

| ↓<br>\$FFFF           | 48 Bytes                                                |                               |                  |                               |                  |                              |                            |

Figure 2-1. Memory Map

**Monitor ROM**

| Addr.               | Register Name                              |                 | Bit 7        | 6          | 5       | 4            | 3          | 2      | 1            | Bit 0 |

|---------------------|--------------------------------------------|-----------------|--------------|------------|---------|--------------|------------|--------|--------------|-------|

|                     |                                            | Read:           | 0            | IF21       | IF20    | IF19         | IF18       | IF17   | IF16         | IF15  |

| \$FE06              | Interrupt Status Register 3<br>(INT3)      | Write:          | R            | R          | R       | R            | R          | R      | R            | R     |

|                     | (1110)                                     | Reset:          | 0            | 0          | 0       | 0            | 0          | 0      | 0            | 0     |

| \$FE07              | Reserved                                   | Read:<br>Write: | R            | R          | R       | R            | R          | R      | R            | R     |

|                     |                                            | Reset:          | [            |            |         | 1            | 1          | 1      | 1            |       |

|                     | FLASH Control Register                     | Read:           | 0            | 0          | 0       | 0            | HVEN       | MASS   | ERASE        | PGM   |

| \$FE08              | (FLCR)                                     | Write:          |              |            |         |              |            |        |              |       |

|                     | , , , , , , , , , , , , , , , , , , ,      | Reset:          | 0            | 0          | 0       | 0            | 0          | 0      | 0            | 0     |

| \$FE09              | FLASH Block Protect<br>Register            | Read:<br>Write: | BPR7         | BPR6       | BPR5    | BPR4         | BPR3       | BPR2   | BPR1         | BPR0  |

|                     | (FLBPR)                                    | Reset:          | 0            | 0          | 0       | 0            | 0          | 0      | 0            | 0     |

| \$FE0A              | Reserved                                   | Read:<br>Write: | R            | R          | R       | R            | R          | R      | R            | R     |

|                     |                                            | Reset:          |              |            |         |              | •          | •      |              |       |

| \$FE0B              | Reserved                                   | Read:<br>Write: | R            | R          | R       | R            | R          | R      | R            | R     |

|                     |                                            | Reset:          |              |            |         |              | •          | •      |              |       |

| \$FE0C              | Break Address<br>Register High             |                 | Bit 15       | 14         | 13      | 12           | 11         | 10     | 9            | Bit 8 |

|                     | (BRKH)                                     | Reset:          | 0            | 0          | 0       | 0            | 0          | 0      | 0            | 0     |

| \$FE0D              | Break Address<br>Register Low              | Read:<br>Write: | Bit 7        | 6          | 5       | 4            | 3          | 2      | 1            | Bit 0 |

|                     | (BRKL)                                     | Reset:          | 0            | 0          | 0       | 0            | 0          | 0      | 0            | 0     |

| \$FE0E              | Break Status and Control<br>Register       | Reset:<br>Read: | BRKE         | BRKA       | 0       | 0            | 0          | 0      | 0            | 0     |

|                     | (BRKSCR)                                   | Write:          | 0            | 0          | 0       | 0            | 0          | 0      | 0            | 0     |

|                     |                                            | Reset:          | LVIOUT       | 0          | 0       | 0            | 0          | 0      | 0            | 0     |

| \$FE0F              | LVI Status Register (LVISR)                | Read:           |              |            |         |              |            |        |              |       |

|                     |                                            | Write:          | 0            | 0          | 0       | 0            | 0          | 0      | 0            | 0     |

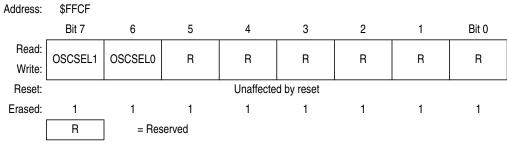

| \$FFCF              | Mask Option Register<br>(MOR) <sup>#</sup> | Read:<br>Write: | OSCSEL1      | OSCSEL0    | R       | R            | R          | R      | R            | R     |

|                     | (MOT)                                      | Erased:         | 1            | 1          | 1       | 1            | 1          | 1      | 1            | 1     |

|                     |                                            | Reset:          | U            | U          | U       | U            | U          | U      | U            | U     |

|                     | Read: Low byte of reset vector             |                 |              |            |         |              |            |        |              |       |

| \$FFFF              | COP Control Register                       | Write:          |              |            | Writin  | g clears COP |            | value) |              |       |

|                     | (COPCTL)                                   | Reset:          | I            |            |         | -            | d by reset | -      |              |       |

| <sup>#</sup> MOR is | a non-volatile FLASH register;             | write by        | programminę  | <b>]</b> . |         | _            |            |        | _            |       |

|                     | U = Unaffected                             |                 | X = Indetern | ninate     |         | = Unimplem   | ented      | R      | ] = Reserved |       |

|                     | Figuro                                     | ົ້              | ontrol (     | Statue a   | ad Data | Dogiator     | o (Shoot   | 0 of 0 |              |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 9 of 9)

#### SCIBDSRC — SCI Baud Rate Clock Source

SCIBDSRC selects the clock source used for the standard SCI module (non-infrared SCI). The setting of this bit affects the frequency at which the SCI operates.

- 1 = Internal data bus clock, f<sub>BUS</sub>, is used as clock source for SCI

- 0 = Oscillator clock, CGMXCLK, is used as clock source for SCI

# 3.5 Mask Option Register (MOR)

The mask option register (MOR) is used for selecting one of the three clock options for the MCU. The MOR is a byte located in FLASH memory, and is written to by a FLASH programming routine.

#### Figure 3-4. Mask Option Register (MOR)

#### OSCSEL1, OSCSEL0 — Oscillator Selection Bits

OSCSEL1 and OSCSEL0 select which oscillator is used for the MCU CGMXCLK clock. The erase state of these two bits is logic 1. These bits are unaffected by reset. (See Table 3-1).

#### Bits 5–0 — Should be left as 1's

| OSCSEL1 | OSCSEL0 | CGMXCLK | OSC2 pin                    | Comments                                                                                                |

|---------|---------|---------|-----------------------------|---------------------------------------------------------------------------------------------------------|

| 0       | 0       | _       | _                           | Not used                                                                                                |

| 0       | 1       | ICLK    | f <sub>BUS</sub>            | Internal oscillator generates the CGMXCLK.                                                              |

| 1       | 0       | RCCLK   | f <sub>BUS</sub>            | RC oscillator generates the CGMXCLK.<br>Internal oscillator is available after each POR<br>or reset.    |

| 1       | 1       | X-TAL   | Inverting<br>output of XTAL | X-tal oscillator generates the CGMXCLK.<br>Internal oscillator is available after each POR<br>or reset. |

Table 3-1. CGMXCLK Clock Selection

#### NOTE

The internal oscillator is a free running oscillator and is available after each POR or reset. It is turned-off in stop mode by setting the STOP\_ICLKDIS bit in CONFIG2.

# MC68HC908AP Family Data Sheet, Rev. 4

|            | Bit Mani             | pulation            | Branch             | Read-Modify-Write  |                     |                     |                     | Control Register/Memory |                    |                    |                   |                   |                   |                   |                   |                   |                   |                   |                  |

|------------|----------------------|---------------------|--------------------|--------------------|---------------------|---------------------|---------------------|-------------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|            | DIR                  | DIR                 | REL                | DIR                | INH                 | INH                 | IX1                 | SP1                     | IX                 | INH                | INH               | IMM               | DIR               | EXT               | IX2               | SP2               | IX1               | SP1               | IX               |

| MSB<br>LSB | 0                    | 1                   | 2                  | 3                  | 4                   | 5                   | 6                   | 9E6                     | 7                  | 8                  | 9                 | A                 | В                 | с                 | D                 | 9ED               | E                 | 9EE               | F                |

| 0          | 5<br>BRSET0<br>3 DIR | 4<br>BSET0<br>2 DIR | 3<br>BRA<br>2 REL  | 4<br>NEG<br>2 DIR  | 1<br>NEGA<br>1 INH  | 1<br>NEGX<br>1 INH  | 4<br>NEG<br>2 IX1   | 5<br>NEG<br>3 SP1       | 3<br>NEG<br>1 IX   | 7<br>RTI<br>1 INH  | 3<br>BGE<br>2 REL | 2<br>SUB<br>2 IMM | 3<br>SUB<br>2 DIR | 4<br>SUB<br>3 EXT | 4<br>SUB<br>3 IX2 | 5<br>SUB<br>4 SP2 | 3<br>SUB<br>2 IX1 | 4<br>SUB<br>3 SP1 | 2<br>SUB<br>1 IX |

| 1          | 5<br>BRCLR0<br>3 DIR | 4<br>BCLR0<br>2 DIR | 3<br>BRN<br>2 REL  | 5<br>CBEQ<br>3 DIR | 4<br>CBEQA<br>3 IMM | 4<br>CBEQX<br>3 IMM | 5<br>CBEQ<br>3 IX1+ | 6<br>CBEQ<br>4 SP1      | 4<br>CBEQ<br>2 IX+ | 4<br>RTS<br>1 INH  | 3<br>BLT<br>2 REL | 2<br>CMP<br>2 IMM | 3<br>CMP<br>2 DIR | 4<br>CMP<br>3 EXT | 4<br>CMP<br>3 IX2 | 5<br>CMP<br>4 SP2 | 3<br>CMP<br>2 IX1 | 4<br>CMP<br>3 SP1 | 2<br>CMP<br>1 IX |

| 2          | 5<br>BRSET1<br>3 DIR | 4<br>BSET1<br>2 DIR | 3<br>BHI<br>2 REL  |                    | 5<br>MUL<br>1 INH   | 7<br>DIV<br>1 INH   | 3<br>NSA<br>1 INH   |                         | 2<br>DAA<br>1 INH  |                    | BGT<br>2 REL      | 2<br>SBC<br>2 IMM | 3<br>SBC<br>2 DIR | 3 EXT             | 4<br>SBC<br>3 IX2 | SBC<br>4 SP2      | 3<br>SBC<br>2 IX1 | 4<br>SBC<br>3 SP1 | 2<br>SBC<br>1 IX |

| 3          | 5<br>BRCLR1<br>3 DIR | 4<br>BCLR1<br>2 DIR | 3<br>BLS<br>2 REL  | 4<br>COM<br>2 DIR  | 1<br>COMA<br>1 INH  | 1<br>COMX<br>1 INH  | 4<br>COM<br>2 IX1   | 5<br>COM<br>3 SP1       | 3<br>COM<br>1 IX   | 9<br>SWI<br>1 INH  | BLE<br>2 REL      | 2<br>CPX<br>2 IMM | 3<br>CPX<br>2 DIR | 4<br>CPX<br>3 EXT | 4<br>CPX<br>3 IX2 | 5<br>CPX<br>4 SP2 | 3<br>CPX<br>2 IX1 | 4<br>CPX<br>3 SP1 | 2<br>CPX<br>1 IX |

| 4          | 5<br>BRSET2<br>3 DIR | 4<br>BSET2<br>2 DIR | 3<br>BCC<br>2 REL  | 4<br>LSR<br>2 DIR  | 1<br>LSRA<br>1 INH  | 1<br>LSRX<br>1 INH  | 4<br>LSR<br>2 IX1   | 5<br>LSR<br>3 SP1       | 3<br>LSR<br>1 IX   | 2<br>TAP<br>1 INH  | 2<br>TXS<br>1 INH | 2<br>AND<br>2 IMM | 3<br>AND<br>2 DIR | 4<br>AND<br>3 EXT | 4<br>AND<br>3 IX2 | 5<br>AND<br>4 SP2 | 3<br>AND<br>2 IX1 | 4<br>AND<br>3 SP1 | 2<br>AND<br>1 IX |

| 5          | 5<br>BRCLR2<br>3 DIR | 4<br>BCLR2<br>2 DIR | BCS<br>2 REL       | 4<br>STHX<br>2 DIR | 3<br>LDHX<br>3 IMM  | 4<br>LDHX<br>2 DIR  | 3<br>CPHX<br>3 IMM  |                         | 4<br>CPHX<br>2 DIR | 1<br>TPA<br>1 INH  | 2<br>TSX<br>1 INH | BIT<br>2 IMM      | BIT<br>2 DIR      | BIT<br>3 EXT      | 4<br>BIT<br>3 IX2 | BIT<br>4 SP2      | 3<br>BIT<br>2 IX1 | 4<br>BIT<br>3 SP1 | 2<br>BIT<br>1 IX |

| 6          |                      | 4<br>BSET3<br>2 DIR |                    | 4<br>ROR<br>2 DIR  | 1<br>RORA<br>1 INH  | 1<br>RORX<br>1 INH  | 4<br>ROR<br>2 IX1   | 5<br>ROR<br>3 SP1       | 3<br>ROR<br>1 IX   | 2<br>PULA<br>1 INH |                   | 2<br>LDA<br>2 IMM | 3<br>LDA<br>2 DIR | 4<br>LDA<br>3 EXT | 4<br>LDA<br>3 IX2 | 5<br>LDA<br>4 SP2 |                   | 4<br>LDA<br>3 SP1 |                  |

| 7          | 5<br>BRCLR3<br>3 DIR | 4<br>BCLR3<br>2 DIR | 3<br>BEQ<br>2 REL  | 4<br>ASR<br>2 DIR  | 1<br>ASRA<br>1 INH  | 1<br>ASRX<br>1 INH  | 4<br>ASR<br>2 IX1   | 5<br>ASR<br>3 SP1       | 3<br>ASR<br>1 IX   | 2<br>PSHA<br>1 INH | 1<br>TAX<br>1 INH | AIS<br>2 IMM      | 3<br>STA<br>2 DIR | 4<br>STA<br>3 EXT | 4<br>STA<br>3 IX2 | 5<br>STA<br>4 SP2 | 3<br>STA<br>2 IX1 | 4<br>STA<br>3 SP1 | 2<br>STA<br>1 IX |

| 8          | 5<br>BRSET4<br>3 DIR | 4<br>BSET4<br>2 DIR | 3<br>BHCC<br>2 REL | 4<br>LSL<br>2 DIR  | 1<br>LSLA<br>1 INH  | 1<br>LSLX<br>1 INH  | 4<br>LSL<br>2 IX1   | 5<br>LSL<br>3 SP1       | 3<br>LSL<br>1 IX   | 2<br>PULX<br>1 INH | 1<br>CLC<br>1 INH | EOR<br>2 IMM      | 3<br>EOR<br>2 DIR | 4<br>EOR<br>3 EXT | 4<br>EOR<br>3 IX2 | 5<br>EOR<br>4 SP2 | 3<br>EOR<br>2 IX1 | 4<br>EOR<br>3 SP1 | EOR<br>1 IX      |

| 9          | 5<br>BRCLR4<br>3 DIR | 4<br>BCLR4<br>2 DIR | 3<br>BHCS<br>2 REL | 4<br>ROL<br>2 DIR  | 1<br>ROLA<br>1 INH  | 1<br>ROLX<br>1 INH  | 4<br>ROL<br>2 IX1   | 5<br>ROL<br>3 SP1       | 3<br>ROL<br>1 IX   | 2<br>PSHX<br>1 INH | 1<br>SEC<br>1 INH | 2<br>ADC<br>2 IMM | 3<br>ADC<br>2 DIR | 4<br>ADC<br>3 EXT | 4<br>ADC<br>3 IX2 | ADC<br>4 SP2      | 3<br>ADC<br>2 IX1 | 4<br>ADC<br>3 SP1 | 2<br>ADC<br>1 IX |

| Α          | 5<br>BRSET5<br>3 DIR | 4<br>BSET5<br>2 DIR | 3<br>BPL<br>2 REL  | 4<br>DEC<br>2 DIR  | 1<br>DECA<br>1 INH  | 1<br>DECX<br>1 INH  | 4<br>DEC<br>2 IX1   | 5<br>DEC<br>3 SP1       | 3<br>DEC<br>1 IX   | 2<br>PULH<br>1 INH | 2<br>CLI<br>1 INH | 2<br>ORA<br>2 IMM | 3<br>ORA<br>2 DIR | 4<br>ORA<br>3 EXT | 4<br>ORA<br>3 IX2 | 5<br>ORA<br>4 SP2 | 3<br>ORA<br>2 IX1 | 4<br>ORA<br>3 SP1 | 2<br>ORA<br>1 IX |

| В          | 5<br>BRCLR5<br>3 DIR | 4<br>BCLR5<br>2 DIR | 3<br>BMI<br>2 REL  | 5<br>DBNZ<br>3 DIR | 3<br>DBNZA<br>2 INH | 3<br>DBNZX<br>2 INH | 5<br>DBNZ<br>3 IX1  | 6<br>DBNZ<br>4 SP1      | 4<br>DBNZ<br>2 IX  | 2<br>PSHH<br>1 INH | SEI<br>1 INH      | ADD<br>2 IMM      | 3<br>ADD<br>2 DIR | 4<br>ADD<br>3 EXT | 4<br>ADD<br>3 IX2 | ADD<br>4 SP2      | 3<br>ADD<br>2 IX1 | 4<br>ADD<br>3 SP1 | ADD<br>1 IX      |

| с          | 5<br>BRSET6<br>3 DIR | 4<br>BSET6<br>2 DIR | 3<br>BMC<br>2 REL  | 4<br>INC<br>2 DIR  | 1<br>INCA<br>1 INH  | 1<br>INCX<br>1 INH  | 4<br>INC<br>2 IX1   | 5<br>INC<br>3 SP1       | 3<br>INC<br>1 IX   | 1<br>CLRH<br>1 INH | 1<br>RSP<br>1 INH |                   | 2<br>JMP<br>2 DIR | 3<br>JMP<br>3 EXT | 4<br>JMP<br>3 IX2 |                   | 3<br>JMP<br>2 IX1 |                   | 2<br>JMP<br>1 IX |

| D          | 5<br>BRCLR6<br>3 DIR | 4<br>BCLR6<br>2 DIR | 3<br>BMS<br>2 REL  | 3<br>TST<br>2 DIR  | 1<br>TSTA<br>1 INH  | 1<br>TSTX<br>1 INH  | 3<br>TST<br>2 IX1   | 4<br>TST<br>3 SP1       | 2<br>TST<br>1 IX   |                    | 1<br>NOP<br>1 INH | 4<br>BSR<br>2 REL | 4<br>JSR<br>2 DIR | 5<br>JSR<br>3 EXT | 6<br>JSR<br>3 IX2 |                   | 5<br>JSR<br>2 IX1 |                   | 4<br>JSR<br>1 IX |

| E          | 5<br>BRSET7<br>3 DIR | 4<br>BSET7<br>2 DIR | 3<br>BIL<br>2 REL  |                    | 5<br>MOV<br>3 DD    | 4<br>MOV<br>2 DIX+  | 4<br>MOV<br>3 IMD   |                         | 4<br>MOV<br>2 IX+D | 1<br>STOP<br>1 INH | *                 | 2<br>LDX<br>2 IMM | 3<br>LDX<br>2 DIR | 4<br>LDX<br>3 EXT | 4<br>LDX<br>3 IX2 | 5<br>LDX<br>4 SP2 | 3<br>LDX<br>2 IX1 | 4<br>LDX<br>3 SP1 | 2<br>LDX<br>1 IX |

| F          | 5<br>BRCLR7<br>3 DIR | 4<br>BCLR7<br>2 DIR | 3<br>BIH<br>2 REL  | 3<br>CLR<br>2 DIR  | 1<br>CLRA<br>1 INH  | 1<br>CLRX<br>1 INH  | 3<br>CLR<br>2 IX1   | 4<br>CLR<br>3 SP1       | 2<br>CLR<br>1 IX   | 1<br>WAIT<br>1 INH | 1<br>TXA<br>1 INH | AIX<br>2 IMM      | 3<br>STX<br>2 DIR | STX<br>3 EXT      | 4<br>STX<br>3 IX2 | STX<br>4 SP2      | 3<br>STX<br>2 IX1 | 4<br>STX<br>3 SP1 | 2<br>STX<br>1 IX |

Table 4-2. Opcode Map

- INH

Inherent

REL

Relative

IMM

Immediate

IX

Indexed, No Offset

DIR

Direct

IX1

Indexed, 8-Bit Offset

EXT

Extended

IX2

Indexed, 16-Bit Offset

DD

Direct-Direct

IX2

Indexed, 16-Bit Offset

DD

Direct-Direct

IMD

Immediate-Direct

IX4

DIX4

Direct-Indexed

SP1 Stack Pointer, 8-Bit Offset SP2 Stack Pointer, 16-Bit Offset IX+ Indexed, No Offset with Post Increment IX1+ Indexed, 1-Byte Offset with Post Increment

Low Byte of Opcode in Hexadecimal

High Byte of Opcode in Hexadecimal 0

MSB

LSB

0

5 BRSET0 Opcode Mnemonic 3 DIR Number of Bytes / Addressing Mode

\*Pre-byte for stack pointer indexed instructions

69

**Clock Generator Module (CGM)**

# 6.4.3 PLL Analog Ground Pin (V<sub>SSA</sub>)

$V_{\rm SSA}$  is a ground pin used by the analog portions of the PLL. Connect the  $V_{\rm SSA}$  pin to the same voltage potential as the  $V_{\rm SS}$  pin.

#### NOTE

Route  $V_{SSA}$  carefully for maximum noise immunity and place bypass capacitors as close as possible to the package.

# 6.4.4 Oscillator Output Frequency Signal (CGMXCLK)

CGMXCLK is the oscillator output signal. It runs at the full speed of the oscillator, and is generated directly from the crystal oscillator circuit, the RC oscillator circuit, or the internal oscillator circuit.

# 6.4.5 CGM Reference Clock (CGMRCLK)

CGMRCLK is a buffered version of CGMXCLK, this clock is the reference clock for the phase-locked-loop circuit.

# 6.4.6 CGM VCO Clock Output (CGMVCLK)

CGMVCLK is the clock output from the VCO.

# 6.4.7 CGM Base Clock Output (CGMOUT)

CGMOUT is the clock output of the CGM. This signal goes to the SIM, which generates the MCU clocks. CGMOUT is a 50 percent duty cycle clock running at twice the bus frequency. CGMOUT is software programmable to be either the oscillator output, CGMXCLK, divided by two or the divided VCO clock, CGMPCLK, divided by two.

# 6.4.8 CGM CPU Interrupt (CGMINT)

CGMINT is the interrupt signal generated by the PLL lock detector.

# 6.5 CGM Registers

The following registers control and monitor operation of the CGM:

- PLL control register (PCTL) (See 6.5.1 PLL Control Register.)

- PLL bandwidth control register (PBWC) (See 6.5.2 PLL Bandwidth Control Register.)

- PLL multiplier select registers (PMSH and PMSL) (See 6.5.3 PLL Multiplier Select Registers.)

- PLL VCO range select register (PMRS) (See 6.5.4 PLL VCO Range Select Register.)

- PLL reference divider select register (PMDS) (See 6.5.5 PLL Reference Divider Select Register.)

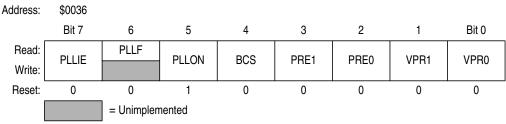

# 6.5.1 PLL Control Register

The PLL control register (PCTL) contains the interrupt enable and flag bits, the on/off switch, the base clock selector bit, the prescaler bits, and the VCO power-of-two range selector bits.

#### Figure 6-4. PLL Control Register (PCTL)

#### PLLIE — PLL Interrupt Enable Bit

This read/write bit enables the PLL to generate an interrupt request when the LOCK bit toggles, setting the PLL flag, PLLF. When the AUTO bit in the PLL bandwidth control register (PBWC) is clear, PLLIE cannot be written and reads as logic 0. Reset clears the PLLIE bit.

1 = PLL interrupts enabled

0 = PLL interrupts disabled

## PLLF — PLL Interrupt Flag Bit

This read-only bit is set whenever the LOCK bit toggles. PLLF generates an interrupt request if the PLLIE bit also is set. PLLF always reads as logic 0 when the AUTO bit in the PLL bandwidth control register (PBWC) is clear. Clear the PLLF bit by reading the PLL control register. Reset clears the PLLF bit.

1 = Change in lock condition

0 = No change in lock condition

#### NOTE

Do not inadvertently clear the PLLF bit. Any read or read-modify-write operation on the PLL control register clears the PLLF bit.

#### PLLON — PLL On Bit

This read/write bit activates the PLL and enables the VCO clock, CGMVCLK. PLLON cannot be cleared if the VCO clock is driving the base clock, CGMOUT (BCS = 1). (See 6.3.8 Base Clock Selector Circuit.) Reset sets this bit so that the loop can stabilize as the MCU is powering up.

1 = PLL on

0 = PLL off

#### BCS — Base Clock Select Bit

This read/write bit selects either the oscillator output, CGMXCLK, or the divided VCO clock, CGMPCLK, as the source of the CGM output, CGMOUT. CGMOUT frequency is one-half the frequency of the selected clock. BCS cannot be set while the PLLON bit is clear. After toggling BCS, it may take up to three CGMXCLK and three CGMPCLK cycles to complete the transition from one source clock to the other. During the transition, CGMOUT is held in stasis. (See 6.3.8 Base Clock Selector Circuit.) Reset clears the BCS bit.

1 = CGMPCLK divided by two drives CGMOUT

0 = CGMXCLK divided by two drives CGMOUT

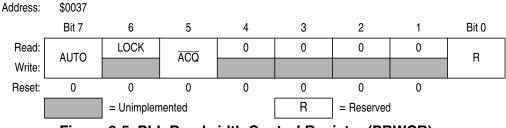

# 6.5.2 PLL Bandwidth Control Register

The PLL bandwidth control register (PBWC):

- · Selects automatic or manual (software-controlled) bandwidth control mode

- Indicates when the PLL is locked

- In automatic bandwidth control mode, indicates when the PLL is in acquisition or tracking mode

- In manual operation, forces the PLL into acquisition or tracking mode

Figure 6-5. PLL Bandwidth Control Register (PBWCR)

#### AUTO — Automatic Bandwidth Control Bit

This read/write bit selects automatic or manual bandwidth control. When initializing the PLL for manual operation (AUTO = 0), clear the  $\overline{ACQ}$  bit before turning on the PLL. Reset clears the AUTO bit.

- 1 = Automatic bandwidth control

- 0 = Manual bandwidth control

#### LOCK — Lock Indicator Bit

When the AUTO bit is set, LOCK is a read-only bit that becomes set when the VCO clock, CGMVCLK, is locked (running at the programmed frequency). When the AUTO bit is clear, LOCK reads as logic 0 and has no meaning. The write one function of this bit is reserved for test, so this bit must *always* be written a 0. Reset clears the LOCK bit.

1 = VCO frequency correct or locked

0 = VCO frequency incorrect or unlocked

#### ACQ — Acquisition Mode Bit

When the AUTO bit is set,  $\overline{ACQ}$  is a read-only bit that indicates whether the PLL is in acquisition mode or tracking mode. When the AUTO bit is clear,  $\overline{ACQ}$  is a read/write bit that controls whether the PLL is in acquisition or tracking mode.

In automatic bandwidth control mode (AUTO = 1), the last-written value from manual operation is stored in a temporary location and is recovered when manual operation resumes. Reset clears this bit, enabling acquisition mode.

1 = Tracking mode

0 = Acquisition mode

#### **SIM Bus Clock Control and Generation**

|                                           |                                              | Read:  | IF6  | IF5       | IF4    | IF3  | IF2  | IF1  | 0    | 0    |

|-------------------------------------------|----------------------------------------------|--------|------|-----------|--------|------|------|------|------|------|

| \$FE04                                    | \$FE04 Interrupt Status Register 1<br>(INT1) | Write: | R    | R         | R      | R    | R    | R    | R    | R    |

|                                           | ()                                           | Reset: | 0    | 0         | 0      | 0    | 0    | 0    | 0    | 0    |

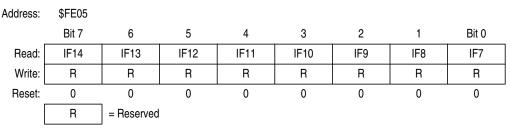

|                                           |                                              | Read:  | IF14 | IF13      | IF12   | IF11 | IF10 | IF9  | IF8  | IF7  |

| \$FE05                                    | \$FE05 Interrupt Status Register 2<br>(INT2) | Write: | R    | R         | R      | R    | R    | R    | R    | R    |

|                                           | ()                                           | Reset: | 0    | 0         | 0      | 0    | 0    | 0    | 0    | 0    |

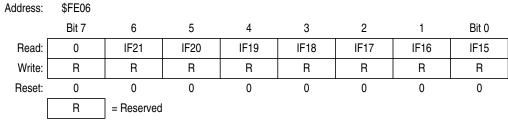

|                                           | Interrupt Statue Degister 2                  | Read:  | 0    | IF21      | IF20   | IF19 | IF18 | IF17 | IF16 | IF15 |

| \$FE06 Interrupt Status Register 3 (INT3) | Write:                                       | R      | R    | R         | R      | R    | R    | R    | R    |      |

|                                           | (                                            | Reset: | 0    | 0         | 0      | 0    | 0    | 0    | 0    | 0    |

|                                           |                                              |        |      | = Unimple | mented |      |      |      |      |      |

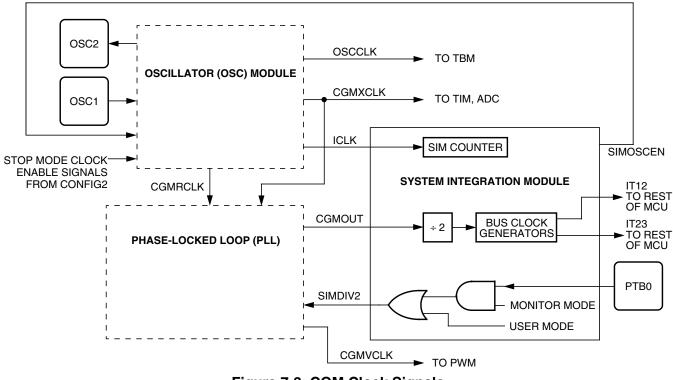

# 7.2 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, CGMOUT, as shown in Figure 7-3. This clock can come from either an external oscillator or from the on-chip PLL. (See Chapter 6 Clock Generator Module (CGM).)

Figure 7-3. CGM Clock Signals

# 7.2.1 Bus Timing

In user mode, the internal bus frequency is either the oscillator output (CGMXCLK) divided by four or the divided PLL output (CGMPCLK) divided by four.

#### System Integration Module (SIM)

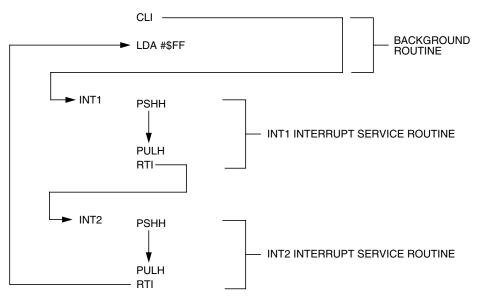

The LDA opcode is prefetched by both the INT1 and INT2 RTI instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

#### NOTE

To maintain compatibility with the M6805 Family, the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, software should save the H register and then restore it prior to exiting the routine.

#### 7.5.1.2 SWI Instruction

The SWI instruction is a non-maskable instruction that causes an interrupt regardless of the state of the interrupt mask (I bit) in the condition code register.

#### NOTE

A software interrupt pushes PC onto the stack. A software interrupt does not push PC – 1, as a hardware interrupt does.

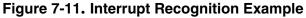

#### 7.5.2 Interrupt Status Registers

The flags in the interrupt status registers identify maskable interrupt sources. Table 7-3 summarizes the interrupt sources and the interrupt status register flags that they set. The interrupt status registers can be useful for debugging.

#### 7.5.2.1 Interrupt Status Register 1

Figure 7-12. Interrupt Status Register 1 (INT1)

#### IF6-IF1 — Interrupt Flags 6-1

These flags indicate the presence of interrupt requests from the sources shown in Table 7-3.

1 = Interrupt request present

0 = No interrupt request present

#### Bit 0 and Bit 1 — Always read 0

#### 7.5.2.2 Interrupt Status Register 2

#### Figure 7-13. Interrupt Status Register 2 (INT2)

#### IF14–IF7 — Interrupt Flags 14–7

These flags indicate the presence of interrupt requests from the sources shown in Table 7-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### 7.5.2.3 Interrupt Status Register 3

#### Figure 7-14. Interrupt Status Register 3 (INT3)

#### IF21–IF15 — Interrupt Flags 21–15

These flags indicate the presence of an interrupt request from the source shown in Table 7-3.

1 = Interrupt request present

0 = No interrupt request present

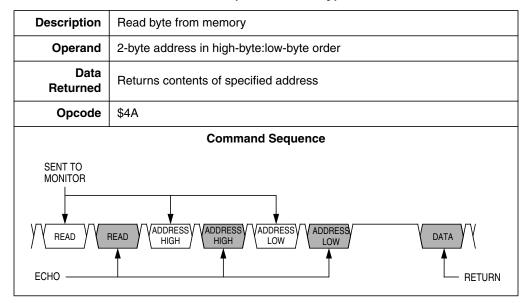

## Table 8-4. READ (Read Memory) Command

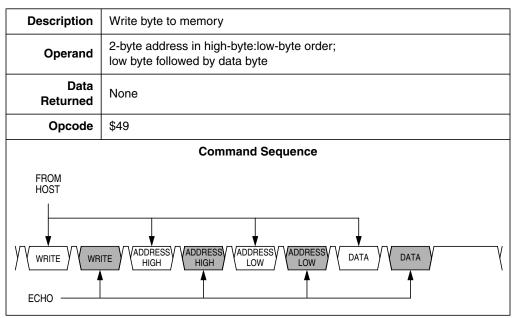

#### Table 8-5. WRITE (Write Memory) Command

The maximum percent difference between the receiver count and the transmitter count of a slow 9-bit character with no errors is

$$\left|\frac{170 - 163}{170}\right| \times 100 = 4.12\%$$

#### Fast Data Tolerance

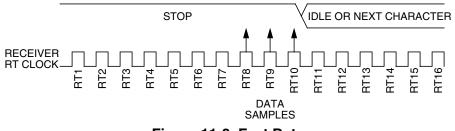

Figure 11-8 shows how much a fast received character can be misaligned without causing a noise error or a framing error. The fast stop bit ends at RT10 instead of RT16 but is still there for the stop bit data samples at RT8, RT9, and RT10.

For an 8-bit character, data sampling of the stop bit takes the receiver 9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 11-8, the receiver counts 154 RT cycles at the point when the count of the transmitting device is

10 bit times  $\times$  16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is

$$\left|\frac{154 - 160}{154}\right| \times 100 = 3.90\%$$

For a 9-bit character, data sampling of the stop bit takes the receiver 10 bit times  $\times$  16 RT cycles + 10 RT cycles = 170 RT cycles.

With the misaligned character shown in Figure 11-8, the receiver counts 170 RT cycles at the point when the count of the transmitting device is

11 bit times  $\times$  16 RT cycles = 176 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 9-bit character with no errors is

$$\left|\frac{170 - 176}{170}\right| \times 100 = 3.53\%$$

#### 11.4.3.6 Receiver Wakeup

So that the MCU can ignore transmissions intended only for other receivers in multiple-receiver systems, the receiver can be put into a standby state. Setting the receiver wakeup bit, RWU, in SCC2 puts the receiver into a standby state during which receiver interrupts are disabled.

#### Serial Communications Interface Module (SCI)

Depending on the state of the WAKE bit in SCC1, either of two conditions on the RxD pin can bring the receiver out of the standby state:

- Address mark An address mark is a logic 1 in the most significant bit position of a received character. When the WAKE bit is set, an address mark wakes the receiver from the standby state by clearing the RWU bit. The address mark also sets the SCI receiver full bit, SCRF. Software can then compare the character containing the address mark to the user-defined address of the receiver. If they are the same, the receiver remains awake and processes the characters that follow. If they are not the same, software can set the RWU bit and put the receiver back into the standby state.

- Idle input line condition When the WAKE bit is clear, an idle character on the RxD pin wakes the

receiver from the standby state by clearing the RWU bit. The idle character that wakes the receiver

does not set the receiver idle bit, IDLE, or the SCI receiver full bit, SCRF. The idle line type bit,

ILTY, determines whether the receiver begins counting logic 1s as idle character bits after the start

bit or after the stop bit.

#### NOTE

With the WAKE bit clear, setting the RWU bit after the RxD pin has been idle may cause the receiver to wake up immediately.

#### 11.4.3.7 Receiver Interrupts

The following sources can generate CPU interrupt requests from the SCI receiver:

- SCI receiver full (SCRF) The SCRF bit in SCS1 indicates that the receive shift register has transferred a character to the SCDR. SCRF can generate a receiver CPU interrupt request. Setting the SCI receive interrupt enable bit, SCRIE, in SCC2 enables the SCRF bit to generate receiver CPU interrupts.

- Idle input (IDLE) The IDLE bit in SCS1 indicates that 10 or 11 consecutive logic 1s shifted in from the RxD pin. The idle line interrupt enable bit, ILIE, in SCC2 enables the IDLE bit to generate CPU interrupt requests.

#### 11.4.3.8 Error Interrupts

The following receiver error flags in SCS1 can generate CPU interrupt requests:

- Receiver overrun (OR) The OR bit indicates that the receive shift register shifted in a new character before the previous character was read from the SCDR. The previous character remains in the SCDR, and the new character is lost. The overrun interrupt enable bit, ORIE, in SCC3 enables OR to generate SCI error CPU interrupt requests.

- Noise flag (NF) The NF bit is set when the SCI detects noise on incoming data or break characters, including start, data, and stop bits. The noise error interrupt enable bit, NEIE, in SCC3 enables NF to generate SCI error CPU interrupt requests.

- Framing error (FE) The FE bit in SCS1 is set when a logic 0 occurs where the receiver expects a stop bit. The framing error interrupt enable bit, FEIE, in SCC3 enables FE to generate SCI error CPU interrupt requests.

- Parity error (PE) The PE bit in SCS1 is set when the SCI detects a parity error in incoming data. The parity error interrupt enable bit, PEIE, in SCC3 enables PE to generate SCI error CPU interrupt requests.

#### Serial Communications Interface Module (SCI)

#### NEIE — Receiver Noise Error Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt requests generated by the noise error bit, NE. Reset clears NEIE.

- 1 = SCI error CPU interrupt requests from NE bit enabled

- 0 = SCI error CPU interrupt requests from NE bit disabled

#### FEIE — Receiver Framing Error Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt requests generated by the framing error bit, FE. Reset clears FEIE.

- 1 = SCI error CPU interrupt requests from FE bit enabled

- 0 = SCI error CPU interrupt requests from FE bit disabled

#### PEIE — Receiver Parity Error Interrupt Enable Bit

This read/write bit enables SCI error CPU interrupt

requests generated by the parity error bit, PE. (See 11.8.4 SCI Status Register 1.) Reset clears PEIE.

- 1 = SCI error CPU interrupt requests from PE bit enabled

- 0 = SCI error CPU interrupt requests from PE bit disabled

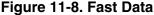

#### 11.8.4 SCI Status Register 1

SCI status register 1 (SCS1) contains flags to signal these conditions:

- Transfer of SCDR data to transmit shift register complete

- Transmission complete

- Transfer of receive shift register data to SCDR complete

- Receiver input idle

- Receiver overrun

- Noisy data

- Framing error

- Parity error

#### Figure 11-12. SCI Status Register 1 (SCS1)

#### SCTE — SCI Transmitter Empty Bit

This clearable, read-only bit is set when the SCDR transfers a character to the transmit shift register. SCTE can generate an SCI transmitter CPU interrupt request. When the SCTIE bit in SCC2 is set, SCTE generates an SCI transmitter CPU interrupt request. In normal operation, clear the SCTE bit by reading SCS1 with SCTE set and then writing to SCDR. Reset sets the SCTE bit.

- 1 = SCDR data transferred to transmit shift register

- 0 = SCDR data not transferred to transmit shift register

# Chapter 12 Infrared Serial Communications Interface Module (IRSCI)

# 12.1 Introduction

The MC68HC908AP64 has two SCI modules:

- SCI1 is a standard SCI module, and

- SCI2 is an infrared SCI module.

This section describes SCI2, the infrared serial communications interface (IRSCI) module which allows high-speed asynchronous communications with peripheral devices and other MCUs. This IRSCI consists of an SCI module for conventional SCI functions and a software programmable infrared encoder/decoder sub-module for encoding/decoding the serial data for connection to infrared LEDs in remote control applications.

# NOTE

# When the IRSCI is enabled, the SCTxD pin is an open-drain output and requires a pullup resistor to be connected for proper SCI operation.

Features of the SCI module include the following:

- Full duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- Programmable 8-bit or 9-bit character length

- Separately enabled transmitter and receiver

- Separate receiver and transmitter CPU interrupt requests

- Two receiver wakeup methods:

- Idle line wakeup

- Address mark wakeup

- Interrupt-driven operation with eight interrupt flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

Features of the infrared (IR) sub-module include the following:

- IR sub-module enable/disable for infrared SCI or conventional SCI on SCTxD and SCRxD pins

- Software selectable infrared modulation/demodulation (3/16, 1/16 or 1/32 width pulses)

# 12.5 SCI Functional Description

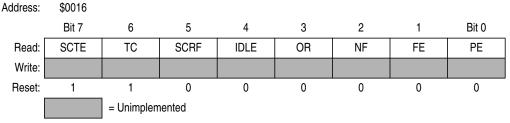

Figure 12-5 shows the structure of the SCI.

Figure 12-5. SCI Module Block Diagram

#### Infrared Serial Communications Interface Module (IRSCI)

- IRSCI status register 1 (IRSCS1)

- IRSCI status register 2 (IRSCS2)

- IRSCI data register (IRSCDR)

- IRSCI baud rate register (IRSCBR)

- IRSCI infrared control register (IRSCIRCR)

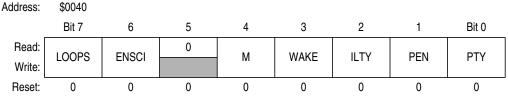

#### 12.9.1 IRSCI Control Register 1

SCI control register 1:

- Enables loop mode operation

- Enables the SCI

- Controls output polarity

- Controls character length

- Controls SCI wakeup method

- Controls idle character detection

- Enables parity function

- Controls parity type

#### Figure 12-12. IRSCI Control Register 1 (IRSCC1)

#### LOOPS — Loop Mode Select Bit

This read/write bit enables loop mode operation for the SCI only. In loop mode the RxD pin is disconnected from the SCI, and the transmitter output goes into the receiver input. Both the transmitter and the receiver must be enabled to use loop mode. The infrared encoder/decoder is not in the loop. Reset clears the LOOPS bit.

- 1 = Loop mode enabled

- 0 = Normal operation enabled

#### ENSCI — Enable SCI Bit

This read/write bit enables the SCI and the SCI baud rate generator. Clearing ENSCI sets the SCTE and TC bits in SCI status register 1 and disables transmitter interrupts. Reset clears the ENSCI bit.

1 = SCI enabled

0 = SCI disabled

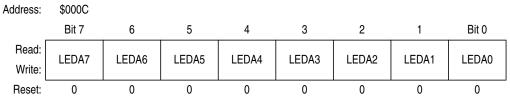

The port-A LED control register (LEDA) controls the direct LED drive capability on PTA7–PTA0 pins. Each bit is individually configurable and requires that the data direction register, DDRA, bit be configured as an output.

Figure 16-5. Port A LED Control Register (LEDA)

#### LEDA[7:0] — Port A LED Drive Enable Bits

These read/write bits are software programmable to enable the direct LED drive on an output port pin.

- 1 = Corresponding port A pin is configured for direct LED drive,

- with 15mA current sinking capability

- 0 = Corresponding port A pin is configured for standard drive

# 16.3 Port B

Port B is an 8-bit special-function port that shares two of its pins with the multi-master IIC (MMIIC) module, two of its pins with SCI module, and four of its pins with two timer interface (TIM1 and TIM2) modules.

#### NOTE

PTB3–PTB0 are open-drain pins when configured as outputs regardless whether the pins are used as general purpose I/O pins, MMIIC pins, or SCI pins. Therefore, when configured as general purpose output pins, MMIIC pins, or SCI pins (the TxD pin), pullup resistors must be connected to these pins.

# 16.3.1 Port B Data Register (PTB)

The port B data register contains a data latch for each of the eight port B pins.

| Address:                   | \$0001 |       |       |       |      |      |      |       |  |  |

|----------------------------|--------|-------|-------|-------|------|------|------|-------|--|--|

|                            | Bit 7  | 6     | 5     | 4     | 3    | 2    | 1    | Bit 0 |  |  |

| Read:<br>Write:            | PTB7   | PTB6  | PTB5  | PTB4  | PTB3 | PTB2 | PTB1 | PTB0  |  |  |

| Reset: Unaffected by reset |        |       |       |       |      |      |      |       |  |  |

| Alternative Function:      | T2CH1  | T2CH0 | T1CH1 | T1CH0 | RxD  | TxD  | SCL  | SDA   |  |  |

Figure 16-6. Port B Data Register (PTB)

#### PTB[7:0] — Port B Data Bits

These read/write bits are software-programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

**Electrical Specifications**

# 22.15 5V SPI Characteristics

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                        | Symbol                                       | Min                                              | Max                                   | Unit                                 |

|----------------------------------|----------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------|---------------------------------------|--------------------------------------|

|                                  | Operating frequency<br>Master<br>Slave                               | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub>     | f <sub>OP</sub> /128<br>dc                       | f <sub>OP</sub> /2<br>f <sub>OP</sub> | MHz<br>MHz                           |

| 1                                | Cycle time<br>Master<br>Slave                                        | t <sub>CYC(M)</sub><br>t <sub>CYC(S)</sub>   | 2<br>1                                           | 128<br>—                              | t <sub>CYC</sub><br>t <sub>CYC</sub> |

| 2                                | Enable lead time                                                     | t <sub>Lead(S)</sub>                         | 1                                                |                                       | t <sub>CYC</sub>                     |

| 3                                | Enable lag time                                                      | t <sub>Lag(S)</sub>                          | 1                                                |                                       | t <sub>CYC</sub>                     |

| 4                                | Clock (SPSCK) high time<br>Master<br>Slave                           | t <sub>SCKH(M)</sub><br>t <sub>SCKH(S)</sub> | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns                             |

| 5                                | Clock (SPSCK) low time<br>Master<br>Slave                            | t <sub>SCKL(M)</sub><br>t <sub>SCKL(S)</sub> | t <sub>CYC</sub> –25<br>1/2 t <sub>CYC</sub> –25 | 64 t <sub>CYC</sub>                   | ns<br>ns                             |

| 6                                | Data setup time (inputs)<br>Master<br>Slave                          | t <sub>SU(M)</sub><br>t <sub>SU(S)</sub>     | 30<br>30                                         |                                       | ns<br>ns                             |

| 7                                | Data hold time (inputs)<br>Master<br>Slave                           | t <sub>H(M)</sub><br>t <sub>H(S)</sub>       | 30<br>30                                         |                                       | ns<br>ns                             |

| 8                                | Access time, slave <sup>(3)</sup><br>CPHA = 0<br>CPHA = 1            | t <sub>A(CP0)</sub><br>t <sub>A(CP1)</sub>   | 0<br>0                                           | 40<br>40                              | ns<br>ns                             |

| 9                                | Disable time, slave <sup>(4)</sup>                                   | t <sub>DIS(S)</sub>                          | _                                                | 40                                    | ns                                   |

| 10                               | Data valid time, after enable edge<br>Master<br>Slave <sup>(5)</sup> | t <sub>V(M)</sub><br>t <sub>V(S)</sub>       | _                                                | 50<br>50                              | ns<br>ns                             |

| 11                               | Data hold time, outputs, after enable edge<br>Master<br>Slave        | t <sub>HO(M)</sub><br>t <sub>HO(S)</sub>     | 0<br>0                                           |                                       | ns<br>ns                             |

Table 22-15. SPI Characteristics (5V)

Numbers refer to dimensions in Figure 22-3 and Figure 22-4.

All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins.

Time to data active from high-impedance state

Hold time to high-impedance state

With 100 pF on all SPI pins