#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | HC08                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | I <sup>2</sup> C, IRSCI, SCI, SPI                         |

| Peripherals                | LED, LVD, POR, PWM                                        |

| Number of I/O              | 30                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 2K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                 |

| Supplier Device Package    | 42-PDIP                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908ap32cbe |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

\_\_\_\_\_

| Date         | Revision<br>Level                                                              | Description                                                                                                                                                                                                                                            | Page<br>Number(s) |

|--------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| January 2007 | 4                                                                              | 15.7.2 ADC Clock Control Register — Changed "The ADC clock should<br>be set to between 500kHz and 2MHz" to "The ADC clock should be set<br>to between 500kHz and 1MHz"                                                                                 | 254               |

|              |                                                                                | Table 22-4 . DC Electrical Characteristics (5V) — Updated $V_{OL}$ values.                                                                                                                                                                             | 299               |

| August 2005  | 3                                                                              | Table 22-6 . Oscillator Specifications (5V) and Table 22-10 . Oscillator Specifications (3V) — Corrected internal oscillator clock frequency, $f_{\rm ICLK}$ . Updated crystal oscillator component values $C_L$ , $C_1$ , $C_2$ , $R_B$ , and $R_S$ . | 301, 305          |

|              |                                                                                | Added MC68HC908AP16/AP8 information throughout.                                                                                                                                                                                                        |                   |

| October 2003 | 2.5                                                                            | Section 10. Monitor ROM (MON) — Corrected RAM address to \$60.                                                                                                                                                                                         | 167               |

|              |                                                                                | Section 24. Electrical Specifications — Added run and wait $\rm I_{\rm DD}$ data for 8MHz at 3V.                                                                                                                                                       | 421               |

| August 2003  | 2.4                                                                            | Section 24. Electrical Specifications — Updated stop I <sub>DD</sub> data.                                                                                                                                                                             | 417, 421          |

|              | 2.3                                                                            | Removed MC68HC908AP16 references throughout.                                                                                                                                                                                                           |                   |

|              |                                                                                | Table 1-2 . Pin Functions — Added footnote for V <sub>REG</sub> .                                                                                                                                                                                      | 30                |

|              |                                                                                | 5.3 Configuration Register 1 (CONFIG1) — Clarified LVIPWRD and LVIREGD bits.                                                                                                                                                                           | 67                |

| July 2003    |                                                                                | Section 8. Clock Generator Module (CGM), 8.7.2 Stop Mode — Updated BSC bit behavior.                                                                                                                                                                   | 125               |

|              |                                                                                | 10.5 ROM-Resident Routines — Corrected data size limits and control byte size for EE_READ and EE_WRITE.                                                                                                                                                |                   |

|              | Figure 12-2 . Timebase Control Register (TBCR) — Corrected register address.   |                                                                                                                                                                                                                                                        | 207               |

|              |                                                                                | Section 24. Electrical Specifications — Updated.                                                                                                                                                                                                       | 415               |

| May 2003     | Updated for f <sub>NOM</sub> = 125kHz and filter components<br>in CGM section. |                                                                                                                                                                                                                                                        | 101               |

|              |                                                                                | Updated electricals.                                                                                                                                                                                                                                   | 415               |

\_\_\_\_\_

| 6.3.9 | CGM External Connections                        |

|-------|-------------------------------------------------|

| 6.4   | I/O Signals                                     |

| 6.4.1 | External Filter Capacitor Pin (CGMXFC) 87       |

| 6.4.2 | PLL Analog Power Pin (V <sub>DDA</sub> )        |

| 6.4.3 | PLL Analog Ground Pin (V <sub>SSA</sub> )       |

| 6.4.4 | Oscillator Output Frequency Signal (CGMXCLK) 88 |

| 6.4.5 | CGM Reference Clock (CGMRCLK) 88                |

| 6.4.6 | CGM VCO Clock Output (CGMVCLK) 88               |

| 6.4.7 | CGM Base Clock Output (CGMOUT) 88               |

| 6.4.8 | CGM CPU Interrupt (CGMINT) 88                   |

| 6.5   | CGM Registers                                   |

| 6.5.1 | PLL Control Register                            |

| 6.5.2 | PLL Bandwidth Control Register                  |

| 6.5.3 | PLL Multiplier Select Registers                 |

| 6.5.4 | PLL VCO Range Select Register                   |

| 6.5.5 | PLL Reference Divider Select Register           |

| 6.6   | Interrupts                                      |

| 6.7   | Special Modes                                   |

| 6.7.1 | Wait Mode                                       |

| 6.7.2 | Stop Mode                                       |

| 6.7.3 | CGM During Break Interrupts                     |

| 6.8   | Acquisition/Lock Time Specifications            |

| 6.8.1 | Acquisition/Lock Time Definitions               |

| 6.8.2 | Parametric Influences on Reaction Time          |

| 6.8.3 | Choosing a Filter                               |

# Chapter 7 System Integration Module (SIM)

| 7.1     | Introduction                               | 97 |

|---------|--------------------------------------------|----|

| 7.2     | SIM Bus Clock Control and Generation       | 99 |

| 7.2.1   | Bus Timing                                 | 99 |

| 7.2.2   | Clock Start-up from POR or LVI Reset 10    | 00 |

| 7.2.3   | Clocks in Stop Mode and Wait Mode 10       | 00 |

| 7.3     | Reset and System Initialization 10         | 00 |

| 7.3.1   | External Pin Reset                         | 00 |

| 7.3.2   | Active Resets from Internal Sources 10     | D1 |

| 7.3.2.1 | Power-On Reset                             | D1 |

| 7.3.2.2 | Computer Operating Properly (COP) Reset 10 | 02 |

| 7.3.2.3 | Illegal Opcode Reset                       |    |

| 7.3.2.4 | Illegal Address Reset                      | 03 |

| 7.3.2.5 | Low-Voltage Inhibit (LVI) Reset 10         | 03 |

| 7.3.2.6 | Monitor Mode Entry Module Reset 10         | 03 |

| 7.4     | SIM Counter                                | 03 |

| 7.4.1   | SIM Counter During Power-On Reset 10       | 03 |

| 7.4.2   | SIM Counter During Stop Mode Recovery      | 03 |

| 7.4.3   | SIM Counter and Reset States 10            |    |

| 7.5     | Exception Control                          | 04 |

**General Description**

| PIN NAME                 | PIN DESCRIPTION                                                                                                            | IN/OUT | VOLTAGE<br>LEVEL |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------|--------|------------------|

|                          | 8-bit general purpose I/O port; PTB0–PTB3 are open drain when configured as output. PTB4–PTB7 have schmitt trigger inputs. | In/Out | V <sub>DD</sub>  |

|                          | PTB0 as SDA of MMIIC.                                                                                                      | In/Out | V <sub>DD</sub>  |

| PTB0/SDA<br>PTB1/SCL     | PTB1 as SCL of MMIIC.                                                                                                      | In/Out | V <sub>DD</sub>  |

| PTB2/TxD                 | PTB2 as TxD of SCI; open drain output.                                                                                     | Out    | V <sub>DD</sub>  |

| PTB3/RxD<br>PTB4/T1CH0   | PTB3 as RxD of SCI.                                                                                                        | In     | V <sub>DD</sub>  |

| PTB5/T1CH1<br>PTB6/T2CH0 | PTB4 as T1CH0 of TIM1.                                                                                                     | In/Out | V <sub>DD</sub>  |

| PTB7/T2CH1               | PTB5 as T1CH1 of TIM1.                                                                                                     | In/Out | V <sub>DD</sub>  |

|                          | PTB6 as T2CH0 of TIM2.                                                                                                     | In/Out | V <sub>DD</sub>  |

|                          | PTB7 as T2CH1 of TIM2.                                                                                                     | In/Out | V <sub>DD</sub>  |

|                          | 8-bit general purpose I/O port; PTC6 and PTC7 are open drain when configured as output.                                    | In/Out | V <sub>DD</sub>  |

| PTC0/IRQ2                | PTC0 is shared with IRQ2 and has schmitt trigger input.                                                                    | In     | V <sub>DD</sub>  |

| PTC1<br>PTC2/MISO        | PTC2 as MISO of SPI.                                                                                                       | In     | V <sub>DD</sub>  |

| PTC3/MOSI                | PTC3 as MOSI of SPI.                                                                                                       | Out    | V <sub>DD</sub>  |

| PTC4/SS<br>PTC5/SPSCK    | PTC4 as SS of SPI.                                                                                                         | In     | V <sub>DD</sub>  |

| PTC6/SCTxD<br>PTC7/SCRxD | PTC5 as SPSCK of SPI.                                                                                                      | In/Out | V <sub>DD</sub>  |

|                          | PTC6 as SCTxD of IRSCI; open drain output.                                                                                 | Out    | V <sub>DD</sub>  |

|                          | PTC7 as SCRxD of IRSCI.                                                                                                    | In     | V <sub>DD</sub>  |

| PTD0/KBI0                | 8-bit general purpose I/O port with schmitt trigger inputs.                                                                | In/Out | V <sub>DD</sub>  |

| :<br>PTD7/KBI7           | Pins as keyboard interrupts (with pullup), KBI0-KBI7.                                                                      | In     | V <sub>DD</sub>  |

## Table 1-2. Pin Functions

1. See Chapter 22 Electrical Specifications for  $V_{\mbox{\scriptsize REG}}$  tolerance.

# 1.6 Power Supply Bypassing (VDD, VDDA, VSS, VSSA)

$V_{\text{DD}}$  and  $V_{\text{SS}}$  are the power supply and ground pins, the MCU operates from a single power supply together with an on chip voltage regulator.

Fast signal transitions on MCU pins place high. short-duration current demands on the power supply. To prevent noise problems, take special care to provide power supply bypassing at the MCU as Figure 1-5 shows. Place the bypass capacitors as close to the MCU power pins as possible. Use high-frequency-response ceramic capacitor for  $C_{BYPASS}$ ,  $C_{BULK}$  are optional bulk current bypass capacitors for use in applications that require the port pins to source high current level.

Configuration & Mask Option Registers (CONFIG & MOR)

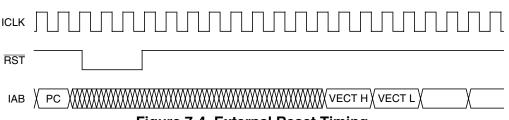

Figure 7-4. External Reset Timing

## 7.3.2 Active Resets from Internal Sources

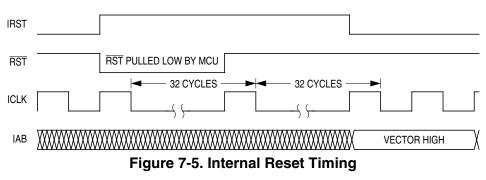

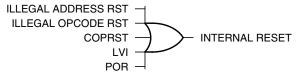

All internal reset sources actively pull the RST pin low for 32 ICLK cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (see Figure 7-5). An internal reset can be caused by an illegal address, illegal opcode, COP timeout, LVI, or POR (see Figure 7-6).

**NOTE** For LVI or POR resets, the SIM cycles through 4096 + 32 ICLK cycles during which the SIM forces the RST pin low. The internal reset signal then follows the sequence from the falling edge of RST shown in Figure 7-5.

The COP reset is asynchronous to the bus clock.

The active reset feature allows the part to issue a reset to peripherals and other chips within a system built around the MCU.

## 7.3.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power-on has occurred. The external reset pin ( $\overline{\text{RST}}$ ) is held low while the SIM counter counts out 4096 + 32 ICLK cycles. Thirty-two ICLK cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

### System Integration Module (SIM)

| Priority | INT<br>Flag | Vector<br>Address | Interrupt Source        |

|----------|-------------|-------------------|-------------------------|

| Lowest   |             | \$FFD0            | Deserved                |

|          | _           | \$FFD1            | Reserved                |

|          | IF21        | \$FFD2            | Timehaaa                |

|          |             | \$FFD3            | Timebase                |

|          | 1500        | \$FFD4            | Infrared SCI Transmit   |

|          | IF20        | \$FFD5            | Infrared SCI Transmit   |

|          | 1510        | \$FFD6            | Infrared CCI Dessive    |

|          | IF19        | \$FFD7            | Infrared SCI Receive    |

|          | IF18        | \$FFD8            | Infrared SCI Error      |

|          |             | \$FFD9            |                         |

|          | IF17        | \$FFDA            | SPI Transmit            |

|          |             | \$FFDB            | SFI Hanshin             |

|          | IF16        | \$FFDC            | SPI Receive             |

|          |             | \$FFDD            |                         |

|          | IF15        | \$FFDE            | ADC Conversion Complete |

|          |             | \$FFDF            | ADC Conversion Complete |

|          | IF14        | \$FFE0            | Keyboard                |

|          |             | \$FFE1            | Reyboard                |

|          | IF13        | \$FFE2            | SCI Transmit            |

|          |             | \$FFE3            | Sor mansmit             |

|          | IF12        | \$FFE4            | SCI Receive             |

|          |             | \$FFE5            |                         |

|          | IF11        | \$FFE6<br>\$FFE7  | SCI Error               |

|          |             | \$FFE8            |                         |

|          | IF10        | \$FFE9            | MMIIC                   |

|          |             | \$FFEA            |                         |

|          | IF9         | \$FFEB            | TIM2 Overflow           |

|          | 1=0         | \$FFEC            |                         |

|          | IF8         | \$FFED            | TIM2 Channel 1          |

|          |             | \$FFEE            |                         |

|          | IF7         | \$FFEF            | TIM2 Channel 0          |

|          | 150         | \$FFF0            |                         |

|          | IF6         | \$FFF1            | TIM1 Overflow           |

|          | 15-         | \$FFF2            | TIMA Observatia         |

|          | IF5         | \$FFF3            | TIM1 Channel 1          |

|          |             | \$FFF4            |                         |

|          | IF4         | \$FFF5            | TIM1 Channel 0          |

|          | 150         | \$FFF6            |                         |

|          | IF3         | \$FFF7            | PLL                     |

|          | IF2         | \$FFF8<br>\$FFF9  | IRQ2                    |

|          |             | \$FFFA            |                         |

|          | IF1         | \$FFFB            | IRQ1                    |

|          |             | \$FFFC            |                         |

|          | -           | \$FFFD            | SWI                     |

| ▼        |             | \$FFFE            | _                       |

| Highest  | -           | \$FFFF            | Reset                   |

|          |             | ψιτι              |                         |

## Table 7-3. Interrupt Sources

Monitor ROM (MON)

## 8.5.6 EE\_WRITE

EE\_WRITE is used to write a set of data from the data array to FLASH.

Table 8-16. EE\_WRITE Routine

| Routine Name        | EE_WRITE                                                                                                                                                                  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Routine Description | Emulated EEPROM write. Data size ranges from 7 to 15 bytes at a time.                                                                                                     |  |  |  |

| Calling Address     | \$FF36                                                                                                                                                                    |  |  |  |

| Stack Used          | 30 bytes                                                                                                                                                                  |  |  |  |

| Data Block Format   | Bus speed (BUS_SPD)<br>Data size (DATASIZE) <sup>(1)</sup><br>Starting address (ADDRH) <sup>(2)</sup><br>Starting address (ADDRL) <sup>(1)</sup><br>Data 1<br>:<br>Data N |  |  |  |

1. The minimum data size is 7 bytes. The maximum data size is 15 bytes.

2. The start address must be a page boundary start address.

The start location of the FLASH to be programmed is specified by the address ADDRH:ADDRL and the number of bytes in the data array is specified by DATASIZE. The minimum number of bytes that can be programmed in one routine call is 7 bytes, the maximum is 15 bytes. ADDRH:ADDRL must always be the start of boundary address (the page start address: \$X000, \$X200, \$X400, \$X600, \$X800, \$XA00, \$XC00, or \$XE00) and DATASIZE must be the same size when accessing the same page.

In some applications, the user may want to repeatedly store and read a set of data from an area of non-volatile memory. This is easily possible when using an EEPROM array. As the write and erase operations can be executed on a byte basis. For FLASH memory, the minimum erase size is the page — 512 bytes per page for MC68HC908AP64. If the data array size is less than the page size, writing and erasing to the same page cannot fully utilize the page. Unused locations in the page will be wasted. The EE\_WRITE routine is designed to emulate the properties similar to the EEPROM. Allowing a more efficient use of the FLASH page for data storage.

When the user dedicates a page of FLASH for data storage, and the size of the data array defined, each call of the EE\_WRTIE routine will automatically transfer the data in the data array (in RAM) to the next blank block of locations in the FLASH page. Once a page is filled up, the EE\_WRITE routine automatically erases the page, and starts reuse the page again. In the 512-byte page, an 9-byte control block is used by the routine to monitor the utilization of the page. In effect, only 503 bytes are used for data storage. (see Figure 8-10). The page control operations are transparent to the user.

When using this routine to store a 8-byte data array, the FLASH page can be programmed 62 times before the an erase is required. In effect, the write/erase endurance is increased by 62 times. When a 15-byte data array is used, the write/erase endurance is increased by 33 times. Due to the FLASH page size limitation, the data array is limited from 7 bytes to 15 bytes.

#### I/O Registers

|        | Bit 7                     | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|--------|---------------------------|---|---|---|---|---|---|-------|

| Read:  | Bit 7                     | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Write: |                           |   |   |   |   |   |   |       |

| Reset: | Indeterminate after reset |   |   |   |   |   |   |       |

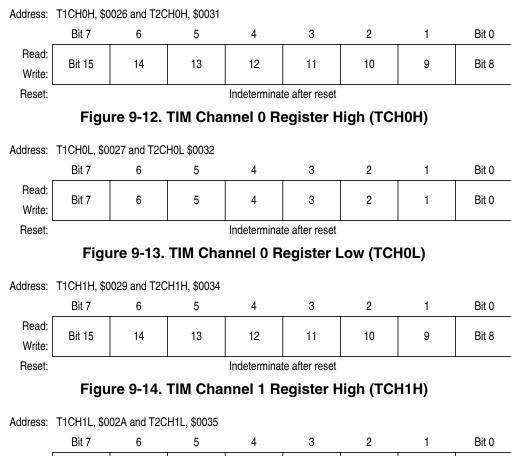

Figure 9-15. TIM Channel 1 Register Low (TCH1L)

#### Timebase Module (TBM)

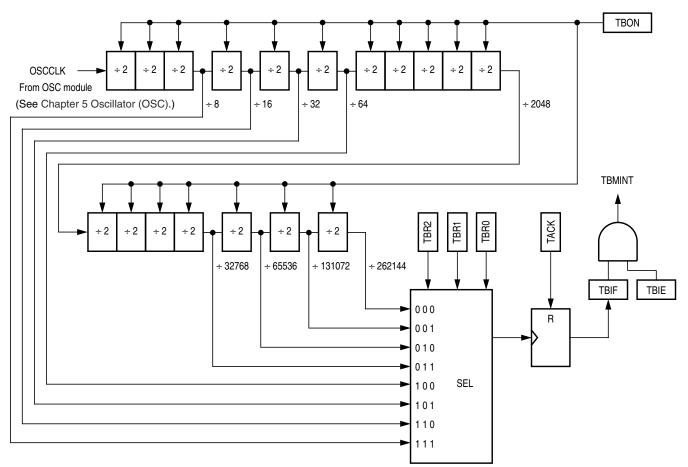

Figure 10-1. Timebase Block Diagram

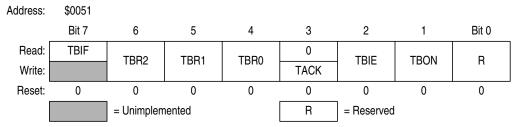

## **10.4 Timebase Register Description**

The timebase has one register, the TBCR, which is used to enable the timebase interrupts and set the rate.

Figure 10-2. Timebase Control Register (TBCR)

## TBIF — Timebase Interrupt Flag

This read-only flag bit is set when the timebase counter has rolled over.

- 1 = Timebase interrupt pending

- 0 = Timebase interrupt not pending

#### Serial Communications Interface Module (SCI)

Depending on the state of the WAKE bit in SCC1, either of two conditions on the RxD pin can bring the receiver out of the standby state:

- Address mark An address mark is a logic 1 in the most significant bit position of a received character. When the WAKE bit is set, an address mark wakes the receiver from the standby state by clearing the RWU bit. The address mark also sets the SCI receiver full bit, SCRF. Software can then compare the character containing the address mark to the user-defined address of the receiver. If they are the same, the receiver remains awake and processes the characters that follow. If they are not the same, software can set the RWU bit and put the receiver back into the standby state.

- Idle input line condition When the WAKE bit is clear, an idle character on the RxD pin wakes the

receiver from the standby state by clearing the RWU bit. The idle character that wakes the receiver

does not set the receiver idle bit, IDLE, or the SCI receiver full bit, SCRF. The idle line type bit,

ILTY, determines whether the receiver begins counting logic 1s as idle character bits after the start

bit or after the stop bit.

### NOTE

With the WAKE bit clear, setting the RWU bit after the RxD pin has been idle may cause the receiver to wake up immediately.

### 11.4.3.7 Receiver Interrupts

The following sources can generate CPU interrupt requests from the SCI receiver:

- SCI receiver full (SCRF) The SCRF bit in SCS1 indicates that the receive shift register has transferred a character to the SCDR. SCRF can generate a receiver CPU interrupt request. Setting the SCI receive interrupt enable bit, SCRIE, in SCC2 enables the SCRF bit to generate receiver CPU interrupts.

- Idle input (IDLE) The IDLE bit in SCS1 indicates that 10 or 11 consecutive logic 1s shifted in from the RxD pin. The idle line interrupt enable bit, ILIE, in SCC2 enables the IDLE bit to generate CPU interrupt requests.

## 11.4.3.8 Error Interrupts

The following receiver error flags in SCS1 can generate CPU interrupt requests:

- Receiver overrun (OR) The OR bit indicates that the receive shift register shifted in a new character before the previous character was read from the SCDR. The previous character remains in the SCDR, and the new character is lost. The overrun interrupt enable bit, ORIE, in SCC3 enables OR to generate SCI error CPU interrupt requests.

- Noise flag (NF) The NF bit is set when the SCI detects noise on incoming data or break characters, including start, data, and stop bits. The noise error interrupt enable bit, NEIE, in SCC3 enables NF to generate SCI error CPU interrupt requests.

- Framing error (FE) The FE bit in SCS1 is set when a logic 0 occurs where the receiver expects a stop bit. The framing error interrupt enable bit, FEIE, in SCC3 enables FE to generate SCI error CPU interrupt requests.

- Parity error (PE) The PE bit in SCS1 is set when the SCI detects a parity error in incoming data. The parity error interrupt enable bit, PEIE, in SCC3 enables PE to generate SCI error CPU interrupt requests.

# 12.5 SCI Functional Description

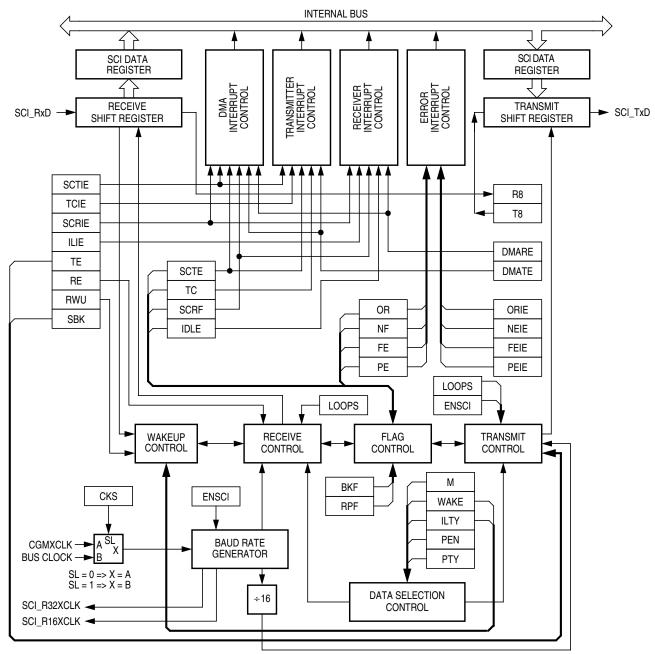

Figure 12-5 shows the structure of the SCI.

Figure 12-5. SCI Module Block Diagram

### 12.5.3.2 Character Reception

During an SCI reception, the receive shift register shifts characters in from the RxD pin. The SCI data register (IRSCDR) is the read-only buffer between the internal data bus and the receive shift register.

After a complete character shifts into the receive shift register, the data portion of the character transfers to the IRSCDR. The SCI receiver full bit, SCRF, in IRSCI status register 1 (IRSCS1) becomes set, indicating that the received byte can be read. If the SCI receive interrupt enable bit, SCRIE, in IRSCC2 is also set, the SCRF bit generates a receiver CPU interrupt request.

### 12.5.3.3 Data Sampling

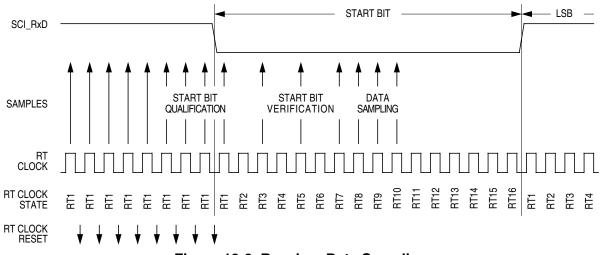

The receiver samples the RxD pin at the RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock is resynchronized at the following times (see Figure 12-9):

- After every start bit

- After the receiver detects a data bit change from logic 1 to logic 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid logic 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid logic 0)

#### Figure 12-9. Receiver Data Sampling

To locate the start bit, data recovery logic does an asynchronous search for a logic 0 preceded by three logic 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Table 12-2 summarizes the results of the start bit verification samples.

| Table | 12-2. | Start | Bit | Verification |

|-------|-------|-------|-----|--------------|

|-------|-------|-------|-----|--------------|

| RT3, RT5, and RT7<br>Samples | Start Bit<br>Verification | Noise Flag |

|------------------------------|---------------------------|------------|

| 000                          | Yes                       | 0          |

| 001                          | Yes                       | 1          |

| 010                          | Yes                       | 1          |

#### NF — Receiver Noise Flag Bit

This clearable, read-only bit is set when the SCI detects noise on the RxD pin. NF generates an SCI error CPU interrupt request if the NEIE bit in IRSCC3 is also set. Clear the NF bit by reading IRSCS1 and then reading the IRSCDR. Reset clears the NF bit.

1 = Noise detected

0 = No noise detected

#### FE — Receiver Framing Error Bit

This clearable, read-only bit is set when a logic 0 is accepted as the stop bit. FE generates an SCI error CPU interrupt request if the FEIE bit in IRSCC3 also is set. Clear the FE bit by reading IRSCS1 with FE set and then reading the IRSCDR. Reset clears the FE bit.

1 = Framing error detected

0 = No framing error detected

#### PE — Receiver Parity Error Bit

This clearable, read-only bit is set when the SCI detects a parity error in incoming data. PE generates an SCI error CPU interrupt request if the PEIE bit in IRSCC3 is also set. Clear the PE bit by reading IRSCS1 with PE set and then reading the IRSCDR. Reset clears the PE bit.

1 = Parity error detected

0 = No parity error detected

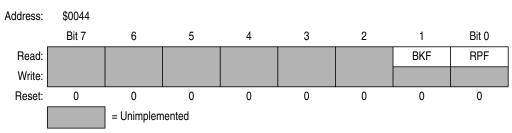

## 12.9.5 IRSCI Status Register 2

IRSCI status register 2 contains flags to signal the following conditions:

- Break character detected

- Incoming data

Figure 12-17. IRSCI Status Register 2 (IRSCS2)

#### BKF — Break Flag Bit

This clearable, read-only bit is set when the SCI detects a break character on the RxD pin. In IRSCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in IRSCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading IRSCS2 with BKF set and then reading the IRSCDR. Once cleared, BKF can become set again only after logic 1s again appear on the RxD pin followed by another break character. Reset clears the BKF bit.

- 1 = Break character detected

- 0 = No break character detected

#### NOTE

To prevent bus contention with another master SPI after a mode fault error, clear all SPI bits of the data direction register of the shared I/O port before enabling the SPI.

When configured as a slave (SPMSTR = 0), the MODF flag is set if  $\overline{SS}$  goes high during a transmission. When CPHA = 0, a transmission begins when  $\overline{SS}$  goes low and ends once the incoming SPSCK goes back to its idle level following the shift of the eighth data bit. When CPHA = 1, the transmission begins when the SPSCK leaves its idle level and  $\overline{SS}$  is already low. The transmission continues until the SPSCK returns to its idle level following the shift of the last data bit. (See 13.5 Transmission Formats.)

#### NOTE

Setting the MODF flag does not clear the SPMSTR bit. The SPMSTR bit has no function when SPE = 0. Reading SPMSTR when MODF = 1 shows the difference between a MODF occurring when the SPI is a master and when it is a slave.

When CPHA = 0, a MODF occurs if a slave is selected ( $\overline{SS}$  is at logic 0) and later unselected ( $\overline{SS}$  is at logic 1) even if no SPSCK is sent to that slave. This happens because  $\overline{SS}$  at logic 0 indicates the start of the transmission (MISO driven out with the value of MSB) for CPHA = 0. When CPHA = 1, a slave can be selected and then later unselected with no transmission occurring. Therefore, MODF does not occur since a transmission was never begun.

In a slave SPI (MSTR = 0), the MODF bit generates an SPI receiver/error CPU interrupt request if the ERRIE bit is set. The MODF bit does not clear the SPE bit or reset the SPI in any way. Software can abort the SPI transmission by clearing the SPE bit of the slave.

#### NOTE

A logic 1 voltage on the  $\overline{SS}$  pin of a slave SPI puts the MISO pin in a high impedance state. Also, the slave SPI ignores all incoming SPSCK clocks, even if it was already in the middle of a transmission.

To clear the MODF flag, read the SPSCR with the MODF bit set and then write to the SPCR register. This entire clearing mechanism must occur with no MODF condition existing or else the flag is not cleared.

## 13.8 Interrupts

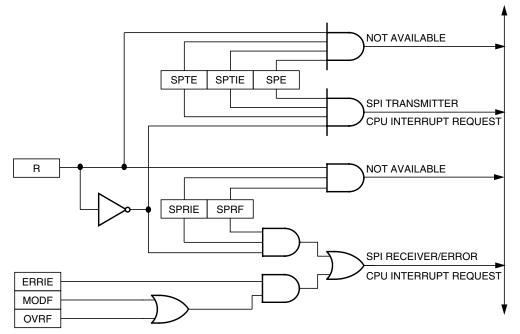

Four SPI status flags can be enabled to generate CPU interrupt requests.

| Flag                      | Request                                                       |

|---------------------------|---------------------------------------------------------------|

| SPTE<br>Transmitter empty | SPI transmitter CPU interrupt request<br>(SPTIE = 1, SPE = 1) |

| SPRF<br>Receiver full     | SPI receiver CPU interrupt request<br>(SPRIE = 1)             |

| OVRF<br>Overflow          | SPI receiver/error interrupt request (ERRIE = 1)              |

| MODF<br>Mode fault        | SPI receiver/error interrupt request (ERRIE = 1)              |

## Table 13-2. SPI Interrupts

#### Serial Peripheral Interface Module (SPI)

Reading the SPI status and control register with SPRF set and then reading the receive data register clears SPRF. The clearing mechanism for the SPTE flag is always just a write to the transmit data register.

The SPI transmitter interrupt enable bit (SPTIE) enables the SPTE flag to generate transmitter CPU interrupt requests, provided that the SPI is enabled (SPE = 1).

The SPI receiver interrupt enable bit (SPRIE) enables the SPRF bit to generate receiver CPU interrupt requests, regardless of the state of the SPE bit. (See Figure 13-11.)

The error interrupt enable bit (ERRIE) enables both the MODF and OVRF bits to generate a receiver/error CPU interrupt request.

The mode fault enable bit (MODFEN) can prevent the MODF flag from being set so that only the OVRF bit is enabled by the ERRIE bit to generate receiver/error CPU interrupt requests.

Figure 13-11. SPI Interrupt Request Generation

The following sources in the SPI status and control register can generate CPU interrupt requests:

- SPI receiver full bit (SPRF) The SPRF bit becomes set every time a byte transfers from the shift

register to the receive data register. If the SPI receiver interrupt enable bit, SPRIE, is also set,

SPRF generates an SPI receiver/error CPU interrupt request.

- SPI transmitter empty (SPTE) The SPTE bit becomes set every time a byte transfers from the transmit data register to the shift register. If the SPI transmit interrupt enable bit, SPTIE, is also set, SPTE generates an SPTE CPU interrupt request.

# 13.9 Resetting the SPI

Any system reset completely resets the SPI. Partial resets occur whenever the SPI enable bit (SPE) is low. Whenever SPE is low, the following occurs:

- The SPTE flag is set.

- Any transmission currently in progress is aborted.

Multi-Master IIC Interface (MMIIC)

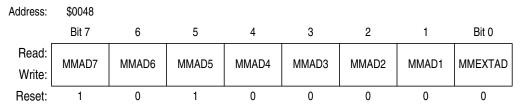

## 14.6.1 MMIIC Address Register (MMADR)

Figure 14-4. MMIIC Address Register (MMADR)

### MMAD[7:1] — Multi-Master Address

These seven bits represent the MMIIC interface's own specific slave address when in slave mode, and the calling address when in master mode. Software must update MMAD[7:1] as the calling address while entering master mode and restore its own slave address after master mode is relinquished. This register is cleared as \$A0 upon reset.

### MMEXTAD — Multi-Master Expanded Address

This bit is set to expand the address of the MMIIC in slave mode. When set, the MMIIC will acknowledge the following addresses from a calling master: \$MMAD[7:1], 0000000, and 0001100. Reset clears this bit.

1 = MMIIC responds to the following calling addresses:

\$MMAD[7:1], 0000000, and 0001100.

0 = MMIIC responds to address \$MMAD[7:1]

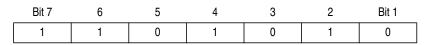

For example, when MMADR is configured as:

| MMAD7 | MMAD6 | MMAD5 | MMAD4 | MMAD3 | MMAD2 | MMAD1 | MMEXTAD |

|-------|-------|-------|-------|-------|-------|-------|---------|

| 1     | 1     | 0     | 1     | 0     | 1     | 0     | 1       |

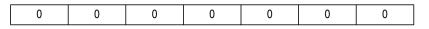

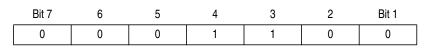

The MMIIC module will respond to the calling address:

or the general calling address:

or the calling address:

Note that bit-0 of the 8-bit calling address is the MMRW bit from the calling master.

#### Multi-Master IIC Interface (MMIIC)

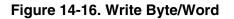

## 14.8.4 Write Byte/Word

| START            | Slave Address     | W ACK | Command Code | ACK | Data Byte     | ACK | STOP           |     |      |

|------------------|-------------------|-------|--------------|-----|---------------|-----|----------------|-----|------|

| (a) Write Byte P | Protocol          |       |              |     |               |     |                |     |      |

| START            | Slave Address     | W ACK | Command Code | ACK | Data Byte     | ACK | PEC            | ACK | STOP |

| (b) Write Byte P | Protocol with PEC |       |              |     |               |     |                |     |      |

| START            | Slave Address     | W ACK | Command Code | ACK | Data Byte Low | ACK | Data Byte High | ACK | STOP |

| (c) Write Word I | Protocol          |       |              |     |               |     |                |     |      |

| START            | Slave Address     | W ACK | Command Code | ACK | Data Byte Low | ACK | Data Byte High | ACK |      |

| PEC              | ACK               | STOP  |              |     |               |     |                |     |      |

| (d) Write Word   | Protocol with PEC | ;     |              |     |               |     |                |     |      |

## 14.8.5 Read Byte/Word

| START            | Slave Address    | W ACK | Command Code | ACK | START | Slave Address | R | ACK | Data Byte     | NAK | STOP |

|------------------|------------------|-------|--------------|-----|-------|---------------|---|-----|---------------|-----|------|

| (a) Read Byte Pr | rotocol          |       |              |     |       |               |   |     |               |     |      |

| START            | Slave Address    | W ACK | Command Code | ACK | START | Slave Address | R | ACK | Data Byte     | ACK |      |

| PEC              | NAK              | STOP  |              |     |       |               |   |     |               |     |      |

| (b) Read Byte Pr | rotocol with PEC |       |              |     |       |               |   |     |               |     |      |

| START            | Slave Address    | W ACK | Command Code | ACK | START | Slave Address | R | ACK | Data Byte Low | ACK |      |

| Data Byte H      | igh NAK          | STOP  |              |     |       |               |   |     |               |     |      |

| (c) Read Word P  | Protocol         |       |              |     |       |               |   |     |               |     |      |

| START            | Slave Address    | W ACK | Command Code | ACK | START | Slave Address | R | ACK | Data Byte Low | ACK |      |

| Data Byte H      | igh ACK          | PEC   | NAK S        | ГОР |       |               |   |     |               |     |      |

(d) Read Word Protocol with PEC

MC68HC908AP Family Data Sheet, Rev. 4

#### Analog-to-Digital Converter (ADC)

| ADCH4       | ADCH3       | ADCH2       | ADCH1       | ADCH0       | ADC Channel        | Input Select                   |

|-------------|-------------|-------------|-------------|-------------|--------------------|--------------------------------|

| 0           | 0           | 0           | 0           | 0           | ADC0               | PTA0                           |

| 0           | 0           | 0           | 0           | 1           | ADC1               | PTA1                           |

| 0           | 0           | 0           | 1           | 0           | ADC2               | PTA2                           |

| 0           | 0           | 0           | 1           | 1           | ADC3               | PTA3                           |

| 0           | 0           | 1           | 0           | 0           | ADC4               | PTA4                           |

| 0           | 0           | 1           | 0           | 1           | ADC5               | PTA5                           |

| 0           | 0           | 1           | 1           | 0           | ADC6               | PTA6                           |

| 0           | 0           | 1           | 1           | 1           | ADC7               | PTA7                           |

| 0<br>↓<br>1 | 1<br>↓<br>1 | 0<br>↓<br>1 | 0<br>↓<br>0 | 0<br>↓<br>0 | ADC8<br>↓<br>ADC28 | Reserved                       |

| 1           | 1           | 1           | 0           | 1           | ADC29              | V <sub>REFH</sub> (see Note 2) |

| 1           | 1           | 1           | 1           | 0           | ADC30              | V <sub>REFL</sub> (see Note 2) |

| 1           | 1           | 1           | 1           | 1           | ADC powered-off    | _                              |

#### Table 15-1. MUX Channel Select

NOTES:

1. If any unused channels are selected, the resulting ADC conversion will be unknown.

2. The voltage levels supplied from internal reference nodes as specified in the table are used to verify the operation of the ADC converter both in production test and for user applications.

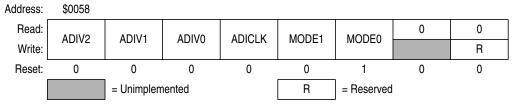

## 15.7.2 ADC Clock Control Register

The ADC clock control register (ADICLK) selects the clock frequency for the ADC.

Figure 15-4. ADC Clock Control Register (ADICLK)

#### ADIV[2:0] — ADC Clock Prescaler Bits

ADIV2, ADIV1, and ADIV0 form a 3-bit field which selects the divide ratio used by the ADC to generate the internal ADC clock.

Table 15-2 shows the available clock configurations. The ADC clock should be set to between 500 kHz and 1MHz.

# 22.5 5V DC Electrical Characteristics

\_\_\_\_

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                                                                    | Symbol                                                                                            | Min                                          | Typ <sup>(2)</sup> | Мах                                       | Unit                  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------|-------------------------------------------|-----------------------|--|--|--|--|

| Output high voltage<br>(I <sub>LOAD</sub> = -12mA) PTA[0:7], PTB[4:7], PTC[0:5], PTD[0:7]<br>(I <sub>LOAD</sub> = -15mA) PTA[0:7], PTB[4:7], PTC[0:5], PTD[0:7]                                                                                                                                                                  | V <sub>OH</sub><br>V <sub>OH</sub>                                                                | V <sub>DD</sub> -0.8<br>V <sub>DD</sub> -1.0 |                    | _                                         | v<br>v                |  |  |  |  |

| Output low voltage<br>$(I_{LOAD} = 6mA) PTA[0:7], PTB[4:7], PTC[0:5], PTD[0:7]$<br>$(I_{LOAD} = 12mA) PTB[0:3], PTC[6:7]$<br>$(I_{LOAD} = 15mA) PTA[0:7], PTB[4:7], PTC[0:5], PTD[0:7]$<br>$(I_{LOAD} = 15mA) PTB[0:3], PTC[6:7]$<br>$(I_{LOAD} = 15mA) as TxD, RxD, SCTxD, SCRxD$<br>$(I_{LOAD} = see Table 22-12) as SDA, SCL$ | V <sub>OL</sub><br>V <sub>OL</sub><br>V <sub>OL</sub><br>V <sub>OLSCI</sub><br>V <sub>OLIIC</sub> |                                              |                    | 0.4<br>0.4<br>0.8<br>0.6<br>0.4<br>0.4    | V<br>V<br>V<br>V<br>V |  |  |  |  |

| LED sink current (V <sub>OL</sub> = 3V)<br>PTA[0:7]                                                                                                                                                                                                                                                                              | I <sub>OL</sub>                                                                                   | 9                                            | 15                 | 25                                        | mA                    |  |  |  |  |

| Input high voltage<br>PTA[0:7], PTB[0:7], PTC[0:7], PTD[0:7], RST, IRQ1<br>OSC1                                                                                                                                                                                                                                                  | V <sub>IH</sub>                                                                                   | $0.7 	imes V_{DD}$<br>$0.7 	imes V_{REG}$    |                    | V <sub>DD</sub><br>V <sub>REG</sub>       | v<br>v                |  |  |  |  |

| Input low voltage<br>PTA[0:7], PTB[0:7], PTC[0:7], PTD[0:7], RST, IRQ1<br>OSC1                                                                                                                                                                                                                                                   | V <sub>IL</sub>                                                                                   | V <sub>SS</sub><br>V <sub>SS</sub>           | _                  | $0.3 	imes V_{DD}$<br>$0.3 	imes V_{REG}$ | v<br>v                |  |  |  |  |

| $V_{DD}$ supply current, f <sub>OP</sub> = 8 MHz<br>Run <sup>(3)</sup><br>Wait <sup>(4)</sup>                                                                                                                                                                                                                                    |                                                                                                   |                                              | 10<br>2.5          | 20<br>10                                  | mA<br>mA              |  |  |  |  |

| Stop (25°C)<br>with OSC, TBM, and LVI modules on <sup>(5)</sup><br>with OSC and TBM modules on <sup>(5)</sup><br>all modules off <sup>(6)</sup>                                                                                                                                                                                  | I <sub>DD</sub>                                                                                   | <br>                                         | 0.8<br>22<br>20    | 1.8<br>150<br>125                         | mA<br>μA<br>μA        |  |  |  |  |

| Stop (0 to 85°C)<br>with OSC, TBM, and LVI modules on <sup>(5)</sup><br>with OSC and TBM modules on <sup>(5)</sup><br>all modules off <sup>(6)</sup>                                                                                                                                                                             |                                                                                                   | <br>                                         | 1<br>45<br>42      | 2.5<br>300<br>250                         | mA<br>μA<br>μA        |  |  |  |  |

| Digital I/O ports Hi-Z leakage current                                                                                                                                                                                                                                                                                           | IIL                                                                                               |                                              | _                  | ± 10                                      | μA                    |  |  |  |  |

| Input current                                                                                                                                                                                                                                                                                                                    | I <sub>IN</sub>                                                                                   | _                                            | _                  | ± 1                                       | μΑ                    |  |  |  |  |

| Capacitance<br>Ports (as input or output)                                                                                                                                                                                                                                                                                        | C <sub>OUT</sub><br>C <sub>IN</sub>                                                               |                                              |                    | 12<br>8                                   | pF<br>pF              |  |  |  |  |

| POR rearm voltage <sup>(7)</sup>                                                                                                                                                                                                                                                                                                 | V <sub>POR</sub>                                                                                  | 0                                            | _                  | 100                                       | mV                    |  |  |  |  |

| POR rise time ramp rate <sup>(8)</sup>                                                                                                                                                                                                                                                                                           | R <sub>POR</sub>                                                                                  | 0.035                                        | _                  | _                                         | V/ms                  |  |  |  |  |

| Monitor mode entry voltage                                                                                                                                                                                                                                                                                                       | V <sub>TST</sub>                                                                                  | $1.4 \times V_{DD}$                          |                    | 8.5                                       | V                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                  | * ISI                                                                                             |                                              |                    | 0.0                                       | v                     |  |  |  |  |

## Table 22-4. DC Electrical Characteristics (5V)

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007. All rights reserved.

MC68HC908AP64 Rev. 4, 01/2007