Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | LED, POR, PWM, WDT                                                         |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 1.25К х 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 32-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5130a-putum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

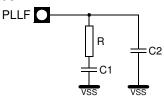

The typical values are: R = 100  $\Omega$ , C1 = 10 nf, C2 = 2.2 nF.

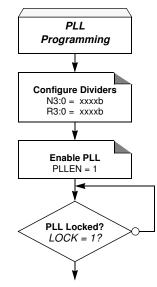

## 5.3.2 PLL Programming

The PLL is programmed using the flow shown in Figure 5-5. As soon as clock generation is enabled user must wait until the lock indicator is set to ensure the clock output is stable.

#### 5.3.3 Divider Values

To generate a 48 MHz clock using the PLL, the divider values have to be configured following the oscillator frequency. The typical divider values are shown in Table 5-1.

| Oscillator Frequency | R+1 | N+1 | PLLDIV |

|----------------------|-----|-----|--------|

| 3 MHz                | 16  | 1   | F0h    |

| 6 MHz                | 8   | 1   | 70h    |

| 8 MHz                | 6   | 1   | 50h    |

| 12 MHz               | 4   | 1   | 30h    |

| 16 MHz               | 3   | 1   | 20h    |

| 18 MHz               | 8   | 3   | 72h    |

| 20 MHz               | 12  | 5   | B4h    |

| 24 MHz               | 2   | 1   | 10h    |

Table 5-1.Typical Divider Values

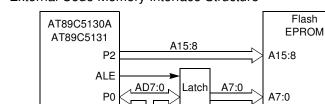

Figure 8-2. External Code Memory Interface Structure

| Table 8-1. | External Data I  | Memory  | Interface | Signals |

|------------|------------------|---------|-----------|---------|

|            | LALEITIAI Dala I | NETHOLY | menace    | Signais |

PSEN

| Signal<br>Name | Туре | Description                                                                                                                             | Alternate<br>Function |

|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A15:8          | 0    | Address Lines<br>Upper address lines for the external bus.                                                                              | P2.7:0                |

| AD7:0          | I/O  | Address/Data Lines<br>Multiplexed lower address lines and data for the external memory.                                                 | P0.7:0                |

| ALE            | 0    | Address Latch Enable<br>ALE signals indicates that valid address information are available on lines<br>AD7:0.                           | -                     |

| PSEN           | 0    | <b>Program Store Enable Output</b><br>This signal is active low during external code fetch or external code read<br>(MOVC instruction). | -                     |

D7:0

OE

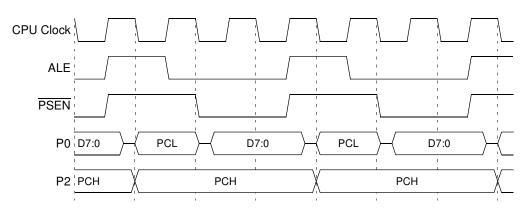

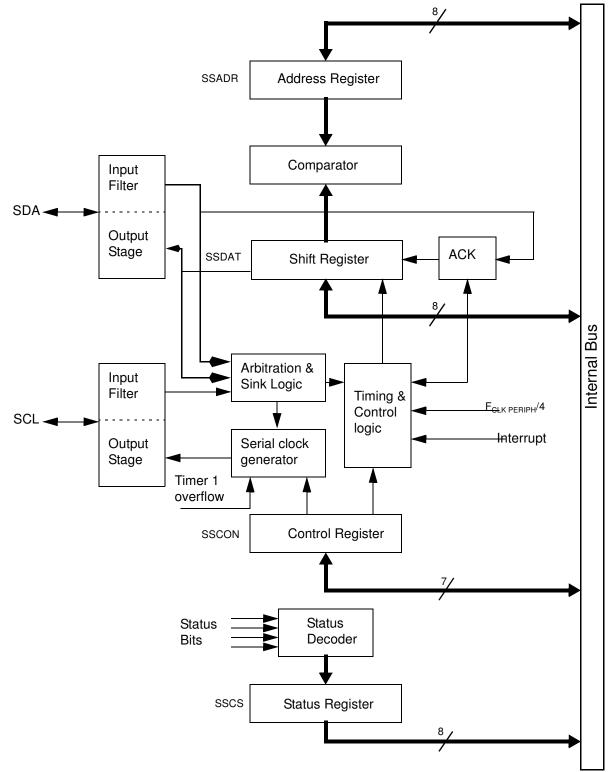

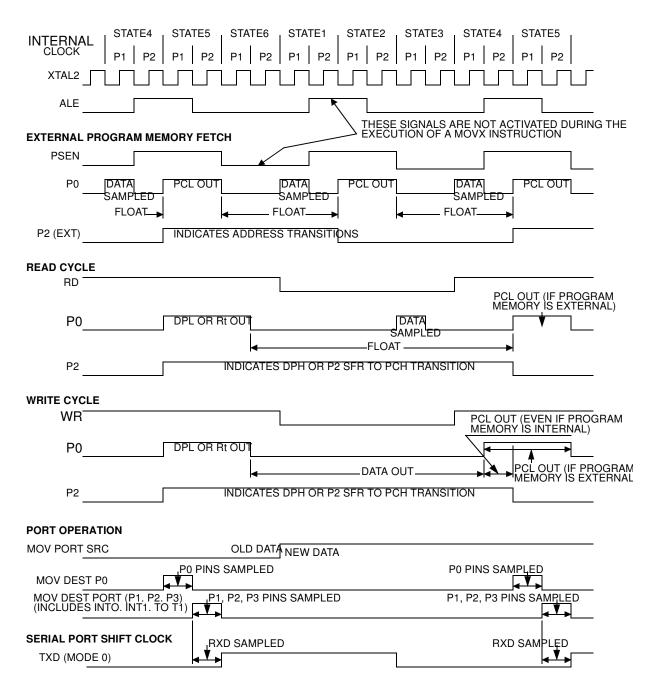

### 8.1.2 External Bus Cycles

This section describes the bus cycles the AT89C5130A/31A-M executes to fetch code (see Figure 8-3) in the external program/code memory.

External memory cycle takes 6 CPU clock periods. This is equivalent to 12 oscillator clock periods in standard mode or 6 oscillator clock periods in X2 mode. For further information on X2 mode (see the clock Section).

For simplicity, the accompanying figure depicts the bus cycle waveforms in idealized form and do not provide precise timing information.

#### Figure 8-3. External Code Fetch Waveforms

# 11. In-System Programming (ISP)

With the implementation of the User Space (FM0) and the Boot Space (FM1) in Flash technology the AT89C5130A/31A-M allows the system engineer the development of applications with a very high level of flexibility. This flexibility is based on the possibility to alter the customer program at any stages of a product's life:

- Before mounting the chip on the PCB, FM0 flash can be programmed with the application code. FM1 is always preprogrammed by Atmel with a USB bootloader.<sup>(1)</sup>

- Once the chip is mounted on the PCB, it can be programmed by serial mode via the USB bus.

Note: 1. The user can also program his own bootloader in FM1.

This ISP allows code modification over the total lifetime of the product.

Besides the default Bootloaders Atmel provide customers all the needed Application-Programming-Interfaces (API) which are needed for the ISP. The API are located in the Boot memory.

This allow the customer to have a full use of the 32-Kbyte user memory.

## 11.1 Flash Programming and Erasure

There are three methods for programming the Flash memory:

- The Atmel bootloader located in FM1 is activated by the application. Low level API routines (located in FM1)will be used to program FM0. The interface used for serial downloading to FM0 is the USB. API can be called also by user's bootloader located in FM0 at [SBV]00h.

- A further method exist in activating the Atmel boot loader by hardware activation. See the Section "Hardware Registers".

- The FM0 can be programmed also by the parallel mode using a programmer.

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                             |  |  |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 5             | MO              | Pulse length<br>Cleared to stretch MOVX control: the $\overline{\text{RD}}$ and the $\overline{\text{WR}}$ pulse length is 6 clock<br>periods (default).<br>Set to stretch MOVX control: the $\overline{\text{RD}}$ and the $\overline{\text{WR}}$ pulse length is 30 clock<br>periods. |  |  |  |

| 4             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                                                                          |  |  |  |

| 3             | XRS1            | ERAM Size                                                                                                                                                                                                                                                                               |  |  |  |

| 2             | XRS0            | XRS1XRS0         ERAM size           0         0         256 bytes           0         1         512 bytes           1         0         768 bytes           1         1         1024 bytes (default)                                                                                   |  |  |  |

| 1             | EXTRAM          | <b>EXTRAM bit</b><br>Cleared to access internal ERAM using MOVX at $\overline{\text{Ri}}$ at DPTR.<br>Set to access external memory.                                                                                                                                                    |  |  |  |

| 0             | AO              | ALE Output bit<br>Cleared, ALE is emitted at a constant rate of 1/6 the oscillator frequency (or<br>1/3 if X2 mode is used) (default).<br>Set, ALE is active only when a MOVX or MOVC instruction is used.                                                                              |  |  |  |

Reset Value = 0X0X 1100b Not bit addressable

# Table 13-1. T2CON Register T2CON Timer 2 Control Reg

| 7             | 6               | 5                                                                                                                                                                                                                                                                                                                   | 4                                                                                                                                                                                                                                             | 3                                                      | 2                | 1               | 0               |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|-----------------|-----------------|

| TF2           | EXF2            | RCLK                                                                                                                                                                                                                                                                                                                | TCLK                                                                                                                                                                                                                                          | EXEN2                                                  | TR2              | C/T2#           | CP/RL2#         |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                               |                                                        |                  |                 |                 |

| 7             | TF2             |                                                                                                                                                                                                                                                                                                                     | red by softwar                                                                                                                                                                                                                                | e.<br>2 overflow, if RC                                | CLK = 0 and TC   | CLK = 0.        |                 |

| 6             | EXF2            | EXEN2 = 1.<br>When set, ca<br>is enabled.                                                                                                                                                                                                                                                                           | apture or a rel<br>auses the CPU<br>red by softwar                                                                                                                                                                                            | oad is caused b<br>to vector to Tim<br>e. EXF2 doesn't | er 2 interrupt r | outine when Tir | ner 2 interrupt |

| 5             | RCLK            | Cleared to us                                                                                                                                                                                                                                                                                                       | <b>Receive Clock bit</b><br>Cleared to use Timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                  |                                                        |                  |                 |                 |

| 4             | TCLK            | Cleared to us                                                                                                                                                                                                                                                                                                       | <b>Transmit Clock bit</b><br>Cleared to use Timer 1 overflow as transmit clock for serial port in mode 1 or 3.<br>Set to use Timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                               |                                                        |                  |                 |                 |

| 3             | EXEN2           | Cleared to ig<br>Set to cause                                                                                                                                                                                                                                                                                       | <b>Timer 2 External Enable bit</b><br>Cleared to ignore events on T2EX pin for Timer 2 operation.<br>Set to cause a capture or reload when a negative transition on T2EX pin is detected, it<br>Timer 2 is not used to clock the serial port. |                                                        |                  |                 | is detected, if |

| 2             | TR2             | Timer 2 Run control bit<br>Cleared to turn off Timer 2.<br>Set to turn on Timer 2.                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                               |                                                        |                  |                 |                 |

| 1             | C/T2#           | <b>Timer/Counter 2 select bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be C<br>clock out mode.                                                                           |                                                                                                                                                                                                                                               |                                                        |                  |                 |                 |

| 0             | CP/RL2#         | <b>Timer 2 Capture/Reload bit</b><br>If RCLK = 1 or TCLK = 1, CP/RL2# is ignored and timer is forced to Auto-reload on<br>Timer 2 overflow.<br>Cleared to Auto-reload on Timer 2 overflows or negative transitions on T2EX pin if<br>EXEN2 = 1.<br>Set to capture on negative transitions on T2EX pin if EXEN2 = 1. |                                                                                                                                                                                                                                               |                                                        |                  |                 |                 |

Reset Value = 0000 0000b Bit addressable

Table 13-2. T2MOD Register T2MOD - Timer 2 Mode Control Register (C9h) 7 2 0 6 5 4 3 1 T2OE DCEN ------Bit Bit Number Mnemonic Description Reserved 7 The value read from this bit is indeterminate. Do not set this bit. Reserved 6 The value read from this bit is indeterminate. Do not set this bit. Reserved 5 -The value read from this bit is indeterminate. Do not set this bit. Reserved 4 The value read from this bit is indeterminate. Do not set this bit. Reserved 3 \_ The value read from this bit is indeterminate. Do not set this bit. Reserved 2 The value read from this bit is indeterminate. Do not set this bit. Timer 2 Output Enable bit 1 T2OE Cleared to program P1.0/T2 as clock input or I/O port. Set to program P1.0/T2 as clock output. Down Counter Enable bit 0 DCEN Cleared to disable Timer 2 as up/down counter. Set to enable Timer 2 as up/down counter.

Reset Value = XXXX XX00b Not bit addressable

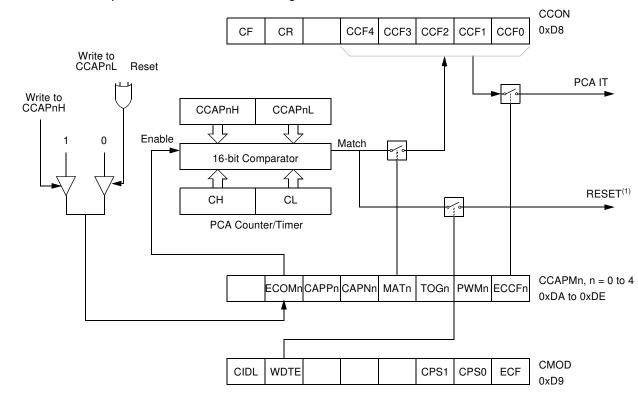

Note: 1. Only for Module 4

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen. Writing to CCAPnH will set the ECOM bit.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

## 14.3 High Speed Output Mode

In this mode, the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (see Figure 14-5).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

## 15. Serial I/O Port

The serial I/O port in the AT89C5130A/31A-M is compatible with the serial I/O port in the 80C52. It provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates.

Serial I/O port includes the following enhancements:

- Framing error detection

- · Automatic address recognition

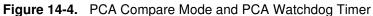

## 15.1 Framing Error Detection

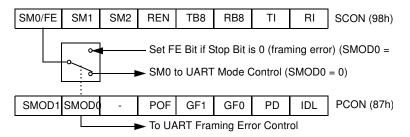

Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (see Figure 15-1).

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 15-1) bit is set.

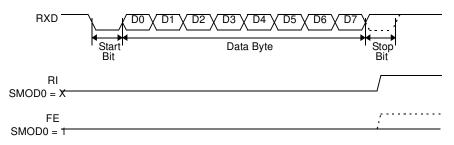

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 15-2 and Figure 15-3).

## Figure 15-2. UART Timings in Mode 1

## 16. Interrupt System

## 16.1 Overview

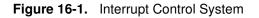

The AT89C5130A/31A-M has a total of 11 interrupt vectors: two external interrupts (INT0 and INT1), three timer interrupts (timers 0, 1 and 2), the serial port interrupt, SPI interrupt, Keyboard interrupt, USB interrupt and the PCA global interrupt. These interrupts are shown in Figure 16-1.

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (Table 16-2). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

| Bit    | Bit      |                                                                                                                                             |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic | Description                                                                                                                                 |

| 7      | EA       | Enable All interrupt bit<br>Cleared to disable all interrupts.<br>Set to enable all interrupts.                                             |

| 6      | EC       | PCA interrupt enable bit<br>Cleared to disable.<br>Set to enable.                                                                           |

| 5      | ET2      | Timer 2 overflow interrupt Enable bit<br>Cleared to disable Timer 2 overflow interrupt.<br>Set to enable Timer 2 overflow interrupt.        |

| 4      | ES       | Serial port Enable bit<br>Cleared to disable serial port interrupt.<br>Set to enable serial port interrupt.                                 |

| 3      | ET1      | Timer 1 overflow interrupt Enable bit<br>Cleared to disable Timer 1 overflow interrupt.<br>Set to enable Timer 1 overflow interrupt.        |

| 2      | EX1      | External interrupt 1 Enable bit<br>Cleared to disable external interrupt 1.<br>Set to enable external interrupt 1.                          |

| 1      | ET0      | <b>Timer 0 overflow interrupt Enable bit</b><br>Cleared to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt. |

| 0      | EX0      | External interrupt 0 Enable bit<br>Cleared to disable external interrupt 0.<br>Set to enable external interrupt 0.                          |

Reset Value = 0000 0000b Bit addressable

# Table 16-3. IPL0 Register

IPL0 - Interrupt Priority Register (B8h)

| 7 | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|---|------|------|-----|------|------|------|------|

| - | PPCL | PT2L | PSL | PT1L | PX1L | PTOL | PX0L |

## 19.2.3 SPI Serial Clock (SCK)

This signal is used to synchronize the data movement both in and out the devices through their MOSI and MISO lines. It is driven by the Master for eight clock cycles which allows to exchange one byte on the serial lines.

## 19.2.4 Slave Select (SS)

Each Slave peripheral is selected by one Slave Select pin  $(\overline{SS})$ . This signal must stay low for any message for a Slave. It is obvious that only one Master ( $\overline{SS}$  high level) can drive the network. The Master may select each Slave device by software through port pins (Figure 19-1). To prevent bus conflicts on the MISO line, only one slave should be selected at a time by the Master for a transmission.

In a Master configuration, the  $\overline{SS}$  line can be used in conjunction with the MODF flag in the SPI Status register (SPSTA) to prevent multiple masters from driving MOSI and SCK (see Section "Error Conditions", page 98).

A high level on the  $\overline{SS}$  pin puts the MISO line of a Slave SPI in a high-impedance state.

The SS pin could be used as a general-purpose if the following conditions are met:

- The device is configured as a Master and the SSDIS control bit in SPCON is set. This kind of configuration can be found when only one Master is driving the network and there is no way that the  $\overline{SS}$  pin could be pulled low. Therefore, the MODF flag in the SPSTA will never be set<sup>(1)</sup>.

- The Device is configured as a Slave with CPHA and SSDIS control bits set<sup>(2)</sup> This kind of configuration can happen when the system comprises one Master and one Slave only. Therefore, the device should always be selected and there is no reason that the Master uses the SS pin to select the communicating Slave device.

- Notes: 1. Clearing SSDIS control bit does not clear MODF.

- 2. Special care should be taken not to set SSDIS control bit when CPHA ='0' because in this mode, the SS is used to start the transmission.

#### 19.2.5 Baud Rate

In Master mode, the baud rate can be selected from a baud rate generator which is controlled by three bits in the SPCON register: SPR2, SPR1 and SPR0. The Master clock is chosen from one of seven clock rates resulting from the division of the internal clock by 4, 8, 16, 32, 64 or 128.

Table 19-1 gives the different clock rates selected by SPR2:SPR1:SPR0:

| SPR2 | SPR1 | SPR0 | Clock Rate                   | Baud Rate Divisor (BD) |

|------|------|------|------------------------------|------------------------|

| 0    | 0    | 0    | Don't Use                    | No BRG                 |

| 0    | 0    | 1    | F <sub>CLK PERIPH</sub> /4   | 4                      |

| 0    | 1    | 0    | F <sub>CLK PERIPH</sub> /8   | 8                      |

| 0    | 1    | 1    | F <sub>CLK PERIPH</sub> /16  | 16                     |

| 1    | 0    | 0    | F <sub>CLK PERIPH</sub> /32  | 32                     |

| 1    | 0    | 1    | F <sub>CLK PERIPH</sub> /64  | 64                     |

| 1    | 1    | 0    | F <sub>CLK PERIPH</sub> /128 | 128                    |

Table 19-1. SPI Master Baud Rate Selection

# 20. Two Wire Interface (TWI)

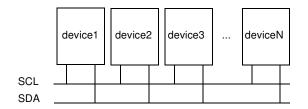

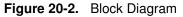

This section describes the 2-wire interface. The 2-wire bus is a bi-directional 2-wire serial communication standard. It is designed primarily for simple but efficient integrated circuit (IC) control. The system is comprised of two lines, SCL (Serial Clock) and SDA (Serial Data) that carry information between the ICs connected to them. The serial data transfer is limited to 400 Kbit/s in standard mode. Various communication configuration can be designed using this bus. Figure 20-1 shows a typical 2-wire bus configuration. All the devices connected to the bus can be master and slave.

Figure 20-1. 2-wire Bus Configuration

The Endpoint 0 is the Default Control Endpoint and will always be configured in Control type.

• Endpoint direction configuration

For Bulk, Interrupt and Isochronous endpoints, the direction is defined with the EPDIR bit of the UEPCONX register with the following values:

- IN:EPDIR = 1b

- OUT:EPDIR = 0b

For Control endpoints, the EPDIR bit has no effect.

• Summary of Endpoint Configuration:

Do not forget to select the correct endpoint number in the UEPNUM register before accessing to endpoint specific registers.

| Endpoint Configuration | EPEN | EPDIR | EPTYPE | UEPCONX   |

|------------------------|------|-------|--------|-----------|

| Disabled               | 0b   | Xb    | XXb    | 0XXX XXXb |

| Control                | 1b   | Xb    | 00b    | 80h       |

| Bulk-in                | 1b   | 1b    | 10b    | 86h       |

| Bulk-out               | 1b   | 0b    | 10b    | 82h       |

| Interrupt-In           | 1b   | 1b    | 11b    | 87h       |

| Interrupt-Out          | 1b   | 0b    | 11b    | 83h       |

| Isochronous-In         | 1b   | 1b    | 01b    | 85h       |

| Isochronous-Out        | 1b   | 0b    | 01b    | 81h       |

Table 21-1. Summary of Endpoint Configuration

Endpoint FIFO reset

Before using an endpoint, its FIFO will be reset. This action resets the FIFO pointer to its original value, resets the byte counter of the endpoint (UBYCTLX and UBYCTHX registers), and resets the data toggle bit (DTGL bit in UEPCONX).

The reset of an endpoint FIFO is performed by setting to 1 and resetting to 0 the corresponding bit in the UEPRST register.

For example, in order to reset the Endpoint number 2 FIFO, write 0000 0100b then 0000 0000b in the UEPRST register.

Note that the endpoint reset doesn't reset the bank number for ping-pong endpoints.

## 21.3 Read/Write Data FIFO

## 21.3.1 FIFO Mapping

Depending on the selected endpoint through the UEPNUM register, the UEPDATX register allows to access the corresponding endpoint data fifo.

The firmware has to clear one of these two bits after having read all the data FIFO to allow a new packet to be stored in the corresponding bank.

If the Host sends more bytes than supported by the endpoint FIFO, the overflow data won't be stored, but the USB controller will consider that the packet is valid if the CRC is correct.

#### 21.6.3 Isochronous IN Transactions in Standard Mode

An endpoint will be first enabled and configured before being able to send Isochronous packets.

The firmware will fill the FIFO with the data to be sent and set the TXRDY bit in the UEPSTAX register to allow the USB controller to send the data stored in FIFO at the next IN request concerning this endpoint.

If the TXRDY bit is not set when the IN request occurs, nothing will be sent by the USB controller.

When the IN packet has been sent, the TXCMPL bit in the UEPSTAX register is set by the USB controller. This triggers a USB interrupt if enabled. The firmware will clear the TXCMPL bit before filling the endpoint FIFO with new data.

The firmware will never write more bytes than supported by the endpoint FIFO

#### 21.6.4 Isochronous IN Transactions in Ping-pong Mode

An endpoint will be first enabled and configured before being able to send Isochronous packets.

The firmware will fill the FIFO bank 0 with the data to be sent and set the TXRDY bit in the UEP-STAX register to allow the USB controller to send the data stored in FIFO at the next IN request concerning the endpoint. The FIFO banks are automatically switched, and the firmware can immediately write into the endpoint FIFO bank 1.

If the TXRDY bit is not set when the IN request occurs, nothing will be sent by the USB controller.

When the IN packet concerning the bank 0 has been sent, the TXCMPL bit is set by the USB controller. This triggers a USB interrupt if enabled. The firmware will clear the TXCMPL bit before filling the endpoint FIFO bank 0 with new data. The FIFO banks are then automatically switched.

When the IN packet concerning the bank 1 has been sent, the TXCMPL bit is set by the USB controller. This triggers a USB interrupt if enabled. The firmware will clear the TXCMPL bit before filling the endpoint FIFO bank 1 with new data.

The bank switch is performed by the USB controller each time the TXRDY bit is set by the firmware. Until the TXRDY bit has been set by the firmware for an endpoint bank, the USB controller won't send anything at each IN requests concerning this bank.

The firmware will never write more bytes than supported by the endpoint FIFO.

## 21.7 Miscellaneous

#### 21.7.1 USB Reset

The EORINT bit in the USBINT register is set by hardware when a End Of Reset has been detected on the USB bus. This triggers a USB interrupt if enabled. The USB controller is still enabled, but all the USB registers are reset by hardware. The firmware will clear the EORINT bit to allow the next USB reset detection.

| B |

|---|

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X Parameter | Units |

|-------------------|------|-------------------|-----------|-------------|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10          | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30          | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10          | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20          | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40          | ns    |

| T <sub>PXIX</sub> | Min  | х                 | x         | 0           | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7           | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40          | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | x         | 10          | ns    |

Table 27-4.

AC Parameters for a Variable Clock

## 27.4.3 External Program Memory Read Cycle

#### 27.4.13 Clock Waveforms

Valid in normal clock mode. In X2 mode XTAL2 must be changed to XTAL2/2.

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A = 25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50 ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

# AT89C5130A/31A-M

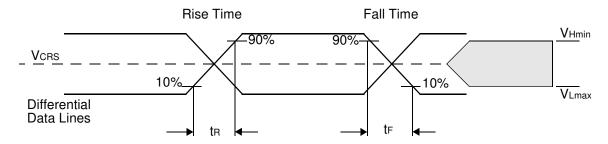

## 27.5 USB AC Parameters

#### Table 27-14. USB AC Parameters

| Symbol              | Parameter                                      | Min     | Тур | Max     | Unit | Test Conditions |

|---------------------|------------------------------------------------|---------|-----|---------|------|-----------------|

| t <sub>R</sub>      | Rise Time                                      | 4       |     | 20      | ns   |                 |

| t <sub>F</sub>      | Fall Time                                      | 4       |     | 20      | ns   |                 |

| t <sub>FDRATE</sub> | Full-speed Data Rate                           | 11.9700 |     | 12.0300 | Mb/s |                 |

| V <sub>CRS</sub>    | Crossover Voltage                              | 1.3     |     | 2.0     | V    |                 |

| t <sub>DJ1</sub>    | Source Jitter Total to Next<br>Transaction     | -3.5    |     | 3.5     | ns   |                 |

| t <sub>DJ2</sub>    | Source Jitter Total for Paired<br>Transactions | -4      |     | 4       | ns   |                 |

| t <sub>JR1</sub>    | Receiver Jitter to Next<br>Transaction         | -18.5   |     | 18.5    | ns   |                 |

| t <sub>JR2</sub>    | Receiver Jitter for Paired<br>Transactions     | -9      |     | 9       | ns   |                 |

## 27.6 SPI Interface AC Parameters

#### 27.6.0.1 Definition of Symbols

Table 27-15. SPI Interface Timing Symbol Definitions

| Signals |          |  |  |

|---------|----------|--|--|

| С       | Clock    |  |  |

| 1       | Data In  |  |  |

| 0       | Data Out |  |  |

| Conditions |                 |  |  |

|------------|-----------------|--|--|

| н          | High            |  |  |

| L          | Low             |  |  |

| V          | Valid           |  |  |

| x          | No Longer Valid |  |  |

| Z          | Floating        |  |  |

## 27.6.0.2 Timings

Test conditions: capacitive load on all pins= 50 pF.

Table 27-16. SPI Interface Master AC Timing

## $V_{DD}$ = 2.7 to 5.5 V, $T_A$ = -40 to +85°C

| Symbol                                | Parameter                                   | Min                    | Мах                    | Unit             |  |  |

|---------------------------------------|---------------------------------------------|------------------------|------------------------|------------------|--|--|

| Slave Mode                            |                                             |                        |                        |                  |  |  |

| Т <sub>снсн</sub>                     | Clock Period                                | 2                      |                        | T <sub>PER</sub> |  |  |

| T <sub>CHCX</sub>                     | Clock High Time                             | 0.8                    |                        | T <sub>PER</sub> |  |  |

| T <sub>CLCX</sub>                     | Clock Low Time                              | 0.8                    |                        | T <sub>PER</sub> |  |  |

| T <sub>SLCH</sub> , T <sub>SLCL</sub> | SS Low to Clock edge                        | 100                    |                        | ns               |  |  |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge              | 50                     |                        | ns               |  |  |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge            | 50                     |                        | ns               |  |  |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge          |                        | 50                     | ns               |  |  |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge      | 0                      |                        | ns               |  |  |

| T <sub>CLSH</sub> , T <sub>CHSH</sub> | SS High after Clock Edge                    | 0                      |                        | ns               |  |  |

| T <sub>SLOV</sub>                     | SS Low to Output Data Valid                 |                        | 4T <sub>PER</sub> +20  | ns               |  |  |

| Т <sub>SHOX</sub>                     | Output Data Hold after SS High              |                        | 2T <sub>PER</sub> +100 | ns               |  |  |

| T <sub>SHSL</sub>                     | $\overline{SS}$ High to $\overline{SS}$ Low | 2T <sub>PER</sub> +120 |                        |                  |  |  |

| T <sub>ILIH</sub>                     | Input Rise Time                             |                        | 2                      | μs               |  |  |

| T <sub>IHIL</sub>                     | Input Fall Time                             |                        | 2                      | μs               |  |  |

| T <sub>OLOH</sub>                     | Output Rise time                            |                        | 100                    | ns               |  |  |

| Т <sub>оног</sub>                     | Output Fall Time                            |                        | 100                    | ns               |  |  |

|                                       | Master Mode                                 |                        |                        |                  |  |  |

| Т <sub>снсн</sub>                     | Clock Period                                | 4                      |                        | T <sub>PER</sub> |  |  |

| Т <sub>снсх</sub>                     | Clock High Time                             | 2T <sub>PER</sub> -20  |                        | ns               |  |  |

| T <sub>CLCX</sub>                     | Clock Low Time                              | 2T <sub>PER</sub> -20  |                        | ns               |  |  |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge              | 50                     |                        | ns               |  |  |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge            | 50                     |                        | ns               |  |  |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge          |                        | 20                     | ns               |  |  |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge      | 0                      |                        | ns               |  |  |

|                                       |                                             |                        |                        |                  |  |  |

Note: T<sub>PER</sub> is XTAL period when SPI interface operates in X2 mode or twice XTAL period when SPI interface operates in X1 mode.

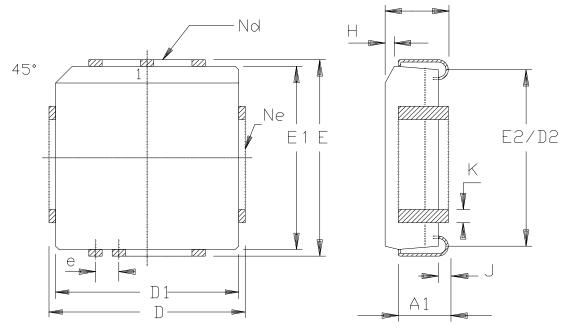

## 29.2 52-lead PLCC

|     | ММ     |        | IN    | СН    |

|-----|--------|--------|-------|-------|

| A   | 4. 20  | 4. 57  | . 165 | . 180 |

| A1  | 2, 29  | 3, 30  | , 090 | , 130 |

| D   | 19.94  | 20.19  | , 785 | . 795 |

| D 1 | 19.05  | 19. 25 | , 750 | . 758 |

| D2  | 17.53  | 18.54  | , 690 | , 730 |

| E   | 19, 94 | 20, 19 | , 785 | , 795 |

| E 1 | 19.05  | 19.25  | , 750 | . 758 |

| E2  | 17.53  | 18.54  | , 690 | , 730 |

| e   | 1. 27  | BSC    | , 050 | BSC   |

| Н   | 1.07   | 1.42   | , 042 | , 056 |

| J   | 0.51   | -      | , 020 | _     |

| К   | 0.33   | 0.53   | . 013 | . 021 |

| Nd  |        | 13     | 13    |       |

| Ne  |        | 13     | 13    |       |

| P   | KG STD | 00     |       |       |

## STANDARD NOTES FOR PLCC

1/ CONTROLLING DIMENSIONS : INCHES

2/ DIMENSIONING AND TOLERANCING PER ANSI Y 14.5M - 1982.

3/ "D" AND "E1" DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTUSIONS.

MOLD FLASH OR PROTUSIONS SHALL NOT EXCEED 0.20 mm (.008 INCH) PER SIDE.