Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | LED, POR, PWM, WDT                                                         |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 16KB (16K × 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-VQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5130a-rdtum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

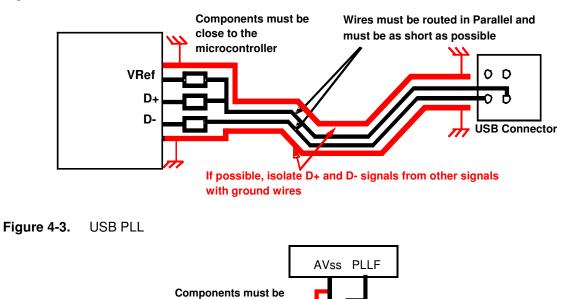

## 4.2 PCB Recommandations

Figure 4-2. USB Pads

Isolate filter components with a ground wire

close to the microcontroller

#### 8.3.7.3 Hardware Security

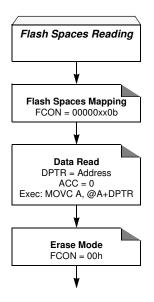

The following procedure is used to read the Hardware Security space and is summarized in Figure 8-8:

- Map the Hardware Security space by writing 04h in FCON register.

- Read the byte in Accumulator by executing MOVC A, @A+DPTR with A = 0 & DPTR = 0000h.

- Figure 8-8. Reading Procedure

#### 8.4 Registers

Table 8-4.

FCON (S:D1h) Flash Control Register

| 7          | 6               | 5                           | 4                                                                                                                                | 3                                        | 2     | 1     | 0     |  |

|------------|-----------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------|-------|-------|--|

| FPL3       | FPL2            | FPL1                        | FPL0                                                                                                                             | FPS                                      | FMOD1 | FMOD0 | FBUSY |  |

| Bit Number | Bit<br>Mnemonic | Description                 |                                                                                                                                  |                                          |       |       |       |  |

| 7-4        | FPL3:0          | Write 5Xh fol               | Programming Launch Command Bits<br>Write 5Xh followed by AXh to launch the programming according to FMOD1:0.<br>(see Table 8-3.) |                                          |       |       |       |  |

| 3          | FPS             | Set to map th               | Flash Map Program Space<br>Set to map the column latch space in the data memory space.<br>Clear to re-map the data memory space. |                                          |       |       |       |  |

| 2-1        | FMOD1:0         | Flash Mode<br>See Table 8-2 | Flash Mode<br>See Table 8-2 or Table 8-3.                                                                                        |                                          |       |       |       |  |

| 0          | FBUSY           | Clear by hard               |                                                                                                                                  | gramming is in<br>rogramming is<br>ware. |       |       |       |  |

Reset Value = 0000 0000b

#### Table 9-5. Program Lock Bits of the SSB

| Progra            | Program Lock Bits |     |                                                                       |

|-------------------|-------------------|-----|-----------------------------------------------------------------------|

| Security<br>Level | LB0               | LB1 | Protection Description                                                |

| 1                 | U                 | U   | No program lock features enabled.                                     |

| 2                 | Р                 | U   | ISP programming of the Flash is disabled.                             |

| 3                 | Р                 | Р   | Same as 2, also verify through ISP programming interface is disabled. |

Notes: 1. U: unprogrammed or "one" level.

2. P: programmed or "zero" level.

3. WARNING: Security level 2 and 3 should only be programmed after Flash and code verification.

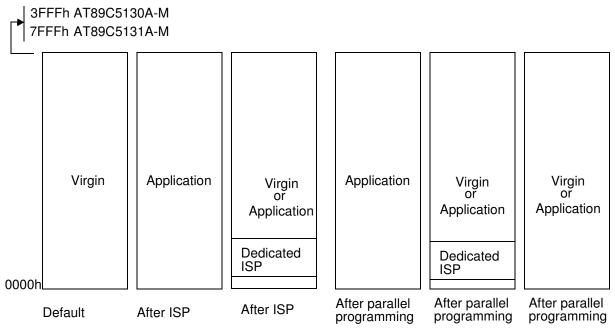

## 9.5 Flash Memory Status

AT89C5130A/31A-M parts are delivered with the ISP boot in the Flash memory. After ISP or parallel programming, the possible contents of the Flash memory are summarized in Figure 9-1:

## 9.6 Memory Organization

In the AT89C5130A/31A-M, the lowest 16/32K of the 64 Kbyte program memory address space is filled by internal Flash.

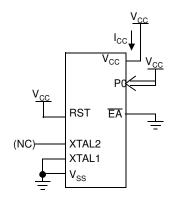

When the  $\overline{EA}$  is pin high, the processor fetches instructions from internal program Flash. Bus expansion for accessing program memory from 16/32K upward is automatic since external instruction fetches occur automatically when the program counter exceeds 3FFFh (16K) or 7FFFh (32K). If the  $\overline{EA}$  pin is tied low, all program memory fetches are from external memory. If all storage is on chip, then byte location 3FFFh (16K) or 7FFFh (32K) should be left vacant to prevent and undesired pre-fetch from external program memory address 4000h (16K) or 8000h (32K).

## 42 AT89C5130A/31A-M

## 13. Timer 2

The Timer 2 in the AT89C5130A/31A-M is the standard C52 Timer 2. It is a 16-bit timer/counter: the count is maintained by two cascaded eight-bit timer registers, TH2 and TL2. It is controlled by T2CON (Table 13-1) and T2MOD (Table 13-2) registers. Timer 2 operation is similar to Timer 0 and Timer 1. C/T2 selects  $F_{OSC}/12$  (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to be incremented by the selected input.

Timer 2 has 3 operating modes: capture, auto reload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).

Refer to the Atmel 8-bit microcontroller hardware documentation for the description of Capture and Baud Rate Generator Modes.

Timer 2 includes the following enhancements:

- · Auto-reload mode with up or down counter

- Programmable Clock-output

### 13.1 Auto-reload Mode

The Auto-reload mode configures Timer 2 as a 16-bit timer or event counter with automatic reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (refer to the Atmel 8-bit microcontroller hardware description). If DCEN bit is set, Timer 2 acts as an Up/down timer/counter as shown in Figure 13-1. In this mode the T2EX pin controls the direction of count.

When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.

When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.

The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.

Table 13-2. T2MOD Register T2MOD - Timer 2 Mode Control Register (C9h) 7 2 0 6 5 4 3 1 T2OE DCEN ------Bit Bit Number Mnemonic Description Reserved 7 The value read from this bit is indeterminate. Do not set this bit. Reserved 6 The value read from this bit is indeterminate. Do not set this bit. Reserved 5 -The value read from this bit is indeterminate. Do not set this bit. Reserved 4 The value read from this bit is indeterminate. Do not set this bit. Reserved 3 \_ The value read from this bit is indeterminate. Do not set this bit. Reserved 2 The value read from this bit is indeterminate. Do not set this bit. Timer 2 Output Enable bit 1 T2OE Cleared to program P1.0/T2 as clock input or I/O port. Set to program P1.0/T2 as clock output. Down Counter Enable bit 0 DCEN Cleared to disable Timer 2 as up/down counter. Set to enable Timer 2 as up/down counter.

Reset Value = XXXX XX00b Not bit addressable

Reset Value = 00XX X000b Not bit addressable

The CMOD register includes three additional bits associated with the PCA (See Figure 14-1 and Table 14-1).

- The CIDL bit allows the PCA to stop during idle mode.

- The WDTE bit enables or disables the watchdog function on module 4.

- The ECF bit when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows.

The CCON register contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (see Table 14-2).

- Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

- Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags can only be cleared by software.

#### Table 14-2. CCON Register

CCON - PCA Counter Control Register (D8h)

| 7  | 6  | 5 | 4    | 3    | 2    | 1    | 0    |

|----|----|---|------|------|------|------|------|

| CF | CR | - | CCF4 | CCF3 | CCF2 | CCF1 | CCF0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                     |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | CF              | PCA Counter Overflow flag<br>Set by hardware when the counter rolls over. CF flags an interrupt if bit ECF in CMOD is set.<br>CF may be set by either hardware or software but can only be cleared by software. |

| 6             | CR              | PCA Counter Run control bit<br>Must be cleared by software to turn the PCA counter off.<br>Set by software to turn the PCA counter on.                                                                          |

| 5             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                 |

| 4             | CCF4            | PCA Module 4 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                  |

| 3             | CCF3            | PCA Module 3 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                  |

| 2             | CCF2            | PCA Module 2 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs.                                                                                                  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                     |

|---------------|-----------------|---------------------------------------------------------------------------------|

| 7             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |

| 6             | PPCL            | PCA interrupt Priority bit<br>Refer to PPCH for priority level.                 |

| 5             | PT2L            | Timer 2 overflow interrupt Priority bit<br>Refer to PT2H for priority level.    |

| 4             | PSL             | Serial port Priority bit<br>Refer to PSH for priority level.                    |

| 3             | PT1L            | Timer 1 overflow interrupt Priority bit<br>Refer to PT1H for priority level.    |

| 2             | PX1L            | External interrupt 1 Priority bit<br>Refer to PX1H for priority level.          |

| 1             | PT0L            | Timer 0 overflow interrupt Priority bit<br>Refer to PT0H for priority level.    |

| 0             | PX0L            | External interrupt 0 Priority bit<br>Refer to PX0H for priority level.          |

Reset Value = X000 0000b Bit addressable

## Table 16-4.IPH0 RegisterIPH0 - Interrupt Priority High Register (B7h)

| 7 | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|---|------|------|-----|------|------|------|------|

| - | PPCH | PT2H | PSH | PT1H | PX1H | РТОН | РХОН |

## IEN1 - Interrupt Enable Register (B1h)

| 7             | 6               | 5              | 4                                                                                             | 3            | 2    | 1    | 0   |  |

|---------------|-----------------|----------------|-----------------------------------------------------------------------------------------------|--------------|------|------|-----|--|

| -             | EUSB            | -              | -                                                                                             | -            | ESPI | ETWI | ЕКВ |  |

| Bit<br>Number | Bit<br>Mnemonic | Description    |                                                                                               |              |      |      |     |  |

| 7             | -               | Reserved       |                                                                                               |              |      |      |     |  |

| 6             | EUSB            | Cleared to dis | JSB Interrupt Enable bit<br>Cleared to disable USB interrupt.<br>Set to enable USB interrupt. |              |      |      |     |  |

| 5             | -               | Reserved       |                                                                                               |              |      |      |     |  |

| 4             | -               | Reserved       |                                                                                               |              |      |      |     |  |

| 3             | -               | Reserved       |                                                                                               |              |      |      |     |  |

| 2             | ESPI            | Cleared to dis | SPI interrupt Enable bit<br>Cleared to disable SPI interrupt.<br>Set to enable SPI interrupt. |              |      |      |     |  |

| 1             | ETWI            |                | t <b>Enable bit</b><br>sable TWI inter<br>TWI interrupt.                                      |              |      |      |     |  |

| 0             | EKB             | Cleared to dis | terrupt Enable<br>sable keyboard<br>keyboard inte                                             | l interrupt. |      |      |     |  |

## 17. Keyboard Interface

## 17.1 Introduction

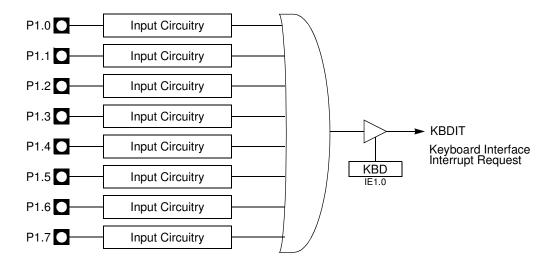

The AT89C5130A/31A-M implements a keyboard interface allowing the connection of a 8 x n matrix keyboard. It is based on 8 inputs with programmable interrupt capability on both high or low level. These inputs are available as an alternate function of P1 and allow to exit from idle and power down modes.

## 17.2 Description

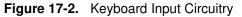

The keyboard interface communicates with the C51 core through 3 special function registers: KBLS, the Keyboard Level Selection register (Table 17-3), KBE, The Keyboard interrupt Enable register (Table 17-2), and KBF, the Keyboard Flag register (Table 17-1).

#### 17.2.1 Interrupt

The keyboard inputs are considered as 8 independent interrupt sources sharing the same interrupt vector. An interrupt enable bit (KBD in IE1) allows global enable or disable of the keyboard interrupt (see Figure 17-1). As detailed in Figure 17-2 each keyboard input has the capability to detect a programmable level according to KBLS.x bit value. Level detection is then reported in interrupt flags KBF.x that can be masked by software using KBE.x bits.

This structure allow keyboard arrangement from 1 by n to 8 by n matrix and allow usage of P1 inputs for other purpose.

Figure 17-1. Keyboard Interface Block Diagram

Table 17-3.

KBLS Register

KBLS-Keyboard Level Selector Register (9Ch)

| 7          | 6               | 5             | 4                                                                                                                                                             | 3                                                       | 2     | 1     | 0     |

|------------|-----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------|-------|-------|

| KBLS7      | KBLS6           | KBLS5         | KBLS4                                                                                                                                                         | KBLS3                                                   | KBLS2 | KBLS1 | KBLS0 |

| Bit Number | Bit<br>Mnemonic | Description   |                                                                                                                                                               |                                                         |       |       |       |

| 7          | KBLS7           | Cleared to en |                                                                                                                                                               | <b>ction bit</b><br>I detection on P<br>tection on Port |       |       |       |

| 6          | KBLS6           | Cleared to en |                                                                                                                                                               | <b>ction bit</b><br>I detection on P<br>tection on Port |       |       |       |

| 5          | KBLS5           | Cleared to en |                                                                                                                                                               | <b>ction bit</b><br>I detection on P<br>tection on Port |       |       |       |

| 4          | KBLS4           | Cleared to en |                                                                                                                                                               | <b>ction bit</b><br>I detection on P<br>tection on Port |       |       |       |

| 3          | KBLS3           | Cleared to en |                                                                                                                                                               | <b>ction bit</b><br>I detection on P<br>tection on Port |       |       |       |

| 2          | KBLS2           | Cleared to en | <b>Keyboard line 2 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 2.<br>Set to enable a high level detection on Port line 2. |                                                         |       |       |       |

| 1          | KBLS1           | Cleared to en | Keyboard line 1 Level Selection bit<br>Cleared to enable a low level detection on Port line 1.<br>Set to enable a high level detection on Port line 1.        |                                                         |       |       |       |

| 0          | KBLS0           | Cleared to en |                                                                                                                                                               | <b>ction bit</b><br>I detection on P<br>tection on Port |       |       |       |

Reset Value = 0000 0000b

#### 19.2.3 SPI Serial Clock (SCK)

This signal is used to synchronize the data movement both in and out the devices through their MOSI and MISO lines. It is driven by the Master for eight clock cycles which allows to exchange one byte on the serial lines.

#### 19.2.4 Slave Select (SS)

Each Slave peripheral is selected by one Slave Select pin  $(\overline{SS})$ . This signal must stay low for any message for a Slave. It is obvious that only one Master ( $\overline{SS}$  high level) can drive the network. The Master may select each Slave device by software through port pins (Figure 19-1). To prevent bus conflicts on the MISO line, only one slave should be selected at a time by the Master for a transmission.

In a Master configuration, the  $\overline{SS}$  line can be used in conjunction with the MODF flag in the SPI Status register (SPSTA) to prevent multiple masters from driving MOSI and SCK (see Section "Error Conditions", page 98).

A high level on the  $\overline{SS}$  pin puts the MISO line of a Slave SPI in a high-impedance state.

The SS pin could be used as a general-purpose if the following conditions are met:

- The device is configured as a Master and the SSDIS control bit in SPCON is set. This kind of configuration can be found when only one Master is driving the network and there is no way that the  $\overline{SS}$  pin could be pulled low. Therefore, the MODF flag in the SPSTA will never be set<sup>(1)</sup>.

- The Device is configured as a Slave with CPHA and SSDIS control bits set<sup>(2)</sup> This kind of configuration can happen when the system comprises one Master and one Slave only. Therefore, the device should always be selected and there is no reason that the Master uses the SS pin to select the communicating Slave device.

- Notes: 1. Clearing SSDIS control bit does not clear MODF.

- 2. Special care should be taken not to set SSDIS control bit when CPHA ='0' because in this mode, the SS is used to start the transmission.

#### 19.2.5 Baud Rate

In Master mode, the baud rate can be selected from a baud rate generator which is controlled by three bits in the SPCON register: SPR2, SPR1 and SPR0. The Master clock is chosen from one of seven clock rates resulting from the division of the internal clock by 4, 8, 16, 32, 64 or 128.

Table 19-1 gives the different clock rates selected by SPR2:SPR1:SPR0:

| SPR2 | SPR1 | SPR0 | Clock Rate                   | Baud Rate Divisor (BD) |

|------|------|------|------------------------------|------------------------|

| 0    | 0    | 0    | Don't Use                    | No BRG                 |

| 0    | 0    | 1    | F <sub>CLK PERIPH</sub> /4   | 4                      |

| 0    | 1    | 0    | F <sub>CLK PERIPH</sub> /8   | 8                      |

| 0    | 1    | 1    | F <sub>CLK PERIPH</sub> /16  | 16                     |

| 1    | 0    | 0    | F <sub>CLK PERIPH</sub> /32  | 32                     |

| 1    | 0    | 1    | F <sub>CLK PERIPH</sub> /64  | 64                     |

| 1    | 1    | 0    | F <sub>CLK PERIPH</sub> /128 | 128                    |

Table 19-1. SPI Master Baud Rate Selection

## 20.1.4 Slave Transmitter Mode

In the slave transmitter mode, a number of data bytes are transmitted to a master receiver (Figure 20-7). Data transfer is initialized as in the slave receiver mode. When SSADR and SSCON have been initialized, the TWI module waits until it is addressed by its own slave address followed by the data direction bit which must be at logic 1 (R) for TWI to operate in the slave transmitter mode. After its own slave address and the R bit have been received, the serial interrupt flag is set and a valid status code can be read from SSCS. This status code is used to vector to an interrupt service routine. The appropriate action to be taken for each of these status code is detailed in Table . The slave transmitter mode may also be entered if arbitration is lost while the TWI module is in the master mode.

If the AA bit is reset during a transfer, the TWI module will transmit the last byte of the transfer and enter state C0h or C8h. the TWI module is switched to the not addressed slave mode and will ignore the master receiver if it continues the transfer. Thus the master receiver receives all 1's as serial data. While AA is reset, the TWI module does not respond to its own slave address. However, the 2-wire bus is still monitored and address recognition may be resume at any time by setting AA. This means that the AA bit may be used to temporarily isolate the TWI module from the 2-wire bus.

## 20.1.5 Miscellaneous States

There are two SSCS codes that do not correspond to a define TWI hardware state (Table 20-9 ). These codes are discuss hereafter.

Status F8h indicates that no relevant information is available because the serial interrupt flag is not set yet. This occurs between other states and when the TWI module is not involved in a serial transfer.

Status 00h indicates that a bus error has occurred during a TWI serial transfer. A bus error is caused when a START or a STOP condition occurs at an illegal position in the format frame. Examples of such illegal positions happen during the serial transfer of an address byte, a data byte, or an acknowledge bit. When a bus error occurs, SI is set. To recover from a bus error, the STO flag must be set and SI must be cleared. This causes the TWI module to enter the not addressed slave mode and to clear the STO flag (no other bits in SSCON are affected). The SDA and SCL lines are released and no STOP condition is transmitted.

## 20.2 Notes

The TWI module interfaces to the external 2-wire bus via two port pins: SCL (serial clock line) and SDA (serial data line). To avoid low level asserting on these lines when the TWI module is enabled, the output latches of SDA and SLC must be set to logic 1.

|     |     |     | Bit Freque                 | ency ( kHz)                |                              |

|-----|-----|-----|----------------------------|----------------------------|------------------------------|

| CR2 | CR1 | CR0 | F <sub>OSCA</sub> = 12 MHz | F <sub>OSCA</sub> = 16 MHz | F <sub>OSCA</sub> divided by |

| 0   | 0   | 0   | 47                         | 62.5                       | 256                          |

| 0   | 0   | 1   | 53.5                       | 71.5                       | 224                          |

| 0   | 1   | 0   | 62.5                       | 83                         | 192                          |

| 0   | 1   | 1   | 75                         | 100                        | 160                          |

**Table 20-4.**Bit Frequency Configuration

## 20.3 Registers

Table 20-10. SSCON Register

SSCON - Synchronous Serial Control Register (93h)

| 7          | 6               | 5                                                                                      | 4                                                                                                                              | 3                                                       | 2  | 1   | 0   |  |  |

|------------|-----------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----|-----|-----|--|--|

| CR2        | SSIE            | STA                                                                                    | STO                                                                                                                            | SI                                                      | AA | CR1 | CR0 |  |  |

| Bit Number | Bit<br>Mnemonic | Description                                                                            |                                                                                                                                |                                                         |    |     |     |  |  |

| 7          | CR2             | Control Rate<br>See .                                                                  | bit 2                                                                                                                          |                                                         |    |     |     |  |  |

| 6          | SSIE            | Clear to disab                                                                         | Synchronous Serial Interface Enable bit<br>Clear to disable SSLC.<br>Set to enable SSLC.                                       |                                                         |    |     |     |  |  |

| 5          | STA             | Start flag<br>Set to send a                                                            | START conditi                                                                                                                  | on on the bus.                                          |    |     |     |  |  |

| 4          | ST0             | Stop flag<br>Set to send a                                                             | Stop flag<br>Set to send a STOP condition on the bus.                                                                          |                                                         |    |     |     |  |  |

| 3          | SI              | Set by hardwa                                                                          |                                                                                                                                | <b>Ipt flag</b><br>al interrupt is re<br>to acknowledge |    |     |     |  |  |

| 2          | AA              | Clear in maste<br>SDA).<br>Clear to disab<br>Set to recogni<br>modes.<br>Set in master | Clear to disable SLA or GCA recognition.<br>Set to recognise SLA or GCA (if GC set) for entering slave receiver or transmitter |                                                         |    |     |     |  |  |

| 1          | CR1             |                                                                                        | Control Rate bit 1<br>See Table 20-4                                                                                           |                                                         |    |     |     |  |  |

| 0          | CR0             | Control Rate<br>See Table 20-                                                          |                                                                                                                                |                                                         |    |     |     |  |  |

## Table 20-11. SSDAT (095h) - Synchronous Serial Data Register (read/write)

| SD7        | SD6             | SD5           | SD4                          | SD3 | SD2 | SD1 | SD0 |  |  |  |

|------------|-----------------|---------------|------------------------------|-----|-----|-----|-----|--|--|--|

| 7          | 6               | 5             | 5 4 3 2 1 0                  |     |     |     |     |  |  |  |

| Bit Number | Bit<br>Mnemonic | Description   | Description                  |     |     |     |     |  |  |  |

| 7          | SD7             | Address bit 7 | Address bit 7 or Data bit 7. |     |     |     |     |  |  |  |

| 6          | SD6             | Address bit 6 | Address bit 6 or Data bit 6. |     |     |     |     |  |  |  |

| 5          | SD5             | Address bit 5 | Address bit 5 or Data bit 5. |     |     |     |     |  |  |  |

| 4          | SD4             | Address bit 4 | Address bit 4 or Data bit 4. |     |     |     |     |  |  |  |

| 3          | SD3             | Address bit 3 | Address bit 3 or Data bit 3. |     |     |     |     |  |  |  |

| 2          | SD2             | Address bit 2 | Address bit 2 or Data bit 2. |     |     |     |     |  |  |  |

Table 21-9. UEPSTAX (S:CEh) USB Endpoint X Status Register

|                  |                 | 7  6  5  4  3  2  1  0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                               |                                                                           |                                                                 |                                                        |                                                       |                                                          |                                        |

|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|----------------------------------------|

|                  |                 | DIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RXOUTB1                                                                       | STALLRQ                                                                   | TXRDY                                                           | STL/CRC                                                | RXSETUP                                               | RXOUTB0                                                  | ТХСМР                                  |

| Bit Number       | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                               |                                                                           |                                                                 |                                                        |                                                       |                                                          |                                        |

| 7                | DIR             | Control Endpoir<br>This bit is used o<br>USB Endpoint X<br>This bit determine<br>The device firmw<br>firmware will clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nly if the endpo<br>Control Registe<br>es the Control o<br>rare will set this | er").<br>data and status                                                  | direction.                                                      |                                                        |                                                       | -                                                        |                                        |

| 6                | RXOUTB1         | Received OUT I<br>This bit is set by H<br>Then, the endpoi<br>Interrupt Register<br>bit has been clea<br>This bit will be clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nardware after a<br>nt interrupt is tr<br>r" on page 148<br>red, excepted t   | a new packet ha<br>iggered if enab<br>and all the folk<br>for Isochronous | as been stored<br>led (see"UEPII<br>owing OUT pac<br>Endpoints. | in the endpoint<br>NT Register UE<br>ckets to the end  | PINT (S:F8h re<br>Ipoint bank 1 ar                    | ead-only) USB E<br>re rejected (NAM                      | Endpoint                               |

| 5                | STALLRQ         | Stall Handshake<br>Set this bit to req<br>For CONTROL e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | uest a STALL a                                                                |                                                                           |                                                                 |                                                        |                                                       | rwise.                                                   |                                        |

| 4                | TXRDY           | TX Packet Read<br>Set this bit after a<br>endpoint FIFO or<br>Length Packet.<br>This bit is cleared<br>acknowledged th<br>triggered if enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | a packet has be<br>hly after this bit<br>d by hardware,<br>e packet for Co    | has been clear<br>as soon as the<br>ontrol, Bulk and                      | ed. Set this bit<br>packet has be<br>Interrupt endp             | without writing<br>en sent for Isoc<br>oints. When thi | data to the end<br>hronous endpo<br>s bit is cleared, | point FIFO to s<br>ints, or after the<br>the endpoint in | end a Zero<br>e host has<br>terrupt is |

| 3                | STLCRC          | Stall Sent/CRC error flag         - For Control, Bulk and Interrupt Endpoints:         This bit is set by hardware after a STALL handshake has been sent as requested by STALLRQ. Then, the endpoint interrupt is triggered if enabled (see"UEPINT Register UEPINT (S:F8h read-only) USB Endpoint Interrupt Register" on page 148)         It will be cleared by the device firmware.         - For Isochronous Endpoints (Read-Only):         This bit is set by hardware if the last received data is corrupted (CRC error on data).         This bit is updated by hardware when a new data is received.                                                                                                                                                                    |                                                                               |                                                                           |                                                                 |                                                        |                                                       |                                                          |                                        |

| 2                | RXSETUP         | <b>Received SETUP</b><br>This bit is set by hardware when a valid SETUP packet has been received from the host. Then, all the other bits of the register are cleared by hardware and the endpoint interrupt is triggered if enabled (see"UEPINT Register UEPINT (S:F8 read-only) USB Endpoint Interrupt Register" on page 148).<br>It will be cleared by the device firmware after reading the SETUP data from the endpoint FIFO.                                                                                                                                                                                                                                                                                                                                              |                                                                               |                                                                           |                                                                 |                                                        |                                                       |                                                          |                                        |

| 1                | RXOUTB0         | <b>Received OUT Data Bank 0</b> (see also RXOUTB1 bit for Ping-pong Endpoints)<br>This bit is set by hardware after a new packet has been stored in the endpoint FIFO data bank 0. Then, the endpoint<br>interrupt is triggered if enabled (see"UEPINT Register UEPINT (S:F8h read-only) USB Endpoint Interrupt Register" on<br>page 148) and all the following OUT packets to the endpoint bank 0 are rejected (NAK'ed) until this bit has been cleared<br>excepted for Isochronous Endpoints. However, for control endpoints, an early SETUP transaction may overwrite the<br>content of the endpoint FIFO, even if its Data packet is received while this bit is set.<br>This bit will be cleared by the device firmware after reading the OUT data from the endpoint FIFO. |                                                                               |                                                                           |                                                                 |                                                        |                                                       | egister" on<br>been cleared,                             |                                        |

| 0<br>Reset Value | TXCMPL          | Transmitted IN I<br>This bit is set by<br>accepted (ACK'e<br>enabled (see"UE<br>This bit will be cle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | hardware after<br>d) by the host f<br>PINT Register                           | an IN packet ha<br>or Control, Bulk<br>UEPINT (S:F8h                      | and Interrupt<br>read-only) US                                  | endpoints. The B Endpoint Int                          | n, the endpoint                                       | interrupt is trigg                                       |                                        |

Reset Value = 00h

# Table 21-12. UBYCTHX Register UBYCTHX (S:E3h) USP Data (S:E3h)

USB Byte Count High Register X (X = EPNUM set in UEPNUM Register UEP-

| 7          | 6            | 5                                         | 4                                                                                                                                                                                                                                                                                                            | 3 | 2 | 1 | 0 |  |  |

|------------|--------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|--|--|

| -          | -            | -                                         | BYCT9 BYC                                                                                                                                                                                                                                                                                                    |   |   |   |   |  |  |

| Bit Number | Bit Mnemonio | Descriptio                                | Description                                                                                                                                                                                                                                                                                                  |   |   |   |   |  |  |

| 7-2        | -            | Reserved<br>The value r                   | Reserved<br>The value read from these bits is always 0. Do not set these bits.                                                                                                                                                                                                                               |   |   |   |   |  |  |

| 2-0        | BYCT[10:8]   | Most Signif<br>part is prov<br>Register X | Byte Count MSB<br>Most Significant Byte of the byte count of a received data packet. The Least significant<br>part is provided by UBYCTLX Register UBYCTLX (S:E2h) USB Byte Count Low<br>Register X (X = EPNUM set in UEPNUM Register UEPNUM (S:C7h) USB Endpoint<br>Number) (see Figure 21-11 on page 145). |   |   |   |   |  |  |

NUM (S:C7h) USB Endpoint Number)

Reset Value = 00h

All other pins are disconnected.

#### 27.2.1 LED's

Table 27-1. LED Outputs DC Parameters

| Symbo           | Parameter                                   | Min | Тур | Max | Unit | Test Conditions     |

|-----------------|---------------------------------------------|-----|-----|-----|------|---------------------|

|                 |                                             | 1   | 2   | 4   | mA   | 2 mA configuration  |

| I <sub>OL</sub> | Output Low Current, P3.6 and P3.7 LED modes | 2   | 4   | 8   | mA   | 4 mA configuration  |

|                 |                                             | 5   | 10  | 20  | mA   | 10 mA configuration |

Note: 1. (Ta = -20°C to +50°C, V<sub>CC</sub> - V<sub>OL</sub> = 2 V  $\pm$  20%)

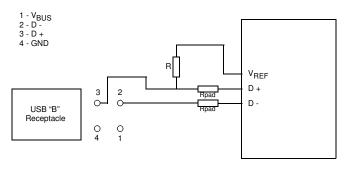

## 27.3 USB DC Parameters

$\begin{array}{l} \mathsf{R}=1.5 \; \mathsf{k}\Omega \\ \mathsf{R}_{\mathsf{pad}}=27\Omega \end{array}$

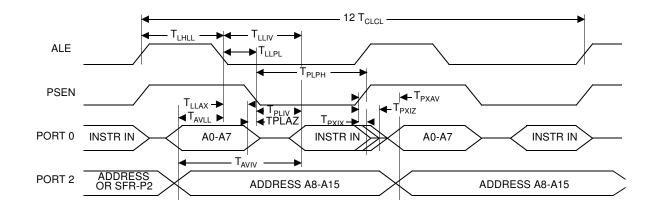

#### 27.4.2 External Program Memory Characteristics Table 27-2. Symbol Descriptio

Symbol Description Parameter Symbol Т Oscillator Clock Period ALE Pulse Width T<sub>LHLL</sub> Address Valid to ALE  $\mathsf{T}_{\mathsf{AVLL}}$  $\mathsf{T}_{\mathsf{LLAX}}$ Address Hold after ALE  $\mathsf{T}_{\mathsf{LLIV}}$ ALE to Valid Instruction In ALE to PSEN  $\mathsf{T}_{\mathsf{LLPL}}$ PSEN Pulse Width T<sub>PLPH</sub> PSEN to Valid Instruction In T<sub>PLIV</sub> Input Instruction Hold after PSEN T<sub>PXIX</sub> Input Instruction Float after PSEN T<sub>PXIZ</sub> Address to Valid Instruction In T<sub>AVIV</sub> PSEN Low to Address Float  $\mathsf{T}_{\mathsf{PLAZ}}$

#### Table 27-3. AC Parameters for a Fix Clock (F = 40 MHz)

| Symbol            | Min | Мах | Units |

|-------------------|-----|-----|-------|

| Т                 | 25  |     | ns    |

| T <sub>LHLL</sub> | 40  |     | ns    |

| T <sub>AVLL</sub> | 10  |     | ns    |

| T <sub>LLAX</sub> | 10  |     | ns    |

| T <sub>LLIV</sub> |     | 70  | ns    |

| T <sub>LLPL</sub> | 15  |     | ns    |

| T <sub>PLPH</sub> | 55  |     | ns    |

| T <sub>PLIV</sub> |     | 35  | ns    |

| T <sub>PXIX</sub> | 0   |     | ns    |

| T <sub>PXIZ</sub> |     | 18  | ns    |

| T <sub>AVIV</sub> |     | 85  | ns    |

| T <sub>PLAZ</sub> |     | 10  | ns    |

| B |

|---|

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X Parameter | Units |

|-------------------|------|-------------------|-----------|-------------|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10          | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30          | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10          | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20          | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40          | ns    |

| T <sub>PXIX</sub> | Min  | х                 | x         | 0           | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7           | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40          | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | x         | 10          | ns    |

Table 27-4.

AC Parameters for a Variable Clock

## 27.4.3 External Program Memory Read Cycle

#### 27.4.6 External Data Memory Read Cycle

#### 27.4.7 Serial Port Timing - Shift Register Mode

Table 27-8. Symbol Description (F = 40 MHz)

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

Table 27-9.

AC Parameters for a Fix Clock (F = 40 MHz)

| Symbol            | Min | Мах | Units |

|-------------------|-----|-----|-------|

| T <sub>XLXL</sub> | 300 |     | ns    |

| T <sub>QVHX</sub> | 200 |     | ns    |

| T <sub>XHQX</sub> | 30  |     | ns    |

| T <sub>XHDX</sub> | 0   |     | ns    |

| T <sub>XHDV</sub> |     | 117 | ns    |

Table 27-10. AC Parameters for a Variable Clock

| Symbol            | Туре | Standard<br>Clock | X2 Clock | X Parameter<br>for -M Range | Units |

|-------------------|------|-------------------|----------|-----------------------------|-------|

| T <sub>XLXL</sub> | Min  | 12 T              | 6 T      |                             | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50                          | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20                          | ns    |

| T <sub>XHDX</sub> | Min  | x                 | х        | 0                           | ns    |

| T <sub>XHDV</sub> | Max  | 10 T - x          | 5 T- x   | 133                         | ns    |

#### Headquarters

*Atmel Corporation* 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com Technical Support 8051@atmel.com

Sales Contact www.atmel.com/contacts

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNTIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.