#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | LED, POR, PWM, WDT                                                         |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | •                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 52-LCC (J-Lead)                                                            |

| Supplier Device Package    | 52-PLCC (19.15x19.15)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5131a-s3sum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

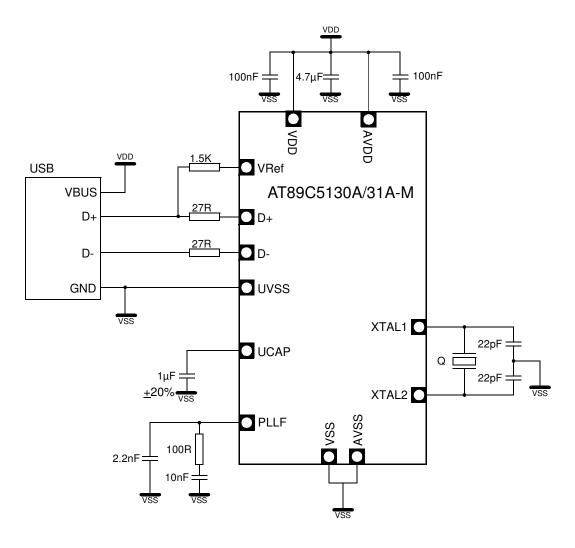

# 4. Typical Application

# 4.1 Recommended External components

All the external components described in the figure below must be implemented as close as possible from the microcontroller package.

The following figure represents the typical wiring schematic.

Figure 4-1. Typical Application

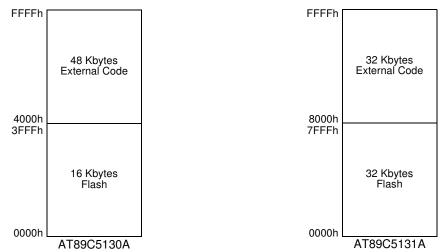

# 8. Program/Code Memory

The AT89C5130A/31A-M implement 16/ 32 Kbytes of on-chip program/code memory. Figure 8-1 shows the split of internal and external program/code memory spaces depending on the product.

The Flash memory increases EPROM and ROM functionality by in-circuit electrical erasure and programming. Thanks to the internal charge pump, the high voltage needed for programming or erasing Flash cells is generated on-chip using the standard  $V_{DD}$  voltage. Thus, the Flash Memory can be programmed using only one voltage and allows In- application Software Programming commonly known as IAP. Hardware programming mode is also available using specific programming tool.

Figure 8-1. Program/Code Memory Organization

Note: If the program executes exclusively from on-chip code memory (not from external memory), beware of executing code from the upper byte of on-chip memory (3FFFh/7FFFh) and thereby disrupting I/O Ports 0 and 2 due to external prefetch. Fetching code constant from this location does not affect Ports 0 and 2.

# 8.1 External Code Memory Access

## 8.1.1 Memory Interface

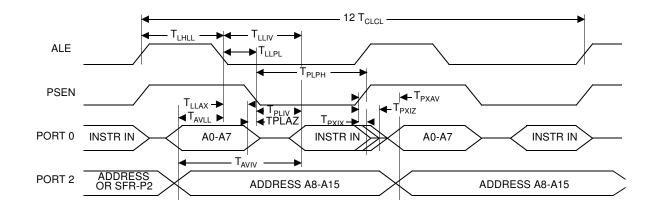

The external memory interface comprises the external bus (Port 0 and Port 2) as well as the bus control signals ( $\overline{\text{PSEN}}$ , and ALE).

Figure 8-2 shows the structure of the external address bus. P0 carries address A7:0 while P2 carries address A15:8. Data D7:0 is multiplexed with A7:0 on P0. Table 8-1 describes the external memory interface signals.

# **10. EEPROM Data Memory**

# 10.1 Description

The 1-Kbyte on-chip EEPROM memory block is located at addresses 0000h to 03FFh of the ERAM memory space and is selected by setting control bits in the EECON register.

A read in the EEPROM memory is done with a MOVX instruction.

A physical write in the EEPROM memory is done in two steps: write data in the column latches and transfer of all data latches into an EEPROM memory row (programming).

The number of data written on the page may vary from 1 to 128 bytes (the page size). When programming, only the data written in the column latch is programmed and a ninth bit is used to obtain this feature. This provides the capability to program the whole memory by bytes, by page or by a number of bytes in a page. Indeed, each ninth bit is set when the writing the corresponding byte in a row and all these ninth bits are reset after the writing of the complete EEPROM row.

# 10.2 Write Data in the Column Latches

Data is written by byte to the column latches as for an external RAM memory. Out of the 11 address bits of the data pointer, the 4 MSBs are used for page selection (row) and 7 are used for byte selection. Between two EEPROM programming sessions, all the addresses in the column latches must stay on the same page, meaning that the 4 MSB must not be changed.

The following procedure is used to write to the column latches:

- Set bit EEE of EECON register

- · Load DPTR with the address to write

- · Store A register with the data to be written

- Execute a MOVX @DPTR, A

- If needed, loop the three last instructions until the end of a 128 bytes page

## 10.3 Programming

The EEPROM programming consists on the following actions:

- Writing one or more bytes of one page in the column latches. Normally, all bytes must belong to the same page; if not, the first page address will be latched and the others discarded.

- Launching programming by writing the control sequence (52h followed by A2h) to the EECON register.

- EEBUSY flag in EECON is then set by hardware to indicate that programming is in progress and that the EEPROM segment is not available for reading.

- The end of programming is indicated by a hardware clear of the EEBUSY flag.

## 10.4 Read Data

The following procedure is used to read the data stored in the EEPROM memory:

- Set bit EEE of EECON register

- Stretch the MOVX to accommodate the slow access time of the column latch (Set bit M0 of AUXR register)

- · Load DPTR with the address to read

- Execute a MOVX A, @DPTR

# Table 13-1. T2CON Register T2CON Timer 2 Control Reg

| 7             | 6               | 5                                                                         | 4                                                                                                                                                                                                                                             | 3                                                                       | 2              | 1        | 0               |  |  |

|---------------|-----------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------|----------|-----------------|--|--|

| TF2           | EXF2            | RCLK                                                                      | TCLK                                                                                                                                                                                                                                          | EXEN2                                                                   | TR2            | C/T2#    | CP/RL2#         |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                               |                                                                                                                                                                                                                                               |                                                                         |                |          |                 |  |  |

| 7             | TF2             |                                                                           | red by softwar                                                                                                                                                                                                                                | e.<br>2 overflow, if RC                                                 | CLK = 0 and TC | CLK = 0. |                 |  |  |

| 6             | EXF2            | Set when a c<br>EXEN2 = 1.<br>When set, ca<br>is enabled.<br>Must be clea | When set, causes the CPU to vector to Timer 2 interrupt routine when Timer 2 interrupt                                                                                                                                                        |                                                                         |                |          |                 |  |  |

| 5             | RCLK            |                                                                           | se Timer 1 ove                                                                                                                                                                                                                                | erflow as receive<br>as receive cloc                                    |                |          |                 |  |  |

| 4             | TCLK            |                                                                           | se Timer 1 ove                                                                                                                                                                                                                                | erflow as transm<br>v as transmit clo                                   |                |          |                 |  |  |

| 3             | EXEN2           | Cleared to ig<br>Set to cause                                             | a capture or re                                                                                                                                                                                                                               | <b>bit</b><br>n T2EX pin for T<br>eload when a ne<br>k the serial port. |                |          | is detected, if |  |  |

| 2             | TR2             | Cleared to tu                                                             | Timer 2 Run control bit<br>Cleared to turn off Timer 2.<br>Set to turn on Timer 2.                                                                                                                                                            |                                                                         |                |          |                 |  |  |

| 1             | C/T2#           | Cleared for to<br>Set for count                                           | <b>Timer/Counter 2 select bit</b><br>Cleared for timer operation (input from internal clock system: F <sub>CLK PERIPH</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0 for<br>clock out mode. |                                                                         |                |          |                 |  |  |

| 0             | CP/RL2#         | If RCLK = 1 of<br>Timer 2 over<br>Cleared to A<br>EXEN2 = 1.              | <b>Timer 2 Capture/Reload bit</b><br>If RCLK = 1 or TCLK = 1, CP/RL2# is ignored and timer is forced to Auto-reload on<br>Timer 2 overflow.<br>Cleared to Auto-reload on Timer 2 overflows or negative transitions on T2EX pin if             |                                                                         |                |          |                 |  |  |

Reset Value = 0000 0000b Bit addressable

# 15. Serial I/O Port

The serial I/O port in the AT89C5130A/31A-M is compatible with the serial I/O port in the 80C52. It provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates.

Serial I/O port includes the following enhancements:

- Framing error detection

- · Automatic address recognition

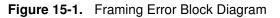

## 15.1 Framing Error Detection

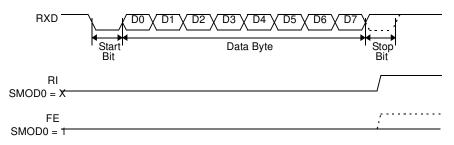

Framing bit error detection is provided for the three asynchronous modes (modes 1, 2 and 3). To enable the framing bit error detection feature, set SMOD0 bit in PCON register (see Figure 15-1).

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register (See Table 15-1) bit is set.

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset can clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 15-2 and Figure 15-3).

#### Figure 15-2. UART Timings in Mode 1

# Table 15-3.PCON RegisterPCON - Power Control Register (87h)

| 7             | 6               | 5                                                              | 4                                                                                                                   | 3                              | 2               | 1              | 0        |  |  |

|---------------|-----------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------|----------------|----------|--|--|

| SMOD1         | SMOD0           | -                                                              | - POF GF1 GF0 PD                                                                                                    |                                |                 |                |          |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                    |                                                                                                                     |                                |                 |                |          |  |  |

| 7             | SMOD1           | Serial port Mo<br>Set to select de                             |                                                                                                                     | <b>ART</b><br>e in mode 1, 2 c | or 3.           |                |          |  |  |

| 6             | SMOD0           | Serial port Mod<br>Cleared to sele<br>Set to select F          | ect SM0 bit in S                                                                                                    | SCON register.                 |                 |                |          |  |  |

| 5             | -               | Reserved<br>The value read                                     | I from this bit is                                                                                                  | s indeterminate.               | Do not set this | bit.           |          |  |  |

| 4             | POF             | Power-Off Fla<br>Cleared to reco<br>Set by hardwa<br>software. | ognize next res                                                                                                     | set type.<br>ses from 0 to its | nominal voltag  | e. Can also be | e set by |  |  |

| 3             | GF1             | General-purper<br>Cleared by use<br>Set by user for            | er for general-p                                                                                                    |                                |                 |                |          |  |  |

| 2             | GF0             | Cleared by use                                                 | <b>General-purpose Flag</b><br>Cleared by user for general-purpose usage.<br>Set by user for general-purpose usage. |                                |                 |                |          |  |  |

| 1             | PD              | Cleared by har                                                 | Power-down Mode Bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                      |                                |                 |                |          |  |  |

| 0             | IDL             | Idle Mode Bit<br>Cleared by har<br>Set to enter idl            |                                                                                                                     | terrupt or reset               | occurs.         |                |          |  |  |

Reset Value = 00X1 0000b Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

# Table 15-4. BDRCON Register

BDRCON - Baud Rate Control Register (9Bh)

| 7 | 6 | 5 | 4   | 3    | 2    | 1   | 0   |

|---|---|---|-----|------|------|-----|-----|

| - | - | - | BRR | ТВСК | RBCK | SPD | SRC |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                             |

| 6             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit                                                                                                                                                             |

| 5             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                                     |

| 4             | BRR             | Baud Rate Run Control bit<br>Cleared to stop the internal Baud Rate Generator.<br>Set to start the internal Baud Rate Generator.                                                                                                           |

| 3             | ТВСК            | Transmission Baud rate Generator Selection bit for UART<br>Cleared to select Timer 1 or Timer 2 for the Baud Rate Generator.<br>Set to select internal Baud Rate Generator.                                                                |

| 2             | RBCK            | Reception Baud Rate Generator Selection bit for UART<br>Cleared to select Timer 1 or Timer 2 for the Baud Rate Generator.<br>Set to select internal Baud Rate Generator.                                                                   |

| 1             | SPD             | Baud Rate Speed Control bit for UART<br>Cleared to select the SLOW Baud Rate Generator.<br>Set to select the FAST Baud Rate Generator.                                                                                                     |

| 0             | SRC             | <b>Baud Rate Source select bit in Mode 0 for UART</b><br>Cleared to select F <sub>OSC</sub> /12 as the Baud Rate Generator (F <sub>CLK PERIPH</sub> /6 in X2 mode).<br>Set to select the internal Baud Rate Generator for UARTs in mode 0. |

Reset Value = XXX0 0000b Not bit addressable

| Bit    | Bit      |                                                                                                                                             |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic | Description                                                                                                                                 |

| 7      | EA       | Enable All interrupt bit<br>Cleared to disable all interrupts.<br>Set to enable all interrupts.                                             |

| 6      | EC       | PCA interrupt enable bit<br>Cleared to disable.<br>Set to enable.                                                                           |

| 5      | ET2      | Timer 2 overflow interrupt Enable bit<br>Cleared to disable Timer 2 overflow interrupt.<br>Set to enable Timer 2 overflow interrupt.        |

| 4      | ES       | Serial port Enable bit<br>Cleared to disable serial port interrupt.<br>Set to enable serial port interrupt.                                 |

| 3      | ET1      | Timer 1 overflow interrupt Enable bit<br>Cleared to disable Timer 1 overflow interrupt.<br>Set to enable Timer 1 overflow interrupt.        |

| 2      | EX1      | External interrupt 1 Enable bit<br>Cleared to disable external interrupt 1.<br>Set to enable external interrupt 1.                          |

| 1      | ET0      | <b>Timer 0 overflow interrupt Enable bit</b><br>Cleared to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt. |

| 0      | EX0      | External interrupt 0 Enable bit<br>Cleared to disable external interrupt 0.<br>Set to enable external interrupt 0.                          |

Reset Value = 0000 0000b Bit addressable

# Table 16-3. IPL0 Register

IPL0 - Interrupt Priority Register (B8h)

| 7 | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|---|------|------|-----|------|------|------|------|

| - | PPCL | PT2L | PSL | PT1L | PX1L | PTOL | PX0L |

# IEN1 - Interrupt Enable Register (B1h)

| 7             | 6               | 5              | 4                                                                                             | 3            | 2    | 1    | 0   |  |  |

|---------------|-----------------|----------------|-----------------------------------------------------------------------------------------------|--------------|------|------|-----|--|--|

| -             | EUSB            | -              | -                                                                                             | -            | ESPI | ETWI | ЕКВ |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description    |                                                                                               |              |      |      |     |  |  |

| 7             | -               | Reserved       |                                                                                               |              |      |      |     |  |  |

| 6             | EUSB            | Cleared to dis | ISB Interrupt Enable bit<br>Cleared to disable USB interrupt.<br>Set to enable USB interrupt. |              |      |      |     |  |  |

| 5             | -               | Reserved       |                                                                                               |              |      |      |     |  |  |

| 4             | -               | Reserved       |                                                                                               |              |      |      |     |  |  |

| 3             | -               | Reserved       |                                                                                               |              |      |      |     |  |  |

| 2             | ESPI            | Cleared to dis | SPI interrupt Enable bit<br>Cleared to disable SPI interrupt.<br>Set to enable SPI interrupt. |              |      |      |     |  |  |

| 1             | ETWI            | Cleared to dis | TWI interrupt Enable bit<br>Cleared to disable TWI interrupt.<br>Set to enable TWI interrupt. |              |      |      |     |  |  |

| 0             | EKB             | Cleared to dis | terrupt Enable<br>sable keyboard<br>keyboard inte                                             | l interrupt. |      |      |     |  |  |

| SPR2 | SPR1 | SPR0 | Clock Rate | Baud Rate Divisor (BD) |

|------|------|------|------------|------------------------|

| 1    | 1    | 1    | Don't Use  | No BRG                 |

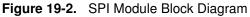

# **19.3 Functional Description**

Figure 19-2 shows a detailed structure of the SPI module.

#### 19.3.1 Operating Modes

The Serial Peripheral Interface can be configured as one of the two modes: Master mode or Slave mode. The configuration and initialization of the SPI module is made through one register:

• The Serial Peripheral CONtrol register (SPCON)

Once the SPI is configured, the data exchange is made using:

- SPCON

- The Serial Peripheral STAtus register (SPSTA)

- The Serial Peripheral DATa register (SPDAT)

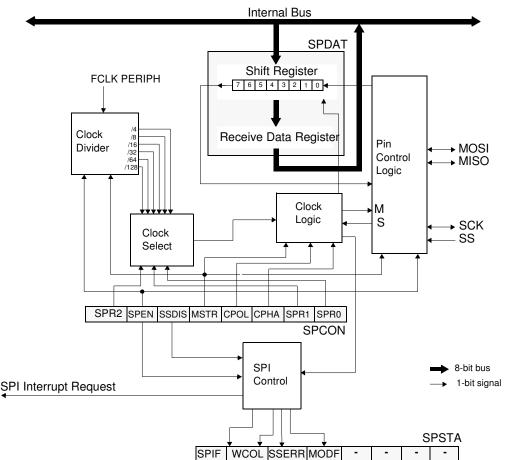

During an SPI transmission, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (SCK) synchronizes shifting and sampling on the two serial data lines (MOSI and MISO). A Slave Select line ( $\overline{SS}$ ) allows individual selection of a Slave SPI device; Slave devices that are not selected do not interfere with SPI bus activities.

When the Master device transmits data to the Slave device via the MOSI line, the Slave device responds by sending data to the Master device via the MISO line. This implies full-duplex transmission with both data out and data in synchronized with the same clock (Figure 19-3).

#### Figure 19-3. Full-duplex Master/Slave Interconnection

#### 19.3.1.1 Master Mode

The SPI operates in Master mode when the Master bit, MSTR <sup>(1)</sup>, in the SPCON register is set. Only one Master SPI device can initiate transmissions. Software begins the transmission from a Master SPI module by writing to the Serial Peripheral Data Register (SPDAT). If the shift register is empty, the byte is immediately transferred to the shift register. The byte begins shifting out on MOSI pin under the control of the serial clock, SCK. Simultaneously, another byte shifts in from the Slave on the Master's MISO pin. The transmission ends when the Serial Peripheral transfer data flag, SPIF, in SPSTA becomes set. At the same time that SPIF becomes set, the received byte from the Slave is transferred to the receive data register in SPDAT. Software clears SPIF by reading the Serial Peripheral Status register (SPSTA) with the SPIF bit set, and then reading the SPDAT.

#### 19.3.1.2 Slave Mode

The SPI operates in Slave mode when the Master bit, MSTR  $^{(2)}$ , in the SPCON register is cleared. Before a data transmission occurs, the Slave Select pin,  $\overline{SS}$ , of the Slave device must be set to'0'.  $\overline{SS}$  must remain low until the transmission is complete.

In a Slave SPI module, data enters the shift register under the control of the SCK from the Master SPI module. After a byte enters the shift register, it is immediately transferred to the receive data register in SPDAT, and the SPIF bit is set. To prevent an overflow condition, Slave software must then read the SPDAT before another byte enters the shift register <sup>(3)</sup>. A Slave SPI must complete the write to the SPDAT (shift register) at least one bus cycle before the Master SPI starts a transmission. If the write to the data register is late, the SPI transmits the data already in the shift register from the previous transmission.

#### 19.3.2 Transmission Formats

Software can select any of four combinations of serial clock (SCK) phase and polarity using two bits in the SPCON: the Clock POLarity (CPOL<sup>(4)</sup>) and the Clock PHAse (CPHA<sup>4</sup>). CPOL defines the default SCK line level in idle state. It has no significant effect on the transmission format. CPHA defines the edges on which the input data are sampled and the edges on which the

- The SPI module should be configured as a Master before it is enabled (SPEN set). Also the Master SPI should be configured before the Slave SPI.

- 2. The SPI module should be configured as a Slave before it is enabled (SPEN set).

- 3. The maximum frequency of the SCK for an SPI configured as a Slave is F<sub>CLK PERIPH</sub>/2.

- 4. Before writing to the CPOL and CPHA bits, the SPI should be disabled (SPEN ='0').

| Bit<br>Number | Bit Mnemonic | Description                                                                                                                                                                          |

|---------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2             | СРНА         | <b>Clock Phase</b><br>Cleared to have the data sampled when the SCK leaves the idle state (see CPOL).<br>Set to have the data sampled when the SCK returns to idle state (see CPOL). |

| 1             | SPR1         | SPR2 SPR1       SPR0 Serial Peripheral Rate         000Reserved         00 1F <sub>CLK PERIPH/</sub> 4         010 F <sub>CLK PERIPH/</sub> 8                                        |

| 0             | SPR0         | 011F <sub>CLK PERIPH</sub> /16<br>100F <sub>CLK PERIPH</sub> /32<br>10 1F <sub>CLK PERIPH</sub> /64<br>110F <sub>CLK PERIPH</sub> /128<br>1 11Reserved                               |

Reset Value = 0001 0100b

Not bit addressable

#### 19.3.5.2 Serial Peripheral Status Register (SPSTA)

The Serial Peripheral Status Register contains flags to signal the following conditions:

- Data transfer complete

- Write collision

- Inconsistent logic level on SS pin (mode fault error)

Table 19-4 describes the SPSTA register and explains the use of every bit in the register.

# Table 19-4. SPSTA Register

SPSTA - Serial Peripheral Status and Control register (0C4H)

| 7          | 6               | 5                                                                                                                                                                                                                              | 4                                                                                                                                                                                                         | 3 | 2 | 1 | 0 |  |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|--|

| SPIF       | WCOL            | SSERR                                                                                                                                                                                                                          | MODF                                                                                                                                                                                                      | - | - | - | - |  |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                    |                                                                                                                                                                                                           |   |   |   |   |  |

| 7          | SPIF            | Serial Peripheral data transfer flag<br>Cleared by hardware to indicate data transfer is in progress or has been approved by a<br>clearing sequence.<br>Set by hardware to indicate that the data transfer has been completed. |                                                                                                                                                                                                           |   |   |   |   |  |

| 6          | WCOL            | Cleared by har<br>clearing seque                                                                                                                                                                                               | Write Collision flag<br>Cleared by hardware to indicate that no collision has occurred or has been approved by a<br>clearing sequence.<br>Set by hardware to indicate that a collision has been detected. |   |   |   |   |  |

| 5          | SSERR           | Synchronous Serial Slave Error flag<br>Set by hardware when SS is de-<br>asserted before the end of a received data.<br>Cleared by disabling the SPI (clearing SPEN bit in SPCON).                                             |                                                                                                                                                                                                           |   |   |   |   |  |

# 21. USB Controller

# 21.1 Description

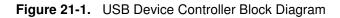

The USB device controller provides the hardware that the AT89C5131 needs to interface a USB link to a data flow stored in a double port memory (DPRAM).

The USB controller requires a 48 MHz ±0.25% reference clock, which is the output of the AT89C5131 PLL (see Section "PLL", page 15) divided by a clock prescaler. This clock is used to generate a 12 MHz Full-speed bit clock from the received USB differential data and to transmit data according to full speed USB device tolerance. Clock recovery is done by a Digital Phase Locked Loop (DPLL) block, which is compliant with the jitter specification of the USB bus.

The Serial Interface Engine (SIE) block performs NRZI encoding and decoding, bit stuffing, CRC generation and checking, and the serial-parallel data conversion.

The Universal Function Interface (UFI) realizes the interface between the data flow and the Dual Port RAM.

#### 21.1.1 Serial Interface Engine (SIE)

The SIE performs the following functions:

- NRZI data encoding and decoding.

- Bit stuffing and un-stuffing.

- CRC generation and checking.

- · Handshakes.

- TOKEN type identifying.

# 120 AT89C5130A/31A-M

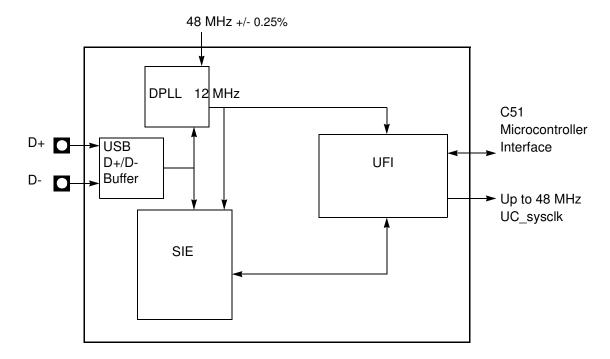

The stop of the 48 MHz clock from the PLL should be done in the following order:

- 1. Clear suspend interrupt bit in USBINT (required to allow the USB pads to enter power down mode).

- 2. Enable USB resume interrupt.

- 3. Disable of the 48 MHz clock input of the USB controller by setting to 1 the SUSPCLK bit in the USBCON register.

- 4. Disable the PLL by clearing the PLLEN bit in the PLLCON register.

- 5. Make the CPU core enter power down mode by setting PDOWN bit in PCON.

#### 21.8.2 Resume

When the USB controller is in Suspend state, the Resume detection is active even if all the clocks are disabled and if the C51 is in Idle or Power-down mode. The WUPCPU bit is set by hardware when a non-idle state occurs on the USB bus. This triggers an interrupt if enabled. This interrupt wakes up the CPU from its Idle or Power-down state and the interrupt function is then executed. The firmware will first enable the 48 MHz generation and then reset to 0 the SUSPCLK bit in the USBCON register if needed.

The firmware has to clear the SPINT bit in the USBINT register before any other USB operation in order to wake up the USB controller from its Suspend mode.

The USB controller is then re-activated.

#### 21.8.3 Upstream Resume

A USB device can be allowed by the Host to send an upstream resume for Remote Wake Up purpose.

# 134 AT89C5130A/31A-M

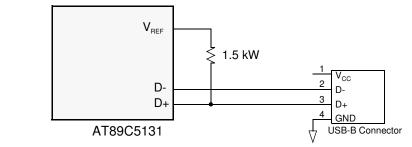

Figure 21-13. Example of  $V_{REF}$  Connection

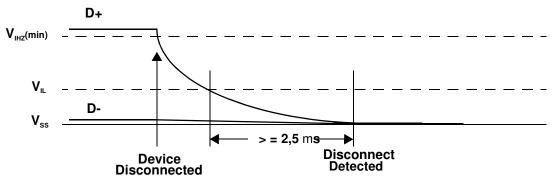

# 21.10 USB Interrupt System

#### 21.10.1 Interrupt System Priorities

Figure 21-15. USB Interrupt Control System

| Table 21-2. | Priority Levels |

|-------------|-----------------|

|-------------|-----------------|

| IPHUSB | IPLUSB | USB Priority Level |

|--------|--------|--------------------|

| 0      | 0      | 0 Lowest           |

| 0      | 1      | 1                  |

| 1      | 0      | 2                  |

| 1      | 1      | 3 Highest          |

# Table 21-15.UEPIEN RegisterUEPIEN (S:C2h)USB Endpoint Interrupt Enable Register

| 7          | 6               | 5                                                                                                                                                      | 4                  | 3                                            | 2                 | 1       | 0       |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------|-------------------|---------|---------|

| -          | EP6INTE         | EP5INTE                                                                                                                                                | EP4INTE            | EP3INTE                                      | EP2INTE           | EP1INTE | EPOINTE |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                            |                    |                                              |                   |         |         |

| 7          | -               | <b>Reserved</b><br>The value read                                                                                                                      | d from this bit is | s always 0. Do                               | not set this bit. |         |         |

| 6          | EP6INTE         | Set this bit to e                                                                                                                                      |                    | e<br>rrupts for this er<br>terrupts for this |                   |         |         |

| 5          | EP5INTE         | Set this bit to e                                                                                                                                      |                    | e<br>rrupts for this er<br>terrupts for this |                   |         |         |

| 4          | EP4INTE         | Set this bit to                                                                                                                                        |                    | e<br>rrupts for this er<br>terrupts for this |                   |         |         |

| 3          | EP3INTE         | Endpoint 3 Interrupt Enable<br>Set this bit to enable the interrupts for this endpoint.<br>Clear this bit to disable the interrupts for this endpoint. |                    |                                              |                   |         |         |

| 2          | EP2INTE         | Set this bit to e                                                                                                                                      |                    | e<br>rrupts for this er<br>terrupts for this |                   |         |         |

| 1          | EP1INTE         | Set this bit to e                                                                                                                                      |                    | e<br>rrupts for this er<br>terrupts for this |                   |         |         |

| 0          | EP0INTE         | Set this bit to                                                                                                                                        |                    | e<br>rrupts for this er<br>terrupts for this |                   |         |         |

Reset Value = 00h

| B |

|---|

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X Parameter | Units |

|-------------------|------|-------------------|-----------|-------------|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10          | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30          | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10          | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20          | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40          | ns    |

| T <sub>PXIX</sub> | Min  | х                 | x         | 0           | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7           | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40          | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | x         | 10          | ns    |

Table 27-4.

AC Parameters for a Variable Clock

# 27.4.3 External Program Memory Read Cycle

# 27.4.4 External Data Memory Characteristics

Table 27-5. Symbol Description

| Symbol            | Parameter                   |

|-------------------|-----------------------------|

| T <sub>RLRH</sub> | RD Pulse Width              |

| T <sub>WLWH</sub> | WR Pulse Width              |

| T <sub>RLDV</sub> | RD to Valid Data In         |

| T <sub>RHDX</sub> | Data Hold After RD          |

| T <sub>RHDZ</sub> | Data Float After RD         |

| T <sub>LLDV</sub> | ALE to Valid Data In        |

| T <sub>AVDV</sub> | Address to Valid Data In    |

| T <sub>LLWL</sub> | ALE to WR or RD             |

| T <sub>AVWL</sub> | Address to WR or RD         |

| T <sub>QVWX</sub> | Data Valid to WR Transition |

| T <sub>QVWH</sub> | Data set-up to WR High      |

| T <sub>WHQX</sub> | Data Hold After WR          |

| T <sub>RLAZ</sub> | RD Low to Address Float     |

| T <sub>WHLH</sub> | RD or WR High to ALE high   |

# Table 27-6. AC Parameters for a Variable Clock (F = 40 MHz)

| Symbol            | Min | Max | Units |

|-------------------|-----|-----|-------|

| T <sub>RLRH</sub> | 130 |     | ns    |

| T <sub>WLWH</sub> | 130 |     | ns    |

| T <sub>RLDV</sub> |     | 100 | ns    |

| T <sub>RHDX</sub> | 0   |     | ns    |

| T <sub>RHDZ</sub> |     | 30  | ns    |

| T <sub>LLDV</sub> |     | 160 | ns    |

| T <sub>AVDV</sub> |     | 165 | ns    |

| T <sub>LLWL</sub> | 50  | 100 | ns    |

| T <sub>AVWL</sub> | 75  |     | ns    |

| T <sub>QVWX</sub> | 10  |     | ns    |

| T <sub>QVWH</sub> | 160 |     | ns    |

| T <sub>WHQX</sub> | 15  |     | ns    |

| T <sub>RLAZ</sub> |     | 0   | ns    |

| T <sub>WHLH</sub> | 10  | 40  | ns    |

| 19 | Serial F | Peripheral Interface (SPI)93      |

|----|----------|-----------------------------------|

|    | 19.1     | Features                          |

|    | 19.2     | Signal Description                |

|    | 19.3     | Functional Description95          |

| 20 | Two W    | ire Interface (TWI)102            |

|    | 20.1     | Description104                    |

|    | 20.2     | Notes107                          |

|    | 20.3     | Registers118                      |

| 21 | USB Co   | ontroller                         |

|    | 21.1     | Description120                    |

|    | 21.2     | Configuration122                  |

|    | 21.3     | Read/Write Data FIFO124           |

|    | 21.4     | Bulk/Interrupt Transactions125    |

|    | 21.5     | Control Transactions              |

|    | 21.6     | Isochronous Transactions          |

|    | 21.7     | Miscellaneous                     |

|    | 21.8     | Suspend/Resume Management133      |

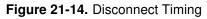

|    | 21.9     | Detach Simulation135              |

|    | 21.10    | USB Interrupt System136           |

|    | 21.11    | USB Registers                     |

| 22 | Reset .  |                                   |

|    | 22.1     | Introduction151                   |

|    | 22.2     | Reset Input151                    |

|    | 22.3     | Reset Output151                   |

| 23 | Power    | Monitor                           |

|    | 23.1     | Description153                    |

| 24 | Power    | Management                        |

|    | 24.1     | Idle Mode155                      |

|    | 24.2     | Power-down Mode155                |

|    | 24.3     | Registers157                      |

| 25 | Hardwa   | are Watchdog Timer 158            |

|    | 25.1     | Using the WDT158                  |

|    | 25.2     | WDT During Power-down and Idle159 |

| 26 | Reduce   | ed EMI Mode 160                   |

# III AT89C5130A/31A-M

| 27 | Electric | cal Characteristics            |

|----|----------|--------------------------------|

|    | 27.1     | Absolute Maximum Ratings161    |

|    | 27.2     | DC Parameters161               |

|    | 27.3     | USB DC Parameters163           |

|    | 27.4     | AC Parameters                  |

|    | 27.5     | USB AC Parameters173           |

|    | 27.6     | SPI Interface AC Parameters    |

| 28 | Orderin  | ng Information 177             |

| 29 | Packag   | ing Information178             |

|    | 29.1     | 64-lead VQFP178                |

|    | 29.2     | 52-lead PLCC180                |

|    | 29.3     | 32-lead QFN181                 |

| 30 | Datash   | eet Revision History 183       |

|    | 30.1     | Changes from 4337F to 4337G183 |

|    | 30.2     | Changes from 4337G to 4337H183 |

|    | 30.3     | Changes from 4337H to 4337I183 |

|    | 30.4     | Changes from 4337I to 4337J183 |

|    | 30.5     | Changes from 4337J to 4337K183 |