#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                             |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CSIO, I <sup>2</sup> C, LINbus, SmartCard, UART/USART                        |

| Peripherals                | I <sup>2</sup> S, LVD, POR, PWM, WDT                                         |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                 |

| Data Converters            | A/D 6x12b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 32-LQFP                                                                      |

| Supplier Device Package    | 32-LQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e1c12b0agp20000 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3. Pin Assignment

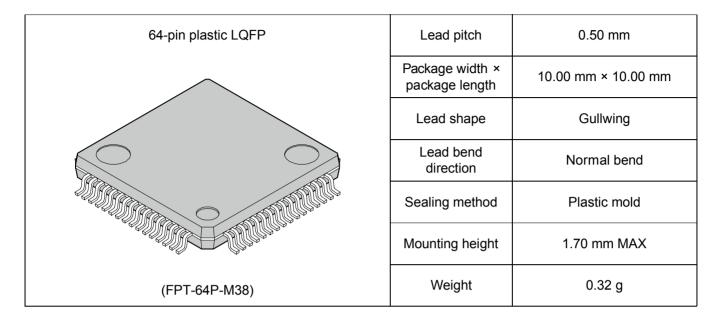

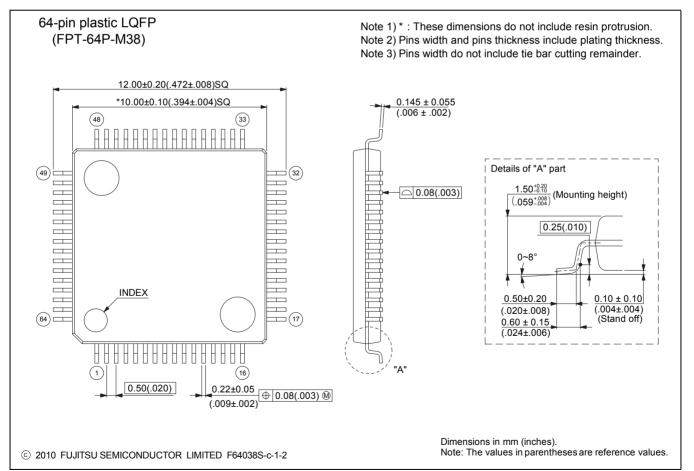

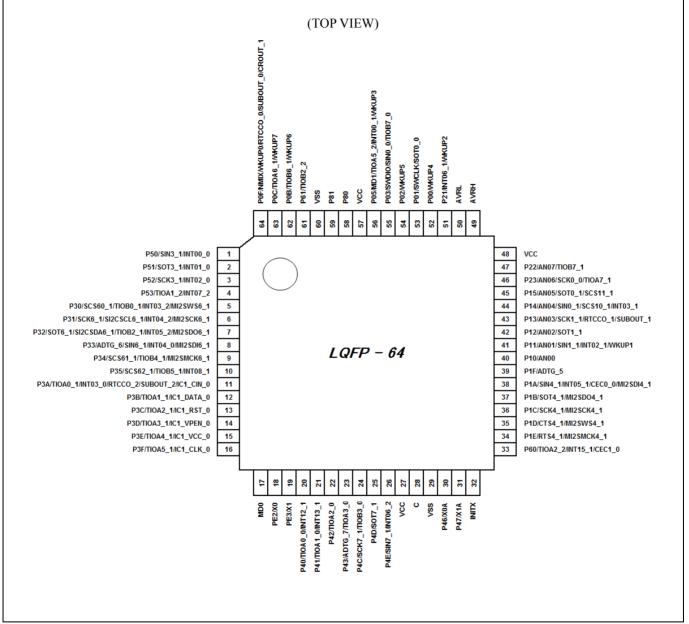

### FPT-64P-M38

Note:

The number after the underscore ("\_") in a pin name such as XXX\_1 and XXX\_2 indicates the relocated port number. The channel on such pin has multiple functions, each of which has its own pin name. Use the Extended Port Function Register (EPFR) to select the pin to be used.

# S6E1C1 Series

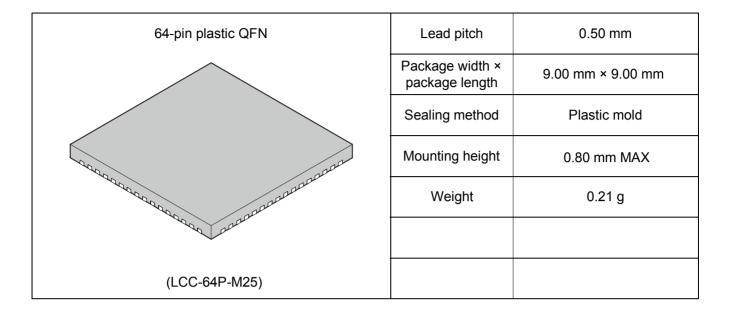

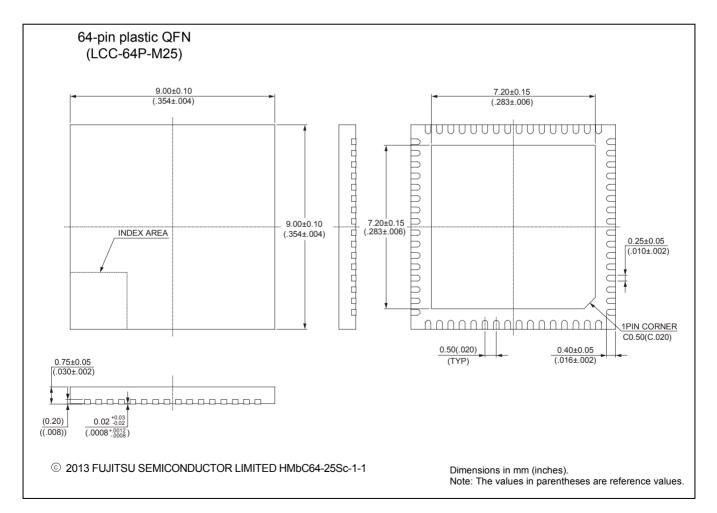

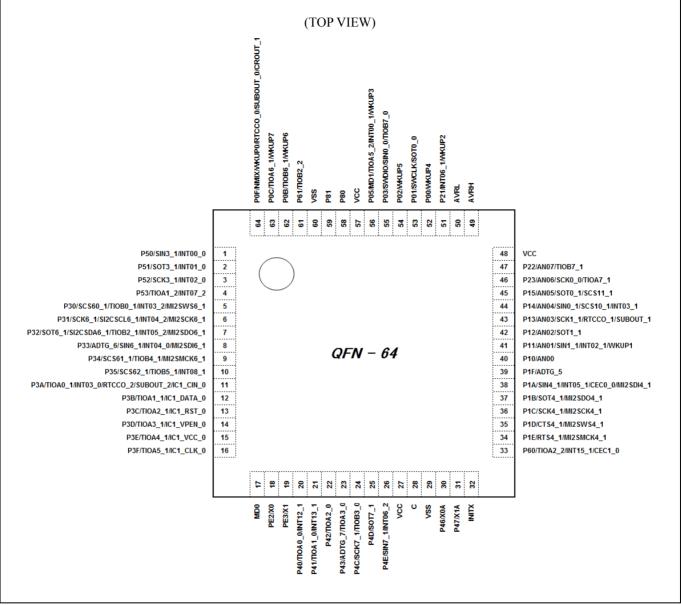

#### LCC-64P-M25

#### Note:

The number after the underscore ("\_") in a pin name such as XXX\_1 and XXX\_2 indicates the relocated port number. The channel on such pin has multiple functions, each of which has its own pin name. Use the Extended Port Function Register (EPFR) to select the pin to be used.

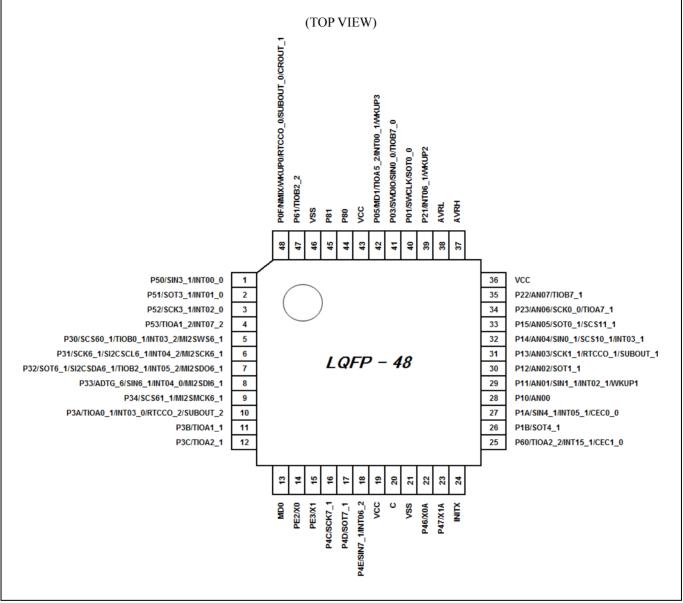

#### **FPT-48P-M49**

#### Note:

The number after the underscore ("\_") in a pin name such as XXX\_1 and XXX\_2 indicates the relocated port number. The

channel on such pin has multiple functions, each of which has its own pin name. Use the Extended Port Function Register

(EPFR) to select the pin to be used.

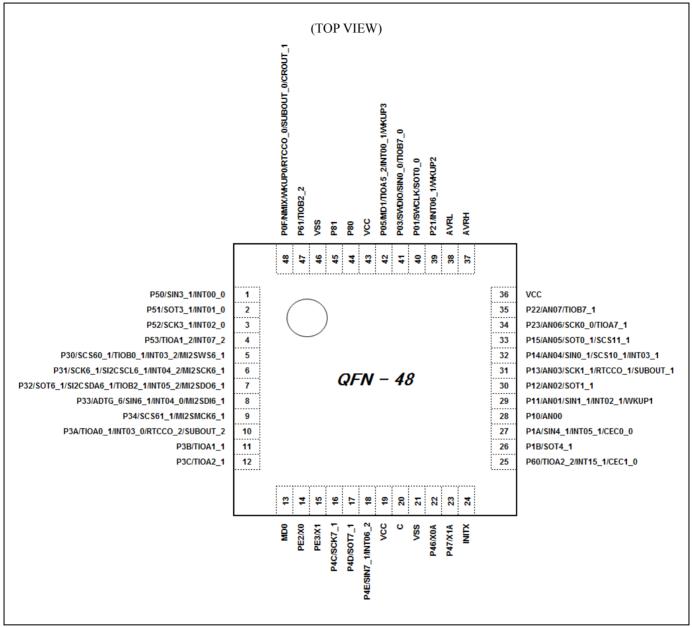

LCC-48P-M74

### Note:

The number after the underscore ("\_") in a pin name such as XXX\_1 and XXX\_2 indicates the relocated port number. The channel on such pin has multiple functions, each of which has its own pin name. Use the Extended Port Function Register (EPFR) to select the pin to be used.

|         | Pin no. |         |              | I/O circuit | Pin state |  |

|---------|---------|---------|--------------|-------------|-----------|--|

| LQFP-64 | LQFP-48 | LQFP-32 | Pin Function | type        | type      |  |

| QFN-64  | QFN-48  | QFN-32  |              |             |           |  |

|         |         | -       | P33          | _           |           |  |

|         |         | -       | ADTG_6       |             |           |  |

| 8       | 8       |         | SIN6_1       | Н           | К         |  |

|         |         | -       | INT04_0      | _           |           |  |

|         |         |         | MI2SDI6_1    |             |           |  |

|         |         | -       | P33          | _           |           |  |

| -       | -       | 7 -     | ADTG_6       | — н         | к         |  |

|         |         | -       | SIN6_1       |             |           |  |

|         |         |         | INT04_0      |             |           |  |

|         |         | -       | P34          |             |           |  |

| 9       | -       |         | SCS61_1      | D           | к         |  |

|         |         |         | TIOB4_1      | 4           |           |  |

|         |         |         | MI2SMCK6_1   |             |           |  |

|         |         | F       | P34          |             |           |  |

| -       | 9       |         | SCS61_1      | D           | K         |  |

|         |         |         | MI2SMCK6_1   |             |           |  |

|         |         | _       | P35          | _           |           |  |

| 10      | -       |         | SCS62_1      | D           | к         |  |

|         |         |         | TIOB5_1      | _           |           |  |

|         |         |         | INT08_1      |             |           |  |

|         |         | _       | P3A          |             | к         |  |

|         |         | _       | TIOA0_1      | D           |           |  |

| 11      | -       |         | INT03_0      |             |           |  |

|         |         |         | RTCCO_2      |             |           |  |

|         |         |         | SUBOUT_2     | _           |           |  |

|         |         |         | IC1_CIN_0    |             |           |  |

|         |         |         | P3A          | _           |           |  |

|         |         |         | TIOA0_1      |             |           |  |

| -       | 10      |         | INT03_0      | D           | К         |  |

|         |         |         | RTCCO_2      |             |           |  |

|         |         |         | SUBOUT_2     |             |           |  |

|         |         |         | P3B          |             |           |  |

| 12      | -       | -       | TIOA1_1      | D           | К         |  |

|         |         |         | IC1_DATA_0   |             |           |  |

| _       | 11      |         | P3B          | D           | к         |  |

| -       |         | -       | TIOA1_1      |             |           |  |

|         |         |         | P3C          |             |           |  |

| 13      | -       | - [     | TIOA2_1      | D           | К         |  |

|         |         |         | IC1_RST_0    |             |           |  |

|         | 12      |         | P3C          |             | K         |  |

| -       | 12      |         | TIOA2_1      | D           | К         |  |

|         |         |         | P3D          |             |           |  |

| 14      | -       |         | TIOA3_1      | D           | К         |  |

|         |         |         | IC1_VPEN_0   | 7           |           |  |

|                            |                    |                                                                                                                                                                                              |         | Pin no. |         |

|----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|

| Pin function               | Pin name           | Function description                                                                                                                                                                         | LQFP-64 | LQFP-48 | LQFP-32 |

|                            |                    |                                                                                                                                                                                              | QFN-64  | QFN-48  | QFN-32  |

|                            | P30                |                                                                                                                                                                                              | 5       | 5       | -       |

|                            | P31                |                                                                                                                                                                                              | 6       | 6       | 5       |

|                            | P32                |                                                                                                                                                                                              | 7       | 7       | 6       |

|                            | P33                |                                                                                                                                                                                              | 8       | 8       | 7       |

|                            | P34                |                                                                                                                                                                                              | 9       | 9       | -       |

| GPIO                       | P35                | General-purpose I/O port 3                                                                                                                                                                   | 10      | -       | -       |

| GFIO                       | P3A                | General-purpose 1/O port 3                                                                                                                                                                   | 11      | 10      | -       |

|                            | P3B                |                                                                                                                                                                                              | 12      | 11      | -       |

|                            | P3C                |                                                                                                                                                                                              | 13      | 12      | -       |

|                            | P3D                |                                                                                                                                                                                              | 14      | -       | -       |

|                            | P3E                |                                                                                                                                                                                              | 15      | -       | -       |

|                            | P3F                |                                                                                                                                                                                              | 16      | -       | -       |

|                            | P40                |                                                                                                                                                                                              | 20      | -       | -       |

|                            | P41                |                                                                                                                                                                                              | 21      | -       | -       |

|                            | P42                | ]                                                                                                                                                                                            | 22      | -       | -       |

|                            | P43                |                                                                                                                                                                                              | 23      | -       | -       |

| GPIO                       | P46                | General-purpose I/O port 4                                                                                                                                                                   | 30      | 22      | 14      |

|                            | P47                |                                                                                                                                                                                              | 31      | 23      | 15      |

|                            | P4C                |                                                                                                                                                                                              | 24      | 16      | -       |

|                            | P4D                |                                                                                                                                                                                              | 25      | 17      | -       |

|                            | P4E                |                                                                                                                                                                                              | 26      | 18      | -       |

|                            | P50                |                                                                                                                                                                                              | 1       | 1       | 2       |

|                            | P51                |                                                                                                                                                                                              | 2       | 2       | 3       |

| GPIO                       | P52                | General-purpose I/O port 5                                                                                                                                                                   | 3       | 3       | 4       |

|                            | P53                |                                                                                                                                                                                              | 4       | 4       | -       |

|                            | P60                |                                                                                                                                                                                              | 33      | 25      | 17      |

| GPIO                       | P61                | General-purpose I/O port 6                                                                                                                                                                   | 61      | 47      | -       |

|                            | P80                |                                                                                                                                                                                              | 58      | 44      | 30      |

| GPIO                       | P81                | General-purpose I/O port 8                                                                                                                                                                   | 59      | 45      | 31      |

|                            | PE2                |                                                                                                                                                                                              | 18      | 14      | 9       |

| GPIO                       | PE3                | General-purpose I/O port E                                                                                                                                                                   | 19      | 15      | 10      |

|                            | SIN0_0             | Multi-function serial interface ch.0 input                                                                                                                                                   | 55      | 41      | 28      |

|                            | SIN0_1             | pin                                                                                                                                                                                          | 44      | 32      | -       |

|                            | SOT0_0             | Multi-function serial interface ch.0 output                                                                                                                                                  | 50      | 40      | 07      |

|                            | (SDA0_0)           | pin. This pin operates as SOT0 when                                                                                                                                                          | 53      | 40      | 27      |

| M. 14: f                   | SOT0_1             | used as a UART/CSIO/LIN pin<br>(operation mode 0 to 3) and as SDA0                                                                                                                           | 45      | 00      |         |

| Multi-function<br>Serial 0 | (SDA0_1)           | when used as an I2C pin (operation mode 4).                                                                                                                                                  | 45      | 33      | -       |

|                            | SCK0_0<br>(SCL0_0) | Multi-function serial interface ch.0 clock<br>I/O pin. This pin operates as SCK0<br>when used as a CSIO pin (operation<br>mode 2) and as SCL0 when used as an<br>I2C pin (operation mode 4). | 46      | 34      | 22      |

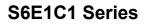

### Туре

This indicates a pin status type that is shown in "pin list table" in "4. List of Pin Functions"

### **Selected Pin function**

This indicates a pin function that is selected by user program.

### **CPU state**

This indicates a state of the CPU that is shown below.

- Reset state.

CPU is initialized by Power-on reset or a reset due to low Power voltage supply.

- (2) Reset state.

CPU is initialized by INITX input signal or system initialization after power on reset.

- (3) Run mode or SLEEP mode state.

- (4) Timer mode, RTC mode or STOP mode state.

- The standby pin level setting bit (SPL) in the Standby Mode Control Register (STB\_CTL) is set to "0". Timer mode, RTC mode or STOP mode state.

- (5) The standby pin level setting bit (SPL) in the Standby Mode Control Register (STB\_CTL) is set to "1".

- (6) Deep standby STOP mode or Deep standby RTC mode state,

- The standby pin level setting bit (SPL) in the Standby Mode Control Register (STB\_CTL) is set to "0" Deep standby STOP mode or Deep standby RTC mode state,

- (7) The standby pin level setting bit (SPL) in the Standby Mode Control Register (STB\_CTL) is set to "1" Run mode state after returning from Deep Standby mode.

- (8) (I/O state hold function(CONTX) is fixed at 1)

### Each pin status

The meaning of the symbols in the pin status table is as follows.

- IS Digital output is disabled. (Hi-Z) Pull up register is off. Digital input is shut off by fixed 0.

- IE Digital output is disabled. (Hi-Z) Pull up register is off. Digital input is not shut off.

- IP Digital output is disabled. (Hi-Z) Pull up register is defined by the value of the PCR register. Digital input is not shut off.

- IE/IS Digital output is disabled. (Hi-Z) Pull up register is off. Digital input is shut off in case of the OSC stop. Digital input is not shut off in case of the OSC operation.

- OE The OSC is in operation state. However, it may be stopped in some operation mode of the CPU.

- For detail, see chapter "Low Power Consumption Mode" in peripheral manual.

- OS The OSC is in stop state. (Hi-Z)

- PC Digital output and pull up register is controlled by the register in the GPIO or peripheral function. Digital input is not shut off

- CP Digital output is controlled by the register in the GPIO or peripheral function. Pull up register is off. Digital input is not shut off.

- HC Digital output and pull up register is maintained the status that is immediately prior to entering the current CPU state. Digital input is not shut off

- HS Digital output and pull up register is maintained the status that is immediately prior to entering the current CPU state. Digital input is shut off

- GS Digital output and pull up register is copied the GPIO status that is immediately prior to entering the current CPU state and the status is maintained. Digital input is shut off

### **11.2 Recommended Operating Conditions**

(V<sub>SS</sub>= 0.0 V)

| Parameter                | Symbol          | Conditions | Va                  | lue             | Unit | Remarks                 |

|--------------------------|-----------------|------------|---------------------|-----------------|------|-------------------------|

| Falailletei              | Symbol          | Conditions | Min                 | Max             | Unit | Reinarks                |

| Power supply voltage     | V <sub>CC</sub> | -          | 1.65 * <sup>2</sup> | 3.6             | V    |                         |

|                          | AVRH            | -          | 2.7                 | V <sub>CC</sub> | V    | V <sub>CC</sub> ≥ 2.7 V |

| Analog reference voltage |                 |            | V <sub>CC</sub>     | V <sub>CC</sub> | V    | V <sub>CC</sub> < 2.7 V |

|                          | AVRL            | -          | VSS                 | VSS             | V    |                         |

| Smoothing capacitor      | Cs              | -          | 1                   | 10              | μF   | For regulator*1         |

| Operating temperature    | Та              | -          | - 40                | + 105           | °C   |                         |

\*1: See "C Pin" in "7. Handling Devices" for the connection of the smoothing capacitor.

\*2: In between less than the minimum power supply voltage reset / interrupt detection voltage or more, instruction execution and low voltage detection function by built-in High-speed CR (including Main PLL is used) or built-in Low-speed CR is possible to operate only.

#### <WARNING>

- 1. The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

- 2. Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

- 3. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet.

- 4. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

### 11.4.6 Reset Input Characteristics

(V<sub>CC</sub> = 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter        | Symbol             | Pin   | Conditions | Va  | lue | Unit | Remarks |  |

|------------------|--------------------|-------|------------|-----|-----|------|---------|--|

| Farameter        | Cymbol             | Name  | Conditions | Min | Max | onic | Remarks |  |

| Reset input time | t <sub>INITX</sub> | INITX | -          | 500 | -   | ns   |         |  |

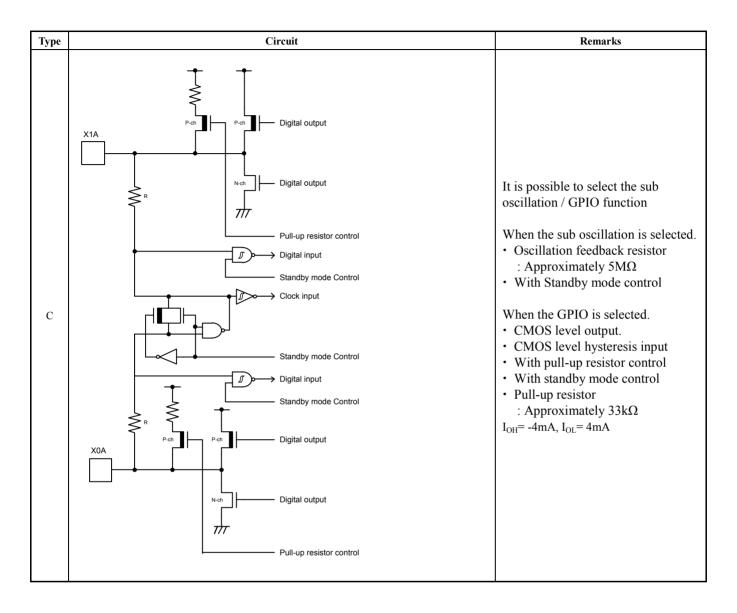

#### 11.4.7 Power-on Reset Timing

(V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter                              | Symbol            | Pin  | Valu | ue  | Unit | Remarks |

|----------------------------------------|-------------------|------|------|-----|------|---------|

| Farameter                              | Symbol            | Name | Min  | Max | Unit | Remarks |

| Power supply rising time               | t <sub>VCCR</sub> |      | 0    | -   | ms   |         |

| Power supply shut down time            | t <sub>OFF</sub>  | VCC  | 1    | -   | ms   |         |

| Time until releasing<br>Power-on reset | t <sub>PRT</sub>  |      | 0.43 | 3.4 | ms   |         |

### Glossary

$\square$  VCC\_minimum : Minimum V<sub>CC</sub> of recommended operating conditions.

UDH\_minimum : Minimum detection voltage of Low-Voltage detection reset.

See "11.6 Low-Voltage Detection Characteristics".

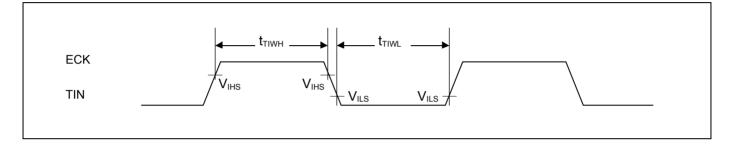

### 11.4.8 Base Timer Input Timing

### **Timer Input Timing**

(V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter         | Symbol                                | Pin Name                                   | Conditions | Va                  | ue  | Unit | Remarks |

|-------------------|---------------------------------------|--------------------------------------------|------------|---------------------|-----|------|---------|

| Falameter         | eter Symbol Pin Na                    |                                            |            |                     | Max | Unit | Remains |

| Input pulse width | t <sub>tiwh</sub> , t <sub>tiwl</sub> | TIOAn/TIOBn<br>(when using as<br>ECK, TIN) | -          | 2 t <sub>CYCP</sub> | -   | ns   |         |

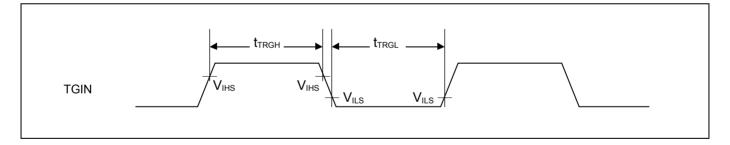

### **Trigger Input Timing**

(V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter         | Symbol                                | Pin Name                               | Conditions | Va                  | ue  | Unit | Remarks   |

|-------------------|---------------------------------------|----------------------------------------|------------|---------------------|-----|------|-----------|

| Farameter         | Symbol                                | Fill Name                              | Conditions | Min                 | Max | Unit | Rellidiks |

| Input pulse width | t <sub>тrgн</sub> , t <sub>trgl</sub> | TIOAn/TIOBn<br>(when using as<br>TGIN) | -          | 2 t <sub>CYCP</sub> | -   | ns   |           |

### Note:

t<sub>CYCP</sub> indicates the APB bus clock cycle time. For the number of the APB bus to which the Base Timer has been connected, see "8. Block Diagram".

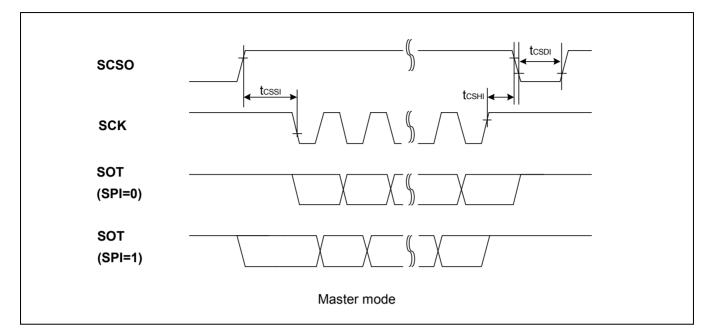

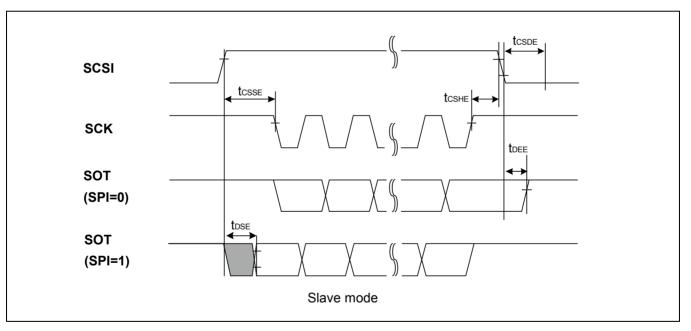

### 11.4.9 CSIO/SPI/UART Timing

### CSIO (SPI=0, SCINV=0)

|                                             |                    |               |             | (V <sub>CC</sub> = 1.6      | 65 V to 3.6 | V, V <sub>SS</sub> = 0 V    | T <sub>A</sub> =- 40°0 | C to +10 |

|---------------------------------------------|--------------------|---------------|-------------|-----------------------------|-------------|-----------------------------|------------------------|----------|

| Parameter                                   | Symbol             | Pin           | Conditions  | V <sub>cc</sub> < 2         |             | V <sub>cc</sub> ≥           |                        | Unit     |

| i urumotor                                  | Cymbol             | name          | Conditione  | Min                         | Max         | Min                         | Max                    | 01110    |

| Serial clock cycle time                     | t <sub>SCYC</sub>  | SCKx          |             | 4 t <sub>CYCP</sub>         | -           | 4 t <sub>CYCP</sub>         | -                      | ns       |

| $SCK \downarrow \to SOT \text{ delay time}$ | t <sub>sLOVI</sub> | SCKx,<br>SOTx |             | - 30                        | + 30        | - 20                        | + 20                   | ns       |

| $SIN \to SCK \uparrow setup \ time$         | t <sub>ivsni</sub> | SCKx,<br>SINx | Master mode | 50                          | -           | 36                          | -                      | ns       |

| $SCK \uparrow \to SIN \text{ hold time}$    | t <sub>shixi</sub> | SCKx,<br>SINx |             | 0                           | -           | 0                           | -                      | ns       |

| Serial clock "L" pulse width                | t <sub>sLSH</sub>  | SCKx          |             | 2 t <sub>CYCP</sub> -<br>10 | -           | 2 t <sub>CYCP</sub> -<br>10 | -                      | ns       |

| Serial clock "H" pulse width                | t <sub>SHSL</sub>  | SCKx          |             | t <sub>CYCP</sub> + 10      | -           | t <sub>CYCP</sub> +<br>10   | -                      | ns       |

| $SCK \downarrow \to SOT \text{ delay time}$ | t <sub>SLOVE</sub> | SCKx,<br>SOTx | Slave mode  | -                           | 50          | -                           | 30                     | ns       |

| $SIN \to SCK \uparrow setup  time$          | t <sub>IVSHE</sub> | SCKx,<br>SINx | Slave mode  | 10                          | -           | 10                          | -                      | ns       |

| $SCK \uparrow \to SIN \text{ hold time}$    | t <sub>SHIXE</sub> | SCKx,<br>SINx |             | 20                          | -           | 20                          | -                      | ns       |

| SCK falling time                            | tF                 | SCKx          |             | -                           | 5           | -                           | 5                      | ns       |

| SCK rising time                             | tR                 | SCKx          | 1           | -                           | 5           | -                           | 5                      | ns       |

## Notes:

The above AC characteristics are for clock synchronous mode. -

$t_{CYCP}$  represents the APB bus clock cycle time. For the number of the APB bus to which Multi-function Serial has been connected, see "8. Block Diagram".

- The characteristics are only applicable when the relocate port numbers are the same. \_ For instance, they are not applicable for the combination of SCKx\_0 and SOTx\_1.

- External load capacitance C<sub>L</sub>=30 pF

### SPI (SPI=1, SCINV=1)

| Parameter                                                      | Symbol             | Pin           | Conditions  | V <sub>cc</sub> < 2         | 2.7 V | V <sub>cc</sub> ≥2          | 2.7 V | Unit |

|----------------------------------------------------------------|--------------------|---------------|-------------|-----------------------------|-------|-----------------------------|-------|------|

| Farameter                                                      | Symbol             | name          | Conditions  | Min                         | Max   | Min                         | Max   | Unit |

| Serial clock cycle time                                        | t <sub>scyc</sub>  | SCKx          |             | 4 t <sub>CYCP</sub>         | -     | 4 t <sub>CYCP</sub>         | -     | ns   |

| $SCK \downarrow \to SOT \text{ delay time}$                    | t <sub>SLOVI</sub> | SCKx,<br>SOTx |             | - 30                        | + 30  | - 20                        | + 20  | ns   |

| $SIN \to SCK \uparrow setup \ time$                            | tıvsнı             | SCKx,<br>SINx | Master mode | 50                          | -     | 36                          | -     | ns   |

| $SCK \uparrow \to SIN$ hold time                               | t <sub>SHIXI</sub> | SCKx,<br>SINx |             | 0                           | -     | 0                           | -     | ns   |

| $\text{SOT} \rightarrow \text{SCK} \uparrow \text{delay time}$ | t <sub>sovнi</sub> | SCKx,<br>SOTx |             | 2 t <sub>CYCP</sub> -<br>30 | -     | 2 t <sub>CYCP</sub> -<br>30 | I     | ns   |

| Serial clock "L" pulse width                                   | t <sub>sLSH</sub>  | SCKx          |             | 2 t <sub>CYCP</sub> -<br>10 | -     | 2 t <sub>CYCP</sub> -<br>10 | -     | ns   |

| Serial clock "H" pulse width                                   | t <sub>SHSL</sub>  | SCKx          |             | t <sub>CYCP</sub> + 10      | -     | t <sub>CYCP</sub> + 10      | -     | ns   |

| $SCK \downarrow \rightarrow SOT$ delay time                    | t <sub>SLOVE</sub> | SCKx,<br>SOTx |             | -                           | 50    | -                           | 33    | ns   |

| $\text{SIN} \rightarrow \text{SCK} \uparrow \text{setup time}$ | t <sub>IVSHE</sub> | SCKx,<br>SINx | Slave mode  | 10                          | -     | 10                          | -     | ns   |

| $SCK \uparrow \to SIN$ hold time                               | t <sub>SHIXE</sub> | SCKx,<br>SINx |             | 20                          | -     | 20                          | -     | ns   |

| SCK falling time                                               | tF                 | SCKx          |             | -                           | 5     | -                           | 5     | ns   |

| SCK rising time                                                | tR                 | SCKx          |             | -                           | 5     | -                           | 5     | ns   |

#### $(V_{CC} = 1.65 \text{ V to } 3.6 \text{ V}, V_{SS} = 0 \text{ V}, T_{A} = -40^{\circ}\text{C to } +105^{\circ}\text{C})$

#### Notes:

- The above AC characteristics are for clock synchronous mode.

t<sub>CYCP</sub> represents the APB bus clock cycle time.

For the number of the APB bus to which Multi-function Serial has been connected, see "8. Block Diagram".

- The characteristics are only applicable when the relocate port numbers are the same. For instance, they are not applicable for the combination of SCKx\_0 and SOTx\_1.

- External load capacitance C<sub>L</sub>=30 pF

### When Using CSIO/SPI Chip Select (SCINV=1, CSLVL=0)

(V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter                                             | Symbol            | Conditions  | V <sub>cc</sub> < 2    | 2.7 V   | V <sub>cc</sub> ≥2     | Unit    |      |

|-------------------------------------------------------|-------------------|-------------|------------------------|---------|------------------------|---------|------|

| Falameter                                             | Symbol            | Conditions  | Min                    | Max     | Min                    | Мах     | Unit |

| SCS↑→SCK↑ setup time                                  | t <sub>cssi</sub> |             | (*1)-50                | (*1)+0  | (*1)-50                | (*1)+0  | ns   |

| $SCK \downarrow \rightarrow SCS \downarrow$ hold time | t <sub>CSHI</sub> | Master mode | (*2)+0                 | (*2)+50 | (*2)+0                 | (*2)+50 | ns   |

| SCS deselect time                                     | t <sub>CSDI</sub> |             | (*3)-50                | (*3)+50 | (*3)-50                | (*3)+50 | ns   |

| SCS↑→SCK↑ setup time                                  | t <sub>CSSE</sub> |             | 3t <sub>CYCP</sub> +30 | -       | 3t <sub>CYCP</sub> +30 | -       | ns   |

| $SCK\downarrow \rightarrow SCS\downarrow$ hold time   | t <sub>CSHE</sub> |             | 0                      | -       | 0                      | -       | ns   |

| SCS deselect time                                     | t <sub>CSDE</sub> | Slave mode  | 3t <sub>CYCP</sub> +30 | -       | $3t_{CYCP}+30$         | -       | ns   |

| SCS↑→SOT delay time                                   | t <sub>DSE</sub>  |             | -                      | 55      | -                      | 40      | ns   |

| $SCS\downarrow \rightarrow SOT$ delay time            | t <sub>DEE</sub>  |             | 0                      | -       | 0                      | -       | ns   |

\*1: CSSU bit value × serial chip select timing operating clock cycle.

\*2: CSHD bit value × serial chip select timing operating clock cycle.

#### Notes:

- t<sub>CYCP</sub> indicates the APB bus clock cycle time.

For information about the APB bus number which Multi-function Serial is connected to, see "8. Block Diagram".

- For information about CSSU, CSHD, CSDS, serial chip select timing operating clock, see "FM0+ Family Peripheral Manual".

- These characteristics only guarantee the same relocate port number.

For example, the combination of SCKx\_0 and SCSIx\_1 is not guaranteed.

- When the external load capacitance  $C_L$ =30 pF.

<sup>\*3:</sup> CSDS bit value × serial chip select timing operating clock cycle. Irrespective of CSDS bit setting, 5t<sub>CYCP</sub> or more are required for the period the time when the serial chip select pin becomes inactive to the time when the serial chip select pin becomes active again.

## 11.6.2 Low-Voltage Detection Interrupt

(T<sub>A</sub>=-40°C to +105°C)

| Parameter                   | Symbo              | Conditions |      | Value |                                  | Uni | Remarks            |

|-----------------------------|--------------------|------------|------|-------|----------------------------------|-----|--------------------|

| Falameter                   | Ī                  |            | Min  | Тур   | Max                              | t   | Kelliarks          |

| Detected voltage            | VDL                | SVHI=00100 | 1.56 | 1.70  | 1.84                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.61 | 1.75  | 1.89                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=00101 | 1.61 | 1.75  | 1.89                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.66 | 1.80  | 1.94                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=00110 | 1.66 | 1.80  | 1.94                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.70 | 1.85  | 2.00                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=00111 | 1.70 | 1.85  | 2.00                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.75 | 1.90  | 2.05                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01000 | 1.75 | 1.90  | 2.05                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.79 | 1.95  | 2.11                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01001 | 1.79 | 1.95  | 2.11                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.84 | 2.00  | 2.16                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01010 | 1.84 | 2.00  | 2.16                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.89 | 2.05  | 2.21                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01011 | 1.89 | 2.05  | 2.21                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.93 | 2.10  | 2.27                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01100 | 2.30 | 2.50  | 2.70                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.39 | 2.60  | 2.81                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01101 | 2.39 | 2.60  | 2.81                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.48 | 2.70  | 2.92                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01110 | 2.48 | 2.70  | 2.92                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.58 | 2.80  | 3.02                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01111 | 2.58 | 2.80  | 3.02                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.67 | 2.90  | 3.13                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=10000 | 2.67 | 2.90  | 3.13                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.76 | 3.00  | 3.24                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=10001 | 2.76 | 3.00  | 3.24                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.85 | 3.10  | 3.35                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=10010 | 2.85 | 3.10  | 3.35                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.94 | 3.20  | 3.46                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=10011 | 2.94 | 3.20  | 3.46                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 3.04 | 3.30  | 3.56                             | V   | When voltage rises |

| LVD stabilization wait time | T <sub>LVDW</sub>  | -          | -    | -     | 8160<br>×<br>t <sub>CYCP</sub> * | μs  |                    |

| LVD detection delay time    | T <sub>LVDDL</sub> | -          | -    | -     | 200                              | μs  |                    |

\*: t<sub>CYCP</sub> represents the APB1 bus clock cycle time.

### 11.7 Flash Memory Write/Erase Characteristics

(V<sub>CC</sub>=1.65 V to 3.6 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter                    |                 | Value |     |      | Unit | Remarks                                                                     |  |

|------------------------------|-----------------|-------|-----|------|------|-----------------------------------------------------------------------------|--|

|                              |                 | Min   | Тур | Max  | Unit | Rellidiks                                                                   |  |

| Sector erase time            | Large<br>sector | -     | 1.1 | 2.7  | S    | The sector erase time includes the time of writing prior to internal erase. |  |

|                              | Small sector    | -     | 0.3 | 0.9  |      |                                                                             |  |

| Halfword (16-bit) write time |                 | -     | 30  | 528  | μs   | The halfword (16-bit) write time excludes the system-level overhead.        |  |

| Chip erase time              |                 | -     | 4.5 | 11.7 | s    | The chip erase time includes the time of writing prior to internal erase.   |  |

\*: The typical value is immediately after shipment, the maximum value is guarantee value under 10,000 cycle of erase/write.

### Write/Erase Cycle and Data Hold Time

| Write/Erase Cycle |       | Data Hold Time (Year) | Remarks |

|-------------------|-------|-----------------------|---------|

|                   | 1,000 | 20*                   |         |

| 10,000 10*        |       | 10*                   |         |

\*: This value comes from the technology qualification (using Arrhenius equation to translate high temperature acceleration test result into average temperature value at + 85°C).

# 12. Ordering Information

| Part number       | On-chip<br>Flash<br>memory<br>[Kbyte] | On-Chip<br>SRAM<br>[Kbyte] | Package                                  | Packing |

|-------------------|---------------------------------------|----------------------------|------------------------------------------|---------|

| S6E1C12D0AGV20000 | 128                                   | 16                         | Plastic • LQFP (0.50 mm pitch), 64 pins  | Trov    |

| S6E1C11D0AGV20000 | 64                                    | 12                         | (FPT-64P-M38)                            | Tray    |

| S6E1C12C0AGV20000 | 128                                   | 16                         | Plastic • LQFP (0.50 mm pitch), 48 pins  | Tray    |

| S6E1C11C0AGV20000 | 64                                    | 12                         | (FPT-48P-M49)                            |         |

| S6E1C12B0AGP20000 | 128                                   | 16                         | Plastic • LQFP (0.80 mm pitch), 32 pins  | Tray    |

| S6E1C11B0AGP20000 | 64                                    | 12                         | (FPT-32P-M30)                            |         |

| S6E1C12D0AGN20000 | 128                                   | 16                         | Plastic • QFN64 (0.50 mm pitch), 64 pins | Tray    |

| S6E1C11D0AGN20000 | 64                                    | 12                         | (LCC-64P-M25)                            |         |

| S6E1C12C0AGN20000 | 128                                   | 16                         | Plastic • QFN48 (0.50 mm pitch), 48 pins | Tray    |

| S6E1C11C0AGN20000 | 64                                    | 12                         | (LCC-48P-M74)                            |         |

| S6E1C12B0AGN20000 | 128                                   | 16                         | Plastic • QFN32 (0.50 mm pitch), 32 pins | Tray    |

| S6E1C11B0AGN20000 | 64                                    | 12                         | (LCC-32P-M73)                            |         |