Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                             |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CSIO, I <sup>2</sup> C, LINbus, SmartCard, UART/USART                        |

| Peripherals                | I <sup>2</sup> S, LVD, POR, PWM, WDT                                         |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x12b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-LQFP                                                                      |

| Supplier Device Package    | 48-LQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e1c12c0agv20000 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              |          |                                           |         | Pin no. |         |

|--------------|----------|-------------------------------------------|---------|---------|---------|

| Pin function | Pin name | Function description                      | LQFP-64 | LQFP-48 | LQFP-32 |

|              |          |                                           | QFN-64  | QFN-48  | QFN-32  |

|              | INT00_0  | - External interrupt request 00 input pin | 1       | 1       | 2       |

|              | INT00_1  | External interrupt request of input pin   | 56      | 42      | 29      |

|              | INT01_0  | External interrupt request 01 input pin   | 2       | 2       | 3       |

|              | INT02_0  | External interrupt request 02 input pin   | 3       | 3       | 4       |

|              | INT02_1  | External interrupt request of input pin   | 41      | 29      | 19      |

|              | INT03_0  |                                           | 11      | 10      | -       |

|              | INT03_1  | External interrupt request 03 input pin   | 44      | 32      | -       |

|              | INT03_2  |                                           | 5       | 5       | -       |

|              | INT04_0  | External interrupt request 04 input hip   | 8       | 8       | 7       |

| External     | INT04_2  | External interrupt request 04 input pin   | 6       | 6       | 5       |

| Interrupt    | INT05_1  |                                           | 38      | 27      | -       |

|              | INT05_2  | External interrupt request 05 input pin   | 7       | 7       | 6       |

|              | INT06_1  |                                           | 51      | 39      | 26      |

|              | INT06_2  | External interrupt request 06 input pin   | 26      | 18      | -       |

|              | INT07_2  | External interrupt request 07 input pin   | 4       | 4       | -       |

|              | INT08_1  | External interrupt request 08 input pin   | 10      | -       | -       |

|              | INT12_1  | External interrupt request 12 input pin   | 20      | -       | -       |

|              | INT13_1  | External interrupt request 13 input pin   | 21      | -       | -       |

|              | INT15_1  | External interrupt request 15 input pin   | 33      | 25      | 17      |

|              | NMIX     | Non-Maskable Interrupt input pin          | 64      | 48      | 1       |

|              | P00      |                                           | 52      | -       | -       |

|              | P01      |                                           | 53      | 40      | 27      |

|              | P02      |                                           | 54      | -       | -       |

| 0.510        | P03      |                                           | 55      | 41      | 28      |

| GPIO         | P05      | General-purpose I/O port 0                | 56      | 42      | 29      |

|              | P0B      |                                           | 62      | -       | -       |

|              | P0C      |                                           | 63      | -       | -       |

|              | P0F      |                                           | 64      | 48      | 1       |

|              | P10      |                                           | 40      | 28      | 18      |

|              | P11      |                                           | 41      | 29      | 19      |

|              | P12      |                                           | 42      | 30      | 20      |

|              | P13      |                                           | 43      | 31      | 21      |

|              | P14      |                                           | 44      | 32      | -       |

| 0.510        | P15      |                                           | 45      | 33      | -       |

| GPIO         | P1A      | General-purpose I/O port 1                | 38      | 27      | -       |

|              | P1B      |                                           | 37      | 26      | -       |

|              | P1C      |                                           | 36      | -       | -       |

|              | P1D      |                                           | 35      | -       | -       |

|              | P1E      |                                           | 34      | -       | -       |

|              | P1F      |                                           | 39      | -       | -       |

|              | P21      |                                           | 51      | 39      | 26      |

| GPIO         | P22      | General-purpose I/O port 2                | 47      | 35      | 23      |

|              | P23      | 1                                         | 46      | 34      | 22      |

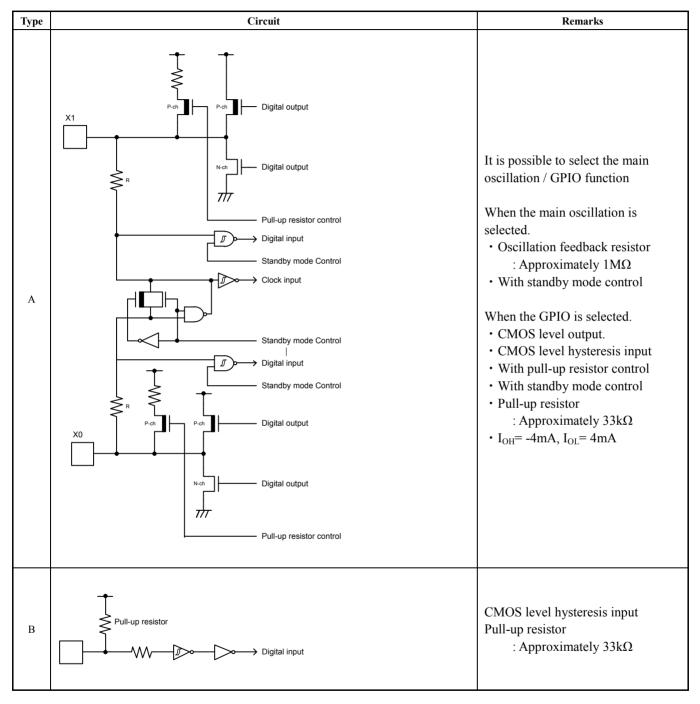

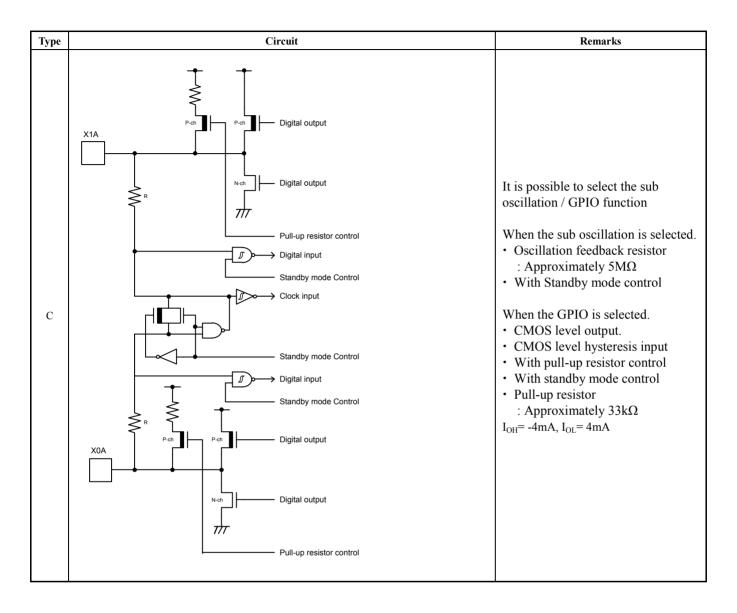

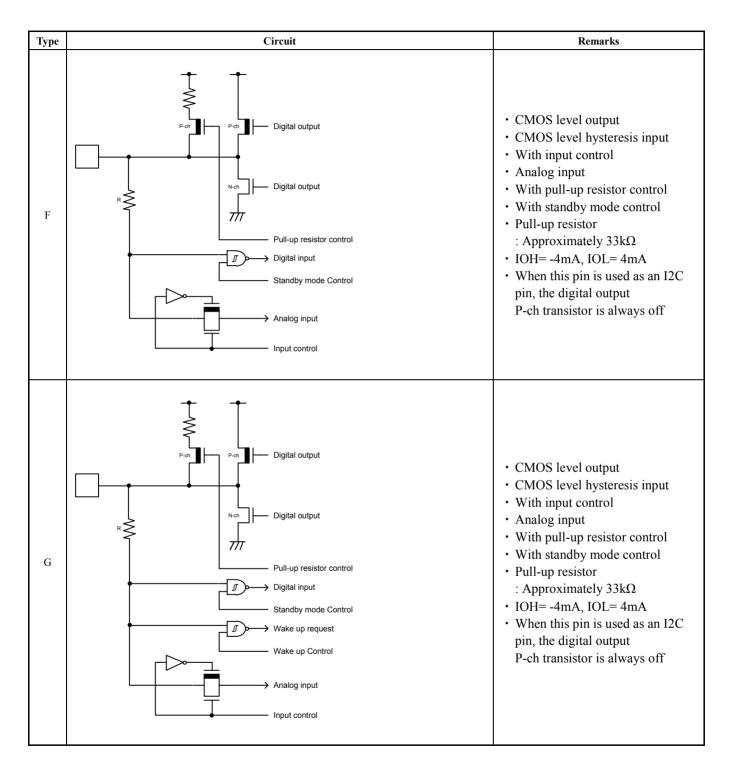

# 5. I/O Circuit Type

# 6. Handling Precautions

Any semiconductor devices have inherently a certain rate of failure. The possibility of failure is greatly affected by the conditions in which they are used (circuit conditions, environmental conditions, etc.). This page describes precautions that must be observed to minimize the chance of failure and to obtain higher reliability from your Spansion semiconductor devices.

### 6.1 Precautions for Product Design

This section describes precautions when designing electronic equipment using semiconductor devices.

### **Absolute Maximum Ratings**

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of certain established limits, called absolute maximum ratings. Do not exceed these ratings.

### **Recommended Operating Conditions**

Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their sales representative beforehand.

### **Processing and Protection of Pins**

These precautions must be followed when handling the pins which connect semiconductor devices to power supply and input/output functions.

(1) Preventing Over-Voltage and Over-Current Conditions

Exposure to voltage or current levels in excess of maximum ratings at any pin is likely to cause deterioration within the device, and in extreme cases leads to permanent damage of the device. Try to prevent such overvoltage or over-current conditions at the design stage.

(2) Protection of Output Pins

Shorting of output pins to supply pins or other output pins, or connection to large capacitance can cause large current flows. Such conditions if present for extended periods of time can damage the device.

Therefore, avoid this type of connection.

(3) Handling of Unused Input Pins

Unconnected input pins with very high impedance levels can adversely affect stability of operation. Such pins should be connected through an appropriate resistance to a power supply pin or ground pin.

# 7. Handling Devices

### **Power Supply Pins**

In products with multiple VCC and VSS pins, respective pins at the same potential are interconnected within the device in order to prevent malfunctions such as latch-up. However, all of these pins should be connected externally to the power supply or ground lines in order to reduce electromagnetic emission levels, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with each Power supply pin and GND pin of this device at low impedance. It is also advisable that a ceramic capacitor of approximately 0.1 µF be connected as a bypass capacitor between each Power supply pin and GND pin, between AVRH pin and AVRL pin near this device.

### **Stabilizing Supply Voltage**

A malfunction may occur when the power supply voltage fluctuates rapidly even though the fluctuation is within the recommended operating conditions of the VCC power supply voltage. As a rule, with voltage stabilization, suppress the voltage fluctuation so that the fluctuation in VCC ripple (peak-to-peak value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the VCC value in the recommended operating conditions, and the transient fluctuation rate does not exceed 0.1 V/µs when there is a momentary fluctuation on switching the power supply.

#### **Crystal Oscillator Circuit**

Noise near the X0/X1 and X0A/X1A pins may cause the device to malfunction. Design the printed circuit board so that X0/X1, X0A/X1A pins, the crystal oscillator, and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended that the PC board artwork be designed such that the X0/X1 and X0A/X1A pins are surrounded by ground plane as this is expected to produce stable operation.

Evaluate oscillation of your using crystal oscillator by your mount board.

#### Sub Crystal Oscillator

This series sub oscillator circuit is low gain to keep the low current consumption. The crystal oscillator to fill the following conditions is recommended for sub crystal oscillator to stabilize the oscillation.

■Surface mount type

Size: More than 3.2 mm × 1.5 mm

Load capacitance: Approximately 6 pF to 7 pF

■Lead type

Load capacitance: Approximately 6 pF to 7 pF

## Additional note

Additional note is described below.

- \*1 In this type, when internal oscillation function is selected, digital output is disabled. (Hi-Z) pull up register is off, digital input is shut off by fixed 0.

- \*2 In this type, when Digital I/O function is selected, internal oscillation function is disabled.

- \*3 In this type, when analog input function is selected, digital output is disabled, (Hi-Z). pull up register is off, digital input is shut off by fixed 0.

- \*4 In this type, when Digital I/O function is selected, analog input function is not available.

- \*5 In this case, PCR register is initialized to "1". Pull up register is on.

- \*6 This pin does not have pull up register.

# LVD Current

(V<sub>CC</sub>=1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter Symbol                                   | Pin    | Conditions | Va           | lue  | Unit | Remarks   |                                |

|----------------------------------------------------|--------|------------|--------------|------|------|-----------|--------------------------------|

| Falameter                                          | Name   | Conditions | Тур          | Max  | Unit | Reillarks |                                |

| Low-Voltage                                        |        |            |              | 0.15 | 0.3  | μA        | For occurrence of reset        |

| detection circuit<br>(LVD) power<br>supply current | ICCLVD | VCC        | At operation | 0.10 | 0.3  | μA        | For occurrence of<br>interrupt |

# **Bipolar Vref Current**

(V<sub>CC</sub>=1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter Symbol Pin<br>Name | Symbol     | Pin | Conditions   | Va   | ue      | Unit | Remarks |

|------------------------------|------------|-----|--------------|------|---------|------|---------|

|                              | Conditions | Тур | Max          | Unit | Remarks |      |         |

| Bipolar Vref<br>Current      | ICCBGR     | VCC | At operation | 100  | 200     | μA   |         |

## Flash Memory Current

(V<sub>CC</sub>=1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Baramatar                                 | Parameter Symbol Pin |            | Conditions     | Va  | lue  | Unit    | Remarks |

|-------------------------------------------|----------------------|------------|----------------|-----|------|---------|---------|

| Parameter                                 | Name Conditi         | Conditions | Тур            | Max | Unit | Remarks |         |

| Flash<br>memory<br>write/erase<br>current | Iccflash             | VCC        | At Write/Erase | 4.4 | 5.6  | mA      |         |

# A/D converter Current

(V<sub>CC</sub>=1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter               | Symbol            | Pin  | Conditions   | Va   | ue   | Unit | Remarks    |

|-------------------------|-------------------|------|--------------|------|------|------|------------|

| Falameter               | Symbol            | Name | Conditions   | Тур  | Max  | Unit | Relliarks  |

| Power supply<br>current | I <sub>CCAD</sub> | VCC  | At operation | 0.5  | 0.75 | mA   |            |

| Reference power supply  |                   | AVRH | At operation | 0.69 | 1.3  | mA   | AVRH=3.6 V |

| current<br>(AVRH)       | ICCAVRH           | АУКП | At stop      | 0.1  | 1.3  | μA   |            |

## 11.3.2 Pin Characteristics

| Damana dam                | 0. makes l        | Dia Nama                        | O a se diti a se a                                                                                |                         | Value                 |                       | 11   | Demontos |

|---------------------------|-------------------|---------------------------------|---------------------------------------------------------------------------------------------------|-------------------------|-----------------------|-----------------------|------|----------|

| Parameter                 | Symbol            | Pin Name                        | Conditions                                                                                        | Min                     | Тур                   | Max                   | Unit | Remarks  |

| H level input             |                   | CMOS<br>hysteresis              | V <sub>CC</sub> ≥ 2.7 V                                                                           | V <sub>CC</sub> × 0.8   | _                     | V <sub>CC</sub> +0.3  | V    |          |

| voltage<br>(hysteresis    | V <sub>IHS</sub>  | input pin,<br>MD0               | V <sub>CC</sub> < 2.7 V                                                                           | V <sub>CC</sub> × 0.7   |                       | V(( ) 0.0             | , ,  |          |

| input)                    |                   | 5 V tolerant                    | $V_{CC} \ge 2.7 V$                                                                                | V <sub>CC</sub> × 0.8   | _                     | V <sub>SS</sub> +5.5  | V    |          |

|                           |                   | input pin                       | $V_{CC}$ < 2.7 V                                                                                  | V <sub>CC</sub> × 0.7   | _                     | V SS 10.0             | v    |          |

| L level input             |                   | CMOS<br>hysteresis              | V <sub>CC</sub> ≥ 2.7 V                                                                           | V <sub>SS</sub> - 0.3   | _                     | V <sub>CC</sub> × 0.2 | V    |          |

| voltage V <sub>ILS</sub>  | input pin,<br>MD0 | $V_{CC}$ < 2.7 V                |                                                                                                   |                         | V <sub>CC</sub> × 0.3 |                       |      |          |

| input)                    |                   | 5 V tolerant                    | $V_{CC} \ge 2.7 V$                                                                                |                         | -                     | V <sub>CC</sub> × 0.2 |      |          |

|                           |                   | input pin                       | V <sub>CC</sub> < 2.7 V                                                                           | - V <sub>SS</sub> - 0.3 | -                     | V <sub>CC</sub> × 0.3 | V    |          |

| H level                   | V <sub>OH</sub>   | 4 mA type                       | V <sub>CC</sub> ≥ 2.7 V,<br>I <sub>OH</sub> = - 4 mA                                              | V <sub>CC</sub> - 0.5   | _                     | V <sub>cc</sub>       | V    |          |

| output voltage            | VON               | i nii (type                     | V <sub>CC</sub> < 2.7 V,<br>I <sub>OH</sub> = - 2 mA                                              | V <sub>CC</sub> - 0.45  |                       | •00                   | , ,  |          |

| L level<br>output voltage | V <sub>OL</sub>   | 4 mA type                       | $V_{CC} \ge 2.7 \text{ V},$ $I_{OL} 4 \text{ mA}$ $V_{CC} < 2.7 \text{ V},$ $I_{OL}=2 \text{ mA}$ | Vss                     | -                     | 0.4                   | V    |          |

| Input leak<br>current     | I <sub>IL</sub>   | -                               | -                                                                                                 | - 5                     | -                     | + 5                   | μA   |          |

| Pull-up                   |                   |                                 | V <sub>CC</sub> ≥ 2.7 V                                                                           | 21                      | 33                    | 48                    |      |          |

|                           | R <sub>PU</sub>   | Pull-up pin                     | V <sub>CC</sub> < 2.7 V                                                                           | -                       | -                     | 88                    | kΩ   |          |

| Input<br>capacitance      | C <sub>IN</sub>   | Other than<br>VCC, VSS,<br>AVRH | -                                                                                                 | -                       | 5                     | 15                    | pF   |          |

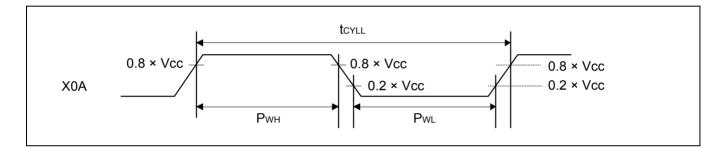

## 11.4.2 Sub Clock Input Characteristics

(V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter               | Symbol            | Pin         | Conditions              |     | Value  |       | Unit | Remarks                                        |  |

|-------------------------|-------------------|-------------|-------------------------|-----|--------|-------|------|------------------------------------------------|--|

| Falameter               | Symbol            | Name        | Conditions              | Min | Тур    | Max   | Onit | Remarks                                        |  |

| Input frequency         | f <sub>CL</sub>   |             | -                       | -   | 32.768 | -     | kHz  | When the crystal<br>oscillator is<br>connected |  |

|                         |                   | X0A,<br>X1A | -                       | 32  | -      | 100   | kHz  | When the external<br>clock is used             |  |

| Input clock cycle       | t <sub>CYLL</sub> |             | -                       | 10  | -      | 31.25 | μs   | When the external<br>clock is used             |  |

| Input clock pulse width | -                 |             | Pwh/tcyll,<br>Pwl/tcyll | 45  | -      | 55    | %    | When the external<br>clock is used             |  |

\*: See "Sub crystal oscillator" in "7. Handling Devices" for the crystal oscillator used.

### 11.4.6 Reset Input Characteristics

(V<sub>CC</sub> = 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter        | Symbol             | Pin   | Conditions - | Va  | lue | Unit | Remarks |

|------------------|--------------------|-------|--------------|-----|-----|------|---------|

|                  | Gymbol             | Name  |              | Min | Max | onic | Remarks |

| Reset input time | t <sub>INITX</sub> | INITX | -            | 500 | -   | ns   |         |

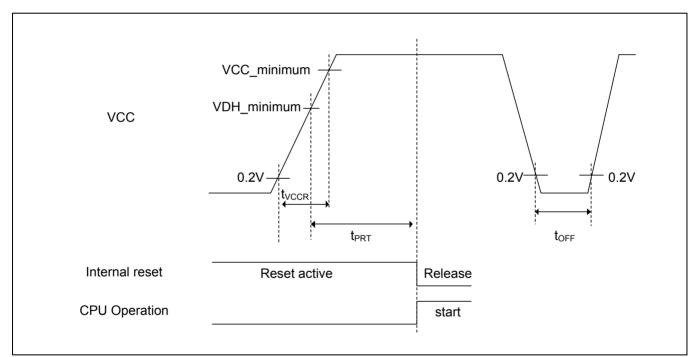

#### 11.4.7 Power-on Reset Timing

(V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter                              | Symbol            | Pin  | Valu | ue  | Unit | Remarks |

|----------------------------------------|-------------------|------|------|-----|------|---------|

|                                        | Symbol            | Name | Min  | Max | Unit | Remarks |

| Power supply rising time               | t <sub>VCCR</sub> |      | 0    | -   | ms   |         |

| Power supply shut down time            | t <sub>OFF</sub>  | VCC  | 1    | -   | ms   |         |

| Time until releasing<br>Power-on reset | t <sub>PRT</sub>  |      | 0.43 | 3.4 | ms   |         |

# Glossary

$\square$  VCC\_minimum : Minimum V<sub>CC</sub> of recommended operating conditions.

UDH\_minimum : Minimum detection voltage of Low-Voltage detection reset.

See "11.6 Low-Voltage Detection Characteristics".

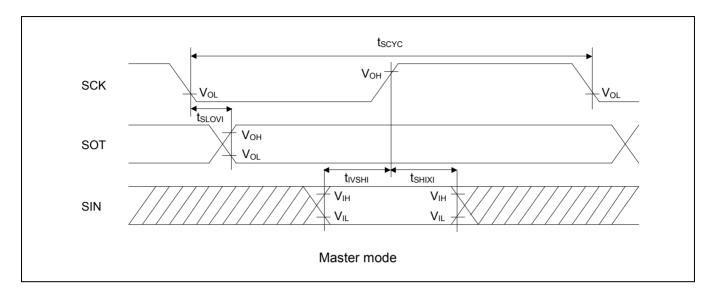

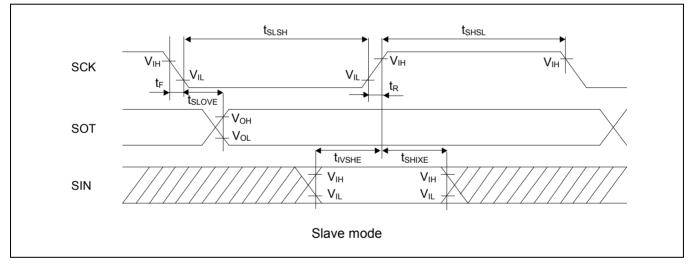

## CSIO (SPI=0, SCINV=1)

| Parameter                                                        | Symbol             | Pin           | Conditions  | V <sub>cc</sub> < 2         | 2.7V | V <sub>cc</sub> ≥:          | 2.7V | Unit |

|------------------------------------------------------------------|--------------------|---------------|-------------|-----------------------------|------|-----------------------------|------|------|

| Parameter                                                        | Symbol             | name          | Conditions  | Min                         | Max  | Min                         | Max  | Unit |

| Serial clock cycle time                                          | t <sub>scyc</sub>  | SCKx          |             | 4 t <sub>CYCP</sub>         | -    | 4 t <sub>CYCP</sub>         | -    | ns   |

| $SCK \uparrow \to SOT \text{ delay time}$                        | tsнovi             | SCKx,<br>SOTx |             | - 30                        | + 30 | - 20                        | + 20 | ns   |

| $SIN \to SCK \downarrow setup time$                              | t <sub>IVSLI</sub> | SCKx,<br>SINx | Master mode | 50                          | -    | 36                          | -    | ns   |

| $SCK \downarrow \to SIN$ hold time                               | t <sub>SLIXI</sub> | SCKx,<br>SINx |             | 0                           | -    | 0                           | -    | ns   |

| Serial clock "L" pulse width                                     | t <sub>sLSH</sub>  | SCKx          |             | 2 t <sub>CYCP</sub> -<br>10 | -    | 2 t <sub>CYCP</sub> -<br>10 | -    | ns   |

| Serial clock "H" pulse width                                     | t <sub>SHSL</sub>  | SCKx          |             | t <sub>CYCP</sub> + 10      | -    | t <sub>CYCP</sub> + 10      | -    | ns   |

| $SCK \uparrow \to SOT$ delay time                                | t <sub>SHOVE</sub> | SCKx,<br>SOTx |             | -                           | 50   | -                           | 33   | ns   |

| $\text{SIN} \rightarrow \text{SCK} \downarrow \text{setup time}$ | $t_{\text{IVSLE}}$ | SCKx,<br>SINx | Slave mode  | 10                          | -    | 10                          | -    | ns   |

| $SCK \downarrow \to SIN \text{ hold time}$                       | t <sub>SLIXE</sub> | SCKx,<br>SINx | -<br>-<br>- | 20                          | -    | 20                          | -    | ns   |

| SCK falling time                                                 | tF                 | SCKx          |             | -                           | 5    | -                           | 5    | ns   |

| SCK rising time                                                  | tR                 | SCKx          | ]           | -                           | 5    | -                           | 5    | ns   |

#### $(V_{CC} = 1.65 \text{ V to } 3.6 \text{ V}, V_{SS} = 0 \text{ V}, T_{A} = -40^{\circ}\text{C to } +105^{\circ}\text{C})$

#### Notes:

- The above AC characteristics are for clock synchronous mode.

- t<sub>CYCP</sub> represents the APB bus clock cycle time.

For the number of the APB bus to which Multi-function Serial has been connected, see "8. Block Diagram".

- The characteristics are only applicable when the relocate port numbers are the same. For instance, they are not applicable for the combination of SCKx\_0 and SOTx\_1.

- External load capacitance C<sub>L</sub>=30 pF

# SPI (SPI=1, SCINV=0)

| _                                                                |                    | Pin           |             | V <sub>cc</sub> < 2         | 7 V  | V <sub>cc</sub> ≥           | 2 7 V |      |

|------------------------------------------------------------------|--------------------|---------------|-------------|-----------------------------|------|-----------------------------|-------|------|

| Parameter                                                        | Symbol             | name          | Conditions  | Min                         | Max  | Min                         | Max   | Unit |

| Serial clock cycle time                                          | tscyc              | SCKx          |             | 4 t <sub>CYCP</sub>         | -    | 4 t <sub>CYCP</sub>         | -     | ns   |

| $SCK \uparrow \to SOT \text{ delay time}$                        | t <sub>shovi</sub> | SCKx,<br>SOTx |             | - 30                        | + 30 | - 20                        | + 20  | ns   |

| $SIN \to SCK \downarrow setup time$                              | t <sub>IVSLI</sub> | SCKx,<br>SINx | Master mode | 50                          | -    | 36                          | -     | ns   |

| $SCK \downarrow \to SIN \text{ hold time}$                       | t <sub>sLixi</sub> | SCKx,<br>SINx |             | 0                           | -    | 0                           | -     | ns   |

| $\text{SOT} \rightarrow \text{SCK} \downarrow \text{delay time}$ | t <sub>SOVLI</sub> | SCKx,<br>SOTx |             | 2 t <sub>CYCP</sub> -<br>30 | -    | 2 t <sub>CYCP</sub> -<br>30 | -     | ns   |

| Serial clock "L" pulse width                                     | t <sub>sLSH</sub>  | SCKx          |             | 2 t <sub>CYCP</sub> -<br>10 | -    | 2 t <sub>CYCP</sub> -<br>10 | -     | ns   |

| Serial clock "H" pulse width                                     | t <sub>SHSL</sub>  | SCKx          |             | t <sub>CYCP</sub> + 10      | -    | t <sub>CYCP</sub> + 10      | -     | ns   |

| $SCK \uparrow \to SOT$ delay time                                | t <sub>shove</sub> | SCKx,<br>SOTx |             | -                           | 50   | -                           | 33    | ns   |

| $SIN \to SCK \downarrow setup time$                              | t <sub>IVSLE</sub> | SCKx,<br>SINx | Slave mode  | 10                          | -    | 10                          | -     | ns   |

| $SCK \downarrow \to SIN \text{ hold time}$                       | t <sub>SLIXE</sub> | SCKx,<br>SINx | -           | 20                          | -    | 20                          | -     | ns   |

| SCK falling time                                                 | tF                 | SCKx          |             | -                           | 5    | -                           | 5     | ns   |

| SCK rising time                                                  | tR                 | SCKx          | ]           | -                           | 5    | -                           | 5     | ns   |

#### (V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

#### Notes:

- The above AC characteristics are for clock synchronous mode.

t<sub>CYCP</sub> represents the APB bus clock cycle time.

For the number of the APB bus to which Multi-function Serial has been connected, see "8. Block Diagram".

- The characteristics are only applicable when the relocate port numbers are the same. For instance, they are not applicable for the combination of SCKx\_0 and SOTx\_1.

- External load capacitance C<sub>L</sub>=30 pF

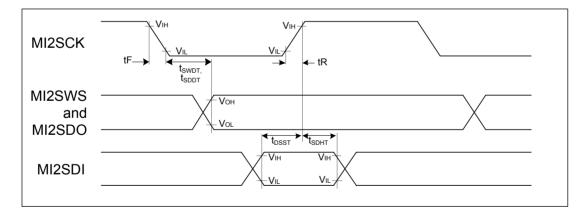

# 11.4.12 I<sup>2</sup>S Timing (MFS-I2S Timing)

# Master Mode Timing

(V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter                                                                                      | Symbo               | Pin                     | Conditions            | V <sub>cc</sub> < 2.7 V |       | V <sub>cc</sub> ≥ 2.7 V |       | Unit |

|------------------------------------------------------------------------------------------------|---------------------|-------------------------|-----------------------|-------------------------|-------|-------------------------|-------|------|

| Farameter                                                                                      | Ī                   | Name                    | Conditions            | Min                     | Max   | Min                     | Max   | Unit |

| MI2SCK max frequency (*1)                                                                      | F <sub>MI2SCK</sub> | MI2SCKx                 |                       | I                       | 6.144 | -                       | 6.144 | MHz  |

| I <sup>2</sup> S clock cycle time (*1)                                                         | t <sub>ICYC</sub>   | MI2SCKx                 |                       | 4 t <sub>CYCP</sub>     | -     | 4 t <sub>CYCP</sub>     | -     | ns   |

| I <sup>2</sup> S clock Duty cycle                                                              | Δ                   | MI2SCKx                 |                       | 45%                     | 55%   | 45%                     | 55%   |      |

|                                                                                                |                     | MI2SCKx                 |                       |                         |       |                         |       |      |

| $\begin{array}{l} MI2SCK \downarrow \ \rightarrow \ MI2SWS \ delay \\ time \end{array}$        | t <sub>SWDT</sub>   | MI2ŚWS<br>x             |                       | -30                     | +30   | -20                     | +20   | ns   |

|                                                                                                |                     | MI2SCKx                 |                       |                         |       |                         |       |      |

| $\begin{array}{l} MI2SCK\downarrow \ \rightarrow \ MI2SDO \ delay \\ time \end{array}$         | t <sub>SDDT</sub>   | MI2SCKX<br>MI2SDO<br>X  | С <sub>∟</sub> =30 рF | -30                     | +30   | -20                     | +20   | ns   |

| $\begin{array}{rl} MI2SDI \ \rightarrow \ MI2SCK \ \uparrow \ setup \\ time \end{array}$       | t <sub>DSST</sub>   | MI2SCKx<br>,<br>MI2SDIx |                       | 50                      | -     | 36                      | -     | ns   |

| $\begin{array}{rcl} MI2SCK & \uparrow & \rightarrow & MI2SDI \text{ hold} \\ time \end{array}$ | t <sub>SDHT</sub>   | MI2SCKx<br>,<br>MI2SDIx |                       | 0                       | -     | 0                       | -     | ns   |

| MI2SCK falling time                                                                            | tF                  | MI2SCKx                 |                       | -                       | 5     | -                       | 5     | ns   |

| MI2SCK rising time                                                                             | tR                  | MI2SCKx                 |                       | -                       | 5     | -                       | 5     | ns   |

\*1: I<sup>2</sup>S clock should meet the multiple of PCLK(t<sub>ICYC</sub>) and the frequency less than F<sub>MI2SCK</sub> meantime. The detail information please refer to Chapter I<sup>2</sup>S of Communication Macro Part of Peripheral Manual.

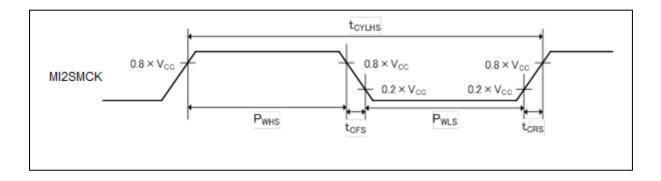

# **MI2SMCK Input Characteristics**

| ·····                               |                                      |          |                                                                              | (V <sub>CC</sub> = 1.65 ) | V to 3.6 V, V | / <sub>SS</sub> = 0 V | ∕, T <sub>A</sub> =- 40°C to +10 |

|-------------------------------------|--------------------------------------|----------|------------------------------------------------------------------------------|---------------------------|---------------|-----------------------|----------------------------------|

| Parameter                           | Symbol                               | Pin Name | Conditions                                                                   | -                         | lue           | Unit                  | Remarks                          |

| Falailletei                         | Oymbol                               |          |                                                                              | Min                       | Max           | Onit                  | Remarks                          |

| Input frequency                     | f <sub>CHS</sub>                     | MI2SMCK  | -                                                                            | -                         | 12.288        | MHz                   |                                  |

| Input clock cycle                   | t <sub>CYLHS</sub>                   | -        | -                                                                            | 81.3                      | -             | ns                    |                                  |

| Input clock pulse width             | -                                    | -        | P <sub>WHS</sub> /t <sub>CYLHS</sub><br>P <sub>WLS</sub> /t <sub>CYLHS</sub> | 45                        | 55            | %                     | When using<br>external clock     |

| Input clock rise time and fall time | t <sub>CFS</sub><br>t <sub>CRS</sub> | -        | -                                                                            | -                         | 5             | ns                    | When using<br>external clock     |

# **MI2SMCK** Output Characteristics

(V\_{CC}= 1.65 V to 3.6 V, V\_{SS}= 0 V, T\_A=- 40^{\circ}C to +105 $^{\circ}C$ )

| Parameter                                 | Symbol | Pin Name  | Conditions | Va  | lue                     | Unit | Remarks   |  |

|-------------------------------------------|--------|-----------|------------|-----|-------------------------|------|-----------|--|

| Falameter                                 | Symbol | Fill Name | Conditions | Min | Max                     | Unit | Relliaiks |  |

| Output frequency f <sub>CHS</sub> MI2SMCK |        | -         | 25         | MHz | V <sub>CC</sub> ≥ 2.7 V |      |           |  |

|                                           |        | -         | 20         | MHz | V <sub>CC</sub> < 2.7 V |      |           |  |

# 11.6.2 Low-Voltage Detection Interrupt

(T<sub>A</sub>=-40°C to +105°C)

| Paramotor                   | Parameter Symbo Conditions |            |      | Value |                                  | Uni | Remarks            |

|-----------------------------|----------------------------|------------|------|-------|----------------------------------|-----|--------------------|

| Falameter                   |                            |            | Min  | Тур   | Max                              | t   | Rellars            |

| Detected voltage            | VDL                        | SVHI=00100 | 1.56 | 1.70  | 1.84                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 1.61 | 1.75  | 1.89                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=00101 | 1.61 | 1.75  | 1.89                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 1.66 | 1.80  | 1.94                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=00110 | 1.66 | 1.80  | 1.94                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 1.70 | 1.85  | 2.00                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=00111 | 1.70 | 1.85  | 2.00                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 1.75 | 1.90  | 2.05                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=01000 | 1.75 | 1.90  | 2.05                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 1.79 | 1.95  | 2.11                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=01001 | 1.79 | 1.95  | 2.11                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 1.84 | 2.00  | 2.16                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=01010 | 1.84 | 2.00  | 2.16                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 1.89 | 2.05  | 2.21                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=01011 | 1.89 | 2.05  | 2.21                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 1.93 | 2.10  | 2.27                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=01100 | 2.30 | 2.50  | 2.70                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 2.39 | 2.60  | 2.81                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=01101 | 2.39 | 2.60  | 2.81                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 2.48 | 2.70  | 2.92                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=01110 | 2.48 | 2.70  | 2.92                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 2.58 | 2.80  | 3.02                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=01111 | 2.58 | 2.80  | 3.02                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 2.67 | 2.90  | 3.13                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=10000 | 2.67 | 2.90  | 3.13                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 2.76 | 3.00  | 3.24                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=10001 | 2.76 | 3.00  | 3.24                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 2.85 | 3.10  | 3.35                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=10010 | 2.85 | 3.10  | 3.35                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 2.94 | 3.20  | 3.46                             | V   | When voltage rises |

| Detected voltage            | VDL                        | SVHI=10011 | 2.94 | 3.20  | 3.46                             | V   | When voltage drops |

| Released voltage            | VDH                        |            | 3.04 | 3.30  | 3.56                             | V   | When voltage rises |

| LVD stabilization wait time | T <sub>LVDW</sub>          | -          | -    | -     | 8160<br>×<br>t <sub>CYCP</sub> * | μs  |                    |

| LVD detection delay time    | T <sub>LVDDL</sub>         | -          | -    | -     | 200                              | μs  |                    |

\*: t<sub>CYCP</sub> represents the APB1 bus clock cycle time.

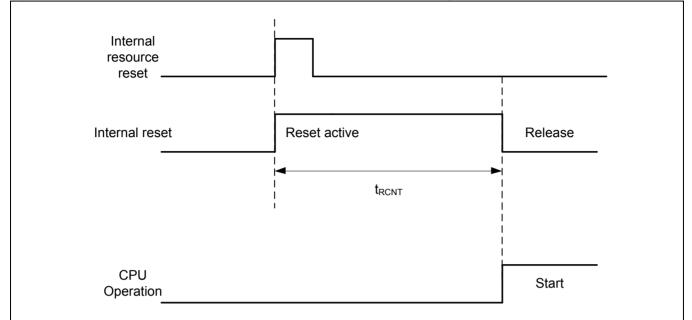

#### Operation Example of Return from Low Power Consumption Mode (by Internal Resource Reset\*)

\*: Internal resource reset is not included in return factor by the kind of Low-Power consumption mode.

#### Notes:

- The return factor is different in each Low-Power consumption modes.

See "Chapter: Low Power Consumption Mode" and "Operations of Standby Modes" in FM0+ Family Peripheral Manual.

- When interrupt recoveries, the operation mode that CPU recoveries depends on the state before the Low-Power consumption mode transition. See "Chapter: Low Power Consumption Mode" in "FM0+ Family Peripheral Manual".

- The time during the power-on reset/low-voltage detection reset is excluded. See "11.4.7 Power-on Reset Timing in 11.4 AC Characteristics in 11. Electrical Characteristics" for the detail on the time during the power-on reset/low -voltage detection reset.

- When in recovery from reset, CPU changes to the high-speed CR run mode. When using the main clock or the PLL clock, it is

necessary to add the main clock oscillation stabilization wait time or the main PLL clock stabilization wait time.

- The internal resource reset means the watchdog reset and the CSV reset.

# Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

| Products<br>Automotive   | cypress.com/go/automotive |

|--------------------------|---------------------------|

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

| Memory                   | cypress.com/go/memory     |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

| Spansion Products        | spansion.com/products     |

PSoC® Solutions psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Community | Forums | Blogs | Video | Training

Technical Support cypress.com/go/support

Cypress, the Cypress logo, Spansion<sup>®</sup>, the Spansion logo, MirrorBit<sup>®</sup>, MirrorBit<sup>®</sup> Eclipse<sup>TM</sup>, ORNAND<sup>TM</sup>, Easy DesignSim<sup>TM</sup>, Traveo<sup>TM</sup> and combinations thereof, are trademarks and registered trademarks of Cypress Semiconductor Corp. ARM and Cortex are the registered trademarks of ARM Limited in the EU and other countries. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

© Cypress Semiconductor Corporation, 2015. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.