#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 56                                                                          |

| Program Memory Size        | 16KB (16K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| Data Converters            | A/D 48x14b; D/A 2x9b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 68-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 68-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24094-24ltxi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4. Contents

| PSOC FUNCTIONAL OVERVIEW                       | 4 |

|------------------------------------------------|---|

| The PSoC Core                                  | 4 |

| The Digital System                             | 4 |

| The Analog System                              | 5 |

| Additional System Resources                    | 6 |

| PSoC Device Characteristics                    | 6 |

| GETTING STARTED                                | 7 |

| Application Notes                              | 7 |

| Development Kits                               | 7 |

| Training                                       | 7 |

| CYPros Consultants                             | 7 |

| Solutions Library                              | 7 |

| Technical Support                              | 7 |

| DEVELOPMENT TOOLS                              | 7 |

| PSoC Designer Software Subsystems              |   |

| DESIGNING WITH PSOC DESIGNER                   |   |

| Select User Modules                            |   |

| Configure User Modules                         |   |

| Organize and Connect                           |   |

| Generate, Verify, and Debug                    |   |

| PIN INFORMATION                                |   |

|                                                |   |

| 56-Pin Part Pinout                             |   |

| 68-Pin Part Pinout (with ARES)                 |   |

| 68-Pin Part Pinout (On-Chip Debug)             |   |

| 100-Ball VFBGA Part Pinout                     |   |

| 100-Ball VFBGA Part Pinout (On-Chip Debug)     |   |

| 100-Pin Part Pinout (On-Chip Debug)            |   |

| REGISTER REFERENCE                             |   |

| Register Conventions                           |   |

| Register Mapping Tables                        |   |

| Register Map Bank 0 Table: User Space          |   |

| Register Map Bank 1 Table: Configuration Space |   |

|                                                |   |

| ELECTRICAL SPECIFICATIONS                      |   |

| Operating Temperature                          |   |

| DC Electrical Characteristics                  |   |

| AC Electrical Characteristics                  |   |

| Thermal Impedance                              |   |

| Solder Reflow Peak Specifications              |   |

|                                                |   |

| DEVELOPMENT TOOL SELECTION                     | - |

| Software                                       |   |

| Development Kits<br>Evaluation Tools           |   |

|                                                |   |

# 6. Getting Started

For in-depth information, along with detailed programming information, see the Technical Reference Manual for this PSoC device.

For up-to-date ordering, packaging, and electrical specification information, see the latest PSoC device datasheets on the web at http://www.cypress.com.

#### 6.1 Application Notes

Cypress application notes are an excellent introduction to the wide variety of possible PSoC designs.

#### 6.2 Development Kits

PSoC Development Kits are available online from and through a growing number of regional and global distributors, which include Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

#### 6.3 Training

Free PSoC technical training (on demand, webinars, and workshops), which is available online via www.cypress.com,

## 7. Development Tools

PSoC Designer<sup>™</sup> is the revolutionary Integrated Design Environment (IDE) that you can use to customize PSoC to meet your specific application requirements. PSoC Designer software accelerates system design and time to market. Develop your applications using a library of precharacterized analog and digital peripherals (called user modules) in a drag-and-drop design environment. Then, customize your design by leveraging the dynamically generated application programming interface (API) libraries of code. Finally, debug and test your designs with the integrated debug environment, including in-circuit emulation and standard software debug features. PSoC Designer includes:

- Application editor graphical user interface (GUI) for device and user module configuration and dynamic reconfiguration

- Extensive user module catalog

- Integrated source-code editor (C and assembly)

- Free C compiler with no size restrictions or time limits

- Built-in debugger

- In-circuit emulation

- Built-in support for communication interfaces:

- □ Hardware and software I<sup>2</sup>C slaves and masters

- □ Full speed USB 2.0

- Up to four full-duplex universal asynchronous receiver/transmitters (UARTs), SPI master and slave, and wireless

PSoC Designer supports the entire library of PSoC 1 devices and runs on Windows XP, Windows Vista, and Windows 7.

#### 7.1 PSoC Designer Software Subsystems

#### 7.1.1 Design Entry

In the chip-level view, choose a base device to work with. Then select different onboard analog and digital components that use covers a wide variety of topics and skill levels to assist you in your designs.

#### 6.4 CYPros Consultants

Certified PSoC consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC consultant go to the CYPros Consultants web site.

#### 6.5 Solutions Library

Visit our growing library of solution-focused designs. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

#### 6.6 Technical Support

Technical support – including a searchable Knowledge Base articles and technical forums – is also available online. If you cannot find an answer to your question, call our Technical Support hotline at 1-800-541-4736.

the PSoC blocks, which are called user modules. Examples of user modules are analog-to-digital converters (ADCs), digital-to-analog converters (DACs), amplifiers, and filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The tool also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic reconfiguration makes it possible to change configurations at run time. In essence, this allows you to use more than 100 percent of PSoC's resources for an application.

#### 7.1.2 Code Generation Tools

The code generation tools work seamlessly within the PSoC Designer interface and have been tested with a full range of debugging tools. You can develop your design in C, assembly, or a combination of the two.

**Assemblers**. The assemblers allow you to merge assembly code seamlessly with C code. Link libraries automatically use absolute addressing or are compiled in relative mode, and are linked with other software modules to get absolute addressing.

**C Language Compilers.** C language compilers are available that support the PSoC family of devices. The products allow you to create complete C programs for the PSoC family devices. The optimizing C compilers provide all of the features of C, tailored to the PSoC architecture. They come complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### 7.1.3 Debugger

PSoC Designer has a debug environment that provides hardware in-circuit emulation, allowing you to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow you to read and program and

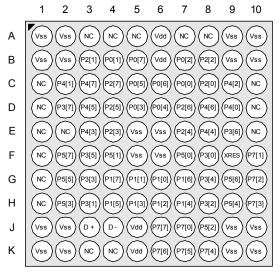

### 9.5 100-Ball VFBGA Part Pinout

The 100-ball VFBGA part is for the CY8C24994 PSoC device.

#### Table 6. 100-Ball Part Pinout (VFBGA<sup>[15]</sup>)

| Pin<br>No. | Digital | Analog     | Name            | Description                               | Pin<br>No. | Digital | Analog | Name                  | Description                                      |

|------------|---------|------------|-----------------|-------------------------------------------|------------|---------|--------|-----------------------|--------------------------------------------------|

| A1         | Power   | ſ          | V <sub>SS</sub> | Ground connection                         | F1         |         |        | NC                    | No connection. Pin must be left floating         |

| A2         | Power   | ·          | V <sub>SS</sub> | Ground connection                         | F2         | I/O     | М      | P5[7]                 |                                                  |

| A3         |         |            | NC              | No connection. Pin must be left floating  | F3         | I/O     | М      | P3[5]                 |                                                  |

| A4         |         |            | NC              | No connection. Pin must be left floating  | F4         | I/O     | М      | P5[1]                 |                                                  |

| A5         |         |            | NC              | No connection. Pin must be left floating  | F5         | Powe    | r      | V <sub>SS</sub>       | Ground connection                                |

| A6         | Power   | -          | V <sub>DD</sub> | Supply voltage                            | F6         | Powe    | r      | V <sub>SS</sub>       | Ground connection                                |

| A7         |         |            | NC              | No connection. Pin must be left floating  | F7         | I/O     | М      | P5[0]                 |                                                  |

| A8         |         |            | NC              | No connection. Pin must be left floating  | F8         | I/O     | М      | P3[0]                 |                                                  |

| A9         | Power   | ſ          | V <sub>SS</sub> | Ground connection                         | F9         |         |        | XRES                  | Active high pin reset with internal pull-down    |

| A10        | Power   | ſ          | V <sub>SS</sub> | Ground connection                         | F10        | I/O     |        | P7[1]                 |                                                  |

| B1         | Power   | ſ          | V <sub>SS</sub> | Ground connection                         | G1         |         |        | NC                    | No connection. Pin must be left floating         |

| B2         | Power   | •          | V <sub>SS</sub> | Ground connection                         | G2         | I/O     | М      | P5[5]                 |                                                  |

| B3         | I/O     | I, M       | P2[1]           | Direct switched capacitor block input     | G3         | I/O     | М      | P3[3]                 |                                                  |

| B4         | I/O     | I, M       | P0[1]           | Analog column mux input                   | G4         | I/O     | М      | P1[7]                 | I <sup>2</sup> C SCL                             |

| B5         | I/O     | I, M       | P0[7]           | Analog column mux input                   | G5         | I/O     | М      | P1[1]                 | I <sup>2</sup> C SCL, ISSP SCLK <sup>[16]</sup>  |

| B6         | Power   | -          | V <sub>DD</sub> | Supply voltage                            | G6         | I/O     | М      | P1[0]                 | I <sup>2</sup> C SDA, ISSP SDATA <sup>[16]</sup> |

| B7         | I/O     | I, M       | P0[2]           | Analog column mux input                   | G7         | I/O     | М      | P1[6]                 |                                                  |

| B8         | I/O     | I, M       | P2[2]           | Direct switched capacitor block input     | G8         | I/O     | М      | P3[4]                 |                                                  |

| B9         | Power   | 1          | V <sub>SS</sub> | Ground connection                         | G9         | I/O     | М      | P5[6]                 |                                                  |

| B10        | Power   |            | V <sub>SS</sub> | Ground connection                         | G10        | I/O     |        | P7[2]                 |                                                  |

| C1         |         |            | NC              | No connection. Pin must be left floating  | H1         |         |        | NC                    | No connection. Pin must be left floating         |

| C2         | I/O     | М          | P4[1]           |                                           | H2         | I/O     | М      | P5[3]                 |                                                  |

| C3         | 1/O     | M          | P4[7]           |                                           | H3         | 1/O     | M      | P3[1]                 |                                                  |

| C4         | I/O     | M          | P2[7]           |                                           | H4         | 1/O     | M      | P1[5]                 | I <sup>2</sup> C SDA                             |

| C5         | I/O     | I/O, M     | P0[5]           | Analog column mux input and column output | H5         | 1/O     | M      | P1[3]                 |                                                  |

| C6         | I/O     | I, M       | P0[6]           | Analog column mux input and column output | H6         | 1/O     | M      | P1[2]                 |                                                  |

| C7         | I/O     | I, M       | P0[0]           | Analog column mux input                   | H7         | 1/O     | M      | P1[4]                 | Optional EXTCLK                                  |

| C8         | 1/O     | I, M       | P2[0]           | Direct switched capacitor block input     | H8         | 1/O     | M      | P3[2]                 |                                                  |

| C9         | I/O     | M          | P4[2]           |                                           | H9         | 1/O     | M      | P5[4]                 |                                                  |

| C10        | 1/0     | 101        | NC              | No connection. Pin must be left floating  | H10        | 1/O     |        | P7[3]                 |                                                  |

| D1         |         |            | NC              | No connection. Pin must be left floating  | J1         | Powe    | r      | V <sub>SS</sub>       | Ground connection                                |

| D1<br>D2   | I/O     | М          | P3[7]           | No connection. I in must be left hoating  | J2         | Powe    |        |                       | Ground connection                                |

| D2<br>D3   | 1/O     | M          | P4[5]           |                                           | J3         | USB     | 1      | V <sub>SS</sub><br>D+ |                                                  |

| D3<br>D4   | 1/O     | M          | P2[5]           |                                           | J4         | USB     |        | D-                    |                                                  |

| D4<br>D5   | 1/O     | I/O, M     | P0[3]           | Analog column mux input and column output | J5         | Powe    | r      |                       | Supply voltage                                   |

| D5<br>D6   | 1/O     | I,M        | P0[3]<br>P0[4]  | Analog column mux input                   | J6         | I/O     | 1      | V <sub>DD</sub>       |                                                  |

| D0<br>D7   | 1/O     | n,ivi<br>M | P0[4]<br>P2[6]  | External VREF input                       | J0<br>J7   | 1/O     |        | P7[7]<br>P7[0]        |                                                  |

| D7<br>D8   | 1/O     | M          | P4[6]           |                                           | J8         | 1/O     | М      | P5[2]                 |                                                  |

| D8<br>D9   | 1/O     | M          |                 |                                           | 19<br>19   |         |        |                       | Cround connection                                |

|            | 1/0     | IVI        | P4[0]           | No conception. Dis much he left floation  |            | Powe    |        | V <sub>SS</sub>       | Ground connection                                |

| D10        |         |            | NC              | No connection. Pin must be left floating  | J10        | Powe    |        | V <sub>SS</sub>       | Ground connection                                |

| E1         |         |            |                 | No connection. Pin must be left floating  | K1         | Powe    |        | V <sub>SS</sub>       | Ground connection                                |

| E2         | 1/0     | N.4        | NC              | No connection. Pin must be left floating  | K2         | Powe    | 1      | V <sub>SS</sub>       | Ground connection                                |

| E3         |         | M          | P4[3]           | Direct outlabed consolter black insut     | K3         |         |        | NC                    | No connection. Pin must be left floating         |

| E4         |         | I, M       | P2[3]           | Direct switched capacitor block input     | K4         | D.      |        | NC                    | No connection. Pin must be left floating         |

| E5         | Power   |            | V <sub>SS</sub> | Ground connection                         | K5         | Powe    | er -   | V <sub>DD</sub>       | Supply voltage                                   |

| E6         | Power   |            | V <sub>SS</sub> | Ground connection                         | K6         | I/O     | L      | P7[6]                 |                                                  |

| E7         |         | М          | P2[4]           | External AGND input                       | K7         | I/O     |        | P7[5]                 |                                                  |

| E8         |         | М          | P4[4]           |                                           | K8         | I/O     |        | P7[4]                 |                                                  |

| E9         | I/O     | М          | P3[6]           |                                           | K9         | Powe    |        | V <sub>SS</sub>       | Ground connection                                |

| E10        |         |            | NC              | No connection. Pin must be left floating  | K10        | Powe    | r      | V <sub>SS</sub>       | Ground connection                                |

LEGEND A = Analog, I = Input, O = Output, M = Analog Mux Input, NC = No connection. Pin must be left floating.

#### Figure 8. CY8C24094 OCD (Not for Production)

BGA (Top View)

Notes 15. All V<sub>SS</sub> pins should be brought out to one common GND plane. 16. These are the ISSP pins, which are not High Z at POR. See the PSoC Technical Reference Manual for details.

#### Figure 9. CY8C24094 OCD (Not for Production)

#### 9.7 100-Pin Part Pinout (On-Chip Debug)

The 100-pin TQFP part is for the CY8C24094 OCD PSoC device.

Note This part is only used for in-circuit debugging. It is NOT available for production.

#### Table 8. 100-Pin Part Pinout (TQFP<sup>[19]</sup>)

| Pin<br>No. | Digital | Analog | Name            | Description                                                       | Pin<br>No. | Digital | Analog   | Name            | Description                                   |

|------------|---------|--------|-----------------|-------------------------------------------------------------------|------------|---------|----------|-----------------|-----------------------------------------------|

| 1          |         |        | NC              | No connection. Pin must be left floating                          | 51         | I/O     | М        | P1[6]           |                                               |

| 2          |         | 1      | NC              | No connection. Pin must be left floating                          | 52         | I/O     | Μ        | P5[0]           |                                               |

| 3          | I/O     | I, M   | P0[1]           | Analog column mux input                                           | 53         | I/O     | М        | P5[2]           |                                               |

| 4          | I/O     | M      | P2[7]           |                                                                   | 54         | I/O     | М        | P5[4]           |                                               |

| 5          | I/O     | Μ      | P2[5]           |                                                                   | 55         | I/O     | Μ        | P5[6]           |                                               |

| 6          | I/O     | I, M   | P2[3]           | Direct switched capacitor block input                             | 56         | I/O     | М        | P3[0]           |                                               |

| 7          | I/O     | I, M   | P2[1]           | Direct switched capacitor block input                             | 57         | I/O     | М        | P3[2]           |                                               |

| 8          | I/O     | M      | P4[7]           |                                                                   | 58         | I/O     | М        | P3[4]           |                                               |

| 9          | I/O     | M      | P4[5]           |                                                                   | 59         | I/O     | М        | P3[6]           |                                               |

| 10         | I/O     | M      | P4[3]           |                                                                   | 60         |         |          | HCLK            | OCD high speed clock output                   |

| 11         | I/O     | Μ      | P4[1]           |                                                                   | 61         |         |          | CCLK            | OCD CPU clock output                          |

| 12         |         |        | OCDE            | OCD even data I/O                                                 | 62         | Input   |          | XRES            | Active high pin reset with internal pull-down |

| 13         |         |        | OCDO            | OCD odd data output                                               | 63         | I/O     | М        | P4[0]           |                                               |

| 14         | _       |        | NC              | No connection. Pin must be left floating                          | 64         | I/O     | Μ        | P4[2]           |                                               |

| 15         | Powe    |        | V <sub>SS</sub> | Ground connection                                                 | 65         | Powe    |          | V <sub>SS</sub> | Ground connection                             |

| 16         | I/O     | М      | P3[7]           |                                                                   | 66         | I/O     | М        | P4[4]           |                                               |

| 17         | I/O     | Μ      | P3[5]           |                                                                   | 67         | I/O     | Μ        | P4[6]           |                                               |

| 18         | I/O     | Μ      | P3[3]           |                                                                   | 68         | I/O     | I, M     | P2[0]           | Direct switched capacitor block input         |

| 19         | I/O     | Μ      | P3[1]           |                                                                   | 69         | I/O     | I, M     | P2[2]           | Direct switched capacitor block input         |

| 20         | I/O     | М      | P5[7]           |                                                                   | 70         | I/O     |          | P2[4]           | External AGND input                           |

| 21         | I/O     | М      | P5[5]           |                                                                   | 71         |         |          | NC              | No connection. Pin must be left floating      |

| 22         | I/O     | М      | P5[3]           |                                                                   | 72         | I/O     |          | P2[6]           | External VREF input                           |

| 23         | I/O     | Μ      | P5[1]           | 0                                                                 | 73         |         |          | NC              | No connection. Pin must be left floating      |

| 24         | I/O     | М      | P1[7]           | I <sup>2</sup> C SCL                                              | 74         | I/O     | I        | P0[0]           | Analog column mux input                       |

| 25         |         |        | NC              | No connection. Pin must be left floating                          | 75         |         |          | NC              | No connection. Pin must be left floating      |

| 26         |         |        | NC              | No connection. Pin must be left floating                          | 76         |         |          | NC              | No connection. Pin must be left floating      |

| 27         |         |        | NC              | No connection. Pin must be left floating                          | 77         | I/O     | I, M     | P0[2]           | Analog column mux input and column output     |

| 28         | I/O     |        | P1[5]           | I <sup>2</sup> C SDA                                              | 78         |         |          | NC              | No connection. Pin must be left floating      |

| 29         | I/O     |        | P1[3]           |                                                                   | 79         | I/O     | I, M     | P0[4]           | Analog column mux input and column output     |

| 30         | I/O     |        | P1[1]           | Crystal (XTALin), I <sup>2</sup> C SCL, ISSP SCLK <sup>[20]</sup> | 80         |         |          | NC              | No connection. Pin must be left floating      |

| 31         |         |        | NC              | No connection. Pin must be left floating                          | 81         | I/O     | I, M     | P0[6]           | Analog column mux input                       |

| 32         | Powe    | er     | V <sub>SS</sub> | Ground connection                                                 | 82         | Powe    | er       | V <sub>DD</sub> | Supply voltage                                |

| 33         | USB     |        | D+              |                                                                   | 83         |         |          | NC              | No connection. Pin must be left floating      |

| 34         | USB     |        | D-              |                                                                   | 84         | Powe    | er       | V <sub>SS</sub> | Ground connection                             |

| 35         | Powe    | er     | V <sub>DD</sub> | Supply voltage                                                    | 85         |         |          | NC              | No connection. Pin must be left floating      |

| 36         | I/O     |        | P7[7]           |                                                                   | 86         |         |          | NC              | No connection. Pin must be left floating      |

| 37         | I/O     |        | P7[6]           |                                                                   | 87         |         |          | NC              | No connection. Pin must be left floating      |

| 38         | I/O     |        | P7[5]           |                                                                   | 88         |         |          | NC              | No connection. Pin must be left floating      |

| 39         | I/O     |        | P7[4]           |                                                                   | 89         |         |          | NC              | No connection. Pin must be left floating      |

| 40         | I/O     |        | P7[3]           |                                                                   | 90         |         |          | NC              | No connection. Pin must be left floating      |

| 41         | I/O     |        | P7[2]           |                                                                   | 91         | NC      |          | NC              | No connection. Pin must be left floating      |

| 42         | I/O     |        | P7[1]           |                                                                   | 92         |         |          | NC              | No connection. Pin must be left floating      |

| 43         | I/O     |        | P7[0]           |                                                                   | 93         |         |          | NC              | No connection. Pin must be left floating      |

| 44         |         |        | NC              | No connection. Pin must be left floating                          | 94         |         |          | NC              | No connection. Pin must be left floating      |

| 45         |         |        | NC              | No connection. Pin must be left floating                          | 95         | I/O     | I, M     | P0[7]           | Analog column mux input                       |

| 46         |         |        | NC              | No connection. Pin must be left floating                          | 96         |         |          | NC              | No connection. Pin must be left floating      |

| 47         |         |        | NC              | No connection. Pin must be left floating                          | 97         | I/O     | I/O, M   | P0[5]           | Analog column mux input and column output     |

| 48         | I/O     |        | P1[0]           | Crystal (XTALout), I2C SDA, ISSP SDATA <sup>[20]</sup>            | 98         |         |          | NC              | No connection. Pin must be left floating      |

| 49         | I/O     | 1      | P1[2]           |                                                                   | 99         | I/O     | I/O, M   | P0[3]           | Analog column mux input and column output     |

| 50         | I/O     | 1      | P1[4]           | Optional EXTCLK                                                   | 100        |         |          | NC              | No connection. Pin must be left floating      |

|            |         | - 4 -  |                 | It. O = Output. NC = No connection. Pin must be left              | flooting   | N4 - 4  | Analog M |                 | DOD - On Ohin Dahuman                         |

LEGEND A = Analog, I = Input, O = Output, NC = No connection. Pin must be left floating, M = Analog Mux Input, OCD = On-Chip Debugger.

#### Notes

19. All V<sub>SS</sub> pins should be brought out to one common GND plane.

20. These are the ISSP pins, which are not High Z at POR. See the PSoC Technical Reference Manual for details.

### 10.3 Register Map Bank 0 Table: User Space

| Name     | Addr (0, Hex) | Access | Name                 | Addr (0, Hex) | Access  | Name               | Addr (0, Hex) | Access | Name     | Addr (0, Hex) | Acces    |

|----------|---------------|--------|----------------------|---------------|---------|--------------------|---------------|--------|----------|---------------|----------|

| PRTODR   | 00            | RW     | PMA0 DR              | 40            | RW      | ASC10CR0           | 80            | RW     | Hame     | C0            | Acces    |

| PRTOIE   | 01            | RW     | PMA1_DR              | 41            | RW      | ASC10CR1           | 81            | RW     |          | C1            |          |

| PRT0GS   | 02            | RW     | PMA2 DR              | 42            | RW      | ASC10CR2           | 82            | RW     |          | C2            |          |

| PRT0DM2  | 03            | RW     | PMA3 DR              | 43            | RW      | ASC10CR3           | 83            | RW     |          | C3            |          |

| PRT1DR   | 04            | RW     | PMA4 DR              | 44            | RW      | ASD11CR0           | 84            | RW     |          | C4            |          |

| PRT1IE   | 05            | RW     | PMA5 DR              | 45            | RW      | ASD11CR1           | 85            | RW     |          | C5            |          |

| PRT1GS   | 06            | RW     | PMA6 DR              | 46            | RW      | ASD11CR2           | 86            | RW     |          | C6            |          |

| PRT1DM2  | 07            | RW     | PMA7 DR              | 47            | RW      | ASD11CR3           | 87            | RW     |          | C7            |          |

| PRT2DR   | 08            | RW     | USB SOF0             | 48            | R       | 7 OD TTOTIO        | 88            |        | -        | C8            |          |

| PRT2IE   | 09            | RW     | USB SOF1             | 49            | R       |                    | 89            |        |          | C9            | -        |

| PRT2GS   | 03<br>0A      | RW     | USB CR0              | 43<br>4A      | RW      |                    | 8A            |        |          | CA            | +        |

| PRT2DM2  | 0A<br>0B      | RW     | USBI/O CR0           | 4B            | #       |                    | 8B            | -      |          | CB            |          |

| PRT3DR   | 00            | RW     | USBI/O CR1           | 4D<br>4C      | #<br>RW |                    | 8C            |        |          | CC            |          |

| PRT3IE   | 0C            | RW     | 03BI/0_CK1           | 40<br>4D      | RW.     |                    | 8D            |        |          | CD            | +        |

| PRT3GS   | 0D<br>0E      | RW     | EP1 CNT1             | 4D<br>4E      | #       |                    | 8E            |        |          | CE            |          |

|          | 0E<br>0F      | RW     | -                    | 4E<br>4F      |         |                    | 8E<br>8F      |        |          | CE            |          |

| PRT3DM2  | -             |        | EP1_CNT              |               | RW      | 4000000            |               | DW     |          | -             | D)4/     |

| PRT4DR   | 10            | RW     | EP2_CNT1             | 50            | #       | ASD20CR0           | 90            | RW     | CUR_PP   | D0            | RW       |

| PRT4IE   | 11            | RW     | EP2_CNT              | 51            | RW      | ASD20CR1           | 91            | RW     | STK_PP   | D1            | RW       |

| PRT4GS   | 12            | RW     | EP3_CNT1             | 52            | #       | ASD20CR2           | 92            | RW     |          | D2            | D14/     |

| PRT4DM2  | 13            | RW     | EP3_CNT              | 53            | RW      | ASD20CR3           | 93            | RW     | IDX_PP   | D3            | RW       |

| PRT5DR   | 14            | RW     | EP4_CNT1             | 54            | #       | ASC21CR0           | 94            | RW     | MVR_PP   | D4            | RW       |

| PRT5IE   | 15            | RW     | EP4_CNT              | 55            | RW      | ASC21CR1           | 95            | RW     | MVW_PP   | D5            | RW       |

| PRT5GS   | 16            | RW     | EP0_CR               | 56            | #       | ASC21CR2           | 96            | RW     | I2C_CFG  | D6            | RW       |

| PRT5DM2  | 17            | RW     | EP0_CNT              | 57            | #       | ASC21CR3           | 97            | RW     | I2C_SCR  | D7            | #        |

|          | 18            |        | EP0_DR0              | 58            | RW      |                    | 98            |        | I2C_DR   | D8            | RW       |

|          | 19            |        | EP0_DR1              | 59            | RW      |                    | 99            |        | I2C_MSCR | D9            | #        |

|          | 1A            |        | EP0_DR2              | 5A            | RW      |                    | 9A            |        | INT_CLR0 | DA            | RW       |

|          | 1B            |        | EP0_DR3              | 5B            | RW      |                    | 9B            |        | INT_CLR1 | DB            | RW       |

| PRT7DR   | 1C            | RW     | EP0_DR4              | 5C            | RW      |                    | 9C            |        | INT_CLR2 | DC            | RW       |

| PRT7IE   | 1D            | RW     | EP0_DR5              | 5D            | RW      |                    | 9D            |        | INT_CLR3 | DD            | RW       |

| PRT7GS   | 1E            | RW     | EP0_DR6              | 5E            | RW      |                    | 9E            |        | INT_MSK3 | DE            | RW       |

| PRT7DM2  | 1F            | RW     | EP0_DR7              | 5F            | RW      |                    | 9F            |        | INT_MSK2 | DF            | RW       |

| DBB00DR0 | 20            | #      | AMX_IN               | 60            | RW      |                    | A0            |        | INT_MSK0 | E0            | RW       |

| DBB00DR1 | 21            | W      | AMUXCFG              | 61            | RW      |                    | A1            |        | INT_MSK1 | E1            | RW       |

| DBB00DR2 | 22            | RW     |                      | 62            |         |                    | A2            |        | INT_VC   | E2            | RC       |

| DBB00CR0 | 23            | #      | ARF_CR               | 63            | RW      |                    | A3            |        | RES_WDT  | E3            | W        |

| DBB01DR0 | 24            | #      | CMP_CR0              | 64            | #       |                    | A4            |        | DEC_DH   | E4            | RC       |

| DBB01DR1 | 25            | W      | ASY_CR               | 65            | #       |                    | A5            |        | DEC_DL   | E5            | RC       |

| DBB01DR2 | 26            | RW     | CMP_CR1              | 66            | RW      |                    | A6            |        | DEC_CR0  | E6            | RW       |

| DBB01CR0 | 27            | #      |                      | 67            |         |                    | A7            |        | DEC_CR1  | E7            | RW       |

| DCB02DR0 | 28            | #      |                      | 68            |         | MUL1_X             | A8            | W      | MULO X   | E8            | W        |

| DCB02DR1 | 29            | W      |                      | 69            |         | MUL1_Y             | A9            | W      | MUL0 Y   | E9            | W        |

| DCB02DR2 | 2A            | RW     |                      | 6A            |         | MUL1 DH            | AA            | R      | MUL0 DH  | EA            | R        |

| DCB02CR0 | 2B            | #      |                      | 6B            |         | MUL1 DL            | AB            | R      | MUL0 DL  | EB            | R        |

| DCB03DR0 | 2C            | #      | TMP DR0              | 6C            | RW      | ACC1 DR1           | AC            | RW     | ACC0 DR1 | EC            | RW       |

| DCB03DR1 | 20<br>2D      | W      | TMP DR1              | 6D            | RW      | ACC1 DR0           | AD            | RW     | ACC0 DR0 | ED            | RW       |

| DCB03DR2 | 2E            | RW     | TMP_DR2              | 6E            | RW      | ACC1_DR3           | AE            | RW     | ACC0_DR3 | EE            | RW       |

| DCB03CR0 | 2E            | #      | TMP_DR3              | 6F            | RW      | ACC1 DR2           | AF            | RW     | ACC0 DR2 | EF            | RW       |

|          | 30            | +      | ACB00CR3             | 70            | RW      | RDIORI             | B0            | RW     |          | F0            | +        |

|          | 31            |        | ACB00CR0             | 71            | RW      | RDIOSYN            | B1            | RW     |          | F1            |          |

|          | 32            | 1      | ACB00CR0             | 72            | RW      | RDI0IS             | B1<br>B2      | RW     |          | F2            | +        |

|          | 33            | +      | ACB00CR1             | 72            | RW      | RDI0LT0            | B3            | RW     |          | F2<br>F3      | ───      |

|          | 34            | +      | ACB00CR2<br>ACB01CR3 | 73            | RW      | RDI0LT0            | B3<br>B4      | RW     |          | F3            | ───      |

|          | 34            |        | ACB01CR3<br>ACB01CR0 | 74 75         | RW      | RDI0LTT<br>RDI0R00 | B4<br>B5      | RW     |          | F4<br>F5      | ┨────    |

|          | 36            |        | ACB01CR0<br>ACB01CR1 | 75            | RW      | RDI0R00            | B5<br>B6      | RW     |          | F5<br>F6      |          |

|          | 36<br>37      | +      | ACB01CR1<br>ACB01CR2 |               |         | RUIURUT            |               | LVA V  | CPU F    | F6<br>F7      | DI       |

|          |               | +      | ACDUICKZ             | 77            | RW      |                    | B7            |        | CPU_F    |               | RL       |

|          | 38            |        |                      | 78            |         |                    | B8            |        |          | F8            |          |

|          | 39            | -      | I                    | 79            |         |                    | B9            |        |          | F9            |          |

|          | 3A            |        | Į                    | 7A<br>7D      |         | Į                  | BA            |        |          | FA            | <u> </u> |

|          | 3B            |        | Į                    | 7B            |         |                    | BB            |        |          | FB            | <u> </u> |

|          | 3C            |        | l                    | 7C            |         |                    | BC            |        |          | FC            | L        |

|          | 3D            |        | Į                    | 7D            |         |                    | BD            |        | DAC_D    | FD            | RW       |

|          | 3E            |        | I                    | 7E            |         |                    | BE            |        | CPU_SCR1 | FE            | #        |

|          | 3F            |        |                      | 7F            | 1       |                    | BF            |        | CPU SCR0 | FF            | #        |

# Access is bit specific.

### 11.2 Operating Temperature

#### Table 10. Operating Temperature

| Symbol            | Description                   | Min | Тур | Max  | Units | Notes                                                                                                                                                                                             |

|-------------------|-------------------------------|-----|-----|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>A</sub>    | Ambient temperature           | -40 | -   | +85  | °C    |                                                                                                                                                                                                   |

| T <sub>AUSB</sub> | Ambient temperature using USB | -10 | -   | +85  | °C    |                                                                                                                                                                                                   |

| Тј                | Junction temperature          | -40 | -   | +100 | °C    | The temperature rise from<br>ambient to junction is package<br>specific. See Thermal<br>Impedance on page 51. The<br>user must limit the power<br>consumption to comply with<br>this requirement. |

### **11.3 DC Electrical Characteristics**

#### 11.3.1 DC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 11. DC Chip-Level Specifications

| Symbol           | Description                                                                                      | Min | Тур | Max  | Units | Notes                                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------|-----|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>  | Supply voltage                                                                                   | 3.0 | _   | 5.25 | V     | See DC POR and LVD specifications,<br>Table 22 on page 39.                                                                                                             |

| I <sub>DD5</sub> | Supply current, IMO = 24 MHz (5 V)                                                               | _   | 14  | 27   | mA    | Conditions are $V_{DD}$ = 5.0 V, $T_A$ = 25 °C,<br>CPU = 3 MHz, SYSCLK doubler<br>disabled,<br>VC1 = 1.5 MHz, VC2 = 93.75 kHz,<br>VC3 = 93.75 kHz, analog power = off. |

| I <sub>DD3</sub> | Supply current, IMO = 24 MHz (3.3 V)                                                             | _   | 8   | 14   | mA    | Conditions are $V_{DD}$ = 3.3 V, $T_A$ = 25 °C,<br>CPU = 3 MHz, SYSCLK doubler<br>disabled,<br>VC1 = 1.5 MHz, VC2 = 93.75 kHz,<br>VC3 = 0.367 kHz, analog power = off. |

| I <sub>SB</sub>  | Sleep <sup>[21]</sup> (mode) current with POR, LVD, sleep timer, and WDT. <sup>[22]</sup>        | _   | 3   | 6.5  | μA    | Conditions are with internal slow speed oscillator, V <sub>DD</sub> = 3.3 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 55 °C, analog power = off.                            |

| I <sub>SBH</sub> | Sleep (mode) current with POR, LVD, Sleep<br>Timer, and WDT at high temperature. <sup>[22]</sup> | -   | 4   | 25   | μA    | Conditions are with internal slow speed oscillator, $V_{DD}$ = 3.3 V, 55 °C < T <sub>A</sub> $\leq$ 85 °C, analog power = off.                                         |

Notes

21. Errata: When the device is operating at 4.75 V to 5.25 V and the 3.3 V regulator is enabled, a short low pulse may be created on the DP signal line during device wake-up. The 15-20 µs low pulse of the DP line may be interpreted by the host computer as a deattach or the beginning of a wake-up. More details in "Errata" on page 66.

22. Standby current includes all functions (POR, LVD, WDT, Sleep Time) needed for reliable system operation. This should be compared with devices that have similar functions enabled.

#### Table 19. 5-V DC Analog Reference Specifications (continued)

| Refer-<br>ence<br>ARF_CR<br>[5:3] | Reference Power<br>Settings          | Symbol             | Reference | Description                                     | Min             | Тур                     | Мах                     | Unit<br>s |

|-----------------------------------|--------------------------------------|--------------------|-----------|-------------------------------------------------|-----------------|-------------------------|-------------------------|-----------|

| 0b101                             | RefPower = high<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.218   | P2[4] + 1.291           | P2[4] + 1.354           | V         |

|                                   |                                      | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -         |

|                                   |                                      | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.335   | P2[4] – 1.294           | P2[4] – 1.237           | V         |

|                                   | RefPower = high<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.221   | P2[4] + 1.293           | P2[4] + 1.358           | V         |

|                                   |                                      | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -         |

|                                   |                                      | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.337   | P2[4] – 1.297           | P2[4] – 1.243           | V         |

|                                   | RefPower =<br>medium                 | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.222   | P2[4] + 1.294           | P2[4] + 1.360           | V         |

|                                   | Opamp bias = high                    | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -         |

|                                   |                                      | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.338   | P2[4] – 1.298           | P2[4] – 1.245           | V         |

|                                   | RefPower =<br>medium                 | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.221   | P2[4] + 1.294           | P2[4] + 1.362           | V         |

|                                   | Opamp bias = low                     | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -         |

|                                   |                                      | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.340   | P2[4] – 1.298           | P2[4] – 1.245           | V         |

| 0b110                             | RefPower = high                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.513           | 2.593                   | 2.672                   | V         |

|                                   | Opamp bias = high                    | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.264           | 1.302                   | 1.340                   | V         |

|                                   |                                      | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.008 | V <sub>SS</sub> + 0.038 | V         |

|                                   | RefPower = high                      | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.514           | 2.593                   | 2.674                   | V         |

|                                   | Opamp bias = low                     | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.264           | 1.301                   | 1.340                   | V         |

|                                   |                                      | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.005 | V <sub>SS</sub> + 0.028 | V         |

|                                   | RefPower =                           | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.514           | 2.593                   | 2.676                   | V         |

|                                   | medium<br>Opamp bias = high          | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.264           | 1.301                   | 1.340                   | V         |

|                                   | - party and a right                  | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.024 | V         |

|                                   | RefPower =                           | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.514           | 2.593                   | 2.677                   | V         |

|                                   | medium<br>Opamp bias = low           | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.264           | 1.300                   | 1.340                   | V         |

|                                   |                                      | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.021 | V         |

#### Table 19. 5-V DC Analog Reference Specifications (continued)

| Refer-<br>ence<br>ARF_CR<br>[5:3] | Reference Power<br>Settings         | Symbol             | Reference | Description     | Min             | Тур                     | Мах                     | Unit<br>s |

|-----------------------------------|-------------------------------------|--------------------|-----------|-----------------|-----------------|-------------------------|-------------------------|-----------|

| 0b111                             | RefPower = high                     | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap   | 4.028           | 4.144                   | 4.242                   | V         |

|                                   | Opamp bias = high                   | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap   | 2.028           | 2.076                   | 2.125                   | V         |

|                                   |                                     | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.008 | V <sub>SS</sub> + 0.034 | V         |

|                                   | RefPower = high<br>Opamp bias = low | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap   | 4.032           | 4.142                   | 4.245                   | V         |

|                                   |                                     | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap   | 2.029           | 2.076                   | 2.126                   | V         |

|                                   |                                     | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.005 | V <sub>SS</sub> + 0.025 | V         |

|                                   | RefPower =                          | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap   | 4.034           | 4.143                   | 4.247                   | V         |

|                                   | medium<br>Opamp bias = high         | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap   | 2.029           | 2.076                   | 2.126                   | V         |

|                                   |                                     | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.021 | V         |

|                                   | RefPower =                          | V <sub>REFHI</sub> | Ref High  | 3.2 × Bandgap   | 4.036           | 4.144                   | 4.249                   | V         |

|                                   | medium<br>Opamp bias = low          | V <sub>AGND</sub>  | AGND      | 1.6 × Bandgap   | 2.029           | 2.076                   | 2.126                   | V         |

|                                   |                                     | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.019 | V         |

#### 11.4.3 AC Full Speed USB Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-10 \degree C \le T_A \le 85 \degree C$ , or 3.0 V to 3.6 V and  $-10 \degree C \le T_A \le 85 \degree C$ , respectively. Typical parameters are measured at 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 27. AC Full Speed (12 Mbps) USB Specifications

| Symbol               | Description                                                | Min      | Тур | Max        | Units | Notes          |

|----------------------|------------------------------------------------------------|----------|-----|------------|-------|----------------|

| t <sub>RFS</sub>     | Transition rise time                                       | 4        | -   | 20         | ns    | For 50 pF load |

| t <sub>FSS</sub>     | Transition fall time                                       | 4        | -   | 20         | ns    | For 50 pF load |

| t <sub>RFMFS</sub>   | Rise/fall time matching: (t <sub>R/</sub> t <sub>F</sub> ) | 90       | -   | 111        | %     | For 50 pF load |

| t <sub>DRATEFS</sub> | Full speed data rate                                       | 12-0.25% | 12  | 12 + 0.25% | Mbps  |                |

#### 11.4.4 AC Operational Amplifier Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V and 3.3 V at 25 °C and are for design guidance only.

Settling times, slew rates, and gain bandwidth are based on the analog continuous time PSoC block.

Power = high and Opamp bias = high is not supported at 3.3 V.

| Table 28. | 5-V AC Operational Amplifier Specifications |

|-----------|---------------------------------------------|

|-----------|---------------------------------------------|

| Symbol            | Description                                                                                 | Min  | Тур | Max  | Units    |

|-------------------|---------------------------------------------------------------------------------------------|------|-----|------|----------|

| t <sub>ROA</sub>  | Rising settling time from 80% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain)  |      |     |      |          |

|                   | Power = low, Opamp bias = low                                                               | -    | -   | 3.9  | μs       |

|                   | Power = medium, Opamp bias = high                                                           | -    | -   | 0.72 | μs       |

|                   | Power = high, Opamp bias = high                                                             | -    | —   | 0.62 | μs       |

| t <sub>SOA</sub>  | Falling settling time from 20% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain) |      |     |      |          |

|                   | Power = low, Opamp bias = low                                                               | -    | _   | 5.9  | μs       |

|                   | Power = medium, Opamp bias = high                                                           | -    | -   | 0.92 | μs       |

|                   | Power = high, Opamp bias = high                                                             | -    | -   | 0.72 | μs       |

| SR <sub>ROA</sub> | Rising slew rate (20% to 80%)(10 pF load, unity gain)                                       |      |     |      |          |

|                   | Power = low, Opamp bias = low                                                               | 0.15 | -   | -    | V/µs     |

|                   | Power = medium, Opamp bias = high                                                           | 1.7  | _   | -    | V/µs     |

|                   | Power = high, Opamp bias = high                                                             | 6.5  | -   | -    | V/µs     |

| SR <sub>FOA</sub> | Falling slew rate (20% to 80%)(10 pF load, unity gain)                                      |      |     |      |          |

|                   | Power = low, Opamp bias = low                                                               | 0.01 | _   | -    | V/µs     |

|                   | Power = medium, Opamp bias = high                                                           | 0.5  | -   | -    | V/µs     |

|                   | Power = high, Opamp bias = high                                                             | 4.0  | _   | -    | V/µs     |

| BW <sub>OA</sub>  | Gain bandwidth product                                                                      |      |     |      |          |

|                   | Power = low, Opamp bias = low                                                               | 0.75 | -   | -    | MHz      |

|                   | Power = medium, Opamp bias = high                                                           | 3.1  | -   | —    | MHz      |

|                   | Power = high, Opamp bias = high                                                             | 5.4  | -   | _    | MHz      |

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = medium, Opamp bias = high)                                          | -    | 100 | _    | nV/rt-Hz |

#### Table 29. 3.3-V AC Operational Amplifier Specifications

| Symbol            | Description                                                                                 | Min  | Тур | Max  | Units    |

|-------------------|---------------------------------------------------------------------------------------------|------|-----|------|----------|

| t <sub>ROA</sub>  | Rising settling time from 80% of $\Delta V$ to 0.1% of $\Delta V$                           |      |     |      |          |

|                   | (10 pF load, unity gain)                                                                    |      |     | 0.00 |          |

|                   | Power = low, Opamp bias = low                                                               | -    | -   | 3.92 | μs       |

|                   | Power = medium, Opamp bias = high                                                           | -    | _   | 0.72 | μs       |

| t <sub>SOA</sub>  | Falling settling time from 20% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, unity gain) |      |     |      |          |

|                   | Power = low, Opamp bias = low                                                               | -    | _   | 5.41 | μs       |

|                   | Power = medium, Opamp bias = high                                                           | -    | -   | 0.72 | μs       |

| SR <sub>ROA</sub> | Rising slew rate (20% to 80%)(10 pF load, unity gain)                                       |      |     |      |          |

| _                 | Power = low, Opamp bias = low                                                               | 0.31 | -   | -    | V/µs     |

|                   | Power = medium, Opamp bias = high                                                           | 2.7  | -   | -    | V/µs     |

| SR <sub>FOA</sub> | Falling slew rate (20% to 80%)(10 pF load, Unity Gain)                                      |      |     |      |          |

| 1 671             | Power = low, Opamp bias = low                                                               | 0.24 | -   | _    | V/µs     |

|                   | Power = medium, Opamp bias = high                                                           | 1.8  | -   | -    | V/µs     |

| BW <sub>OA</sub>  | Gain bandwidth product                                                                      |      |     |      |          |

| <u>e</u> rt       | Power = low, Opamp bias = low                                                               | 0.67 | -   | _    | MHz      |

|                   | Power = medium, Opamp bias = high                                                           | 2.8  | -   | —    | MHz      |

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = medium, Opamp bias = high)                                          | -    | 100 | -    | nV/rt-Hz |

#### Table 31. AC Digital Block Specifications (continued)

| Function                | Description                               | Min                | Тур | Max       | Unit | Notes                                                                                     |  |  |

|-------------------------|-------------------------------------------|--------------------|-----|-----------|------|-------------------------------------------------------------------------------------------|--|--|

| CRCPRS                  | Input clock frequency                     |                    |     |           |      |                                                                                           |  |  |

| (PRS<br>Mode)           | $V_{DD} \ge 4.75 \text{ V}$               | -                  | -   | 49.9<br>2 | MHz  |                                                                                           |  |  |

|                         | V <sub>DD</sub> < 4.75 V                  | -                  | Ι   | 25.9<br>2 | MHz  |                                                                                           |  |  |

| CRCPRS<br>(CRC<br>Mode) | Input clock frequency                     | -                  | -   | 24.6      | MHz  |                                                                                           |  |  |

| SPIM                    | Input clock frequency                     | -                  | -   | 8.2       | MHz  | The SPI serial clock (SCLK) frequency is equal to the input clock frequency divided by 2. |  |  |

| SPIS                    | Input clock (SCLK) frequency              | -                  | -   | 4.1       | MHz  | The input clock is the SPI SCLK in SPIS mode.                                             |  |  |

|                         | Width of SS_negated between transmissions | 50 <sup>[33]</sup> | -   | -         | ns   |                                                                                           |  |  |

| Transmitter             | Input clock frequency                     |                    |     |           |      | The baud rate is equal to the input clock                                                 |  |  |

|                         | $V_{DD} \ge 4.75$ V, 2 stop bits          | -                  | -   | 49.9<br>2 | MHz  | frequency divided by 8.                                                                   |  |  |

|                         | $V_{DD} \ge 4.75$ V, 1 stop bit           | -                  | -   | 24.6      | MHz  |                                                                                           |  |  |

|                         | V <sub>DD</sub> < 4.75 V                  | -                  | -   | 24.6      | MHz  |                                                                                           |  |  |

| Receiver                | Input clock frequency                     |                    |     |           |      | The baud rate is equal to the input clock                                                 |  |  |

|                         | $V_{DD} \ge 4.75$ V, 2 stop bits          | -                  | -   | 49.9<br>2 | MHz  | frequency divided by 8.                                                                   |  |  |

|                         | $V_{DD} \ge 4.75$ V, 1 stop bit           | -                  | -   | 24.6      | MHz  |                                                                                           |  |  |

|                         | V <sub>DD</sub> < 4.75 V                  | -                  | _   | 24.6      | MHz  |                                                                                           |  |  |

#### 11.4.7 AC External Clock Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters are measured at 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 32. AC External Clock Specifications

| Symbol  | Description                    | Min   | Тур | Max   | Units | Notes |

|---------|--------------------------------|-------|-----|-------|-------|-------|

| FOSCEXT | Frequency for USB applications | 23.94 | 24  | 24.06 | MHz   |       |

| -       | Duty cycle                     | 47    | 50  | 53    | %     |       |

| -       | Power-up to IMO switch         | 150   | -   | -     | μs    |       |

## 12. Development Tool Selection

#### 12.1 Software

#### 12.1.1 PSoC Designer

At the core of the PSoC development software suite is PSoC Designer, used to generate PSoC firmware applications. PSoC Designer is available free of charge at http://www.cypress.com and includes a free C compiler.

#### 12.1.2 PSoC Programmer

Flexible enough to be used on the bench in development, yet suitable for factory programming, PSoC Programmer works either as a standalone programming application or it can operate directly from PSoC Designer. PSoC Programmer software is compatible with both PSoC ICE-Cube in-circuit emulator and PSoC MiniProg. PSoC programmer is available free of charge at http://www.cypress.com.

#### 12.2 Development Kits

All development kits can be purchased from the Cypress Online Store.

#### 12.2.1 CY3215-DK Basic Development Kit

The CY3215-DK is for prototyping and development with PSoC Designer. This kit supports in-circuit emulation, and the software interface enables you to run, halt, and single step the processor, and view the content of specific memory locations. Advance emulation features are also supported through PSoC Designer. The kit includes:

- PSoC Designer software CD

- ICE-Cube in-circuit Emulator

- ICE Flex-Pod for CY8C29x66 family

- Cat-5 adapter

- MiniEval programming board

- 110 ~ 240 V power supply, Euro-Plug adapter

- iMAGEcraft C compiler (registration required)

- ISSP cable

- USB 2.0 cable and Blue Cat-5 cable

- Two CY8C29466-24PXI 28-PDIP chip samples

#### 12.3 Evaluation Tools

All evaluation tools can be purchased from the Cypress Online Store.

#### 12.3.1 CY3210-MiniProg1

The CY3210-MiniProg1 kit enables you to program PSoC devices via the MiniProg1 programming unit. The MiniProg is a small, compact prototyping programmer that connects to the PC via a provided USB 2.0 cable. The kit includes:

- MiniProg programming unit

- MiniEval socket programming and evaluation board

- 28-Pin CY8C29466-24PXI PDIP PSoC device sample

- 28-Pin CY8C27443-24PXI PDIP PSoC device sample

- PSoC Designer software CD

- Getting Started guide

- USB 2.0 cable

#### 12.3.2 CY3210-PSoCEval1

The CY3210-PSoCEval1 kit features an evaluation board and the MiniProg1 programming unit. The evaluation board includes an LCD module, potentiometer, LEDs, and plenty of breadboarding space to meet all of your evaluation needs. The kit includes:

- Evaluation board with LCD module

- MiniProg programming unit

- 28-Pin CY8C29466-24PXI PDIP PSoC device sample (2)

- PSoC Designer software CD

- Getting Started guide

- USB 2.0 cable

#### 12.3.3 CY3214-PSoCEvalUSB

The CY3214-PSoCEvalUSB evaluation kit features a development board for the CY8C24794-24LTXI PSoC device. The board supports both USB and capacitive sensing development and debugging support. This evaluation board also includes an LCD module, potentiometer, LEDs, an enunciator and plenty of breadboarding space to meet all of your evaluation needs. The kit includes:

- PSoCEvalUSB board

- LCD module

- MIniProg programming unit

- Mini USB cable

- PSoC Designer and Example Projects CD

- Getting Started guide

- Wire pack

#### 12.4 Device Programmers

All device programmers can be purchased from the Cypress Online Store.

#### 12.4.1 CY3216 Modular Programmer

The CY3216 Modular Programmer kit features a modular programmer and the MiniProg1 programming unit. The modular programmer includes three programming module cards and supports multiple Cypress products. The kit includes:

- Modular programmer base

- Three programming module cards

- MiniProg programming unit

- PSoC Designer software CD

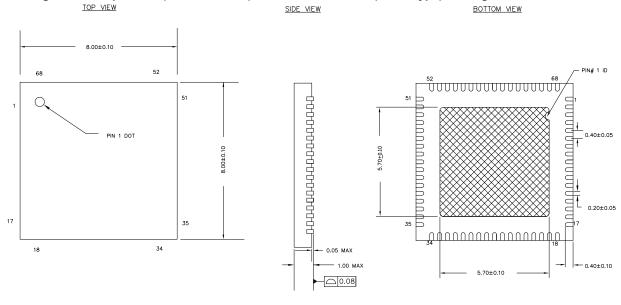

#### Figure 19. 68-pin QFN (8 × 8 × 1.0 mm) LT68 5.7 × 5.7 E-Pad (Sawn Type) Package Outline, 001-09618

NOTES:

1. 🗱 HATCH AREA IS SOLDERABLE EXPOSED METAL.

2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT:  $17 \pm 2mg$

- 4. ALL DIMENSIONS ARE IN MILLIMETERS

001-09618 \*E

# 15. Acronyms

### 15.1 Acronyms Used

The following table lists the acronyms that are used in this document.

| Acronym | Description                                         | Acronym | Description                                   |